4.3__LPM_ROM宏模块H的使用

EDA技术P10-宏模块和IP使用方法新

什么是IP?

知识产权(IP)是指专利、商标、版权等形式的法律保护下的创意和创新。

宏模块与IP的区别

宏模块是具体的硬件设计,而IP是具备知识产权的创新设计,可以包含宏模块。

宏模块和IP的使用价值

宏模块和IP的使用可以加快电路设计过程、提高设计的可靠性以及降低开发成 本。

EDA技术P10-宏模块和IP 使用方法新

本演示介绍EDA技术中的宏模块和IP的使用方法。探索它们的定义、差异、设 计流程、测试与验证以及应用领域。了解宏模块和IP在电路设计中的重要作用。

EDA技术简介

电子设计自动化(EDA)是使用计算机软件和工具来设计、分析和验证集成电路系统的方法。

什么是宏模块?

如何使用宏模块和IP?

使用宏模块和IP要注意选择适合项目需求的设计,灵活运用标准接口和库。

宏模块的设计流程

1

设计

2

使用EDA工具进行宏模块的设计。

3

需求分析

确定宏模块的功能和特性。

验证

对宏模块进行功能验证和仿真。

IP的设计流程

1

需求分析

确定IP的功能和特性。

设计

2

使用EDA工具进行IP的设计。

3

验证

对IP进行功能验证和仿真。

宏模块的测试与验证

测试和验证宏模块的功能和性能是确保其正确工作的关键步骤。

IP的测试与验证

测试和验证IP的功能和性能是确保其正确工作的关键步骤。

宏模块和IP的维护

定期进行宏模块和IP的维护,包括修复错误、改进性能和支持新的软件和硬件 标准。

常见的宏模块

常见的宏模块包括时钟模块、存储器控制器和通信接口。

实验2参数可设置宏功能模块lpm的应用

功能描述

浮点加法器、减法器模块 浮点参数化除法器宏模块 浮点参数化乘法器宏模块 参数化存储乘法器宏模块 参数化乘累加器宏模块 参数化乘加器宏模块 参数化整数平方根运算宏模块 参数化除法器宏模块 参数化绝对值运算宏模块(Altera推荐使用)

10 lpm_add_sub

11 lpm_compare 12 lpm_counter 13 lpm_divide

参数化加法器-减法器宏模块(Altera推荐使 用)

参数化比较器宏模块(Altera推荐使用) 参数化计数器宏模块(Altera推荐使用) 参数化除法器宏模块(Altera推荐使用)

第四页,编辑于星期三:十二点 三十分。

一、参数可设置模块库(续3)

门电路

序号 模块名称

功能描述

1 lpm_and/or/xor 参数化与门模块/或门/异或门模块

地址低4位,十 六进制表示9

地址高4位,十 六进制表示9

存储数据 9 ×9=81

保存,文件名romdata.hex

第十三页,编辑于星期三:十二点 三十分。

二、利用lpm-rom设计一个乘法器

定制lpm_rom元件 Tools→MegaWizard Plug-In Manager

第十四页,编辑于星期三:十二点 三十分。

第七页,编辑于星期三:十二点 三十分。

一、参数可设置模块库(续6)

2、调用宏功能模块的方法

新建原理图编辑文件,双击 打开Symbol对话框调用

也可通过菜单Tools→MegaWizard Plug-In Manager

第八页,编辑于星期三:十二点 三十分。

二、利用lpm-rom设计一个乘法器

1、ROM工作原理

二、利用lpm-rom设计一个乘法器

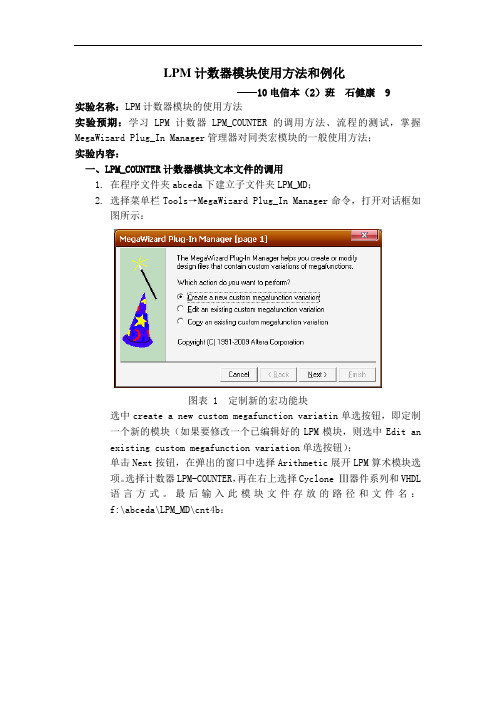

LPM计数器模块使用方法

LPM计数器模块使用方法和例化——10电信本(2)班石健康 9实验名称:LPM计数器模块的使用方法实验预期:学习LPM计数器LPM_COUNTER的调用方法、流程的测试,掌握MegaWizard Plug_In Manager管理器对同类宏模块的一般使用方法;实验内容:一、LPM_COUNTER计数器模块文本文件的调用1.在程序文件夹abceda下建立子文件夹LPM_MD;2.选择菜单栏Tools→MegaWizard Plug_In Manager命令,打开对话框如图所示:图表 1 定制新的宏功能块选中create a new custom megafunction variatin单选按钮,即定制一个新的模块(如果要修改一个已编辑好的LPM模块,则选中Edit an existing custom megafunction variation单选按钮);单击Next按钮,在弹出的窗口中选择Arithmetic展开LPM算术模块选项。

选择计数器LPM-COUNTER,再在右上选择Cyclone Ⅲ器件系列和VHDL语言方式。

最后输入此模块文件存放的路径和文件名:f:\abceda\LPM_MD\cnt4b:单击next按钮,弹出对话框。

选择4位计数器,选择“Creat an updown input…”使计数器有加减控制功能。

单击next按钮,打开对话框,选择Modulus…12,则表示模12计数器,从0记到11(若选择Plain binary则表示是普通的二进制计数器)。

然后选择时钟使能控制Clock Enable和进位输出Carry-out,如图:7.再单击next按钮,打开对话框,选择4位数据同步加载控制Load和异步清零控制Clear,如图:8.再按next按钮结束设置。

二、例化1)生成的LPM计数器模块VHDL源程序cnt4b如下:LIBRARY ieee;USE lpm;USE ;ENTITY cnt4b ISPORT(aclr : IN STD_LOGIC ;clk_en : IN STD_LOGIC ;clock : IN STD_LOGIC ;data : IN STD_LOGIC_VECTOR (3 DOWNTO 0);sload : IN STD_LOGIC ;updown : IN STD_LOGIC ;cout : OUT STD_LOGIC ;q : OUT STD_LOGIC_VECTOR (3 DOWNTO 0) );END cnt4b;ARCHITECTURE SYN OF cnt4b ISSIGNAL sub_wire0 : STD_LOGIC ;SIGNAL sub_wire1 : STD_LOGIC_VECTOR (3 DOWNTO 0);COMPONENT lpm_counterGENERIC (lpm_direction : STRING;lpm_modulus : NATURAL;lpm_port_updown : STRING;lpm_type : STRING;lpm_width : NATURAL);PORT (sload : IN STD_LOGIC ;clk_en : IN STD_LOGIC ;aclr : IN STD_LOGIC ;clock : IN STD_LOGIC ;cout : OUT STD_LOGIC ;q : OUT STD_LOGIC_VECTOR (3 DOWNTO 0);data : IN STD_LOGIC_VECTOR (3 DOWNTO 0);updown : IN STD_LOGIC);END COMPONENT;BEGINcout <= sub_wire0;q <= sub_wire1(3 DOWNTO 0);lpm_counter_component : lpm_counterGENERIC MAP (lpm_direction => "UNUSED",lpm_modulus => 12,lpm_port_updown => "PORT_USED",lpm_type => "LPM_COUNTER",lpm_width => 4)PORT MAP (sload => sload,clk_en => clk_en,aclr => aclr,clock => clock,data => data,updown => updown,cout => sub_wire0,q => sub_wire1);END SYN;它调用了更底层的文件lpm_counter,同时可以作为一个底层元件被上一层设计调用或例化。

LPM宏模块使用方法

RTL图:

波形仿真:

实验总结

通过这次实验,我学会了如何使用工具快速设计相关器件的VHDL代码。加强了如何去例化元件。在实验过程中,我遇到了无法编译成功的困难,原因是:我生成的计数器代码和给的代码是不一样的,主要是接口不一样,例化的时候出现了接口不搭配,改正后就成功了。

指导教师意见

签名: 年 月 日

cnt_en1: IN STD_LOGIC ;

data1: IN STD_LOGIC_VECTOR (3 DOWNTO 0);

sclr1: IN STD_LOGIC ;

updown1: IN STD_LOGIC ;

cout1: OUT STD_LOGIC ;

q1: OUT STD_LOGIC_VECTOR (3 DOWNTO 0)

data: IN STD_LOGIC_VECTOR (3 DOWNTO 0);

sclr: IN STD_LOGIC ;

updown: IN STD_LOGIC ;

cout: OUT STD_LOGIC ;

q: OUT STD_LOGIC_VECTOR (3 DOWNTO 0)

);

END COMPONENT;

利用计数宏模块构建一个12进制计数器。

实验数据

1、由于软件之间的偏差,cnt4bb,需要重新设计,设计如下:

LIBRARY ieee;

USE ieee.std_logic_1164.all;

entity cnt4bb IS

PORT(aload1: IN STD_LOGIC ;

clock1: IN STD_LOGIC ;

sload: IN STD_LOGIC ;

updown: IN STD_LOGIC ;

LPM的使用

七段码显示 a b c d e f g 1 1 1 1 1 1 0 0 1 1 0 0 0 0 1 1 0 1 1 0 1 1 1 1 1 0 0 1

. . .

提高电路设计效率的常用方法

• 对ROM储存内容进行初始化的文件格 式是: Hexademial(Intel-Formal)File(.hex)

提高电路设计效率的常用方法

(4)给电路加上相应的输入模块input和输 出模块output,并给出相应的名字,构建 完整的电路。

(5)如果未对ROM进行初始化,则电路编 译之后,在message窗口有如下信息: Critical Warning: Can‘t find Memory Initialization File or Hexadecimal (IntelFormat) File …/seg7/rom.mif -- setting all initial values to 0

或 Altera Memory Initialize File(.mif)

提高电路设计效率的常用方法

(2)以.bdf方式(图形化设计方式)打开 一个新的设计,并将该设计文件命名为 seg7.bdf,然后把新文件设定在当前 project下。

(3)从megafunctions中选择器件lpm_rom 宏单元,并放在设计文件中,同时设置其 各项接口信息与参数。

提高电路设计效率的常用方法

以七段数码管显示为例说明LPM的应用:

• (1)确定译码关系表显示译码关系表

字符 二进制表示 a3 a2 a1 a0 0 0 0 0 0 1 0 0 0 1 2 0 0 1 0 3 0 0 1 1

. . . . . .

提高电路设计效率的常用方法

使用LPM宏单元库

参数可设置LPM宏功能块

3

Altera提供的宏功能模块与LPM函数:

算术组件 组合组件 I/O组件 存储器编译器 存储组件

4

6.1 LPM模块的原理图方式调用

LPM_COUNTER LPM_ROM

6.1.1 基于LPM_COUNTER的数控分频器设计

5

数控分频器的功能就是当在输入端给定不同输入数据时,将对 输入的时钟信号有不同的分频比

DEPTH = 256 ;

ADDRESS_RADIX = HEX ;

DATA_RADIX = HEX ;

CONTENT BEGIN

00:00 ; 01:00 ; 02:00 ; 03:00 ; 04:00 ; 05:00 ; 06:00 ; 07:00 ; 08:00 ; 09:00;

10:00 ; 11:01 ; 12:02 ; 13:03 ; 14:04 ; 15:05 ; 16:06 ; 17:07 ; 18:08 ; 19:09;

地址/数据表

以CONTENT BEGIN开始,以END结束; 地址/数据表达方法: 47:28 冒号左边为ROM地址值, 冒号右边为此地址中放置的数据

文件编辑好,后以.mif为后缀保存文件

设定LPM—FILE的路径指向该文件名

LPM_ROM中作为乘法表的数据文件rom_data.mif

12

WIDTH = 8 ;

40:00 ; 41:04 ; 42:08 ; 43:12 ; 44:16 ; 45:20 ; 46:24 ; 47:28 ; 48:32 ; 49:36;

50:00 ; 51:05 ; 52:10 ; 53:15 ; 54:20 ; 55:25 ; 56:30 ; 57:35 ; 58:40 ; 59:45;

quartus宏功能模块介绍

-----------------------------------------------------RAM宏模块宏模块名称功能描述csdpram 参数化循环共享双端口RAMlpm_ram_dp 参数化双端口RAMlpm_ram_dq 参数化RAM,输入/输出端分离lpm_ram_io 参数化RAM,输入/输出端公用一个端口FIFO宏模块宏模块名称功能描述csfifo 参数化循环共享FIFOdcfifo 参数化双时钟FIFOscfifo 参数化单时钟FIFOlpm_fifo 参数化单时钟FIFOlpm_fifo_dc 参数化双时钟FIFOROM的设计lpm_romQuartus II开发软件中的宏模块--时序电路宏模块触发器宏模块名称功能描述lpm_ff 参数化D或T触发器lpm_dff 参数化D触发器和移位寄存器lpm_tff 参数化T触发器enadff 带使能端的D触发器expdff 用扩展电路实现的D触发器7470 带预置和清零端的与门JK触发器7471 带预置端的JK触发器7472 带预置和清零端的与门JK触发器7473 带清零端的双JK触发器7474 带异步预置和异步清零端的双D触发器7476 带异步预置和异步清零端的双JK触发器7478 带异步预置、公共清零和公共时钟端的双JK触发器74107 带清零端的双JK触发器74109 带预置和清零端的双JK触发器74112 带预置和清零端的双JK时钟下降沿触发器74113 带预置端的双JK时钟下降沿触发器74114 带异步预置、公共清零和公共时钟端的双JK时钟下降沿触发器74171 带清零端的4D触发器74172 带三态输出的多端口寄存器74173 4位D型寄存器74174 带公共清零端的16进制D触发器74174b 带公共清零端的16进制D触发器74175 带公共时钟和清零端的4D触发器74273 带异步清零端的8进制触发器74273b 带异步清零端的8进制触发器74276 带公共预置和清零端的4JK触发器寄存器74374 带三态输出和输出使能端的8进制D触发器74374b 带三态输出和输出使能端的8进制D触发器74376 带公共时钟和公共清零端4JK触发器74377 带使能端的8进制D触发器74377b 带使能端的8进制D触发器74378 带使能端的16进制D触发器74379 带使能端的4D触发器74396 8进制存储寄存器74548 带三态输出的8位两级流水线寄存器74670 带三态输出的4位寄存器74821 带三态输出的10位总线接口触发器74821b 带三态输出的10位D触发器74822 带三态反相输出的10位总线接口触发器74822b 带三态反相输出的10位D触发器74823 带三态输出的9位总线接口触发器74823b 带三态输出的9位D触发器74824 带三态反相输出的9位总线接口触发器74824b 带三态反相输出的9位D触发器74825 带三态反相输出的8位总线接口触发器74825b 带三态输出的8进制D触发器74826 带三态反相输出的9位总线接口触发器74826b 带三态反相输出的8进制D触发器锁存器宏模块名称功能描述lpm_latch参数化锁存器explatch用扩展电路实现的锁存器Inpltch 用扩展电路实现的输入锁存器nandltch用扩展电路实现的SR(非)与非门锁存器norltch 用扩展电路实现的SR或非门锁存器7475 4位双稳态锁存器7477 4位双稳态锁存器74116 带清零端的双4位锁存器74259 带清零端、可设定地址的锁存器74279 4路SR(非)锁存器74373 带三态输出的8进制透明D锁存器74373b 带三态输出的8进制透明D锁存器74375 4位双稳态锁存器74549 8位二级流水线锁存器74604 带三态输出的8进制2输入多路锁存器74841 带三态输出的10位总线接口D锁存器74841b 带三态输出的10位总线接口D锁存器74842 带三态输出的10位总线接口D锁存器74842b 带三态输出的10位总线接口D反相锁存器74843 带三态输出的9位总线接口D锁存器74844 带三态输出的9位总线接口D反相锁存器74845 带三态输出的8位总线接口D锁存器74846 带三态输出的8位总线接口D反相锁存器74990 8位透明读回锁存器计数器宏模块名称功能描述lpm_conter参数化计数器(仅限FLEX系列器件)gray4 格雷码计数器unicnt 通用4位加/减计数器,可异步设置、读取、清零和级联的左/右移位寄存器16cudslr 16位2进制加/减计数器,带异步设置的左/右移位寄存器16cudsrb 16位2进制加/减计数器,带异步清零和设置的左/右移位寄存器4count 4位2进制加/减计数器,同步/异步读取,异步清零8count 8位2进制加/减计数器,同步/异步读取,异步清零7468 双10进制计数器7469 双12进制计数器7490 10/2进制计数器7492 12进制计数器7493 4位2进制计数器74143 4位计数/锁存器,带7位输出驱动器74160 4位10进制计数器,同步读取,异步清零74161 4位2进制加法计数器,同步读取,异步清零74162 4位2进制加法计数器,同步读取,同步清零74163 4位2进制加法计数器,同步读取,同步清零74168 同步4位10进制加/减计数器74169 同步4位2进制加/减计数器74176 可预置10进制计数器74177 可预置2进制计数器74190 4位10进制加/减计数器,异步读取74191 4位2进制加/减计数器,异步读取74192 4位10进制加/减计数器,异步清零74193 4位2进制加/减计数器,异步清零74196 可预置10进制计数器74197 可预置2进制计数器74290 10进制计数器74292 可编程分频器/数字定时器74293 2进制计数器74294 可编程分频器/数字定时器74390 双10进制计数器74393 双4位加法计数器,异步清零74490 双4位10进制计数器74568 10进制加/减计数器,同步读取,同步和异步清零74569 2进制加/减计数器,同步读取,同步和异步清零74590 8位2进制计数器,带三态输出寄存器74592 8位2进制计数器,带输入寄存器74668 同步10进制加/减计数器74669 同步4位2进制加/减计数器74690 同步10进制计数器,带输出寄存器,多重三态输出,异步清零74691 同步2进制计数器,带输出寄存器,多重三态输出,异步清零74693 同步2进制计数器,带输出寄存器,多重三态输出,同步清零74696 同步10进制加/减计数器,带输出寄存器,多重三态输出,异步清零74697 同步2进制加/减计数器,带输出寄存器,多重三态输出,异步清零74698 同步10进制加/减计数器,带输出寄存器,多重三态输出,同步清零74699 同步2进制加/减计数器,带输出寄存器,多重三态输出,同步清零分频器宏模块名称功能描述Freqdiv 2,4,8,16分频器7456 双时钟5,10分频器7457 双时钟5,6,10分频器多路复用器宏模块名称功能描述lpm_mux 参数化多路复用器2lmux 2线-1线多路复用器16lmux 16线-1线多路复用器2X8mux 8位总线的2线-1线多路复用器8lmux 8线-1线多路复用器74151 8线-1线多路复用器74151b 8线-1线多路复用器74153 双4线-1线多路复用器74157 四2线-1线多路复用器74158 带反相输出的四2线-1线多路复用器74251 带三态输出的8线-1线数据选择器74253 带三态输出的双4线-1线数据选择器74257 带三态输出的四2线-1线多路复用器74258 带三态反相输出的四2线-1线多路复用器74298 带存储功能的四2输入多路复用器74352 带反相输出的双4线-1线数据选择器/多路复用器74353 带三态反相输出的双4线-1线数据选择器/多路复用器74354 带三态输出的8线-1线数据选择器/多路复用器74356 带三态输出的8线-1线数据选择器/多路复用器74398 带存储功能的四2输入多路复用器74399 带存储功能的四2输入多路复用器移位寄存器宏模块名称功能描述lpm_clshift参数化组合逻辑移位器lpm_shiftreg参数化移位寄存器barrelst 8位桶形移位器barrlstb 8位桶形移位器7491 串入串出移位寄存器7494 带异步预置和异步清零端的4位移位寄存器7495 4位并行移位寄存器7496 5位移位寄存器7499 带JK串入串出端的4位移位寄存器74164 串入并出移位寄存器74164b 串入并出移位寄存器74165 并行读入8位移位寄存器74165b 并行读入8位移位寄存器74166 带时钟禁止端的8位移位寄存器74178 4位移位寄存器74179 带清零端的4位移位寄存器74194 带并行读入端的4位双向移位寄存器74195 4位并行移位寄存器74198 8位双向移位寄存器74199 8位双向移位寄存器74295 带三态输出端的4位左右移位寄存器74299 8位通用移位/存储寄存器74350 带三态输出端的4位移位寄存器74395 带三态输出端的4位可级联移位寄存器74589 带输入锁存和三态输出端的8位移位寄存器74594 带输入锁存的8位移位寄存器74595 带输入锁存和三态输出端的8位移位寄存器74597 带输入寄存器的8位移位寄存器74671 带强制清零和三态输出端的4位通用移位寄存器/锁存器Quartus II开发软件中的宏模块--运算电路宏模块加法器和减法器宏模块名称功能描述lpm_add_sub 参数化加法器/减法器8fadd 8位全加器8faddb 8位全加器7480 门控全加器7482 2位2进制全加器7483 带快速进位的4位2进制全加器74183 双进位存储全加器74283 带快速进位的4位全加器74385 带清零端的4位加法器/减法器乘法器宏模块名称功能描述lpm_mult 参数化乘法器mult2 2位带符号数乘法器mult24 2X4位并行2进制乘法器mult4 4位并行2进制乘法器mult4b 4位并行2进制乘法器tmult4 4X4位并行2进制乘法器7497 同步6位速率乘法器74261 2位并行2进制乘法器74284 4X4位并行2进制乘法器(输出结果的最高4位)74285 4X4位并行2进制乘法器(输出结果的最低4位)除法器divide和lpm_divide绝对值运算lpm_abs数值比较器宏模块名称功能描述lpm_compare 参数化比较器8mcomp 8位数值比较器8mcompb 8位数值比较器7485 4位数值比较器74518 8位恒等比较器74518b 8位恒等比较器74684 8位数值/恒等比较器74686 8位数值/恒等比较器74688 8位恒等比较器编码器模块名称功能描述74147 10线-3线BCD编码器74148 8线-3线8进制编码器74384 带三态输出的8线-3线优先权编码器译码器宏模块名称功能描述lpm_decode 参数化译码器16dmux 4位2进制-16线译码器16ndmux 4位2进制-16线译码器7442 1线-10线BCD-10进制译码器7443 余3码-10进制译码器7444 余3格雷码-10进制译码器7445 BCD码-10进制译码器7446 BCD码-7段译码器7447 BCD码-7段译码器7448 BCD码-7段译码器7449 BCD码-7段译码器74137 带地址锁存的3线-8线译码器74138 3线-8线译码器74139 双2线-4线译码器74145 BCD码-10进制译码器74154 4线-16线译码器74155 双2线-4线译码器/多路输出选择器74156 双2线-4线译码器/多路输出选择器74246 BCD码-7段译码器74247 BCD码-7段译码器74248 BCD码-7段译码器74445 BCD码-10进制译码器奇偶校验器宏模块名称功能描述74180 9位奇偶产生器/校验器74180b 9位奇偶产生器/校验器74280 9位奇偶产生器/校验器74280b 9位奇偶产生器/校验器LPM库单元列表模块分类宏单元简要说明门单元模块lpm_and 参数化与门lpm_bustri 参数化三态缓冲器lpm_clshift 参数化组合逻辑移位器lpm_constant 参数化常数产生器lpm_decode 参数化译码器lpm_inv 参数化反向器lpm_mux 参数化多路选择器busmux 参数化总线选择器mux 多路选择器lpm_or 参数化或门lpm_xor 参数化异或门算术运算模块lpm_abs 参数化绝对值运算lpm_add_sub 参数化的加/减法器lpm_compare 参数化比较器lpm_counter 参数化计数器lpm_mult 参数化乘法器存储器模块lpm_ff 参数化D触发器lpm_latch 参数化锁存器lpm_ram_dq 输入输出分开的参数化RAMlpm_ram_io 输入输出复用的参数化RAMlpm_rom 参数化ROMlpm_shitreg 参数化移位寄存器csfifo class="style8">参数化先进先出队列csdpram 参数化双口RAM其它功能模块pll 参数化锁相环电路。

第7章LPM参数化宏模块的应用

【例8-28】 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY Tone IS PORT ( Index : IN STD_LOGIC_VECTOR(7 DOWNTO 0); CODE : OUT INTEGER RANGE 0 TO 15; HIGH : OUT STD_LOGIC; Tone : OUT INTEGER RANGE 0 TO 16#7FF# ); END; ARCHITECTURE one OF Tone IS BEGIN Search : PROCESS(Index) BEGIN CASE Index IS -- 译码电路,查表方式,控制音调的预置数 WHEN "00000001" => Tone <= 773; CODE <= 1; HIGH <= '0'; WHEN "00000010" => Tone <= 912; CODE <= 2; HIGH <= '0'; WHEN "00000100" => Tone <= 1036; CODE <= 3; HIGH <= '0'; WHEN "00001000" => Tone <= 1116; CODE <= 4; HIGH <= '0'; WHEN "00010000" => Tone <= 1197; CODE <= 5; HIGH <= '0'; WHEN "00100000" => Tone <= 1290; CODE <= 6; HIGH <= '0'; WHEN "01000000" => Tone <= 1372; CODE <= 7; HIGH <= '0'; WHEN "10000000" => Tone <= 1410; CODE <= 1; HIGH <= '1'; WHEN OTHERS => Tone <= 2047; CODE <= 0; HIGH <= '0'; END CASE; END PROCESS; END;

quartus中调用宏模块中文介绍

quartus -->tool -->MegaWizard Plug-In Manager 就可以进入了置于参数设置要看是什么模块了,你根据自己的需求选择就是了quarts 最后会自动生成一个你命名的这个模块文件verilog语言就是"你为这个模块起的名字.v"你可以在工程里面找到它打开看看你只需在你的工程里面例化它就可以了就像你例化自定义模块一样。

Gate FunctionLPM_and : 可编程的按位做与运算的与门LPM_bustri :可编程的三态门(可单向,也可双向)enabletr(高电平有效)使能tridata => resultenabledt(高电平有效)使能data => tridataLPM_clshift : 可编程的组合逻辑移位器。

方向和距离是可以编程的。

LPM_constant: 可编程常数生成器LPM_decode : 可编程译码器LPM_inv : 可编程反向器(位数可控)LPM_mux : 可编程多路选择器(sel选择哪路输出)busmus : 可编程2路选择器(LPM_mux的特殊情况)mux : 可编程多路选择器,只有一位输出结果(LPM_mux的宽度为1) LPM_or : 可编程的按位做或运算的或门LPM_xor : 可编程的按位做异或运算的异或门Arithmetic FuntionsLMP_abs : 求绝对值(如果data = 1000000,overflow=1)LPM_add_sub : 可编程加减法器(可以由管脚决定)LPM_compare : 可编程的比较器(可以设定各种输出)LPM_counter : 可编程计数器LPM_mult : 可编程乘法器LPM_divide : 可编程除法器divide : 可编程除法器(与LPM_divide没有什么区别)Parallel_add : 可编程多路并行加法器altmult_accum : 可编程乘加器altaccumulate : 可编程累加器altmemmult :Storage FunctionsLPM_ff : 可编程的触发器(D触发器或T触发器)LPM_latch : 可编程的锁存器(gate=0锁存)LPM_ram_dq : 可编程的同步或异步单端口RAM(两套地址线).LPM_ram_dp : 可编程的简单双端口和真正双端口RAM().LPM_ram_io : 可编程的RAM(地址线一套,数据线为双向的IO)LPM_rom : 可编程的ROMLPM_shiftreg : 可编程的移位寄存器Custom Parameterized Functions csfifo : 可编程的FIFOcsdpram : 可编程的双口RAM。

第6讲-LPM参数化宏模块应用07

7.3 在系统存储器数据读写编辑器应用

图7-15 从FPGA中的ROM读取波形数据

25

7.3 在系统存储器数据读写编辑器应用

图7-16 编辑波形数据

图7-16下载编辑数据后的SignalTap II采样波形

26

7.4 编辑SignalTapII的触发信号

图7-17 选择高级触发条件

27

7.4 编辑SignalTapII的触发信号

2.建立.hex格式文件---直接填表

图7-2 将波形数据填入mif文件表中

10

7.2.2 定制LPM_ROM初始化数据文件

2.建立.hex格式文件 ---汇编程序编译器

图7-3 ASM格式建hex文件

11

7.2 LPM模块应用实例

7.2.2 定制LPM_ROM初始化数据文件

2.建立.hex格式文件

END;

8

7.2 LPM模块应用实例

7.2.2 定制LPM_ROM初始化数据文件

1.建立.mif格式文件 ---程序语言生成,如 C

【例7-2】 #include <stdio.h> #include "math.h" main() {int i;float s; for(i=0;i<1024;i++)

31

7.5 其它存储器模块的定制与应用

7.5.2 FIFO定制

图7-22 FIFO编辑窗

32

7.5 其它存储器模块的定制与应用

7.5.2 FIFO定制

图7-23 FIFO的仿真波形

33

7.5 其它存储器模块的定制与应用

7.5.3 基于LPM_ROM的4位乘法器设计

address_aclr_a => "NONE",

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

∙摘要:《EDA技术与VHDL程序开发基础教程》第4章Quartus II操作指南,本章主要介绍Altera公司配套的EDA 开发套件Quartus II的使用方法。

该软件在大学教学中使用最为广泛。

通过介绍Quartus II工具的设计流程、嵌入式逻辑分析仪和宏单元模块的使用,力求使读者熟练掌握现代数字系统的设计流程和仿真验证方法。

本小节为大家介绍LPM_ROM宏模块的工作原理。

∙标签:EDA VHDL EDA技术与VHDL程序开发基础教程

在上述结构中,顶层文件在FPGA中实现包含ROM地址信号发生器和正弦数据ROM两部分。

其中,ROM 地址信号发生器由一个5位计数器实现,正弦数据ROM由LPM_ROM模块构成。

LPM_ROM的底层是FPGA 中的EAB或M4K等模块。

正弦信号数据的采样率是64,即CLK频率为正弦信号频率的64倍。

4.3.2 初始化数据文件

由图4-27可知,正弦信号的数据ROM是通过LPM_ROM宏模块生成的。

目前,Quartus II能接受的LPM模块的初始化数据文件的格式有两种,即Memory Initialization File(.mif)格式和Hexadecimal File(.hex)格式。

下面以64点正弦波形数据为例使用.mif文件进行说明。

当然,除了Quartus II之外,还可以用其他编辑器设计MIF文件,只要格式符合要求,均能够被正常使用。

设计者甚至可以编写C语言程序生成目标MIF文件或者利用MATLAB来生成。

由于这些方法超出了本书的范围,在此不做过多的讨论,有兴趣的读者可以参阅相关资料。

2. 选择ROM控制线和地址、数据线

在图4-31和图4-32所示的窗口中选择地址与数据的位宽分别为6和8,选择地址所存控制信号inclock,去除输出锁存功能。

4.3.3 定制LPM_ROM元件(2)

3. 选择数据文件

单击Next按钮进行图4-33所示的窗口,选择"Yes,use this file for the memory content data"单选按钮并在File name文本框中选择数据文件romd.mif,最后选中"Allow In-System Memory…"复选框,完成ROM文件data_rom.vhd的生成。

"Allow In-System Memory…"是Altera的新功能,支持对FPGA中的ROM进行"在系统"测试和读写,且不影响数字系统的正常工作。

15.ARCHITECTURE SYN OF data_rom IS

16. SIGNAL sub_wire0 : STD_LOGIC_VECTOR (7 DOWNTO 0);

17. COMPONENT altsyncram --例化

altsyncram元件,调用LPM模块altsyncram

18. GENERIC (

--参数传递

19. address_aclr_a : STRING;

20. init_file : STRING;

21. intended_device_family : STRING;

--类属参量数据类型定义

22. lpm_hint : STRING;

23. lpm_type : STRING;

24. numwords_a : NATURAL;

25. operation_mode : STRING;

26. outdata_aclr_a : STRING;

27. outdata_reg_a : STRING;

28. widthad_a : NATURAL;

29. width_a : NATURAL;

30. width_byteena_a : NATURAL

31. );

32. PORT (

33. clock0 : IN STD_LOGIC ;

34. address_a : IN STD_LOGIC_VECTOR (5 DOWNTO 0);

35. q_a : OUT STD_LOGIC_VECTOR (7 DOWNTO 0)

36. );

37. END COMPONENT;

38.BEGIN

39. q <= sub_wire0(7 DOWNTO 0);

40. altsyncram_component : altsyncram

--参数传递映射

41. GENERIC MAP (

42.address_aclr_a => "NONE",

43.init_file => "romd.mif",

44.intended_device_family => "Cyclone",

45.lpm_hint => "ENABLE_RUNTIME_MOD=YES,

INSTANCE_NAME=ROM1",

46.lpm_type => "altsyncram",

47.numwords_a => 64,

48.operation_mode => "ROM",

49.outdata_aclr_a => "NONE",

50.outdata_reg_a => "UNREGISTERED",

51.widthad_a => 6,

52.width_a => 8,

53.width_byteena_a => 1

4.3.4 顶层文件的仿真测试

顶层文件的仿真测试是检查整个系统是否能够正常工作最有效的方法。

在生成data_rom.vhd文件后,完成项目的操作流程与4.1节基本相同,包括编辑顶层设计文件,例化刚刚生成的LPM_ROM宏模块、创建工程、全程编译、观察RTL电路、仿真、了解时序分析报告、指定引脚及下载测试等。

例4-2给出了一个使用LPM_ROM宏模块的顶层设计范例。

【例4-2】顶层设计文件

1.LIBRARY IEEE;

--声明IEEE库

E IEEE.STD_LOGIC_1164.ALL;

--声明程序包

E IEEE.STD_LOGIC_UNSIGNED.ALL;

4.ENTITY SINGT IS

5. PORT(CLK:IN STD_LOGIC;

--实体声明

6. DOUT:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));

7.END;

8.ARCHITECTURE DACC OF SINGT IS

PONENT data_rom

--声明LPM_ROM

10. PORT(address:IN STD_LOGIC_VECTOR(5 DOWNTO 0);

11. inclock:IN STD_LOGIC;

12. q:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));

13.END COMPONENT;

14. SIGNAL Q1:STD_LOGIC_VECTOR(5 DOWNTO 0);

15.BEGIN

16. PROCESS(CLK)

17. BEGIN

18. IF CLK'EVENT AND CLK='1' THEN

19.Q1<=Q1+1;

20. END IF;

21.END PROCESS;

22. U1:data_rom PORT MAP(address=> Q1,q=>DOUT,

inclock=>CLK); --调用data_rom

23. END;

(点击查看大图)图4-35 用SignalTap II实时观察正弦信号发生器的结果

4.4 本章小结

本章主要讲述了采用EDA软件Quartus II进行VHDL设计的操作方法以及嵌入式逻辑分析仪(SignalTap II)和LPM_ROM宏模块的使用。

熟练掌握这些操作对于工程师快速、高效地设计正确的数字系统有很大帮助。

通过本章的学习,读者应该掌握以下几个知识点:

掌握Quartus II基本设计流程;

掌握嵌入式逻辑分析仪的设计目的、原理和使用方法;

掌握LPM_ROM宏模块的工作原理和使用方法。