2.加减运算电路的设计及分析

减法运算电路设计

减法运算电路设计1.减法原理减法运算的基本原理是通过将被减数与减数进行按位取反,然后加1,再进行加法运算,即可得到减法运算的结果。

这是因为减法运算可以转化为加法运算,减法可以通过加法实现。

2.减法电路设计减法电路的设计包含三个主要的步骤:将减法转化为加法、设计加法器、设计控制逻辑。

2.1将减法转化为加法将减法转化为加法是减法电路设计的第一步。

这里需要实现减数的取反和加1、取反可以通过异或门来实现,加1可以通过加法器来实现。

2.2设计加法器为了实现减法运算,我们需要设计一个能够同时处理加减法的加法器。

常用的加法器有半加器、全加器和多位加法器。

在减法电路中,我们可以使用多个全加器来实现两个二进制数的加法和减法运算。

2.3设计控制逻辑控制逻辑用于控制减法电路的操作,根据输入的操作信号,控制减数的取反和加法器的运行。

通常,控制逻辑由逻辑门和触发器组成,可以根据输入的操作码进行控制。

3.电路实现下面是一个4位减法器的例子,使用全加器进行加法和减法运算。

输入A:A3A2A1A0(被减数)输入B:B3B2B1B0(减数)输出D:D3D2D1D0(差值)首先,实现四个全加器用于处理每一位的减法运算。

全加器的输入包括两个加数和进位(来自前一位的借位),输出为和值和进位。

全加器的真值表如下:ABCi,SCo000,00001,10010,10011,01100,10101,01110,01111,11其中,A和B分别表示两个二进制数的对应位,Ci表示进位,S表示和值,Co表示进位。

根据全加器的真值表,我们可以通过组合逻辑来实现四个全加器。

每个全加器的输入包括A、B和前一位的进位(初始进位为0),输出为当前位的差值和进位。

最后,将四个全加器的输出作为减法器的输出,即得到了4位减法器的设计。

4.总结减法运算电路是数字电路中常见的逻辑电路,它可以通过将减法转化为加法,并实现加减法器和控制逻辑来实现减法运算。

在设计减法电路时,需要考虑减法转化为加法,选择适当的加法器,以及设计合适的控制逻辑。

可控加减法电路设计实验报告

可控加减法电路设计实验报告一、实验目的。

1.了解四位二进制数运算的基本原理,制定设计方案。

2.利用ISE软件进行可编程逻辑器件设计,完成逻辑仿真功能。

3.使用编译器将设计实现,下载到BASYS2实验板上进行调试和验证所设计的四位二进制数的运算。

二、实验器材。

1.Pentium—Ⅲ计算机一台;2.BASYS2 实验板一只;三、实验方案。

1.基本功能。

实现了两个四位二进制数的加减法运算,能够在输出端得出结果.2.清零功能。

利用一个微动开关,在逻辑程序中表示出当按下微动开关后两个操作数都变为零。

再调用以前的加法程序,即可实现输出结果清零。

3.用数码管显示。

编写程序,将数值转换为七段显示器显示。

将运算结果输送到数码管中。

值得注意的是四个数码管要显示不同的数字,就需要利用到人的视觉误差,做一些短暂的延时。

4.溢出显示。

本实验中,设计的是一个无符号数加减法器,因而其共有两种溢出情况一,减法时,减数大于被减数,针对这种情况可以利用比较大小进行溢出判断;二,加法时,被操作数之和大于15。

判断进位,如果进位为1则显示溢出,若反之,则不显示。

四、实验原理图。

五、实验模块说明及部分代码。

1.add1部分。

将输入的两个操作数相加并判断大小。

相加结果放在led中,进位放在carry中。

led[0]=num1[0]^num2[0];carry[0]=num1[0]&num2[0];led[1]=num1[1]^num2[1]^carry[0];carry[1]=(num1[1]&num2[1])|(carry[0]&(num1[1]^num2[1]));led[2]=num1[2]^num2[2]^carry[1];carry[2]=(num1[2]&num2[2])|(carry[1]&(num1[2]^num2[2]));led[3]=num1[3]^num2[3]^carry[2];if(add)begincarry[3]=(num1[3]&num2[3])|(carry[2]&(num1[3]^num2[3]));endif(sub)beginif(compare)carry[3]=1;elsecarry[3]=(num1[3]&num2[3])|(carry[2]&(num1[3]^num2[3]))&(~sub); 2.seg7ment。

数字电路课程设计之加减法运算电路设计(1)

设计资料1加减法运算电路设计1.设计内容及要求1.设计一个4位并行加减法运算电路,输入数为一位十进制数,且作减法运算时被减数要大于或等于减数。

2.led 灯组成的七段式数码管显示置入的待运算的两个数,按键控制运算模式,运算完毕,所得结果亦用数码管显示。

3.提出至少两种设计实现方案,并优选方案进行设计2.结构设计与方案选择2.1电路原理方框图电路原理方框图如下→ →图1-1二进制加减运算原理框图如图1-1所示,第一步置入两个四位二进制数(要求置入的数小于1010),如(1001)2和(0111)2,同时在两个七段译码显示器上显示出对应的十进制数9和7;第二步通过开关选择运算方式加或者减;第三步,若选择加运算方式,所置数送入加法运算电路进行运算,同理若选择减运算方式,则所置数送入减法运算电路运算;第四步,前面所得结果通过另外两个七段译码器显示。

即:若选择加法运算方式,则(1001)2+(0111)2=(10000)2 十进制9+7=16置数开关选择运算方式加法运算电路减法运算电路译码显示计算结果显示所置入的两个一位十进制数并在七段译码显示器上显示16.若选择减法运算方式,则(1001)2-(0111)2=(00010)2十进制9-7=2 并在七段译码显示器上显示02.2.2加减运算电路方案设计2.2.1加减运算方案一如图2-2-1所示:通过开关S2——S9接不同的高低电平来控制输入端所置的两个一位十进制数,译码显示器U13和U15分别显示所置入的两个数。

数A 直接置入四位超前进位加法器74LS283的A4——A1端,74LS283的B4——B1端接四个2输入异或门。

四个2输入异或门的一输入端同时接到开关S1上,另一输入端分别接开关S6——S9,通过开关S6——S9控制数B的输入。

当开关S1接低电平时,B与0异或的结果为B,通过加法器74LS283完成两个数A和B的相加。

当开关S1接高电平时,B与1异或的结果为B非,置入的数B在74LS283的输入端为B的反码,且74LS283的进位信号C0为1,其完成S=A+B (反码)+1,实际上其计算的结果为S=A-B完成减法运算。

加法运算和减法运算电路

=8V

12

例:由三运放放大器组成的温度测量电路。

E=+5V

R

R

R

Rt

+ A1 +

ui

_

+ A2 +

R R1 RW R R1

R2

+ A3 +

uo

R2

Rt :热敏电阻

集成化:仪表放大器

13

E=+5V

R

R

R

Rt

+ A1 +

ui _

+ A2 +

R R1 RW R R1

R2

+ A3 +

uo

R2

Rt f (TC)

( RP2 // R RP1 RP 2 //

R ui1

RP

RP1 // R 2 RP1 //

R

ui

2

)

(R1 Rf )Rf R1 R f

( RP1

//

RP 2

//

R)(

ui1 RP1

ui 2 ) RP 2

将RP= RN的条件代入可得:

uo

Rf

( ui1 RP1

ui 2 RP 2

)

在RP1=

RP2

ui1

可以变为:

uo ui2 ui1

反相输入结构的减法电路,由于出现虚地,放大电路没

有共模信号,故允许 ui1 、ui2 的共模电压范围较大,且输

入阻抗较低。在电路中,为减小温漂提高运算精度,同相端

须加接平衡电阻。

4

6.2.2 减法运算电路

1、差动减法器

由Ui1产生的输出电压为:

uo

Rf R1

加减运算电路

加减运算电路加减运算电路:一、介绍1. 加减运算电路是可以进行加减运算操作的电路系统。

它是数字电路系统中最重要的组成部分之一,主要用于完成数字计算机等数字电路系统的运算操作。

2. 加减运算电路包括整数加法、减法、移位运算、位计数等多种操作,简称“四运算”。

整数加法是指在数字电路中,把两个二进制数相加,得到其和;减法是指在数字电路中,把两个二进制数相减,得到其差;移位运算是指在数字电路中,把中间输出的数值改变位置,以满足特定要求;位计数是指在数字电路中,把二进制数中1的个数进行统计和记录。

二、结构1. 加减运算电路通常主要由两部分组成:数据输入部分和运算控制部分。

数据输入部分由数据缓冲器,数据移位器等组成,主要用于收集被加减数据,并把它们传输到运算控制部分。

运算控制部分由加减器,运算控制电路以及计数器等组成,主要负责运算控制,跟踪不同的运算状态。

2. 加减运算电路结构不同,元件的组成也有所不同。

比如,可以使用半加器来完成整数加法,使用XOR门完成减法,使用带移位器完成移位运算,使用计数器电路完成位计数。

三、性能1. 加减运算电路具有高计算精度、高效率和高稳定性等优点,是现代计算机数字处理的核心技术。

2. 加减运算电路的高计算精度和高效率使它能够实现复杂的运算,而在稳定性方面,该电路可以长期稳定工作,即使在高温条件下仍能保持精度不变。

3. 此外,加减运算电路还具有抗干扰性能良好、受控制快速,可实现快速动态操作等优点。

四、应用1. 由于加减运算电路有着高计算精度、高效率和高稳定性等特性,它被广泛应用于航空、航天、汽车、机器人、医学、工业自动化等多个领域,是计算机系统的主要组成部分。

2. 加减运算电路还用于智能家居、大型安全系统、智能医疗仪器等诸多应用场景,可以实现智能化控制、数据采集、安全保障等功能。

3. 此外,加减运算电路还会出现在微处理器、控制器、数据处理机等设备中,用于实现数据处理、计算机管理和指令决策等功能。

加法运算电路

加法运算电路是一种关键的数字电路,它被广泛应用于各种计算机和电子设备中,它可以对两个二进制数进行加法运算,并输出结果。

本文将详细介绍加法运算电路的工作原理以及它的基本设计和应用。

一、加法运算电路的工作原理加法运算电路是基于全加器的原理设计的,全加器是一种可以实现三个二进制数相加的电路,它包括两个输入和三个输出,分别是和值、进位以及输出值。

当两个二进制数相加时,进位信号是从高位到低位传递的,因此需要多个全加器级联使用,这样才能对两个多位二进制数进行加法运算。

二、加法运算电路的基本设计加法运算电路的基本设计需要满足以下要求:1、能够对两个二进制数进行加法运算;2、能够处理进位信号和溢出;3、具有高速和可靠的性能。

基于这些要求,加法运算电路可以采用不同的设计方法,其中最常见的是串行加法器和并行加法器。

串行加法器逐位相加,计算速度慢但结构简单,而并行加法器可以同时处理多位二进制数,因此计算速度快,但结构复杂。

三、加法运算电路的应用加法运算电路广泛应用于各种数字电路和计算机系统中,其中最常见的应用包括:1、算术逻辑单元:在计算机系统中,加法运算电路被设计为算术逻辑单元的一部分,负责处理整数和浮点数的加减法运算;2、信号处理:在音频和视频信号处理中,加法运算电路可用于对信号进行混合和平均;3、加密和解密:在信息安全和保密通信中,加法运算电路被广泛使用于各种加密和解密算法中。

四、总结加法运算电路是一种重要的数字电路,它可以对两个多位二进制数进行加法运算,并输出结果。

加法运算电路的设计需要考虑诸多因素,如计算速度、结构复杂度以及性能可靠性等。

在各种数字电路和计算机系统中,加法运算电路都有着广泛的应用。

8位可控加减法电路设计实验报告

8位可控加减法电路设计实验报告本文针对8位可控加减法电路设计实验,利用TM1638底板,结合TTL集成电路实现了一个可以实现8位加减法计算的电路系统,并分析设计主要原理及关键技术点,如TTL集成电路的基本原理、TM1638底板的工作原理、LED显示灯的控制原理等。

最后,结合实验结果得出结论,使实验通过率达100%,并对其作出展望,认为者该电路设计具有较强的灵活性及实用性,可以应用在其他计算机系统中,用于计算出大量的结果。

【Keywords】:TM1638底板减法电路 TTL成电路 LED【1.言】近年来,在电子工程领域,加减法电路应用越来越普遍。

它可以实现简单的运算操作,不仅可以提高计算机系统的效率,也可以减少复杂的运算步骤,从而更有效地实现加减法的计算,极大提高了计算能力。

因此,加减法电路的设计变得越来越重要。

本文旨在为8位可控加减法电路设计实验提供实验研究报告,使用TM1638底板和TTL集成电路实现8位加减法计算。

在本实验中,采用测试方法和实验技术进行实验,并分析了设计的主要原理及关键技术点。

【2.文】(1)TM1638底板.TM1638底板用来连接TTL集成电路和LED显示灯,以实现加减法电路设计。

该底板的工作原理是:将微处理器的控制信号由串行输入口输入,然后由控制电路将控制信号转变为8路控制,并将其分配到各个LED显示灯,实现控制功能。

(2)TTL集成电路.TTL集成电路是一种由TTL(Transistor-Transistor Logic)集成电路组成的封装式模块,是用于实现加减法运算的关键环节。

集成电路的基本原理是:利用集成电路中的电路元件实现复杂的加减法运算。

(3)LED显示灯.LED示灯用于显示加减法运算的结果,实现电路设计核心功能。

LED显示灯的控制原理是:利用TTL集成电路产生的控制信号,根据不同的信号类型控制LED显示灯亮灭,从而实现加减法运算的计算结果的显示。

(4)实验结果.本实验中,采用测试方法和实验技术,实现了一个8位加减法电路设计。

减法运算电路

积件 4-1-3-2:加减运算放大的仿真研究

2) 同相加法运算电路

图4-11 同相加法运算电路

积件 4-1-3-2:加减运算放大的仿真研究

(2)减法运算电路

图 412 减 法 运 算 电 路

积件 4-1-3-2:加减运算放大的仿真研究

二、其它方面的应用

1.电压比较器 (1)基本电路

图4-13 电压比较器

积件 4-1-3-2:加减运算放大的仿真研究

作业: 1、画出集成运放电路组成的加法器、 减法器电路图。并证明输入电压与输出 电压的关系式。 2、画出输出电压Uo与输入电压Ui符合 下列关系的运放电路图;(1) Uo/Ui=-1;(2)Uo/Ui=15;(3) Uo/(Ui1+Ui2+Ui3)=-20。

加减运算放大的仿真研究一集成运放的线性应用二运算电路1加法运算电路反相加法运算电路图410反相加法运算电路电路输出电压

积件 4-1-3-2:加减运算放大的仿真研究

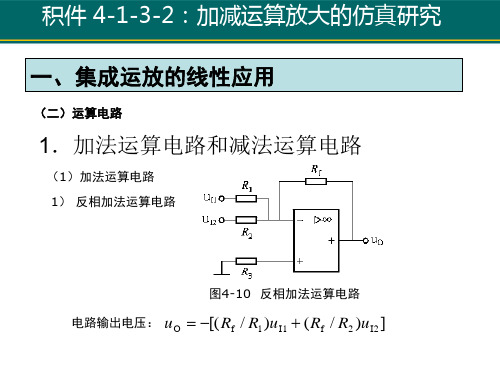

一、集成运放的线性应用

(二)运算电路

1.加法运算电路和减法运算电路

(1)加法运算电路 1) 反相加法运算电路

图4-10 反相加法运算电路

电路输出电压: uO [( Rf / R1 )uI1 (Rf / R2 )uI2 ]

积件 4-1-3-2:加减运算放大的仿真研究

可见,输出电压与输入电压反相,且uo是两输入信号加权后的负值相加,故称反相

加法器。

若取, R1 R2 则

uO (Rf / R1 )(uI1 uI2 )

若取,Rf R1 R2 则, uO (uI1 uI2 )

电路成为反相加法器。

积件 4-1-3-2:加减运算放大的仿真研究

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验2《电子技术》课程设计任务书

1. 实验原理

通常在分析运算电路时均设集成运方位理想运放,因而其输入端的净输入电压和净输入电流均为0,即具有“虚短路”和“虚断路”两个特点,这是分析运算电路输出电压和输入电压关系的基本出发点。

从对比例运算电路的分析可知,输出电压与同相输入信号电压极性相同,与反相输入端电压极性相反,因而如果多个信号同时作用于两个输入端,那么必然可以实现加减运算电路。

第一级电路实现加减运算,第二级电路通过运用反响比例运算电路来放大第一级的输出信号。

图(a )

根据虚断iN=iP=0 (1)

虚短UN=UP (2)

iN=(U1-UN )/R1+(U2-UN )/R2-(Uo1/Rf1-UN ) (3) iP=(U3-UP )/R3 (4) 根据式(1)(2)(3)(4)可知,当满足R1//R2//Rf=R3时

Uo1=Rf1(U3/R3-U2/R2-U1/R1)

OPAMP_3T_VIRTUAL

Rf1100kΩ

图(b )这是一个电压串联负反馈电路 根据电路分析可得U02=-Uo1*Rf2/R5 将两级电路连到一起,可得

U1

OPAMP_3T_VIRTUAL U2

OPAMP_3T_VIRTUAL

R150kΩR250kΩR340kΩ

Rf1100kΩ

R540kΩ

R6

20kΩRf240kΩR440kΩ

代入各具体数值可得Uo2=(2Uo1+2Uo2-2.5Uo3)

2. 用软件的仿真结果

U1

OPAMP_3T_VIRTUAL

U2

OPAMP_3T_VIRTUAL

R150kΩR2

50kΩR320kΩ

Rf1100kΩ

R540kΩ

R6

20kΩRf240kΩXSC1

A

B

C

D

G T

XFG1

XFG2

XFG3

实验结论

当U1=-0.2203,U2=-0.2203,U3=-1.175时,Uo2=2.0563,与仿真实验结果一样。