开关电源中的EMI分析以及抑制技术

开关电源的共模干扰抑制技术开关电源共模电磁干扰(EMI)对策详解

开关电源的共模干扰抑制技术开关电源共模电磁干扰(EMI)对策详解開關電源的共模干擾抑制技術|開關電源共模電磁干擾(EMI)對策詳解0 引言由於MOSFET及IGBT和軟開關技術在電力電子電路中的廣泛應用,使得功率變換器的開關頻率越來越高,結構更加緊湊,但亦帶來許多問題,如寄生元件產生的影響加劇,電磁輻射加劇等,所以EMI 問題是目前電力電子界關注的主要問題之一。

傳導是電力電子裝置中干擾傳播的重要途徑。

差模干擾和共模干擾是主要的傳導干擾形態。

多數情況下,功率變換器的傳導干擾以共模干擾為主。

本文介紹了一種基於補償原理的無源共模干擾抑制技術,並成功地應用於多種功率變換器拓撲中。

理論和實驗結果都證明了,它能有效地減小電路中的高頻傳導共模干擾。

這一方案的優越性在於,它無需額外的控制電路和輔助電源,不依賴於電源變換器其他部分的運行情況,結構簡單、緊湊。

1 補償原理共模雜訊與差模雜訊產生的內部機制有所不同:差模雜訊主要由開關變換器的脈動電流引起;共模雜訊則主要由較高的d/d與雜散參數間相互作用而產生的高頻振盪引起。

如圖1所示。

共模電流包含連線到接地面的位移電流,同時,由於開關器件端子上的d/d是最大的,所以開關器件與散熱片之間的雜散電容也將產生共模電流。

圖2給出了這種新型共模雜訊抑制電路所依據的本質概念。

開關器件的d/d通過外殼和散熱片之間的寄生電容對地形成雜訊電流。

抑制電路通過檢測器件的d/d,並把它反相,然後加到一個補償電容上面,從而形成補償電流對雜訊電流的抵消。

即補償電流與雜訊電流等幅但相位相差180°,並且也流入接地層。

根據基爾霍夫電流定律,這兩股電流在接地點匯流為零,於是50Ω的阻抗平衡網路(LISN)電阻(接測量接收機的BNC埠)上的共模雜訊電壓被大大減弱了。

圖1 CM及DM雜訊電流的耦合路徑示意圖圖2 提出的共模雜訊消除方法2 基於補償原理的共模干擾抑制技術在開關電源中的應用本文以單端反激電路為例,介紹基於補償原理的共模干擾抑制技術在功率變換器中的應用。

开关电源emi电路原理

开关电源emi电路原理

开关电源EMI电路是指用来抑制电磁干扰(EMI)的电路。

开关电源是一种使用开关元件(如晶体管或MOSFET)工作

的电源,通过周期性地开关电流来提供电能。

开关电源会产生一定的电磁干扰,主要原因有以下几点:

1. 开关元件的快速开关会引起电压和电流的急剧变化,导致高频谐波成分的产生;

2. 开关电源中的变压器和电感器会产生磁场,进一步引起电磁辐射;

3. 开关电源中的电容器会产生串扰电容耦合,导致干扰信号的传导。

为了抑制开关电源的电磁干扰,可以采取以下措施:

1. 在开关电源输入端添加滤波器,用来抑制高频噪声,常见的滤波器包括电容滤波器和电感滤波器;

2. 设计合适的开关元件驱动电路,减小开关元件的开关速度,从而减小高频谐波的产生;

3. 采用引入屏蔽外壳或屏蔽包围电路等的屏蔽手段,减小电磁辐射;

4. 采用良好的地线布局和接地措施,降低地线电阻和噪声干扰;

5. 使用高频绕线技术和特殊布板设计,减少电感和电容器之间的串扰。

通过以上措施,可以有效地抑制开关电源产生的电磁干扰,提高电源的抗干扰能力,确保设备的正常运行。

开关电源中开关管及二极管 EMI抑制方法分析

开关电源中开关管及二极管EMI抑制方法分析1 引言 电磁干扰( EMI) 就是电磁兼容不足,是破坏性电磁能从一个电子设备通过传导或辐射到另一个电子设备的过程。

近年来,开关电源以其频率高、效率高、体积小、输出稳定等优点而迅速发展起来。

开关电源已逐步取代了线性稳压电源,广泛应用于计算机、通信、自控系统、家用电器等领域。

但是由于开关电源工作在高频状态及其高di/dt和高dv/dt,使开关电源存在非常突出的缺点——容易产生比较强的电磁干扰(EMI)信号。

EMI信号不但具有很宽的频率范围,还具有一定的幅度,经传导和辐射会污染电磁环境,对通信设备和电子产品造成干扰。

所以,如何降低甚至消除开关电源中的EMI问题已经成为开关电源设计师们非常关注的问题。

本文着重介绍开关电源中开关管及二极管EMI的四种抑制方法。

2 开关管及二极管EMI产生机理 开关管工作在硬开关条件下开关电源自身产生电磁干扰的根本原因,就是在其工作过程中的开关管的高速开关及整流二极管的反向恢复产生高di/dt和高dv/dt,它们产生的浪涌电流和尖峰电压形成了干扰源。

开关管工作在硬开关时还会产生高di/dt和高dv/dt,从而产生大的电磁干扰。

图1绘出了接感性负载时,开关管工作在硬开关条件下的开关管的开关轨迹,图中虚线为双极性晶体管的安全工作区,如果不改善开关管的开关条件,其开关轨迹很可能会超出安全工作区,导致开关管的损坏。

由于开关管的高速开关,使得开关电源中的高频变压器或储能电感等感性负载在开关管导通的瞬间,迫使变压器的初级出现很大的浪涌电流,将造成尖峰电压。

开关管在截止期间,高频变压器绕组的漏感引起的电流突变,从而产生反电势E=-Ldi/dt,其值与电。

开关电源的共模干扰抑制技术,开关电源共模电磁干扰(EMI)对策详解

开关电源的共模干扰抑制技术|开关电源共模电磁干扰(EMI)对策详解由于MOSFET及IGBT和软开关技术在电力电子电路中的广泛应用,使得功率变换器的开关频率越来越高,结构更加紧凑,但亦带来许多问题,如寄生元件产生的影响加剧,电磁辐射加剧等,所以EMI问题是目前电力电子界关注的主要问题之一。

传导是电力电子装置中干扰传播的重要途径。

差模干扰和共模干扰是主要的传导干扰形态。

多数情况下,功率变换器的传导干扰以共模干扰为主。

本文介绍了一种基于补偿原理的无源共模干扰抑制技术,并成功地应用于多种功率变换器拓扑中。

理论和实验结果都证明了,它能有效地减小电路中的高频传导共模干扰。

这一方案的优越性在于,它无需额外的控制电路和辅助电源,不依赖于电源变换器其他部分的运行情况,结构简单、紧凑。

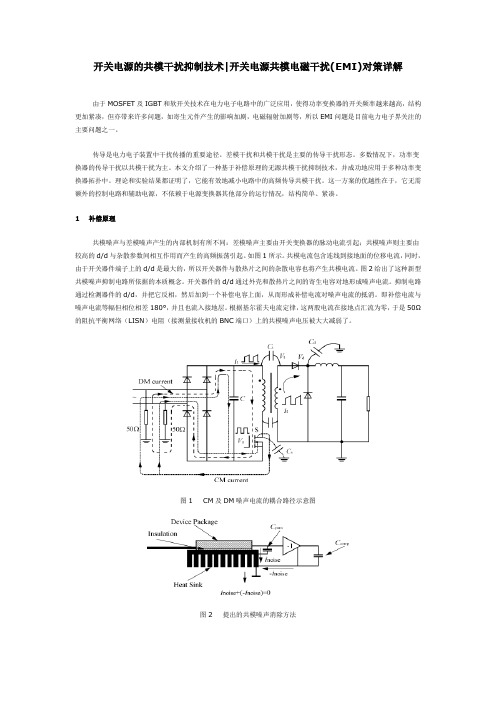

1 补偿原理共模噪声与差模噪声产生的内部机制有所不同:差模噪声主要由开关变换器的脉动电流引起;共模噪声则主要由较高的d/d与杂散参数间相互作用而产生的高频振荡引起。

如图1所示。

共模电流包含连线到接地面的位移电流,同时,由于开关器件端子上的d/d是最大的,所以开关器件与散热片之间的杂散电容也将产生共模电流。

图2给出了这种新型共模噪声抑制电路所依据的本质概念。

开关器件的d/d通过外壳和散热片之间的寄生电容对地形成噪声电流。

抑制电路通过检测器件的d/d,并把它反相,然后加到一个补偿电容上面,从而形成补偿电流对噪声电流的抵消。

即补偿电流与噪声电流等幅但相位相差180°,并且也流入接地层。

根据基尔霍夫电流定律,这两股电流在接地点汇流为零,于是50Ω的阻抗平衡网络(LISN)电阻(接测量接收机的BNC端口)上的共模噪声电压被大大减弱了。

图1 CM及DM噪声电流的耦合路径示意图图2 提出的共模噪声消除方法2 基于补偿原理的共模干扰抑制技术在开关电源中的应用本文以单端反激电路为例,介绍基于补偿原理的共模干扰抑制技术在功率变换器中的应用。

图3给出了典型单端反激变换器的拓扑结构,并加入了新的共模噪声抑制电路。

开关电源EMI整改经验总结

开关电源EMI整改中,关于不同频段干扰原因及抑制办法:一、1MHZ以内----以差模干扰为主(整改建议)1. 增大X电容量;2. 添加差模电感;3. 小功率电源可采用PI型滤波器处理(建议靠近变压器的电解电容可选用较大些)。

二、1MHZ---5MHZ---差模共模混合采用输入端并联一系列X电容来滤除差摸干扰并分析出是哪种干扰超标并以解决,(整改建议)1. 对于差模干扰超标可调整X电容量,添加差模电感器,调差模电感量;2. 对于共模干扰超标可添加共模电感,选用合理的电感量来抑制;3. 也可改变整流二极管特性来处理一对快速二极管如FR107一对普通整流二极管1N4007。

三、5M---以上以共摸干扰为主,采用抑制共摸的方法。

(整改建议)对于外壳接地的,在地线上用一个磁环串绕2-3圈会对10MHZ以上干扰有较大的衰减作用;可选择紧贴变压器的铁芯粘铜箔,铜箔闭环。

处理后端输出整流管的吸收电路和初级大电路并联电容的大小。

四、对于20--30MHZ,(整改建议)1. 对于一类产品可以采用调整对地Y2电容量或改变Y2电容位置;2. 调整一二次侧间的Y1电容位置及参数值;3. 在变压器外面包铜箔;变压器最里层加屏蔽层;调整变压器的各绕组的排布。

4. 改变PCB LAYOUT;5. 输出线前面接一个双线并绕的小共模电感;6. 在输出整流管两端并联RC滤波器且调整合理的参数;7. 在变压器与MOSFET之间加BEAD CORE;8. 在变压器的输入电压脚加一个小电容。

9. 可以用增大MOS驱动电阻。

五、30---50MHZ 普遍是MOS管高速开通关断引起(整改建议)1. 可以用增大MOS驱动电阻;2. RCD缓冲电路采用1N4007慢管;3. VCC供电电压用1N4007慢管来解决;4. 或者输出线前端串接一个双线并绕的小共模电感;5. 在MOSFET的D-S脚并联一个小吸收电路;6. 在变压器与MOSFET之间加BEAD CORE;7. 在变压器的输入电压脚加一个小电容;8. PCB心LAYOUT时大电解电容,变压器,MOS构成的电路环尽可能的小;9. 变压器,输出二极管,输出平波电解电容构成的电路环尽可能的小。

解读电源设计中的EMI问题与解决方案

解读电源设计中的EMI问题与解决方案电源设计中的EMI问题与解决方案电磁干扰(Electromagnetic Interference,简称EMI)是电源设计过程中需要重点考虑的问题之一。

EMI问题可能对电子设备的性能产生负面影响,干扰其正常工作并导致其他设备的性能下降。

本文将介绍电源设计中的EMI问题以及一些常见的解决方案。

一、电源设计中的EMI问题1. 什么是EMI问题?EMI指的是由电子设备产生的电磁场干扰。

当电子设备中的电流和信号在设备内部或外部传输时,会产生电磁辐射和电磁敏感性。

如果这些辐射或敏感性超过了某个特定的范围,就会导致EMI问题。

2. EMI问题可能导致的影响EMI问题可能导致以下影响:- 对设备本身造成干扰:电源系统中的高频噪声可能干扰设备的正常工作,降低设备性能。

- 对其他设备造成干扰:电磁辐射可能传播到其他设备上,导致它们的性能下降,甚至损坏。

- 不符合法规:有些国家和地区对EMI有严格的法规要求,如果不符合这些要求,产品可能无法上市销售。

二、解决EMI问题的常见方案1. 电源线滤波器电源线滤波器是最常见的解决EMI问题的措施之一。

它通过滤波器电路将高频噪声滤除,防止其传播到其他设备上。

电源线滤波器通常由电感器和电容器组成,通过选择合适的元件参数来实现滤波效果。

2. 地线设计正确的地线设计对于减少EMI问题非常重要。

地线应该尽可能短而宽,以减小回路面积,降低电磁辐射。

可以采用单点接地或多点接地的方式,根据具体情况选择最合适的设计方案。

3. 布局设计良好的布局设计可以减少EMI问题。

重要的电路应该远离敏感的传感器、接收器等部件,以减少电磁辐射对它们的影响。

同时,电路板的铺铜区域应尽可能广泛,以提供良好的地面平面。

4. 屏蔽设计屏蔽设计可以有效地减少EMI问题。

对于电源模块,可以使用金属屏蔽罩来封闭电路,将电磁辐射限制在较小的范围内。

此外,对于敏感部分,如高频元件和传感器,还可以采用局部屏蔽来降低电磁辐射。

开关电源EMI杂讯分析及抑制

遮罩

濾波

接地

遮罩

遮罩可以用來控制電場或磁場從空間的一個區域到另一個區域的傳播, 這是克服電場耦合干擾、磁場耦合干擾以及電磁輻射干擾的最有效手段。

遮罩的目的是利用導電材料或高 磁導率材料來減少磁場、電場或電 磁場的強度。

採用兩層遮罩技術,外層遮罩材料的磁 導率不是很高,但是其達到磁飽和的磁場 強度卻很高,內層遮罩材料採用高磁導率, 以充分吸收雜訊。 遮罩示意圖

電源正負 輸入線

開關電源的寄生電容Cp分佈

共模雜訊電流

共模雜訊電流 雜訊電流

開關電源的寄生電容Cp分佈

初級差模雜訊電流

在功率開關管Q1開 開關電源 關時,高頻脈衝的上 輸入直流變換 升和下降所引起的基 回路 波及諧波會沿著輸入 濾波電容Ci傳向輸入 供電端,這種沿著輸 入電源線正負端傳播 的雜訊電流稱之為初 級差模雜訊電流IDIFF

對於低頻地電流,小 電容阻抗很大,該方式 相當於並行單點接地;

對於高頻電流,該方 式相當於多點接板地。 混合接地方式

EMI濾波器

加裝EMI電源濾波器是抑制EMI雜訊最好的方法之一。 在電源輸入端加裝 EMI電源濾波器可以獲 得雙重效果: ① 抑制開關電源產生 的EMI干擾傳向電源端; ② 抑制來自電源端的 EMI雜訊對開關電源造 成的干擾。

開關電源EMI雜訊分析 及抑制

76081 張輝 劉興兵 李政

電源雜訊基本概念 雜訊分析 抑制措施

電源雜訊基本概念

電源雜訊

電源雜訊是電磁 干擾的一種,其傳 導雜訊的頻譜大致 為10kHz~30MHz, 最高可150MHz。

電源雜訊,特別是瞬態雜訊干擾,其上 升速度快、持續時間短、電壓振幅度高、 隨機性強,對微機和數位電路易產生嚴重 干擾。

几种有效开关电源EMI的抑制方案解析

几种有效开关电源EMI的抑制方案解析关于开关电源EMI(Electro-Magnetic Interference)的研究,有些从EMI产生的机理出发,有些从EMI 产生的影响出发,都提出了许多实用有价值的方案。

这里分析与比较了几种有效的方案,并为开关电源EMI 的抑制措施提出新的参考建议。

开关电源电磁干扰的产生机理开关电源产生的干扰,按噪声干扰源种类来分,可分为尖峰干扰和谐波干扰两种;若按耦合通路来分,可分为传导干扰和辐射干扰两种。

现在按噪声干扰源来分别说明:1、二极管的反向恢复时间引起的干扰高频整流回路中的整流二极管正向导通时有较大的正向电流流过,在其受反偏电压而转向截止时,由于PN结中有较多的载流子积累,因而在载流子消失之前的一段时间里,电流会反向流动,致使载流子消失的反向恢复电流急剧减少而发生很大的电流变化(di/dt)。

2、开关管工作时产生的谐波干扰功率开关管在导通时流过较大的脉冲电流。

例如正激型、推挽型和桥式变换器的输入电流波形在阻性负载时近似为矩形波,其中含有丰富的高次谐波分量。

当采用零电流、零电压开关时,这种谐波干扰将会很小。

另外,功率开关管在截止期间,高频变压器绕组漏感引起的电流突变,也会产生尖峰干扰。

3、交流输入回路产生的干扰无工频变压器的开关电源输入端整流管在反向恢复期间会引起高频衰减振荡产生干扰。

开关电源产生的尖峰干扰和谐波干扰能量,通过开关电源的输入输出线传播出去而形成的干扰称之为传导干扰;而谐波和寄生振荡的能量,通过输入输出线传播时,都会在空间产生电场和磁场。

这种通过电磁辐射产生的干扰称为辐射干扰。

4、其他原因元器件的寄生参数,开关电源的原理图设计不够完美,印刷线路板(PCB)走线通常采用手工布置,具有很大的随意性,PCB的近场干扰大,并且印刷板上器件的安装、放置,以及方位的不合理都会造成EMI干扰。

开关电源EMI的特点作为工作于开关状态的能量转换装置,开关电源的电压、电流变化率很高,产生的干扰强度较大;干扰源主要集中在功率开关期间以及与之相连的散热器和高平变压器,相对于数字电路干扰源的位置较为清楚;开关频率不高(从几十千赫和数兆赫兹),主要的干扰形式是传导干扰和近场干扰;而印刷线路板(PCB)走线通常采用手工布线,具有更大的随意性,这增加了PCB分布参数的提取和近场干扰估计的难度。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

34

MPS Confidential------Internal Use Only

变压器的共模噪声以及抑制

2. 优化变压器的共模噪声

c. 平衡和干扰对消法-3

35 35

MPS Confidential------Internal Use Only

PCB布局对噪声的影响

环路小 分开不同的环路

输入环路尽可能的小 高频环路尽可能小

C PS2 V D2

C PS2 1 Z LISN 2 V D2

17 17

MPS Confidential------Internal Use Only

差模耦合路径

------反激差模耦合路径

LISN D1 D2

IS

AC

CB

S D4 D3

Equivalent Noise Model 2Z LISN

C Equ.

8

HV

VCC

CS

GND

HFC0500

3 4 6 5

VCC

DRV

The Future of Analog IC Technology®

抑制干扰源

HFC0500抖频控制电路

2.72uA

14pF

The Future of Analog IC Technology®

抑制差模噪声

LISN D1 D2

S

AC

15 15

MPS Confidential------Internal Use Only

共模耦合路径

------ 反激耦合路径2

C SP V D1

C SP 1 Z LISN 2 V D1

16 16

MPS Confidential------Internal Use Only

共模耦合路径

------ 反激耦合路径3

电磁兼容的三要素

干扰源

耦合路径

敏感设备 接受机

开关电源

耦合路径

LISN

The Future of Analog IC Technology®

干扰源

------MOS

Voltage, Vsw

关断

t

Current, Isw

t

开通

11

The Future of Analog IC Technology®

A B

C SP

C

D

isp

Cps

ips

Ips

X-3

A x

C PS 1 Z LISN 2

VP

5-6 4-X

x B

30 The Future of Analog IC Technology®

变压器的共模噪声以及抑制

2. 优化变压器的共模噪声

c. 平衡和干扰对消法-1

A B

C SP

C D

isp

加屏蔽后: Cps Csp

<=80W

No ±3.5% No YES YES YES (Latch) Hysteres is YES

8W

No ±4% Yes YES YES YES Hysteresi s YES

<=80W

Yes ±6.7% Yes YES YES YES Timer Based YES

*

TIMER FB

1 2

CB

S D4 D3

增大电容或者 增加LC滤波器

2Z LISN

C Equ.

IS

2Z LISN

C Equ.

IS

The Future of Analog IC Technology®

抑制共模噪声

1. 散热器接原边地- 切断散热器的耦合路径

VP

27

MPS Confidential------Internal Use Only

Cps

Csp

C SP

isp

A B

C D

ips

增加Ca, ips=isp,icm=0.

MPS Confidential------Internal Use Only

33 33

变压器的共模噪声以及抑制

2. 优化变压器的共模噪声

c. 平衡和干扰对消法-2

Without Cadd With Cadd

34

Monolithic Power Systems

®

开关电源中的EMI分析以及抑制技术

The Future of Analog IC Technology

®

内容

• 电磁兼容的简介 • 开关电源中的电磁干扰分析 • 电磁干扰的抑制技术

The Future of Analog IC Technology®

c. 平衡和干扰对消法-1

dBμV 100 90

Two traditional Shielding

dBμV 100 90

Optimized Shielding length

80

70 60 50 40 30 20 10 0 0.15 1 10 30 MHz

80

70 60 50 40 30 20 10 0 0.15 1 10 30 MHz

变压器的共模噪声以及抑制

2. 优化变压器的共模噪声

a. 改变变压器的端子来减小Cps

A B

C

D

C-D

C-D

X-A

B

A-B A-B

A

C-D

A x x B

A 差 好

B

B-X

最差

The Future of Analog IC Technology®

变压器的共模噪声以及抑制

2. 优化变压器的共模噪声

b. 采用屏蔽较小Cps

LISN-线路阻抗稳定性网络

电网 差模噪声 共模噪声

滤除电力线中的干扰 阻止开关电源中的干扰进入到电力线 在150k-30MHz频率范围内能够提供稳定的50ohm

The Future of Analog IC Technology®

共模耦合路径

------ 反激耦合路径1

CPS VP

C PS 1 Z LISN 2 VP

干扰源

------Power Diode

t

Voltage, Vsw

Current, Isw

t

Turn-off Turn-on 12

The Future of Analog IC Technology®

干扰源

------变压器,电感中的du/dt变化

The Future of Analog IC Technology®

IS

18 18

MPS Confidential------Internal Use Only

19 19

MPS Confidential------Internal Use Only

如何抑制EMI

开关电源

耦合路径

LISN 抑制干扰来自 切断耦合路径The Future of Analog IC Technology®

A(f)

Tr/Tf Increase

1 Duty π× fs

1 π× tr

f

1 Duty π× fs

1 π× tr

f

减小开关频率 减小du/dt

The Future of Analog IC Technology®

抑制干扰源

增大驱动电阻 增加snubber电路

平衡 EMI

效率

The Future of Analog IC Technology®

抑制干扰源

A(t) -----FFT

1 Duty fs

A(f)

----f傅里叶分析

tr=tf

- 20dB/Dec - 40dB/Dec

FFT

tr

1 / fs

tf

t

1 Duty π× fs

1 π ×t r

f

Duty Increase

A(f)

占空比,开关频率,以及tr、tf的影响 fs Increase

电磁干扰的标准

电磁干扰测试标准

• • • CISPR14 /EN55014 CISPR15 /EN55015 CISPR22 /EN55022 家电,电动工具 照明产品 开关电源

EN55022

The Future of Analog IC Technology®

The Future of Analog IC Technology®

电磁干扰的危害

干扰导致设备系统性能下降、无法工作甚至损坏

电网保护装置误动作,导致电网事故

通信故障、中断,影响飞机导航危及人身安全

The Future of Analog IC Technology®

电磁干扰的危害

电子设备损坏的原因

,

电磁干扰的危害不容小觑

The Future of Analog IC Technology®

ips isp

θ =0 Ips<isp,

ips

d Core

X-3

A x

Pri. winding Shielding Sec. winding

5-6 4-X

x B

ips=isp,icm=0

θ

31

The Future of Analog IC Technology®

变压器的共模噪声以及抑制

2. 优化变压器的共模噪声

抑制共模噪声

2. 优化变压器的共模噪声

C SP

V D1

VP

C PS

+ VD1 Zcm Csp Cps

VP

输出电压比较低且原边没有屏蔽时,Vp是主要共模干扰源

+ 输出电压比较高且原边有屏蔽时,需要考虑VD1的共模干扰