2.4 GHz射频低噪声放大器分析与设计

2.4GHz射频功率放大器的设计

毕业论文(设计)论文(设计)题目:2.4GHz射频功率放大器的设计目录中文摘要 (1)Abstract (2)第一章绪论 (3)第二章理论基础 (5)2.1 二端口网络 (5)2.2 技术指标 (6)2.2.1 输出功率 (7)2.2.2 功率增益 (8)2.3 匹配网络 (9)2.3.1共轭匹配 (11)2.3.2负载牵引 (11)2.4 传输线理论简介 (12)2.5 ADS软件简介 (12)第三章电路设计 (14)3.1器件选型和功率分配 (14)3.1.1器件选型 (14)3.1.2 功率和增益分配 (14)3.2 单级放大器设计 (15)3.2.1功率级(Power stage)设计 (15)3.2.2驱动级(Driver stage)设计 (23)3.2.3 两级功率放大器系统设计 (26)第四章总结与展望 (29)谢辞 (30)参考文献 (31)附录翻译 (33)中文摘要近年来,RFID技术的应用在全球掀起一场热潮。

2.4G技术标准由于它的广泛应用,更是成为技术和市场领域的宠儿。

RFID最重要的部分是发射机,而射频功率放大器作为发射机的核心部件,它的性能是制约整个RFID系统性能和技术水平的关键因素。

本文介绍了基于ADS用于RFID系统的2.4GHz射频功率放大器的硬件电路设计方法。

整个系统以MOSFET器件为核心功放晶体管,在2.4GHz、工作电压为3.3V 条件下,采用两级功放级联方式,前端驱动级工作于小信号状态,为后端提供高功率增益,后端功率级工作于大信号,提供高功率输出。

级联之后的效果是实现了27dB功率增益和高达近27dBm功率输出。

该系统主要应用于超高频射频识别读写器系统。

本文深入探讨了整体硬件电路的设计方案,详细阐述了电路设计的原理和方法,最后给出了具体的实现过程。

关键词:GaAs FET;RFID;ADS;2.4G无线系统;射频功率放大器AbstractIn recent years, RFID technology has led to a boom in the world. 2.4G technology standard has become a cosset of the technology and market field, just because of its wide range of applications. Transmitter is the most important part of the RFID system. As the core component of a transmitter, the performance of RFPA becomes to the key factor restricting capability and technical level of the whole RFID systemThis paper introduces a method of 2.4GHz RFPA hardware circuit designing used in RFID system based on ADS. The entire system using MOSFET component as the core power transistor contains two-stage cascade amplifiers working in 3.3V supply voltage, 2.4GHz. The driver-level works in small-signal state, providing high power gain for the back-end; power-level works in large-signal state, providing high output-power for the load. The effect after cascade is to achieve a 27dB power gain and a 27dBm output-power.We discuss the blue print of the overall hardware circuit design in this paper, expatiate the principles and methods of circuit design in detail, and finally give a concrete realization of the process.Key words: GaAs FET; RFID; ADS; 2.4G wireless system; RF Power Amplifier第一章绪论随着人类社会进入信息时代,无线通信技术有了飞速的发展,尤其是射频微波通信技术的产生和发展无疑对无线通信技术的发展起到了决定的作用。

2.4GHz低噪声放大器的设计

作者 简介: 杨虹( 1 9 6 6 -) , 男, 四川蓬溪人, 1 9 8 8 年毕业于 东南大学半导体物理及 器件专业, 获 工学学士学位, 1 9 9 5 年8 月毕业于电子科技 大学

电子材料与元器件专业, 获工 学学士学位, 现任重庆邮电大学光 电学院副院长, 教授 , 主要从事微 电子材料 与元器件及微波 / 毫米

F

FL 0

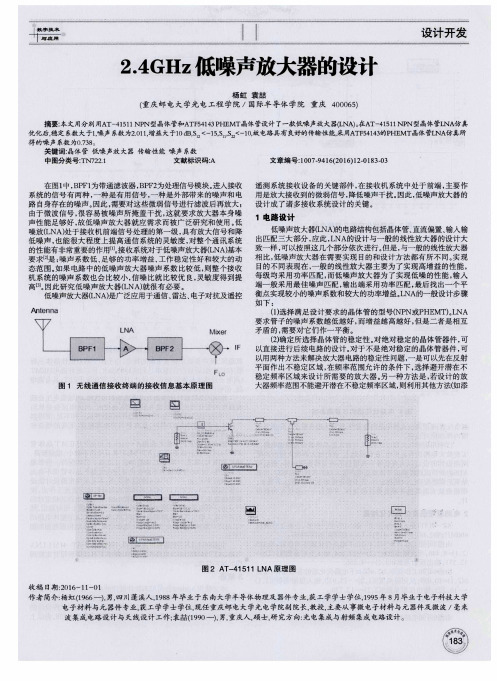

图 1 无线通信接收终端 的接收信息基本原理图

圈

‘

圜

—

。

:

自 安 : 蒙 菇 : ≤ 。 。 鬻

豳

…

_

■r

.

…。 一蠹

.

l _ I

囹臣三 墨口 一

圈

2 嚣 黜瞄

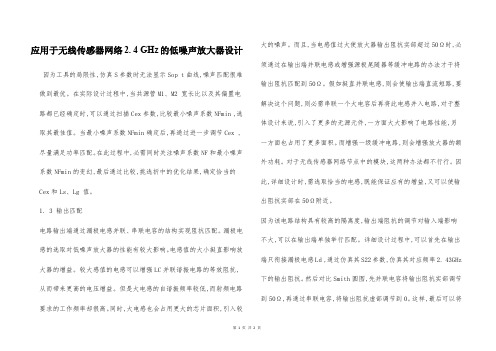

图2 A T 一 4 1 5 1 1 L NA原 理 图 收 稿 日期 : 2 0 1 6 -1 1 — 0 1

波集成电路设计 与天线设计工作; 袁 ( 1 9 9 0 -) , 男, 重庆人, 硕 士, 研 究方向: 光 电集成与射频 集成 电路设计。

{ 姻n

霾 _ [ 一

图7 A TF 5 41 4 3 L NA原 理 图

固

南

t

在图1 中, B P F 1 为 带 通滤 波器 , B P F 2 为 处理 信 号模 块 。 进 入 接 收 系 统 的信 号 有 两 种 , 一种是有用信号 , 一 种 是 外部 带 来 的 噪 声 和 电 路 自身存在的噪声 。 因此 , 需要对这些微弱信号进行滤波后再放大; 由于微波信号 , 很容 易被 噪声所掩盖 干扰 , 这就要求放大器本身 噪 声性能足够好 , 故低噪声放大器就 应需求而被 广泛研究和使用 。 低 噪放( L NA) 处于接收机前端信号处理的第一级 , 具有放大信号和降 低噪声 , 也能 很大 程度上 提高通信系统的灵敏度 , 对整个通讯 系统 的性 能有非常重要的作用【 l 1 。 接收系统对于低 噪声放大器( L N A) 基本 要 求f 0 1 是: 噪声 系 数 低 、 足够的功率增益 、 工 作 稳 定性 好 和 较 大 的 动 态范 围。 如果电路中的低噪声放大器 噪声 系数 比较 低 , 则整个接 收 机系统的噪声 系数也 会比较小 , 信噪 比就 比较优 良, 灵敏 度得 到提 高[ 3 】 。 因此研究低 噪声放 大器( L NA) 就很有 必要 。 低噪声放大器( L N A) 是广泛应用于通信、 雷达、 电子对抗及遥控

2.4G放大器电路原理图

2.4G 射频双向功放的设计与实现在两个或多个网络互连时,无线局域网的低功率与高频率限制了其覆盖范围,为了扩大覆盖范围,可以引入蜂窝或者微蜂窝的网络结构或者通过增大发射功率扩大覆盖半径等措施来实现。

前者实现成本较高,而后者则相对较便宜,且容易实现。

现有的产品基本上通信距离都比较小,而且实现双向收发的比较少。

本文主要研究的是距离扩展射频前端的方案与硬件的实现,通过增大发射信号功率、放大接收信号提高灵敏度以及选择增益较大的天线来实现,同时实现了双向收发,最终成果可以直接应用于与IEEE802.11b/g兼容的无线通信系统中。

双向功率放大器的设计双向功率放大器设计指标:工作频率:2400MHz~2483MHz最大输出功率:+30dBm(1W)发射增益:≥27dB接收增益:≥14dB接收端噪声系数:< 3.5dB频率响应:<±1dB输入端最小输入功率门限:<?15dB m具有收发指示功能具有电源极性反接保护功能根据时分双工TDD的工作原理,收发是分开进行的,因此可以得出采用图1的功放整体框图。

功率检波器信号输入端接在RF信号输入通道上的定向耦合器上。

当无线收发器处在发射状态时,功率检波器检测到无线收发器发出的信号,产生开关切换信号控制RF开关打向发射PA通路,LNA电路被断开,双向功率放大器处在发射状态。

当无线收发器处在接收状态时,功率检波器由于定向耦合器的单方向性而基本没有输入信号,这时通过开关切换信号将RF 开关切换到LNA通路,PA通路断开,此时双向功率放大器处在接收状态。

下面介绍重点部位的设计:发射功率放大(PA)电路发射功率放大电路的作用是将无线收发器输入功率放大以达到期望输出功率。

此处选择单片微波集成电路(MMIC)作为功率放大器件,并采用两级级联的方式来同时达到最大输出功率与增益的要求。

前级功率放大芯片选择RFMD公司的RF5189,该芯片主要应用在IEEE802.11b WLAN、2.4GHz ISM频段商用及消费类电子、无线局域网系统、扩频与MMDS 系统等等。

应用于无线传感器网络2. 4 GHz的低噪声放大器设计

应用于无线传感器网络2. 4 GHz的低噪声放大器设计因为工具的局限性,仿真S参数时无法显示Sop t曲线,噪声匹配很难做到最优。

在实际设计过程中,当共源管M1、M2 宽长比以及其偏置电路都已经确定时,可以通过扫描Cex参数,比较最小噪声系数NFmin ,选取其最佳值。

当最小噪声系数NFmin确定后,再通过进一步调节Cex ,尽量满足功率匹配。

在此过程中,必需同时关注噪声系数NF和最小噪声系数NFmin的变幻,最后通过比较,挑选折中的优化结果,确定恰当的Cex和Ls、Lg 值。

1. 3 输出匹配电路输出端通过漏极电感并联、串联电容的结构实现阻抗匹配。

漏极电感的选取对低噪声放大器的性能有较大影响。

电感值的大小挺直影响放大器的增益。

较大感值的电感可以增强LC并联谐振电路的等效阻抗,从而带来更高的电压增益。

但是大电感的自谐振频率较低,而射频电路要求的工作频率却很高。

同时,大电感也会占用更大的芯片面积,引入较大的噪声。

而且,当电感值过大使放大器输出阻抗实部超过50Ω时,必须通过在输出端并联电感或增强源极尾随器等缓冲电路的办法才干将输出阻抗匹配到50Ω。

假如挺直并联电感,则会使输出端直流短路,要解决这个问题,则必需串联一个大电容后再将此电感并入电路,对于整体设计来说,引入了更多的无源元件,一方面大大影响了电路性能,另一方面也占用了更多面积。

而增强一级缓冲电路,则会增强放大器的额外功耗。

对于无线传感器网络节点中的模块,这两种办法都不行行。

因此,详细设计时,需选取恰当的电感,既能保证应有的增益,又可以使输出阻抗实部在50Ω附近。

因为该电路结构具有较高的隔离度,输出端阻抗的调节对输入端影响不大,可以在输出端单独举行匹配。

详细设计过程中,可以首先在输出端只衔接漏极电感Ld ,通过仿真其S22参数,仿真其对应频率2. 43GHz 下的输出阻抗。

然后对比Smith圆图,先并联电容将输出阻抗实部调节到50Ω,再通过串联电容,将输出阻抗虚部调节到0。

S波段低噪声放大器研究与设计的开题报告

S波段低噪声放大器研究与设计的开题报告一、选题背景随着现代通信技术的不断发展,无线通信系统让人们的生活更加方便和舒适,低噪声放大器(low noise amplifier,LNA)作为无线通信系统中的重要组成部分,在无线电收发机中主要用于增加系统的灵敏度和带宽,起到放大信号、提高信噪比等作用。

其中,S波段(2-4 GHz)是一个重要的通信频段,在高速数字通信、雷达和卫星通信等领域中得到了广泛的应用。

因此,本文选取了S波段低噪声放大器的研究与设计作为课题,旨在探究S波段LNA的性能和优化方法,设计出高性能的S波段LNA,为无线通信系统的研究和发展提供理论和实践基础。

二、选题意义1.弥补国内S波段LNA的研究缺乏目前国内在S波段LNA方面的研究比较缺乏,而LNA的性能直接影响整个无线通信系统的性能。

因此,本文的研究将填补国内在S波段LNA方面的空白。

2.提高S波段LNA的灵敏度和带宽在无线通信系统中,提高灵敏度和带宽是关键问题,而LNA作为信号放大器的重要组成部分,其性能优化将能够提高整个通信系统的灵敏度和带宽。

3.推动S波段通信技术的发展S波段通信技术在高速数字通信、雷达和卫星通信等领域中发挥着重要作用,而高性能的S波段LNA将能够促进S波段通信技术的发展,推动无线通信技术的研究和发展。

三、研究内容本文将围绕以下几个方向展开研究:1.对S波段LNA的基本原理进行研究和分析。

2.分析S波段LNA的性能,包括增益、噪声系数、线性度等。

3.对S波段LNA的优化设计进行探究和研究。

4.开展实验,验证所设计的S波段LNA的性能和优良特性。

四、研究方法1.文献调研法:对S波段LNA的基本原理进行深入的文献调研和分析,掌握并研究相关文献的资料,对S波段LNA的性能、设计方法进行全面了解和理解。

2.理论分析法:计算和推导S波段LNA的设计公式和参数,分析LNA的性能和特性,为设计优良的LNA提供理论基础。

3.仿真模拟法:应用模拟器进行电路仿真,检验和改善LNA的性能,并对LNA的参数进行优化调整。

2.4GHz低噪声放大器的设计

2.4GHz低噪声放大器的设计作者:杨虹袁喆来源:《数字技术与应用》2016年第12期摘要:本文用分别用AT-41511 NPN型晶体管和ATF54143 PHEMT晶体管设计了一款低噪声放大器(LNA)。

在AT-41511 NPN型晶体管LNA仿真优化后,稳定系数大于1,噪声系数为2.011,增益大于10 dB,S12关键词:晶体管低噪声放大器传输性能噪声系数中图分类号:TN722.1 文献标识码:A 文章编号:1007-9416(2016)12-0183-03在图1中,BPF1为带通滤波器,BPF2为处理信号模块。

进入接收系统的信号有两种,一种是有用信号,一种是外部带来的噪声和电路自身存在的噪声。

因此,需要对这些微弱信号进行滤波后再放大;由于微波信号,很容易被噪声所掩盖干扰,这就要求放大器本身噪声性能足够好,故低噪声放大器就应需求而被广泛研究和使用。

低噪放(LNA)处于接收机前端信号处理的第一级,具有放大信号和降低噪声,也能很大程度上提高通信系统的灵敏度,对整个通讯系统的性能有非常重要的作用[1]。

接收系统对于低噪声放大器(LNA)基本要求[2]是:噪声系数低、足够的功率增益、工作稳定性好和较大的动态范围。

如果电路中的低噪声放大器噪声系数比较低,则整个接收机系统的噪声系数也会比较小,信噪比就比较优良,灵敏度得到提高[3]。

因此研究低噪声放大器(LNA)就很有必要。

低噪声放大器(LNA)是广泛应用于通信、雷达、电子对抗及遥控遥测系统接收设备的关键部件,在接收机系统中处于前端,主要作用是放大接收到的微弱信号,降低噪声干扰。

因此,低噪声放大器的设计成了诸多接收系统设计的关键。

1 电路设计低噪声放大器(LNA)的电路结构包括晶体管、直流偏置、输入输出匹配三大部分,应此,LNA的设计与一般的线性放大器的设计大致一样,可以按照这几个部分依次进行。

但是,与一般的线性放大器相比,低噪声放大器在需要实现目的和设计方法都有所不同。

2.4GHz E类射频功率放大器的设计

图 2为理想 E类功率放大器两端 电压 、电流 的

波形图 。

为 了使 该功率放 大器的效率达 到 1 0 0 %, 该功率放大器 的瞬态响应网络应该满足 以下三 个条件: ( 1 )晶体 管导通 时,晶体管两 端的 电压

必 须 为 零 ,即 晶体 管 的瞬 态 响 应 网 络 应 在 晶体

并且趋 向于零 。当晶体管断开时,晶体管 电压

虽然 有 点 高 ,但 无 电 流 通 过 晶 体 管 , 从 而 达 到 减 小耗 散 功 率 的 目 的 。E类 功 率 放 大 器 就 是 按

照 电压 与电流 不重叠出现而设计出来的,使得 在任 意时刻,电压与电流的乘积为零,即耗散 功 率为零 。图 l 为 E类功率放大器的拓扑结构

键 词 】E类 功 放 2 . 4 G H z 伪 差分 饱和输

, 率

提 供 直 流 偏 置 , 电 容 cl为 外 加 电容 和 晶 体 管

电疆

C a )

寄生 电容之 和 ,电感 L 2和 电容 C 2构成滤 波 谐振 网络,该 谐振 网络谐 振频率 为 2 . 4 G Hz 。 R。 为从晶体管获得最大 功率 的最佳匹配负载 。 E类射频功率放大器 由单个 晶体 管和负载匹配

流 才 不 会 发 生 重 叠 ,从 而 保证 其 1 0 0 % 的 效率 。 根 据 以上 三 点 ,可 以列 出微 分 方 程 。通 过 对 微 分 方 程 进 行 解 析 ,可 以得 出 E类 功 率 放 大 器 负

,

图3 :反 相 器驱 动 级 电路 图

:

—

,

j 可穿戴系统等 ,E类射频 功率 放大器的效

图。 该 拓 扑 机 构 由 Gr e b e n n i k o v在 2 0 0 2年 提 出 , 经过 l 0余 年 的 发 展 ,该 放 大 器 以 其 效 率 高 , 可 设计 性 强等 优 点而 被 广 泛 应 用 。

低功耗2.4GHz 0.18μm CMOS全集成低噪声放大器设计

电路设计分 析采用 A S仿真软件 , D 电源电压 I 工作 电流 8 A, V, m 增益为 1 . d , 5 4 B 噪声 系数 z 7 B 线性度指标 I 3为一0 6 B 结论是 C S .d , I P ・d 。 MO

工艺 在 工艺 和模 型 方 面 的改 进 , 得 C 使 MOSRF电 路 设计 更 为 精 确 , 集 成 度 更 高 。 可

的低 噪声 放大 器 。

以上 , 得 利用 C 使 MOS工 艺 实 现 GHz 段 的 高 频 频

模 拟 电路成 为可 能 。 此外 , 无线 接 收机 小 型化 和低 价

格 的发 展趋 势 , 动 着 收 发机 射频 电路 和基 带 电 路 推

1 电路 设 计 原 理

基于 C M0S工 艺 的低 噪 声 放 大 器设 计 一 般采 用 经 典 的共源 共栅 级联 结构 , 过 减小 密勒 效应 , 通 增

O 引 言

快速 增 长 的无 线 通 信 市场 , 对 低 功 耗 和低 价 使

砷 化 镓 有 很 强 的 优 势 , 是说 , 就 只有 利用 C MOS工

艺 , 有 可 能将 射 频 、 才 中频 , 以及 基 带部 分 的电路 全 部 集成 到一 块 芯 片上 。 由于 接 收机越 来越 多 的使用 在 小 型移 动 设 备 上 , 因此 低 功 耗 是 一个 未来 的发展

要求。 -

格 的接 收机 芯 片组 的需求 越来 越 大 。以往 的接 收机 大 都 是利用 砷化镓 或 双极 性硅 工 艺实 现 的功率 放 大 器 、 频 器 、 噪 声 放 大 器 等 射 频 电路 与 C 混 低 MOS工 艺 实 现 的中频 和基带 电路 进行 混 合集 成 。 且 , 并 那些 射 频 电路 主要 由分 离元 件或低 集 成度 的射 频 芯片 构 成 的 。近 年 来 , 着 特征 尺 寸 的 不 断 减 小 ,. 8 m 随 0 1

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

本文设计了一个基于TSMC 0.18p.m CMOS工艺。工作频 率为2.4 GHz的射频低噪声放大器,通过优化达到了较好的性 能。电路结构如图l所示,电路采用的是电感源极负反馈的共 源一共栅结构(ca蚰ede结构、.这种结构可以在提供较低的噪声 系数的同时.实现50n的输入阻抗。

r、图l LNA电路结梅

英文刊名: 年,卷(期): 引用次数:

王宁章, 周长川, WANG NINGZHANG, ZHOU CHANGCHUAN 计算机与电子信息学院,广西大学,530004

微计算机信息 MICROCOMPUTER INFORMATION 2007,23(29) 2次

参考文献(2条) 1.Behzad Razavi.余志平.周润德 射频微电子 2006

流可以,表示一如下=:mk%(击)%,老吩2彘

v-是MOS管的饱和速度,V乎V旷V疆称为栅过驱电压.、k 为栅源偏置电压,¨为有效迁移率,V髓为阈值电压。0为迁移

率的衰减系数,0的值可以通过估计得到。利用泰勒展开式,计

lIP3:8VsatLeffV。d(1+盟×1+—!监L)2 算L-的泰勒系数,可以推出短沟道MOS管的lIP3的表达式为:

2.段晓峰.陈向东.黎文模 0.5umCMOS工艺参数电流反馈运算放大器[期刊论文]-微计算机信息 2006(11)

相似文献(9条)

1.期刊论文 王宁章.周长川.WANG Ning Zhang.ZHOU Chang Chuan 2.4GHz 0.18μm CMOS低噪声放大器分析与设计

-电子技术应用2007,33(7)

鎏;堕

图4 S参数和噪声系数的仿真结果图

在设计过程中,充分考虑了电感O值对噪声的影响,使用 INDQ模型来模拟电感,O值设为6,中心频率设为2.4GHz,电感 的值一般不超过7nil.采用1.5V电源供电。

上图可以看出,低噪声放大器工作在2.4GHz时.噪声系散 (noise矗鼬蚋为1.768dB,噪声系数较低;正向传输增益s21大于 20dB,具有较高的增益;SII、¥22在工作频率2.4GHz处达到援 值。说明输入、输出阻抗匹配良好,S11等于—26.t37dB,S22等 于-41.323dB,说明回波损耗很小;¥12为一34.532dB。说明反向 隔离特性比较理想。

电子设计

文章编号:1008-0570(2007)10_4-o“2—n2

中文核心期刊‘微计算机信息'(嵌入式与SOC)2007年第23卷第10—2期

2.4 G Hz射频低噪声放大器分析与设计

Analysis and Design of a 2.4 GHz Radio Frequency Low-Noise Amplifier

2.学位论文 谢婷婷 0.18μmCMOS工艺5GHz WLAN低噪声放大器和Low-IF下变频器 2003

最近十年,网络与无线通信的迅猛发展极大地推动了社会的信息化进程.一方面,各种信息,包括文字、图片、声音和图像,广泛地通过网络传播到信息 终端,网络的各种业务已渗透到各行各业.另一方面,各种无线通信技术的广泛应用已经使人类摆脱了通信场所的限制,基本实现了随时随地通信的梦想.为 了适应信息爆炸增长对通信领域的更高要求,人们渴望将网络和无线通信的优点合而为一.具体米说,就是人们的智能终端不需要通过不同类型的连接线米 连接,而是直接以无线方式、低成本接入当地的有线网络,实时地共享并交换各种信息资源,无线局域网(WLAN)技术正是在这种背景下产生的.本课题采用 TSMC 0.18μm的CMOS工艺设计并实现用于IEEE 802.11a 5GHz WLAN系统的射频接收机中的低噪声放大器(LNA)和低中频下变频器(Dowr Converter).其中 ,LNA的主要功能是将天线接收到的微弱信号在引入较低的噪声的情况下进行放大.输入端要求实现50欧姆阻抗匹配.Down Converter将LNA输出的信号与本 振信号(LO)混频产生低中频信号,要求噪声低、线性度高并提供适当的增益.本论文第二章介绍接收机的基本结构及其性能参数.第三章介绍了集成电路的 工艺渠道,工艺选择和设计流程.第四章介绍了LNA阻抗匹配的几种结构,在此基础上确定了源极电感反馈式结构.然后对LNA的噪声进行了分析和优化,给出 了电路的仿真结果.论文第五章首先介绍变频器的基本原理和几种不同的电路结构,引入了差分平衡Gilbert式结构,通过对变频器噪声机理的分析,在原有 的结构上增加了电流注入模块.最后给出了电路的仿真结果和芯片照片.第六章介绍芯片的测试,包括在片测试和基片测试,LNA的测试结果表明电路工作在 4.7GHz的增益为15.7dB,噪声为2.5dB,1dB增益压缩点对应的输入功率为-9.6dBm,基本满足指标.变频器的测试工作已在进行中.

IP3l、ILP32。根据公式回,可以估计出系统的lIP3约为2.34dBm。

图3 IIP3与的变化关系网

3电路仿真结果及讨论

车设计是基于TSMC的0.189in工艺.采用BSIM3V3.2模 型.利用ADS2005A(AdvancedDesi印System):进行设计和仿真, 取得了较好的效果。噪声系数和S参数的仿真结果如下罔所示!

2}‘d)oLef CosRsQ:p 变大,会使功耗增加、增益降低。需要选择合适的栅宽度,以实

现优异的噪声性能,按照功率约束条件下的设计方法。得到MI 的最优栅宽度:

wopt

c叵是单位面积栅氧化层电容,k是有效栅长,这两个参数 由工艺决定。Q。是最佳品质因数。根据TSMC 0.181xm CMOS工 艺参数,通过计算可以得到W戚,M2的栅宽度取M1栅宽度的1,

。+

· ’:

Abstract:The aspects of noise。linearity,impedance mashing,the design methoddo舒0f the[ow-noi∞amplifier is preseaated in de-

tail.based the principle of the low-noisB amplifier.This circuit is designed in a TSMC 0.18pan CMOS process and simulated埘tII

基于低噪声放大器设计原理,从噪声、线性度、阻抗匹配等方面详细讨论了低噪声放大器的设计.电路采用TSMC 0.18μm CMOS工艺进行设计,利用 ADS2005A对电路进行谐波平衡、S参数分析及双音测试,结果表明,其噪声系数为1.795dB,正向增益为17.35dB,IIP3约为-1.43dBm,功耗约8.96mW.

Key words:Low-noise Amplifier皿NA).Linearity.Match

1引言

现代无线通讯设备不断地朝着低成本、便携式的方向发展。

使得基于CMOS工艺的射频集成电路设计成为近年来的研究 热点。射频低噪声放大器旺擅LNA)是无线通信系统射频接收机 前端的关键模块.它必须在一定的功耗条件下提供足够的增益. 优异的噪声性能。良好的线性度.足够的增益可以抑制后续级模 块的噪声.优异的噪声性能几乎央定整个接收机的噪声性能. 良好的线性度可以使其在较大的信号动态范围内正常工作。

构级联而成.系统的输人三阶交词点llP3(input-refened third— order imercept poin0.可以表示为:

丽I 。砰+1 育+k‘,B’1/P口 322… }t (5)

其中HF3I、lIP3:分别表示MI和M3的输^三阶变调点。由 于啦表示M1的增益,且瑾1大于1,所以系统的线性度主要由 后一级的线性度央定。工作在饱和区的短沟道MOS管的捕极电

10。因为cp=12W印f‘盯c甜CP的值一定,根据公式(2),可以得 到c一。已知0.18p。mCMOS工艺的截止频率‘可以达到40GHz 以上,根据公式(3)、(4),可以得到k、k的值,由于电感与衬底阃 寄生电容以及栅电阻的影响,k的值要比计算得到的值要小。

2.3线性度分析和M3宽度的选取

图 1所示Caseode结构RF LNA可以等效为两级非线性结

k、L的值变小,改善了噪声性能,也易于使用CMOS工艺实现。 输出匹配主要是由k、L和cd相匹配完成。k和C。主要完

成输出匹配,为了调节S11、¥22参数,引人了电感L。如果L的值

变大,ISllll蟹/值变大,而IS22l的值变小,反之也成立.可以利用L

来调节Sll、¥22参数,使输人、输出阻抗匹配达到理想的效果。

宽度,来提高橱过驱电压、0,增大MOS管的线性度。图3给出 了Vd与Ⅲ13的关系,可以看出IIP3随着、0的变大而变大。

由于系统的线性度主要由M3决定,为了得到较好的线性度。

M3管的栅宽度取MI管的一半。通过测量v。,根据工艺参效计算 得到e,我们可以估计出lIP3的值。测量Ml管和M3管的栅过驱

电压v础和V吨,根据公式旧,可以计算得到M1管和M3管的I.

ADS2005A.Results from simulation show that the circuit has a noise figure 0f 1.768dB,a forward power gain of 20.36 dB,蛐lIP3

0f 2.34dBm.and the power di%ipation is below 12mW hom a 1.5 V supply.

(530004广西大学计算机与电子信息学院)王宁章周长川

通讯地:吐:(530004广西广西大学计算机与电子信息学院)王宁章

(收稿曰期:20079上3)(修稿日期..2007.10.25)

万方数据

邮局订阅号:82.946 360元,年一243—

2.4 GHz射频低噪声放大器分析与设计

作者: 作者单位: 刊名:

提供良好的隔离,并减小了M1漏栅电容Cd的影响。Ml和M2 组成电流镜,由于电阻的阻值随温度变化.为了保持偏置支路稳

定,采用电流源SRCl提供稳定的偏置电流。Rk是偏置电阻,k 和I’完成输人端口阻抗匹配,在第二级电路中.k、L和cd完成 输出端口阻抗匹配,C。、Cd用于隔离直流信号。