一款多功能电能计量芯片简介(CS5463)

CS5464电能计量芯片 中文版

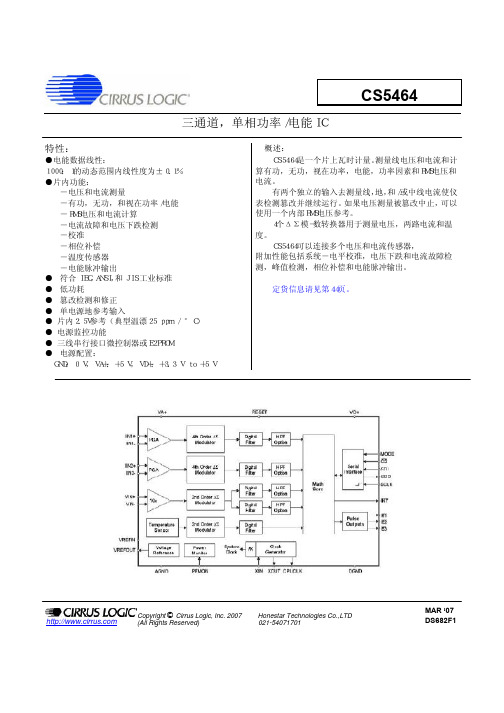

概述:

CS5464是一个片上瓦时计量。测量线电压和电流和计 算有功,无功,视在功率,电能,功率因素和RMS电压和 电流。

有两个独立的输入去测量线,地,和/或中线电流使仪 表检测篡改并继续运行。如果电压测量被篡改中止,可以 使用一个内部RMS电压参考。

4个ΔΣ模-数转换器用于测量电压,两路电流和温 度。

CS5464可以连接多个电压和电流传感器, 附加性能包括系统-电平校准,电压下跌和电流故障检 测,峰值检测,相位补偿和电能脉冲输出。

定货信息请见第44页。

Copyright © Cirrus Logic, Inc. 2007

(All Rights Reserved)

5.1.2 电流1和电流2输入 ................................................................17 5.1.3 功率故障监控输入 ................................................................17

2

DS682F1

5.1.4 参考电压输入 .............................................1.5 参考电压输出 ....................................................................17

Honestar Technologies Co.,LTD 021-54071701

MAR ‘07 DS682F1

CS5464

目录

1.综述 .................................................................

用电设备功率测试仪毕业设计

石家庄铁道大学四方学院毕业设计用电设备功率测试仪Electrical Equipment Power TestInstrument毕业设计任务书题目用电设备功率测试仪设计学生姓名学号班级0809-3 专业电子信息工程承担指导任务单位石家庄铁道大学导师姓名导师职称一、主要内容设计一个用电设备的用电环境和功率检测的检测装置,用以测出用电器的瞬时功率、电流、负载的性质及功率因数,以及用电环境的电压、电流、频率等。

二、基本要求1.设计一个检测装置,使用电器通过此设备接通电源时可在设备上读出所需参数。

连接图如图1. 图1 2.当用电设备接上该装置工作时,用电设备可正常工作,屏幕上可根据功能按钮选择显示用电设备功率、工作电压、电流、工作时间、累计电能、负载的功率因数电源频率等信息3.具有过载保护和漏电保护。

4.完成硬件电路图设计,程序设计,电路版图设计,设计说明书正文不少于1万字,查阅文献资料不少于15篇,其中外文文献2篇以上,翻译与课题有关的外文资料不少于3000汉字。

三、主要技术指标(或研究方法)1.工作电压AC220V、频率50Hz,电流0.5-5A,精度1.0级。

2.功耗:≤1.0W,工作电压范围在在70%~120%的额定电压范围内,能正常工作,且保持准确度符合等级要求,并能承受400V电压而不损坏。

3.可累积负载工作时间,以及负载所有电能累积。

4.最大负载功率1200VA。

四、应收集的资料及参考文献电工与电子技术单片机编程与控制技术模数转换技术及应用Lcd应用指南电力电子技术五、进度计划第1周:开题,完成开题报告。

第2周——第3周:资料收集,文献阅读。

第4周——第8周:系统设计,电路实现,程序仿真。

第9周——第11周:期中检测,系统综合调试。

第12周:系统统调完成。

第13周——第14周:设计说明书撰写。

第15周——第16周:答辩环节。

教研室主任签字时间年月日毕业设计开题报告题目用电设备功率测试仪设计学生姓名刘猛学号20086383 班级0809-3 专业电气工程系一、本课题的研究背景近年来,随着冶金工业、化学工业和电气化铁路的发展,以及直流输电、大功率单相整流技术在工业部门和用电设备上的广泛应用,电力系统的污染也日益严重。

带有串行接口的功率电能计量芯片CS5460及其应用

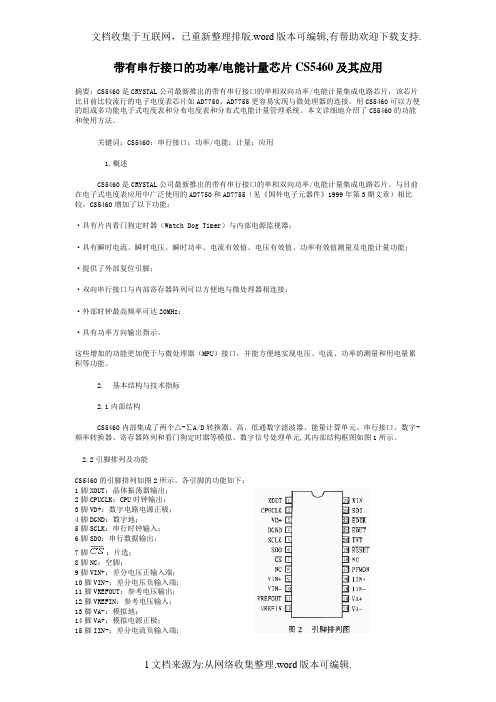

带有串行接口的功率/电能计量芯片CS5460及其应用摘要:CS5460是CRYSTAL公司最新推出的带有串行接口的单相双向功率/电能计量集成电路芯片,该芯片比目前比较流行的电子电度表芯片如AD7750、AD7755更容易实现与微处理器的连接。

用CS5460可以方便的组成多功能电子式电度表和分布电度表和分布式电能计量管理系统。

本文详细地介绍了CS5460的功能和使用方法。

关键词:CS5460;串行接口;功率/电能;计量;应用1.概述CS5460是CRYSTAL公司最新推出的带有串行接口的单相双向功率/电能计量集成电路芯片。

与目前在电子式电度表应用中广泛使用的AD7750和AD7755(见《国外电子元器件》1999年第3期文章)相比较,CS5460增加了以下功能:·具有片内看门狗定时器(Watch Dog Timer)与内部电源监视器;·具有瞬时电流、瞬时电压、瞬时功率、电流有效值、电压有效值、功率有效值测量及电能计量功能;·提供了外部复位引脚;·双向串行接口与内部寄存器阵列可以方便地与微处理器相连接;·外部时钟最高频率可达20MHz;·具有功率方向输出指示。

这些增加的功能更加便于与微处理器(MPU)接口,并能方便地实现电压、电流、功率的测量和用电量累积等功能。

2. 基本结构与技术指标2.1内部结构CS5460内部集成了两个△-∑A/D转换器、高、低通数字滤波器、能量计算单元、串行接口、数字-频率转换器、寄存器阵列和看门狗定时器等模拟、数字信号处理单元,其内部结构框图如图1所示。

2.2引脚排列及功能CS5460的引脚排列如图2所示。

各引脚的功能如下:1脚XOUT:晶体振荡器输出;2脚CPUCLK:CPU时钟输出;3脚VD+:数字电路电源正极;4脚DGND:数字地;5脚SCLK:串行时钟输入;6脚SDO:串行数据输出;7脚:片选;8脚NC:空脚;9脚VIN+:差分电压正输入端;10脚VIN-:差分电压负输入端;11脚VREFOUT:参考电压输出;12脚VREFIN:参考电压输入;13脚VA-:模拟地;14脚VA+:模拟电源正极;15脚IIN-:差分电流负输入端;16脚IIN+:差分电流正输入端;17脚PFMON:电源掉电监视输出;18脚NC:空脚;19脚:复位输入;20脚:中断输出;21脚:电能脉冲输出;22脚:功率方向指示输出;脚SDI:串行数据输入;24脚XIN:晶体振荡器输入。

基于电能计量芯片CS5463A的电子式电能表的设计_甘建平

技术论坛

基于电能计量芯片 CS5463A 的电子式电能表的设计

Design of Watt-hour Meter Based on Energy IC CS5463A

甘建平 朱 青 湖南大学电气与信息工程学院(长沙 410082)

摘要:针对目前应用需求设计了一款新型多功能电子式电能表。本文主要介绍该电能表的主要功能以及 所采用的电能计量芯片 CS5463A 的特性、工作原理以及在电子式电能表中的应用电路,最后介绍了 CS5463A 芯片通讯接口的实现。

近年来,电子式电能表在国际、国内得到了迅速 推广。国外许多 IC(Integrate circuit)厂家不失时机的 推出了各种电子式电能表专用芯片。目前国内较为常 用的电子式电能表芯片有美国 Cirrus Logic 公司的 CS5460A、CS5463A、美国 ADI 公司的 ADE7758、珠 海炬力公司的 ATT7022、日本 TDK 公司的 71M6513H 等。其中 CS5463A 是美国 Cirrus Logic 公司生产的专用 于电力参数测量的单相双向功率/电能 IC,可以精确 测量和计量有功电能、无功电能、瞬时功率、IRMS 和 VRMS,具有与微控制器通讯的 SPI 口。

所示;由视在功率、有功功率可以计算出三角无功功

率 QTg,如式(5)所示。

视在功率: = ×

(2)

功率因数: =

(= 2

2

(4) (5)

3.3 CS5463A 的外部引脚电路 图 2 为 CS5463A 的典型应用电路图。电网电压经

过电压采样电路得到小电压信号输入到CS5463A 的电 压通道输入引脚。电压采样电路由 R205、R206、R207、 R208、C205 组成。电压采样电路由精密电阻网络及滤 波电容组成。为了保证精度,采样电阻全部采用高稳 定度的精密电阻,误差为 25ppm。电流互感器的电流 信号经过电流采样电路将电流信号转换为小电压信号 输入到 CS5463A 的电流通道输入引脚。电流采样电路 由 R213、R201、R202、R203、R204、C207、C210、R209、 C206 组成。C205、C207、C210 起滤除高频谐波分量 的作用;R209、C206 起滤波和抗混叠的作用;D201、 D203 为输入保护器件,防止由于输入电压过高而造成 CS5463A 的损坏。

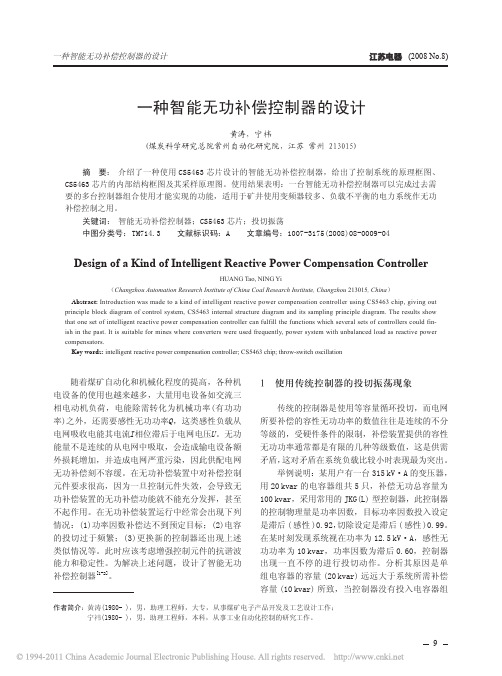

一种智能无功补偿控制器的设计

9江苏电器 (2008 No.8)作者简介:黄涛(1980- ),男,助理工程师,大专,从事煤矿电子产品开发及工艺设计工作;宁礻韦(1980- ),男,助理工程师,本科,从事工业自动化控制的研究工作。

随着煤矿自动化和机械化程度的提高,各种机电设备的使用也越来越多,大量用电设备如交流三相电动机负荷,电能除需转化为机械功率(有功功率)之外,还需要感性无功功率Q ,这类感性负载从电网吸收电能其电流I 相位滞后于电网电压U 。

无功能量不是连续的从电网中吸取,会造成输电设备额外损耗增加,并造成电网严重污染,因此供配电网无功补偿刻不容缓。

在无功补偿装置中对补偿控制元件要求很高,因为一旦控制元件失效,会导致无功补偿装置的无功补偿功能就不能充分发挥,甚至不起作用。

在无功补偿装置运行中经常会出现下列情况:(1)功率因数补偿达不到预定目标;(2)电容的投切过于频繁;(3)更换新的控制器还出现上述类似情况等。

此时应该考虑增强控制元件的抗谐波能力和稳定性。

为解决上述问题,设计了智能无功补偿控制器[1-2]。

1 使用传统控制器的投切振荡现象传统的控制器是使用等容量循环投切,而电网所要补偿的容性无功功率的数值往往是连续的不分等级的,受硬件条件的限制,补偿装置提供的容性无功功率通常都是有限的几种等级数值,这是供需矛盾,这对矛盾在系统负载比较小时表现最为突出。

举例说明:某用户有一台315kV·A 的变压器,用20kvar 的电容器组共5只,补偿无功总容量为100kvar,采用常用的JKG(L)型控制器,此控制器的控制物理量是功率因数,目标功率因数投入设定是滞后(感性)0.92,切除设定是滞后(感性)0.99。

在某时刻发现系统视在功率为12.5kV·A,感性无功功率为10kvar,功率因数为滞后0.60,控制器出现一直不停的进行投切动作。

分析其原因是单组电容器的容量(20kvar)远远大于系统所需补偿容量(10kvar)所致,当控制器没有投入电容器组一种智能无功补偿控制器的设计摘 要:介绍了一种使用CS5463芯片设计的智能无功补偿控制器,给出了控制系统的原理框图、CS5463芯片的内部结构框图及其采样原理图。

电子式电能表专用芯片CS5460及其在电测仪表中的应用

屏 蔽 时 ),所 以 若 让 电 压 、电 流 、功 率 的 瞬 时 值 数 据 每 应 的 1 、2 、3 个 空 操 作( NOP )命 令 字 节( 0 XFE )。

更 新 一 次 就 产 生 一 个 中 断 请 求 ,需 将 循 环 计 数 寄 存 器

图 2 是 笔 者 在 课 题 中 使 用 的 CS 5460 与 MCS 51 系

和 50 可 选 ·一 个 电 压 通 道 固 定 增 益 放 大 器 , 其 增 益 为 10 ·两 个 同 时 采 样 的 # - $ 模 / 数 转 换 器 ·两 个 高 速 数 字 滤 波 器 ·两 个 可 选 用 的 高 通 滤 波 器 ·一 个 功 率 计 算 引 擎 ·一 个 2 . 5 V 片 内 电 压 基 准 ·一 个 可 以 检 测 电 力 不 足 或 电 源 故 障 的 电 源 监 视 器 · 一个持续监视串口通讯的看门狗 · 一 个 2 . 5 MHZ ~ 20 MHZ 可 选 的 内 部 时 钟 发 生 器 · 一个双向串行接口 · 一个电能 / 脉冲变换器 · 一 个 校 准 用 SRAM

P1.0 P1.1 P 1 . 2 MCS 51 P 1 . 3 MCU

INT 1

和 50 , 分 别 对 应 于 最 大 有 效 值 为 150 mV 和 30 mV 的

图 2 CS 5460 与 MCS 51 系 列 单 片 机 接 口 原 理 图

交流信号输入;电压通道的最大有效值输入为 150 mV 。 由 于 CS 5460 的 ! - " 型 模 / 数 转 换 器 采 用 过 采 样 原 理 ,对 高 频 噪 声 有 较 强 的 抑 制 作 用 ,因 而 对 输 入 信 号 无 需 进 行 复 杂 的 滤 波 处 理( 引 入 阻 容 滤 波 电 路 反 而 容 易 引 起 相 移 )。

CS5463中文资料

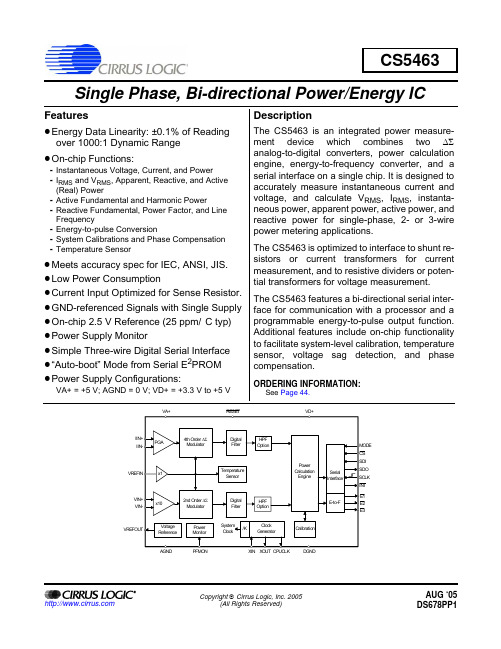

Copyright © Cirrus Logic, Inc. 2005(All Rights Reserved)CS5463Single Phase, Bi-directional Power/Energy ICFeaturesz Energy Data Linearity: ±0.1% of Readingover 1000:1 Dynamic Rangez On-chip Functions:-Instantaneous Voltage, Current, and Power-I RMS and V RMS , Apparent, Reactive, and Active (Real) Power-Active Fundamental and Harmonic Power-Reactive Fundamental, Power Factor, and Line Frequency-Energy-to-pulse Conversion-System Calibrations and Phase Compensation -Temperature Sensorz Meets accuracy spec for IEC, ANSI, JIS.z Low Power Consumptionz Current Input Optimized for Sense Resistor.z GND-referenced Signals with Single Supply z On-chip 2.5V Reference (25 ppm/°C typ)z Power Supply Monitorz Simple Three-wire Digital Serial Interface z “Auto-boot” Mode from Serial E 2PROM z Power Supply Configurations:VA+ = +5V; AGND = 0V; VD+ = +3.3V to +5VDescriptionThe CS5463 is an integrated power measure-ment device which combines two ∆Σanalog-to-digital converters, power calculation engine, energy-to-frequency converter, and a serial interface on a single chip. It is designed to accurately measure instantaneous current and voltage, and calculate V RMS , I RMS , instanta-neous power, apparent power, active power, and reactive power for single-phase, 2- or 3-wire power metering applications.The CS5463 is optimized to interface to shunt re-sistors or current transformers for current measurement, and to resistive dividers or poten-tial transformers for voltage measurement. The CS5463 features a bi-directional serial inter-face for communication with a processor and a programmable energy-to-pulse output function.Additional features include on-chip functionality to facilitate system-level calibration, temperature sensor, voltage sag detection, and phase compensation.ORDERING INFORMATION:See Page 44.AUG ‘05TABLE OF CONTENTS1. Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52. Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63. Characteristics & Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74. Theory of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144.1 Digital Filters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144.2 Voltage and Current Measurements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144.3 Power Measurements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144.4 Linearity Performance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 155. Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 165.1 Analog Inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 165.1.1 Voltage Channel . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 165.1.2 Current Channel . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 165.2 IIR Filters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 165.3 High-pass Filters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 165.4 Performing Measurements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 165.5 Energy Pulse Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 175.5.1 Active Energy . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 175.5.2 Apparent Energy Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 185.5.3 Reactive Energy Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 185.5.4 Voltage Channel Sign Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 185.5.5 PFMON Output Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 195.5.6 Design Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 195.6 Sag and Fault Detect Feature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 195.7 On-chip Temperature Sensor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 195.8 Voltage Reference . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 205.9 System Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 205.10 Power-down States . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 205.11 Oscillator Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 205.12 Event Handler . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 215.12.1 Typical Interrupt Handler . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 215.13 Serial Port Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 215.13.1 Serial Port Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 215.14 Register Paging . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 225.15 Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 235.15.1 Start Conversions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 235.15.2 SYNC0 and SYNC1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 235.15.3 Power-up/Halt . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 235.15.4 Power-down and Software Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 235.15.5 Register Read/Write . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 245.15.6 Calibration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 256. Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 266.1 Page 0 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 266.1.1 Configuration Register ( Config ). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 266.1.2 Current and Voltage DC Offset Register ( I DCoff , V DCoff ) . . . . . . . . . . . . 276.1.3 Current and Voltage Gain Register ( I gn , V gn ) . . . . . . . . . . . . . . . . . . . . 276.1.4 Cycle Count Register ( Cycle Count ) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 276.1.5 PulseRateE Register ( PulseRateE ). . . . . . . . . . . . . . . . . . . . . . . . . . . . . 276.1.6 Instantaneous Current, Voltage, and Power Registers ( I , V , P ) . . . . . . 286.1.7 Active (Real) Power Register ( P Active ) . . . . . . . . . . . . . . . . . . . . . . . . . . 286.1.8 RMS Current & Voltage Registers ( I RMS , V RMS ). . . . . . . . . . . . . . . . . . 286.1.9 Epsilon Register ( ε ). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 286.1.10 Power Offset Register ( P off ). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 296.1.11 Status Register and Mask Register ( Status , Mask ). . . . . . . . . . . . . . . 296.1.12 Current and Voltage AC Offset Register ( V ACoff , I ACoff ). . . . . . . . . . . 306.1.13 Operational Mode Register ( Mode ). . . . . . . . . . . . . . . . . . . . . . . . . . . . 306.1.14 Temperature Register ( T ) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 316.1.15 Average and Instantaneous Reactive Power Register ( Q AVG , Q ) . . . . 316.1.16 Peak Current and Peak Voltage Register ( I peak , V peak ). . . . . . . . . . . . 316.1.17 Reactive Power Register ( Q Trig ). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 326.1.18 Power Factor Register ( PF ) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 326.1.19 Apparent Power Register ( S ) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 326.1.20 Control Register ( Ctrl ). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 336.1.21 Harmonic Active Power Register ( P H ) . . . . . . . . . . . . . . . . . . . . . . . . . 336.1.22 Fundamental Active Power Register ( P F ) . . . . . . . . . . . . . . . . . . . . . . 336.1.23 Fundamental Reactive Power Register ( Q H ) . . . . . . . . . . . . . . . . . . . . 346.1.24 Page Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 346.2 Page 1 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 346.2.1 Temperature Gain Register ( T Gain ). . . . . . . . . . . . . . . . . . . . . . . . . . . . . 346.2.2 Temperature Offset Register ( T Off ). . . . . . . . . . . . . . . . . . . . . . . . . . . . . 346.3 Page 3 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 356.3.1 Voltage Sag and Current Fault Duration Registers( VSAG Duration , ISAG Duration ) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 356.3.2 Voltage Sag and Current Fault Level Registers( VSAG Level , ISAG Level ) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35 7. System Calibration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 367.1 Channel Offset and Gain Calibration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 367.1.1 Calibration Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 367.1.1.1 Duration of Calibration Sequence . . . . . . . . . . . . . . . . . . . . . 367.1.2 Offset Calibration Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 367.1.2.1 DC Offset Calibration Sequence . . . . . . . . . . . . . . . . . . . . . . 367.1.2.2 AC Offset Calibration Sequence . . . . . . . . . . . . . . . . . . . . . . 377.1.3 Gain Calibration Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 377.1.3.1 AC Gain Calibration Sequence . . . . . . . . . . . . . . . . . . . . . . . 377.1.3.2 DC Gain Calibration Sequence . . . . . . . . . . . . . . . . . . . . . . . 387.1.4 Order of Calibration Sequences . . . . . . . . . . . . . . . . . . . . . . . . . . 387.2 Phase Compensation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 387.3 Active Power Offset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 388. Auto-boot Mode Using E2PROM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 398.1 Auto-boot Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 398.2 Auto-boot Data for E2PROM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 398.3 Which E2PROMs Can Be Used? . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 399. Basic Application Circuits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4010. Package Dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4311. Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4412. Environmental, Manufacturing, & Handling Information . . . . . . . . . . . . . . . . . 4413. Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44LIST OF FIGURESFigure 1. CS5463 Read and Write Timing Diagrams (12)Figure 2. Timing Diagram for E1, E2 and E3 (13)Figure 3. Data Measurement Flow Diagram (14)Figure 4. Power Calculation Flow (15)Figure 5. Active and Reactive energy pulse outputs (17)Figure 6. Apparent energy pulse outputs (18)Figure 7. Voltage Channel Sign Pulse outputs (18)Figure 8. PFMON output to pin E3 (19)Figure 9. Sag and Fault Detect (19)Figure 10. Oscillator Connection (20)Figure 11. CS5463 Memory Map (22)Figure 12. Calibration Data Flow (36)Figure 13. System Calibration of Offset (36)Figure 14. System Calibration of Gain (37)Figure 15. Example of AC Gain Calibration (37)Figure 16. Example of AC Gain Calibration (37)Figure 17. Typical Interface of E2PROM to CS5463 (39)Figure 18. Typical Connection Diagram (Single-phase, 2-wire – Direct Connect to Power Line)40 Figure 20. Typical Connection Diagram (Single-phase, 3-wire) (41)Figure 19. Typical Connection Diagram (Single-phase, 2-wire – Isolated from Power Line) (41)Figure 21. Typical Connection Diagram (Single-phase, 3-wire – No Neutral Available) (42)LIST OF TABLESTable 1. Current Channel PGA Setting . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16 Table 2. E2 Pin Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1717 Table 4. Interrupt Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 211.OVERVIEWThe CS5463 is a CMOS monolithic power measurement device with a computation engine and an ener-gy-to-frequency pulse output. The CS5463 combines a programmable gain amplifier, two ∆Σ Ana-log-to-Digital Converters (ADCs), system calibration and a computation engine on a single chip.The CS5463 is designed for power measurement applications and is optimized to interface to a current sense resistor or transformer for current measurement, and to a resistive divider or potential transformer for voltage measurement. The current channel provides programmable gains to accommodate various in-put levels from a multitude of sensing elements. With single +5V supply on VA+/AGND, both of the CS5463’s input channels can accommodate common mode plus signal levels between (AGND - 0.25V) and VA+.The CS5463 also is equipped with a computation engine that calculates instantaneous power, I RMS, V RMS, apparent power, active (real) power, reactive power, harmonic active power, active and reactive fundamental power, and power factor. The CS5463 additional features include line frequency, current and voltage sag detection, zero-cross detection, positive-only accumulation mode, and three programmable pulse output pins. To facilitate communication to a microprocessor, the CS5463 includes a simple three-wire serial interface which is SPI™ and Microwire™ compatible. The CS5463 provides three out-puts for energy registration. E1, E2 and E3 are designed to interface to a microprocessor.2. PIN DESCRIPTION Clock GeneratorCrystal Out Crystal In 1,24XOUT, XIN - The output and input of an inverting amplifier. Oscillation occurs when connected toa crystal, providing an on-chip system clock. Alternatively, an external clock can be supplied tothe XIN pin to provide the system clock for the device.CPU Clock Output2CPUCLK - Output of on-chip oscillator which can drive one standard CMOS load.Control Pins and Serial Data I/OSerial Clock Input5SCLK - A Schmitt-Trigger input pin. Clocks data from the SDI pin into the receive buffer and outof the transmit buffer onto the SDO pin when CS is low.Serial Data Output6SDO -Serial port data output pin.SDO is forced into a high-impedance state when CS is high. Chip Select7CS - Low, activates the serial port interface.Mode Select8MODE - High, enables the “auto-boot” mode. The mode pin has an internal pull-down resistor. Energy Output18,21,22E3,E1, E2 - Active-low pulses with an output frequency proportional to the selected power. Con-figurable outputs for active, apparent, and reactive power, negative energy indication, zero crossdetection, and power failure monitoring. E1, E2, E3 outputs are configured in the OperationalModes Register.Reset19RESET - A Schmitt-Trigger input pin. Low activates Reset, all internal registers (some of whichdrive output pins) are set to their default states.Interrupt20INT - Low, indicates that an enabled event has occurred.Serial Data Input23SDI - Serial port data input pin. Data will be input at a rate determined by SCLK.Analog Inputs/OutputsDifferential Voltage Inputs9,10VIN+, VIN- - Differential analog input pins for the voltage channel.Differential Current Inputs15,16IIN+, IIN- - Differential analog input pins for the current channel.Voltage Reference Output11VREFOUT - The on-chip voltage reference output. The voltage reference has a nominal magni-tude of 2.5V and is referenced to the AGND pin on the converter.Voltage Reference Input12VREFIN - The input to this pin establishes the voltage reference for the on-chip modulator. Power Supply ConnectionsPositive Digital Supply3VD+ - The positive digital supply.Digital Ground4DGND - Digital Ground.Positive Analog Supply14VA+ - The positive analog supply.Analog Ground13AGND - Analog ground.Power Fail Monitor 17PFMON - The power fail monitor pin monitors the analog supply. If the analog supply does notmeet or falls below PFMON’s voltage threshold, a Low-supply Detect (LSD) event is set in thestatus register.3.CHARACTERISTICS & SPECIFICATIONSRECOMMENDED OPERATING CONDITIONSANALOG CHARACTERISTICS•Min / Max characteristics and specifications are guaranteed over all Operating Conditions.•Typical characteristics and specifications are measured at nominal supply voltages and TA = 25°C.•VA+ = VD+ = 5V ±5%; AGND = DGND = 0V; VREFIN = +2.5V. All voltages with respect to 0V.•MCLK = 4.096MHz.Notes: 1.Applies when the HPF option is enabled.2.Applies when the line frequency is equal to the product of the Output Word Rate (OWR) and the valueof epsilon (ε).ParameterSymbol Min Typ MaxUnit Positive Digital Power Supply VD+ 3.135 5.0 5.25V Positive Analog Power Supply VA+ 4.75 5.0 5.25V Voltage ReferenceVREFIN - 2.5-V Specified Temperature RangeT A -40-+85°CParameterSymbol Min Typ Max UnitAccuracyActive Power All Gain Ranges(Note 1)Input Range 0.1% - 100%P Active -±0.1-%Average Reactive Power All Gain Ranges(Note 1 and 2)Input Range 0.1% - 100%Q Avg -±0.2-%Power Factor All Gain Ranges(Note 1 and 2)Input Range 1.0% - 100%Input Range 0.1% - 1.0%PF--±0.2±0.27--%%Current RMS All Gain Ranges(Note 1)Input Range 1.0% - 100%Input Range 0.1% - 1.0%I RMS--±0.1±0.17--%%%Voltage RMS All Gain Ranges(Note 1)Input Range 5% - 100%V RMS-±0.1-%Analog Inputs (Both Channels)Common Mode Rejection (DC,50,60Hz)CMRR80--dB Common Mode + SignalAll Gain Ranges-0.25-VA+V Analog Inputs (Current Channel)Differential Input Range (Gain = 10)[(IIN+) - (IIN-)](Gain = 50)IIN --500100--mV P-P mV P-P Total Harmonic Distortion(Gain = 50)THD 8094-dB Crosstalk with Voltage Channel at Full Scale (50, 60Hz)--115-dB Input Capacitance (Gain = 10)(Gain = 50)IC --3252--pF pF Effective Input Impedance EII 30--k ΩNoise (Referred to Input)(Gain = 10)(Gain = 50)N I ----22.54.5µV rms µV rms Offset Drift (Without the High Pass Filter)OD - 4.0-µV/°C Gain Error(Note 3)GE-±0.4%ANALOG CHARACTERISTICS (Continued)Notes: 3.Applies before system calibration.4.All outputs unloaded. All inputs CMOS level.5.Definition for PSRR: VREFIN tied to VREFOUT, VA+ = VD+ = 5V, a 150mV (zero-to-peak) (60Hz)sinewave is imposed onto the +5V DC supply voltage at VA+ and VD+ pins. The “+” and “-” input pins of both input channels are shorted to AGND. Then the CS5463 is commanded to continuous conversion acquisition mode, and digital output data is collected for the channel under test. The (zero-to-peak) value of the digital sinusoidal output signal is determined, and this value is converted into the(zero-to-peak) value of the sinusoidal voltage (measured in mV) that would need to be applied at the channel’s inputs, in order to cause the same digital sinusoidal output. This voltage is then defined as Veq. PSRR is then (in dB):6.When voltage level on PFMON is sagging, and LSD bit is at 0, the voltage at which LSD bit is set to 1.7.If the LSD bit has been set to 1 (because PFMON voltage fell below PMLO), this is the voltage level onPFMON at which the LSD bit can be permanently reset back to 0.ParameterSymbol MinTyp Max Unit Analog Inputs (Voltage Channel)Differential Input Range [(VIN+) - (VIN-)]VIN - 500-mV P-P Total Harmonic DistortionTHD 6575-dB Crosstalk with Current Channel at Full Scale (50, 60Hz)--70-dB Input Capacitance All Gain Ranges IC -0.2-pF Effective Input Impedance EII 2--M ΩNoise (Referred to Input)N V --140µV rms Offset Drift (Without the High Pass Filter)OD -16.0-µV/°C Gain Error(Note 3)GE -±3.0%Temperature ChannelTemperature AccuracyT -±5-°C Power SuppliesPower Supply Currents (Active State)I A+I D+ (VA+ = VD+ = 5V)I D+ (VA+ = 5V, VD+ = 3.3V)PSCA PSCD PSCD --- 1.32.91.7---mA mA mA Power Consumption Active State (VA+ = VD+ = 5V)(Note 4) Active State (VA+ = 5V, VD+ = 3.3V)Stand-by State Sleep StatePC----2111.68102917.5--mW mW mW µW Power Supply Rejection Ratio (50, 60Hz)(Note 5)Voltage ChannelCurrent ChannelPSRR 4570-6575---dB dB PFMON Low-voltage Trigger Threshold (Note 6)PMLO2.3 2.45-V PFMON High-voltage Power-on Trip Point (Note 7)PMHI- 2.552.7VPSRR 20150V eq---------log ⋅=VOLTAGE REFERENCENotes:8.The voltage at VREFOUT is measured across the temperature range. From these measurements the9.Specified at maximum recommended output of 1µA, source or sink.DIGITAL CHARACTERISTICS•Min / Max characteristics and specifications are guaranteed over all Operating Conditions.•Typical characteristics and specifications are measured at nominal supply voltages and TA = 25°C.•VA+ = VD+ = 5V ±5%; AGND = DGND = 0V. All voltages with respect to 0V.•MCLK = 4.096MHz.ParameterSymbol Min Typ Max Unit Reference OutputOutput VoltageVREFOUT+2.4+2.5+2.6V Temperature Coefficient (Note 8)TC VREF -2560ppm/°C Load Regulation(Note 9)∆V R -610mV Reference InputInput Voltage Range VREFIN+2.4+2.5+2.6V Input Capacitance -4-pF Input CVF Current-25-nAParameterSymbol MinTypMax Unit Master Clock CharacteristicsMaster Clock Frequency Internal Gate Oscillator (Note 11)MCLK 2.5 4.09620MHz Master Clock Duty Cycle 40-60%CPUCLK Duty Cycle(Note 12 and 13)40-60%Filter CharacteristicsPhase Compensation Range (Voltage Channel, 60Hz)-2.8-+2.8°Input Sampling RateDCLK = MCLK/K -DCLK/8-Hz Digital Filter Output Word Rate (Both Channels)OWR-DCLK/1024-Hz High-pass Filter Corner Frequency-3dB -0.5-Hz Full-scale DC Calibration Range (Referred to Input )(Note 14)FSCR 25-100%F.S.Channel-to-channel Time-shift Error(Note 15)1.0µsInput/Output CharacteristicsHigh-level Input VoltageAll Pins Except XIN and SCLK and RESETXINSCLK and RESET V IH0.6 VD+(VD+) - 0.50.8 VD+------V V V Low-level Input Voltage (VD =5V)All Pins Except XIN and SCLK and RESETXINSCLK and RESETV IL------0.81.50.2 VD+V V VNotes:10.All measurements performed under static conditions.11. If a crystal is used, then XIN frequency must remain between 2.5MHz -5.0MHz. If an externaloscillator is used, XIN frequency range is 2.5MHz -20MHz, but K must be set so that MCLK is between 2.5MHz -5.0MHz.12.If external MCLK is used, then the duty cycle must be between 45% and 55% to maintain thisspecification.13.The frequency of CPUCLK is equal to MCLK.14.The minimum FSCR is limited by the maximum allowed gain register value. The maximum FSCR islimited by the full-scale signal applied to the channel input.15.Configuration Register bits PC[6:0] are set to “0000000”.Low-level Input Voltage (VD =3.3V)All Pins Except XIN and SCLK and RESETXINSCLK and RESET V IL------0.480.30.2 VD+V V V High-level Output Voltage I out = +5mA V OH (VD+) - 1.0--V Low-level Output Voltage I out = -5mAV OL --0.4V Input Leakage Current I in -±1±10µA 3-state Leakage Current I OZ --±10µA Digital Output Pin CapacitanceC out-5-pFParameterSymbol Min Typ Max UnitSWITCHING CHARACTERISTICS• Min / Max characteristics and specifications are guaranteed over all Operating Conditions.•Typical characteristics and specifications are measured at nominal supply voltages and TA = 25°C.•VA+ = 5V ±5% VD+ = 3.3V ±5% or 5V ±5%; AGND = DGND = 0V. All voltages with respect to 0V.•Logic Levels: Logic 0 = 0V, Logic 1 = VD+.Notes:16.Specified using 10% and 90% points on waveform of interest. Output loaded with 50pF.17.Oscillator start-up time varies with crystal parameters. This specification does not apply when using anexternal clock source.ParameterSymbol Min Typ Max Unit Rise Times Any Digital Input Except SCLK(Note 16)SCLKAny Digital Output t rise-----50 1.0100-µs µs ns Fall Times Any Digital Input Except SCLK(Note 16)SCLKAny Digital Output t fall-----50 1.0100-µs µs ns Start-upOscillator Start-up TimeXTAL = 4.096MHz (Note 17)t ost -60-ms Serial Port TimingSerial Clock Frequency SCLK--2MHz Serial ClockPulse Width High Pulse Width Lowt 1t 2200200----ns ns SDI TimingCS Falling to SCLK Risingt 350--ns Data Set-up Time Prior to SCLK Rising t 450--ns Data Hold Time After SCLK Risingt 5100--ns SDO TimingCS Falling to SDI Drivingt 6-2050ns SCLK Falling to New Data Bit (hold time)t 7-2050ns CS Rising to SDO Hi-Zt 8-2050ns Auto-Boot TimingSerial ClockPulse Width Low Pulse Width Hight 9t 1088MCLK MCLK MODE setup time to RESET Rising t 1150ns RESET rising to CS falling t 1248MCLK CS falling to SCLK rising t 131008MCLK SCLK falling to CS risingt 1416MCLK CS rising to driving MODE low (to end auto-boot sequence).t 1550ns SDO guaranteed setup time to SCLK risingt 16100nsSDI Write Timing (Not to Scale)SDO Read Timing (Not to Scale)Figure 1. CS5463 Read and Write Timing DiagramsSWITCHING CHARACTERISTICS (Continued)Notes:18.Pulse output timing is specified at MCLK =4.096MHz, E2MODE =0 and E3MODE1:0=0. Refer toSection 5.5 Energy Pulse Output on page 17 for more information on pulse output pins.19.Timing is proportional to the frequency of MCLK.ABSOLUTE MAXIMUM RATINGSWARNING:Operation at or beyond these limits may result in permanent damage to the device.Normal operation is not guaranteed at these extremes .Notes:20.VA+ and AGND must satisfy [(VA+) - (AGND)] ≤ + 6.0V.21.VD+ and AGND must satisfy [(VD+) - (AGND)] ≤ + 6.0V.22.Applies to all pins including continuous over-voltage conditions at the analog input pins.23.Transient current of up to 100mA will not cause SCR latch-up.24.Maximum DC input current for a power supply pin is ±50mA.25.Total power dissipation, including all input currents and output currents.ParameterSymbol Min TypMaxUnitE1, E2 and E3 Timing (Note 18 and 19)Period t period 250--µs Pulse Widtht pw 244--µs Rising Edge to Falling Edget 36--µs E2 Setup to E1 and/or E3 Falling Edge t 4 1.5--µs E1 Falling Edge to E3 Falling Edget 5248--µsParameterSymbol Min Typ Max Unit DC Power Supplies(Notes 20 and 21)Positive Digital Positive Analog VD+VA+-0.3-0.3--+6.0+6.0V V Input Current, Any Pin Except Supplies (Notes 22, 23, 24)I IN --±10mA Output Current, Any Pin Except VREFOUTI OUT --100mA Power Dissipation (Note 25)P D --500mW Analog Input Voltage All Analog Pins V INA - 0.3-(VA+) + 0.3V Digital Input VoltageAll Digital PinsV IND -0.3-(VD+) + 0.3V Ambient Operating Temperature T A -40-85°C Storage TemperatureT stg-65-150°CFigure 2. Timing Diagram for E1, E2 and E3。

一款多功能电能计量芯片简介(CS5463)

CS5463的分析及应用

汇报人:李贵玉 汇报时间:2017/9/28

CONTENTS

1 CS5463芯片概述 2 引脚及内部功能结构 3 工作原理与应用特点 4 典型应用电路 5 国内外产品简介 6 小结

什么是CS5463?

SSOP ( Shrink SmallOutline Package):即窄间 距小外型塑封。

(Σ-ΔADC)、三个数字串行接口;CS5467 可为并发的两相测量提供两个电流通 道和两个电压通道,并有系统电平校准、温度感应、电压骤降、电流错误监测以 及相位补偿等特性。

国内生产电子电度表芯片的厂商主要有复旦微电子、上海贝岭、珠海 炬力等几家。

公司名称

国家/地区

主要(最新)芯片

复旦微电子股份有限公司

微处理器、片内闪存、LCD 驱动器、实时时钟和智能电池管理电路结合在一起, 允许电能表保持时间、检测温度变化、读出 LCD 数据并且完成其它的重要系统功 能。另外,还支持远程抄表系统、计时收费以及卸负载(当电源超载时切断某条 输电线的电流)等高级服务。

Cirrus Logic的电能芯片: CS5467 集成了四个 Sigma-流器接口

N

Qn

平均无功功率:QAVg

n1

N

单电源地参考信号 片内2.5V参考电压(最大温漂25ppm/OC)

S P 三角无功功率:QTr lg

2 2 Active

内带电源监视器

简单的三线数字串行接口

可以从串行EEPROM进行“自引导”,不需要微控制器

图1 CS5463引脚排列图

1脚XOUT: 2脚CPUCLK: 3脚VD+: 4脚DGND: 5脚SCLK: 6脚SDO: 7脚CS: 8脚MODE: 9脚VIN+: 10脚VIN-: 11脚VREFOUT: 12脚VREFIN:

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

CONTENTS

1 2 3 4 5 6

CS5463芯片概述

引脚及内部功能结构

工作原理与应用特点

典型应用电路

国内外产品简介

小结

Typical Connection Diagram (Single-phase, 2-wire – Direct Connect to Power Line)

Typical Connection Diagram (Single-phase, 2-wire – Isolated from Power Line)

优化的分流器接口

单电源地参考信号 片内2.5V参考电压(最大温漂25ppm/OC) 内带电源监视器 简单的三线数字串行接口

平均无功功率: QAVg

Q

n 1

N

n

N

三角无功功率: QTr lg

S

2

P Active

2

可以从串行EEPROM进行“自引导”,不需要微控制器

小结

工作原理

大电压 信号 电 压 互 感 器 小电压 信号

电 压 通 道

10倍增益 放大器

二阶 ∆∑调 制器

数 字 滤 波 器

功率计算 引擎

串行 口

MC U

大电流 信号

电 流 互 感 器

小电压 信号

电 流 通 道

PGA

四阶 ∆∑调 制器

数 字 滤 波 器

电能/ 频率 转换

步进 电机

应用特性

电能数据线性度:在1000:1动态范围内线性度为 0.1% 两种无功计算方式 功耗<12mW

可编程增益放大器 集成了两个A/D转换器 高通数字滤波器

片上温度传感器,有助于设 计师调整温度漂移误差

差分输入电压满量程为 250mV

图2 CS5463内部结构框图

CONTENTS

1 2 3 4 5 6

CS5463芯片概述

引脚及内部功能结构

工作原理与应用特点

典型应用电路

国内外产品简介

由美国Cirrus Logic 公司推出,采用24 脚SSOP封装形式。

多功能

CS5463

高精度

电能测量芯片

哦,原来是这样!

该芯片不仅延续了广受欢迎的CS5460A的功能,与其引脚完全兼

容,而且新增了如下等测量功能。

• 有功功率 • 无功功率 • 功率因数 • 电能脉冲转换

• 线路频率 • 视在功率 • 系统校准和相位补偿 • 温度传感器

单的电路结构,所需的单片机资源也少,因此可以缩短开发时间,大大提高了仪

器的性能指标和性价比。从某宝上查询到芯片的价格从2元到10左右价格不等, 考虑可能有二手拆机芯片和原装新品差价。具体如下图所示。

THANKS

引脚及内部功能结构

工作原理与应用特点

典型应用电路

国内外产品简介

小结

目前,国际上电子式电表中的电能计量芯片市场一直由 ADI、 Cirrus Logic、SAMES等国际公司占据如表1所示。

公司名称 国家/地区 主要(最新)芯片

ADI

美国

(ADE71xx、ADE75xx)

Cirrus Logic

美国

小结

1脚XOUT: 2脚CPUCLK: 3脚VD+: 4脚DGND: 5脚SCLK: 6脚SDO: 7脚CS:

晶体振荡器输出端(4.096MHz) CPU时钟输出端 数字电源正极(3.3V-5V) 数字地 串行时钟输入端 串行数据输出端 片选

8脚MODE:

9脚VIN+:

模式选择

差分电压正输入端 差分电压负输入端 参考电压输出端 参考电压输入端

模拟电源:模拟电源发出的是模拟信号。 数字电源与模拟电源的区别:主要是控制与通信部分。在简单易用、参数变更要

求不多的应用场合,模拟电源产品更具优势,因为其应用的针对性可以通过硬件固话来实现。 而在可控因素较多、实时反应速度更快、需要多个模拟系统电源管理的、复杂的高性能系统 应用中,数字电源则更具优势。

上海贝岭股份有限公司

中国上海

珠海炬力集成电路设计股份 有限公司

中国珠海

CONTENTS

1 2 3 4 5 6

CS5463芯片概述

引脚及内部功能结构

工作原理与应用特点

典型应用电路

国内外产品简介

小结

通过上述分析,作为测量电量原始信号的核心器件,并与目前比较流行的芯 片如AD7750、AD7755、CS5460A等相比,CS5463有测量变化多、测量数据准 确、抗干扰性能好等优点。由于能提高测量数据的准确性,该芯片为新一代数字 电表的设计提供了很好的选择性。它不仅可以增强仪表的功能,而且具有较为简

SA2002H SA4101A/4104 A、B/4106A

SA2007H

SA9605A SA2005M/4301 A/9105G

SA2007M

SA2002P

SA2007P

校准和设置存储在外部EEPROM中,直接驱动机 电式计度器,快速脉冲输出/LED校准输出,应用 于基于MCU的电能表

SA9904B SPI输出,电压有效值、频率、有功、无功测量, 应用于基于MCU的电能表

Typical Connection Diagram (Single-phase, 3-wire)

Typical Connection Diagram (Single-phase, 3-wire – No Neutral Available)

CONTENTS

1 2 3 4 5 6

CS5463芯片概述

输电线的电流)等高级服务。

Cirrus Logic的电能芯片: CS5467 集成了四个 Sigma-Delta 模数转换器

(Σ-ΔADC)、三个数字串行接口;CS5467 可为并发的两相测量提供两个电流通

道和两个电压通道,并有系统电平校准、温度感应、电压骤降、电流错误监测以

及相位补偿等特性。

国内生产电子电度表芯片的厂商主要有复旦微电子、上海贝岭、珠海 炬力等几家。

SA9903B

表2 SAMES公司芯片情况表

ADI的电能芯片: ADE7100 和 ADE7500 电能表系统芯片把电能测量内核与

微处理器、片内闪存、LCD 驱动器、实时时钟和智能电池管理电路结合在一起, 允许电能表保持时间、检测温度变化、读出 LCD 数据并且完成其它的重要系统功

能。另外,还支持远程抄表系统、计时收费以及卸负载(当电源超载时切断某条

电源掉电检测输出

高频电能脉冲输出 复位输入 中断输出 电能脉冲输出1端 电能脉冲输出2端 串行数据输入端 晶体振荡器输入端

图1 CS5463引脚排列图

22脚E2: 23脚SDI: 24脚XIN:

PS:

数字电源:是以DSP或者MCU为核心,将数字电源驱动器、PWM控制器等作为

控制对象,能实现控制、管理和检测功能的电源产品。

图1 CS5463引脚排列图

10脚VIN-: 11脚VREFOUT: 12脚VREFIN:

13脚AGND:

模拟地

14脚 VA+:

15脚IIN-: 16脚IIN+:

模拟电源正极(+5V)

差分电流负输入端 差分电流正输入端

17脚PFMON:

18脚E3: 19脚RESET: 20脚INT: 21脚E1:

CS5451A、5461A、5462、5463、5464、5466、5467

SAMES

南非

具体见表2

表1 国外主要的电能芯片公司简介

SAMES公司的相关产品情况如表2所示。

单相单电流输入 单相双电流输入 三相 应用 快速脉冲输出,应用于基于MCU的电能表 直接驱动机电式计度器,快速脉冲输出/LED校准 输出,应用于基于MCU的电能表 直接驱动机电式计度器,LED校准输出,应用于基 于单芯片的电能表

PS:在交流电路中

有功功率

电阻元件上所消耗的功率叫做有功 功率。

无功功率

电感或电容元件与电源之间进行能 量交换的振幅值叫做无功功率。

视在功率

电压与电流的直接乘积叫做视在功 率。

CONTENTS

1 2 3 4 5 6

CS5463芯片概述

引脚及内部功能结构

工作原理与应用特点

典型应用电路

国内外产品简介

公司名称

国家/地区

主要(最新)芯片

复旦微电子股份有限公司

中国上海

FM7755、FM230x 系列 有单相的BL0930、BL0932B、BL6503、BL6501,三相 的 BL0952、BL0962,和三相四线的 BL6513、BL6514 。 ATT7021、ATT7022A、ATT7022B、ATT7023、 ATT7026A、ATT7028A、ATT7030A 等

CS5463的分析及应用

汇报人:李贵玉

汇报时间:2017/9/28

信息工程学院E211实验室

CONTENTS

1 2 3 4 5 6

CS5463芯片概述

引脚及内部功能结构

工作原理与应用特点

典型应用电路

国内外产品简介

小结

什么是CS5463?

SSOP ( Shrink SmallOutline Package ) : 即窄间 距小外型塑封。