基于CPLD的高速时钟电路论文

基于CPLD的多功能数字钟设计

说明书目录1 前言 (1)2 总体方案设计 (2)2.1 方案论述 (2)2.2 设计方式 (3)3 单元模块电路设计 (4)3.1时间显示电路模块设计 (4)3.2按键及指示灯电路模块的设计 (6)3.3蜂鸣器及有源晶振电路的设计 (8)3.4 CPLD编程下载电路的设计 (9)3.5电源电路电路的设计 (10)3.6 EPM7128SLC84器件介绍 (11)4 CPLD 编程设计 (12)4.1系统信号的定义及顶层模块 (12)4.2 时钟节拍产生模块 (13)4.3模式选择功能模块 (15)4.4快速时间设置功能模块 (17)4.5秒、分、时计时与时间调整模块 (17)4.6闹铃时间设置模块 (19)4.7闹铃与整点报时模块 (20)4.8 7段显示译码模块 (21)4.9 LED显示模块 (23)5 系统功能及功能仿真 (25)5.1系统功能 (25)5.2功能仿真 (26)5.2.1 时钟节拍产生模块的仿真波形 (26)5.2.2 模式选择功能模块的仿真波形 (28)5.2.3 闹铃设置功能模块的仿真波形 (29)5.2.4 7段译码功能模块的仿真波形 (30)5.2.5 LED显示功能模块的仿真波形 (31)5.2.6 系统总体功能仿真波形 (32)6 设计总结 (33)7 参考文献 (34)附录:基于CPLD的多功能数字钟电路图 (35)说明书1 前言我们已经进入了数字化和信息化的时代,其特点是各种数字产品的广泛应用。

现代数字产品在性能提高、复杂度增大的同时,其更新换代的步伐也越来越快,实现这种进步的因素在于生产制造技术和电子设计技术的进步。

生产制造技术以微细加工技术为代表,目前已进展到深亚微米阶段,可以在几平方厘米的芯片上集成数千万个晶体管。

PLD器件和EDA技术的出现,改变了这种传统的设计思路,使人们可以立足于PLD 芯片来实现各种不同的功能,新的设计方法能够由设计者自己定义器件内部逻辑和管脚,将原来由电路板设计完成的工作大部分放在芯片的设计中进行。

基于CPLD的1/100秒计时器电路

基于CPLD的1/100秒计时器电路本设计为基于CPLD的1/100秒计时器电路。

计时器能实现0.01s~59.99s 的计时功能,计时误差≤ 0.01s,具有启、停和清零功能,计时数据采用七段数码管显示。

所有电路采用美国ALTERA公司的EPM7128SLC84-15芯片实现,使外围电路简单,性能可靠,特别是该芯片具有现场可编程功能,使修改设计简单。

在软件设计中使用了功能按键消抖技术,使功能操作准确无误。

标签:CPLD VHDL 计时器一、引言1/100s计时器常用于体育竞赛及各种要求有较高精确定时的领域。

本文设计的1/100s计时器具有如下功能:1.分、秒、1/100秒计时功能;2.具有分、秒、1/100秒显示功能;3.具有启停功能;4.具有复位功能。

整个系统的设计借助于VHDL,在EDA设计工具maxplus 下进行仿真,得到了良好的结果。

由于采用模块化的设计思想,使设计变得简单、方便、灵活性强。

二、设计方案分析如图1所示,为1/100s计时器的整体方框图。

包括四部分组成:计时控制芯片(cpld)、复位及启停开关、四位数码管、时钟。

根据计时器的功能特点,具体实现时可分为五个子模块:键输入模块、时钟产生模块、定时计数数模块、控制模块、四位数码管显示驱动模块。

各模块的功能独立,可扩充性强,具有再次开发的潜力。

各模块的关系如图2所示。

三、模块设计1.键输入模块(keyin)键输入模块(keyin)即键扫描电路,25HZ键扫描脉冲对按键扫描,产生启/停单脉冲(stst)和清零单脉冲(res),并具有消抖功能。

键扫描电路工作原理如下(以产生清零单脉冲res为例,启/停单脉冲stst与此相同):IF(keyclk’EVENT AND keyclk=‘0’)THENres1<=res0;res0<=reset_sw;stst1<=stst0;stst0<=start_stop_sw;END IF;2.时钟产生模块(clkgen)时钟产生模块是一个分频电路,对1000HZ时钟脉冲(clk)分频产生100HZ的计时脉冲(cntclk)和25HZ的键扫描脉冲(keyclk)。

#基于CPLD的数字时钟设计

学号0803021116分数电子设计自动化课程设计报告[基于CPLD的数字时钟设计]系部:信息工程系班级: 08电信(1)班姓名:指导教师:湖北轻工职业技术学院完成日期:2010 年 6 月 18日目录引言 (2)一VHDL的概述 (2)二设计方案和分析 (3)第一章模块设计 (4)一设计要求及目的 (4)1.1 要求 (4)1.2 目的 (5)二程序设计及模块说明和仿真 (5)2.1 二十四进制 (5)2.2 六十进制 (7)2.3 扫描电路 (9)2.4 整点报时 (12)第二章总体设计效果 (13)一电路仿真 (13) (13)二、实验结果 (13)总结 (14)一心得体会 (14)引言一VHDL的概述硬件描述语言(hardware description language,HDL)是电子系统硬件行为描述、结构描述、数据流描述的语言。

目前,利用硬件描述语言可以进行数字电子系统的设计。

随着研究的深入,利用硬件描述语言进行模拟电子系统设计或混合电子系统设计也正在探索中。

国外硬件描述语言种类很多,有的从Pascal发展而来,也有一些从C语言发展而来。

有些HDL成为IEEE标准,但大部分是企业标准。

VHDL来源于美国军方,其他的硬件描述语言则多来源于民间公司。

可谓百家争鸣,百花齐放。

这些不同的语言传播到国内,同样也引起了不同的影响。

在我国比较有影响的有两种硬件描述语言:VHDL语言和Verilog HDL语言。

这两种语言已成为IEEE标准语言。

电子设计自动化(electronic design automation,EDA)技术的理论基础、设计工具、设计器件应是这样的关系:设计师用硬件描述语言HDL描绘出硬件的结构或硬件的行为,再用设计工具将这些描述综合映射成和半导体工艺有关的硬件配置文件,半导体器件FPGA则是这些硬件配置文件的载体。

当这些FPGA器件加载、配置上不同的文件时,这个器件便具有了相应的功能。

毕业设计(论文)-基于cpld秒表计时器设计[管理资料]

![毕业设计(论文)-基于cpld秒表计时器设计[管理资料]](https://img.taocdn.com/s3/m/db8ec9b733687e21ae45a9b4.png)

设计题目: 基于CPLD秒表计时器设计院系: 一系专业: 电子科学与技术班级: 0 3 0 6 姓名:指导老师:华中科技大学武昌分校2006年12月18日毕业设计(论文)任务书学生姓名朱林志专业班级电子科学与技术系指导教师乐雄军工作单位武汉理工大学设计(论文)题目:基于CPLD秒表计时器设计设计(论文)主要内容:、实施原理。

、数码显示电路。

要求完成的主要任务:1. 设计精度为1%的秒表数字电路。

2. 设计可调时间的中断装置、数字调节;3. 设计并调试电路。

主要参考文献:,2001年10月.. CPLD原理及应用. 电子工业出版社, 2003年1月.3. 单片机原理及其应用方面的资料4.电路设计方面的资料。

指导教师签名系主任签名院长签名(章)_____________开题报告本次设计目的主要分为以下几点:;;;,增强实际动手能力。

计时器在许多领域中均得到普遍应用,诸如在体育比赛、公共汽车到站时间统计中需进行计时和统计。

现今的计时器通常只能通过启/停按键实现断点计时的功能,即通过启/停按键来记录一段时间。

这种计时器查看的时间只能为计时结束时刻。

实际的应用中往往需要在不影响正常计时的基础上,能查看记录过程中的某些点的时间,即中途计时,如记录长跑运动员跑每圈所用时间,以便了解其各阶段的情况。

本文即针对此问题,设计了一种能通过按键方式查看记录过程中任一时刻值的计时器。

这种计时器在查看中间值时不会影响整个记录过程,并且能把相应数据送入存储模块及显示模块,以便查看。

整个系统的设计借助于VHDL和数字逻辑电路,在EDA设计工具MaxplusII下进行仿真,得到了良好的结果。

由于采用模块化的设计思想,使设计变得简单、方便、灵活性强。

根据计时器的功能特点,具体实现时可划分为6个子模块:键输入模块,时钟分频模块,控制模块,秒表计时模块,计时存储模块和显示模块。

各模块的功能独立,可扩充性强,具有再次开发的潜力。

模块设计:键输入模块:计时器的输入控制为按键方式,由于手动按键,会产生开关簧片反弹引起的电平抖动现象,为保证系统能捕捉到输出脉冲,在每一个开关后面安排一个消抖和同步电路,以并保证每按一键,只形成一个宽度为系统时钟周期的脉冲。

基于CPLD的多功能数字时钟实现

( S 1 S 0 = 0 0 ) 、 M 2 正常显示分秒( S 1 S 0 = 0 1 ) 、 M 3 分钟校时 闪烁( s l s o = 1 0 ) 、 M 4 小 时校时 闪烁 ( S 1 S 0 - l 1 ) ; 模 式切换 信号分两种 : ①数码 管上显 示 小时 和分钟 ②数码管 上显示分钟 和秒 钟 ; 闪烁信号 也分两种 : ①小 时 部分闪烁并校时②分钟部分闪烁并校时。 需要模式切换信号①的模 式 有 M1 、 M 3 、 M 4 , 需要模式切换 信号② 的模式有 M 2 。 使模式切换信号① 为低 电平 : 模式切换 信号②为 高电平 . 那么采用 一定的逻辑 电路便 可 完成高 电平和低 电平的分离 . 获取所需信号 采用 的电路结构为 S 1 与 非 门 连接 然 后 和 s 0相与 得 到 切换 信 号 C 1 .并将 Cl信 号输 出给

2 数 字钟 模 块 实 现

在确定整体 思路基 础后 . 进行模 块化设计 . 采用模块 化设计方 便 进行 局部 调整 . 以及模块的重用 , 便于开发 . 节 省开发流程 对 于该 系 统 划分为以下几个模块去实现 : ①分频 电路② 秒钟 计时 电路③ 时钟计 时电路④ 动态刷新和译 码 显示 电路 ⑤控制 电路⑥防机 械按键抖 动电 路⑦ 闪烁电路⑧ 校时电路⑨ 功能选择 电路 。下面详细介绍控制 电路 、 防机械按 键抖动电路的实现 2 . 1 控 制电路 实现 控制电路是该系统能实现各种模式切换 以及闪烁 的重要部分 控 制 电路是本 系统 的核心电路 . 尽管结构简单但却 有着“ 四两拨千斤 ” 的 作用 。 在控 制电路 中主要输 出模 式切换信号 、 闪烁信号 、 校时信号 。 决 定 了模式 的状态 和是否闪烁以及闪烁小时部分还是分钟部分 本系统 设计 了正常显示小时分钟 、 正常显示分秒 、 分钟校 时闪烁 、 小时校 时闪 烁 这四种状态 . 四种状态 的实现通 过一个状态 机循环 , 即 采 用 模 二 进 制计 数器 。对 应模式 和模二计数器 状态如下 : M1正常显示 小时分钟

基于CPLD的数字时钟设计

CPLD课程学习报告学生姓名:熊军同组者姓名:黄辉CPLD的全称是Complex Programmable Logic Device (即复杂可编程器件),但本次试验所使用的器件并不是CPLD而是FPGA,FPGA的全称是Field Programmable Gate Array (即现场可编程门阵列)。

FPGA与CPLD有很多相似点,它们都是可编程数字逻辑器件,都在时序逻辑电路和组合逻辑电路中有很强的优势。

它们的区别在于,FPGA的容量大、速度慢且不可预测、掉电信息丢失,二CPLD容量小、速度快且有很好的可预测性、掉电信息不丢失。

CAD 的全称是Computer Aided Design(即计算机辅助设计)。

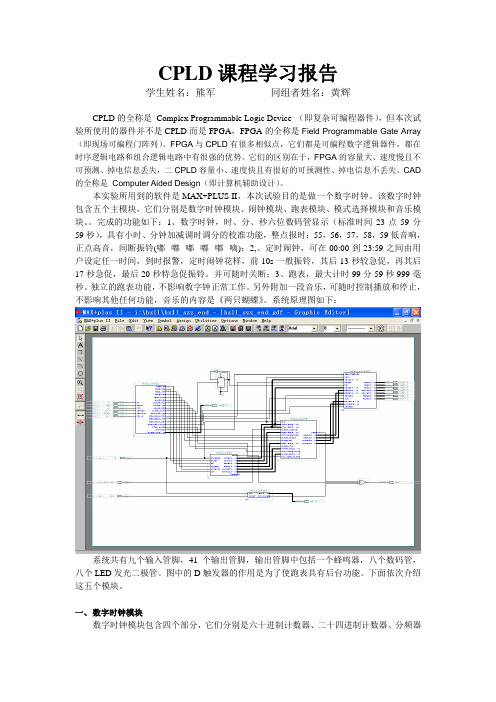

本实验所用到的软件是MAX+PLUS II,本次试验目的是做一个数字时钟。

该数字时钟包含五个主模块,它们分别是数字时钟模块、闹钟模块、跑表模块、模式选择模块和音乐模块。

完成的功能如下:1、数字时钟,时、分、秒六位数码管显示(标准时间23点59分59秒),具有小时、分钟加减调时调分的校准功能,整点报时:55,56,57,58,59低音响,正点高音,间断振铃(嘟--嘟--嘟--嘟--嘟--嘀);2,、定时闹钟,可在00:00到23:59之间由用户设定任一时间,到时报警,定时闹钟花样,前10s一般振铃,其后13秒较急促,再其后17秒急促,最后20秒特急促振铃。

并可随时关断;3、跑表,最大计时99分59秒999毫秒。

独立的跑表功能,不影响数字钟正常工作。

另外附加一段音乐,可随时控制播放和停止,不影响其他任何功能,音乐的内容是《两只蝴蝶》。

系统原理图如下:系统共有九个输入管脚,41个输出管脚,输出管脚中包括一个蜂鸣器,八个数码管,八个LED发光二极管。

图中的D触发器的作用是为了使跑表具有后台功能。

下面依次介绍这五个模块。

一、数字时钟模块数字时钟模块包含四个部分,它们分别是六十进制计数器、二十四进制计数器、分频器和整点报时控制器。

高速数据采集系统中精确时标的cpld实现方法

高速数据采集系统中精确时标的cpld实现方法高速数据采集系统中精确时标的CPLD实现方法陈靖,张承学(武汉大学电气工程学院武汉430072)摘要:本文介绍一种利用复杂可编程逻辑器件给高速数据采集系统中的采集数据贴上精确时间标签的方法,并利用MAX PLUSⅡ开发环境验证设计方案的正确性。

此设计方案已经成功地应用到自行设计的高速数据采集卡中。

关键词:ADuC812;时间标签;CPLD;GPS A method of realizing precise time label in high-speed data acquisition systemChen jing, Zhang Cheng-xue, Liu Yanhua(School of Electrical Engineering, Wuhan University, 430072, Wuhan,China)Abstract: This paper introduces a new method, using Complex Programmable Logic Device to attach a precise time label for sample data in very high-speed sample data system. It has used MAX PLUS II to simulate the function and it has been proved to be accurate. The system has been applied in high-speed data sample board, which has been designed successfully.Key words:ADuC812time laberCPLDglobal positioning system)GPS)0 引言基于GPS的双端行波故障定位系统是利用行波的第一个波头到达线路两端的时间差来计算故障点的位置,由于行波的传播速度非常快(约为光速的98%),这就对线路两端行波波头到达时刻的时间精度要求非常高。

基于高频时钟驱动的CPLD超声相控发射电路仿真设计

Ke y wo r d s : u l t r a s o n i c ; p h a s e d a r r a y ;p h a s e d e l a y ; c o m p l e x p r o g o a mm a b l e l o g i c d e v i c e( C P L D )

Ab s t r a c t : Hi g h — p r e c i s i o n u l t r a s o n i c t r a n s mi s s i o n p h a s e d e l a y i s t h e k e y t e c h n o l o g y i n p h a s e d a r r a y u l t r a s o n i c b e a ms .An u l t r a s o n i c p h a s e - c o n t r o l l e d t r a n s mi s s i o n b a s e d o n t h e CP L D d r i v e d b y 2 5 0 MHz f r e q u e n c y c l o c k w a s d e s i g n e d .T h e p h a s e d l a u n c h r e s o l u t i o n

达到 波束 聚 焦 、 波束 形 成 等 多 种 相 控效 果 。 因此 , 相控延 时是 相控 阵技 术 的核 心 , 是 多 种相 控 阵 效果

目前 相控 发 射 电路 大 多 采 用 较 低 频 率 时 钟 的 可编 程逻 辑器 件 和 L c延迟 线 的结构 来获 得较 高 的 相控 发射 精度 , 但 L c网络 对 元 器 件 一 致 性 和 温 稳

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

关于1756热备问题

在硬件配置时,组态一个就可以了!但是要记住两个机架上的CNBR的开关不能是最小,但是必须一样!有几个要点还是注意一下:

1.AB推荐你CPU机架上的地址最好是最高地址,

即大于任何一个IO站的地址。

所以2个CPU机架上的地址最好设成31,

这样,先上电的CPU为主站,地址为31,后上电的那个为备用站,地址为32。

热备切换时2个CPU会互相交换地址,即任何时候主站都是31,备用站是32。

2.IO从站数量不能少于2个。

IO从站数量小于2,会在热备切换时导致部分IO复位。

原来我们为此可是吃够了苦头。

某高校AB联合实验室。

试验台装置,

2套CPU站组成一套热备冗余系统,为了省成本,只配了一个IO站,

各样IO模块只配了一个。

结果每次在热备切换时都会发生IO数据复位的情况。

后来一看手册,哦,人家早就写了很明白,我们没有注意看而已。

至于为何配置的IO站数量必须大于2,北京的技术支持回复,

美国的技术支持也讲不明白,反正必须>2.

3.热备冗余系统的IO全部都挂在ControlNe网络上,

所以还需要RSNetworx for ControlNet软件,用一下就可以了。

4.跟上位机通讯需要RSLinx。

一般来讲都是用RSLinx来作OPC Server,组太软件作

OPC Client。

RSLinx是必须时时刻刻用的。

不像RSNetworx用一下子就可以了。

5.编程软件最好用新版的V13.27。

V13以上版本支持热备切换时以太网地址互换,

V13以前版本只支持ControlNet地址互换,不支持以太网地址互换。

我的冗余硬件配置是:

主机架:电源-CPU-ENBT-CNBR-SRM

从机架:电源-CPU-ENBT-CNBR-SRM

IO机架:电源-CNBR-IO模块……

“两个机架上的CNBR的开关不能是最小,但是必须一样”,是不是指软件组态时只要把主机架上的CNBR 卡件节点设为一个较高的地址,而在硬件设置时要把主、从机架上的CNBR卡件的地址开关设为一样?是的,在软件中你将CNBR设置一个较高的地址即可。

比如31或25。

但是需要注意的是32和26(X+1)就不能再分配给任何站了,

因为备用站会占用这个地址。

而且,在硬件上的拨码地址都设成31或25即可。

因为不允许有2个相同的地址。

所以一个CNBR是X,另外一个CNBR自动就变成了X+1。