同济大学微机原理期末试题范围

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

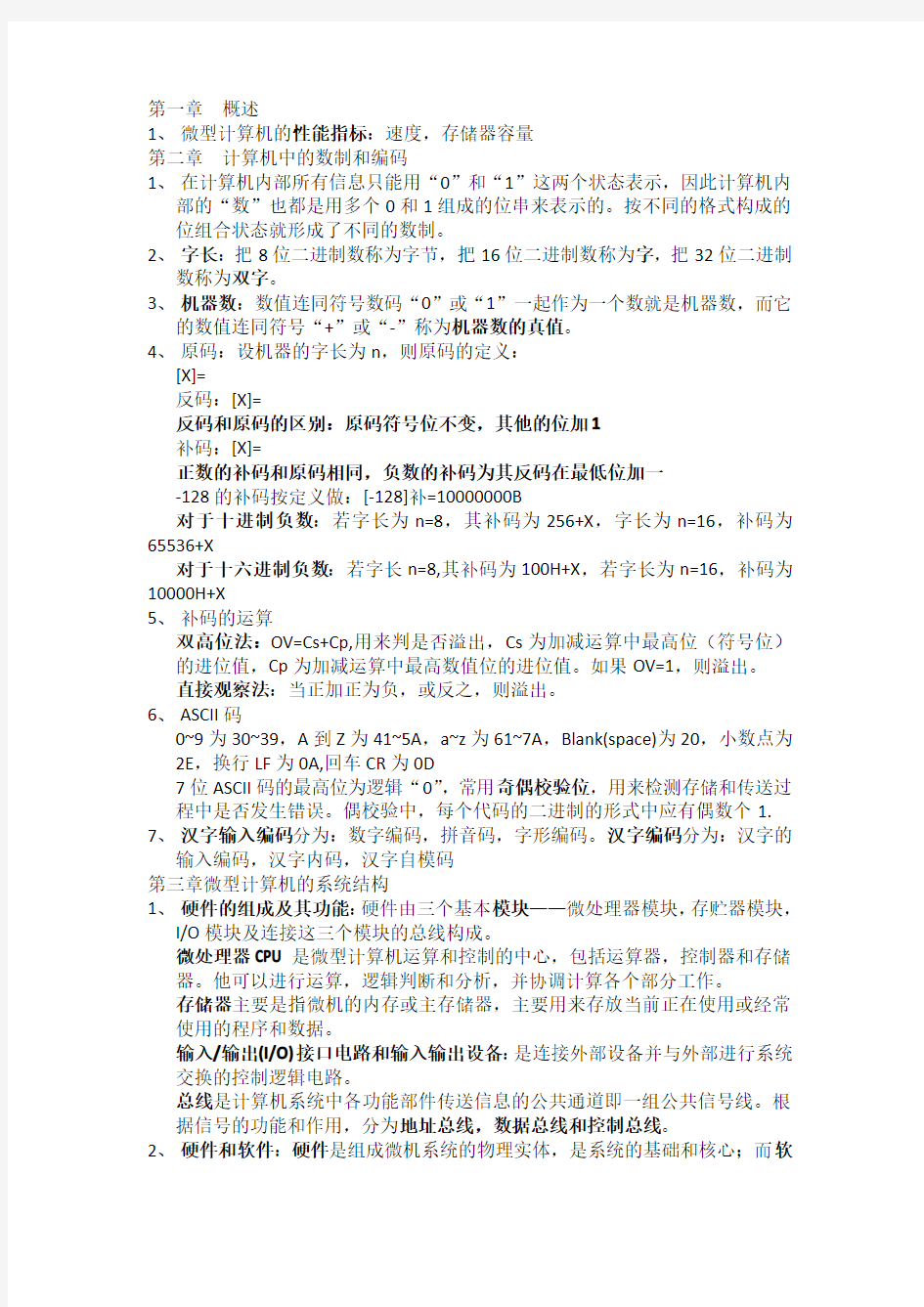

第一章概述

1、微型计算机的性能指标:速度,存储器容量

第二章计算机中的数制和编码

1、在计算机内部所有信息只能用“0”和“1”这两个状态表示,因此计算机内

部的“数”也都是用多个0和1组成的位串来表示的。按不同的格式构成的位组合状态就形成了不同的数制。

2、字长:把8位二进制数称为字节,把16位二进制数称为字,把32位二进制

数称为双字。

3、机器数:数值连同符号数码“0”或“1”一起作为一个数就是机器数,而它

的数值连同符号“+”或“-”称为机器数的真值。

4、原码:设机器的字长为n,则原码的定义:

[X]=

反码:[X]=

反码和原码的区别:原码符号位不变,其他的位加1

补码:[X]=

正数的补码和原码相同,负数的补码为其反码在最低位加一

-128的补码按定义做:[-128]补=10000000B

对于十进制负数:若字长为n=8,其补码为256+X,字长为n=16,补码为65536+X

对于十六进制负数:若字长n=8,其补码为100H+X,若字长为n=16,补码为10000H+X

5、补码的运算

双高位法:OV=Cs+Cp,用来判是否溢出,Cs为加减运算中最高位(符号位)的进位值,Cp为加减运算中最高数值位的进位值。如果OV=1,则溢出。

直接观察法:当正加正为负,或反之,则溢出。

6、ASCII码

0~9为30~39,A到Z为41~5A,a~z为61~7A,Blank(space)为20,小数点为2E,换行LF为0A,回车CR为0D

7位ASCII码的最高位为逻辑“0”,常用奇偶校验位,用来检测存储和传送过程中是否发生错误。偶校验中,每个代码的二进制的形式中应有偶数个1. 7、汉字输入编码分为:数字编码,拼音码,字形编码。汉字编码分为:汉字的

输入编码,汉字内码,汉字自模码

第三章微型计算机的系统结构

1、硬件的组成及其功能:硬件由三个基本模块——微处理器模块,存贮器模块,

I/O模块及连接这三个模块的总线构成。

微处理器CPU是微型计算机运算和控制的中心,包括运算器,控制器和存储器。他可以进行运算,逻辑判断和分析,并协调计算各个部分工作。

存储器主要是指微机的内存或主存储器,主要用来存放当前正在使用或经常使用的程序和数据。

输入/输出(I/O)接口电路和输入输出设备:是连接外部设备并与外部进行系统交换的控制逻辑电路。

总线是计算机系统中各功能部件传送信息的公共通道即一组公共信号线。根据信号的功能和作用,分为地址总线,数据总线和控制总线。

2、硬件和软件:硬件是组成微机系统的物理实体,是系统的基础和核心;而软

件是依赖于硬件执行的程序或程序的集合。软件分为系统软件和应用软件。

3、术语解释:RISC——精简指令集,CISC——复杂指令集,RAM——随机存储

器,ROM——只读存储器,EPROM——可擦除可编程的只读存储器,EEPROM——电可擦除可编程的只读存储器,Flash Memory——快速擦出的可读写存储器,DRAM——动态RAM,Cache——高速缓存,SA,EISA——标准总线的一种,PCI ——微处理器和外部设备的高速通道,CPU——中央处理单元,Memory——存储器

4、指令周期:CPU执行一条指令的时间(包括取指令和执行该指令所需的全部

时间)。

CPU通过对系统总线对存储器或I/O进行一次读,写的操作过程称为总线周期或机器周期(Tm),显然一个指令周期由若干个机器周期构成,而一个机器周期则由若干个时钟周期TC构成。Tm=K*Tc=K/fc,fc是CPU的时钟频率(主频),K为倍频。

5、存储器的分层结构:CPU(寄存器)——高速缓存(Cache)——主存储器(内

存)——辅助存储器(外存)存储容量,价格,高到低,存取速度,低到高

6、存储器分层原因:设计计算机存储系统是需要在容量、速度、价格之间折中

平衡。

7、存储容量和存取时间是存储器最重要的性能指标。

存储容量以kb,mb为单位,反应存储空间的大小。

存取时间反映了存储器的工作速度,它是从CPU给出有效的存储器地址启动一次存储读/写操作到该操作所经历的时间。

存取周期:连续两次独立的读/写操作所必须的最小时间间隔。

8、I/O接口的功能:数据缓冲功能,实现数据传输控制,接受主机命令,提供设

备状态,并按照主机的命令控制设备,数据格式转换功能。

I/O采用两种编址方式:存储器统一编址即存储器映像法,I/O独立编址法。

CPU和I/O接口间的数据传送方式:程序控制法,中断方式和直接存储器存取即DMA方式,共享RAM方式。

9、DAM控制器的工作方式:CPU暂停方式,总线周期的窃取方式,直接访问存

储器工作方式,(按总线占用方式)。按照数据传送方式分,单字节传送方式,数据块传送方式,请求传送方式。

DAM控制器包括多个寄存器:MDR,ADR,WC,CSC,DBR

DAM操作过程:预处理,数据传送,结束或后处理阶段

10、系统总线:连接微型计算机各主要功能部件实现信息传输的总线

数据总线:提供系统功能模块间的传输数据的通路。

地址总线:指明数据总线上的数据的来源和流。

控制总线:控制地址线和控制线的使用和访问。

典型控制信号:存储器读信号——memory read,将寻址的单元数据放到总线上。

存储器写信号——memory write,将总线的数据写入寻址的单元。

I/O读信号——I/O Read,使寻址的I/O端口的数据放到总线上。

I/O写信号——I/OWrite,使总线上的数据写入寻址的I/O端口。

11、总线的操作:获取总线控制权,发出操作命令和相关地址,数据传送和

释放总线。