接口技术 8259A中断控制器原理及应用

8259A中断控制器

CAS0 CAS1 CAS3

级 联 缓 冲 比较器

内 部 总 线

中 断 服 务 寄 存 器

ISR

优 先 权 处 理 器

中 断 请 求 寄 存 器

IRR

IR0 IR1 IR2 IR3 IR4 IR5 IR6 IR7

SP / EN

中断屏蔽寄存器 IMR

IRR,IMR

1.中断请求寄存器IRR

IRi(i=07)上有中断请求时,IRR相应位置1。

AEOI=1自动中断结束方式AEOI=0:非自动中断结束(EOI) µ PM=1:86系列CPU; µ PM=0:非86系列CPU 。

普通全嵌套方式

普通全嵌套方式也叫固定优先权方式。 优先权从IR0到IR7依次递降。 级别高的中断请求可以中断级别低的中断服 务子程序。 一中断被响应的过程中,自动屏蔽同级和更 低级别的中断。

8259A在PC机中的I/O端口地址

PC机中相当有两片8259A级联,一个主片,一个从片。

ICW1 ICW2 ICW3 ICW4 OCW1 OCW2 OCW3

主片 0x20 从片 0xa0

0x21 0xa1

0x21 0xa1

0x21 0xa1

0x21 0xa1

0x20 0xa0

0x20 0xa0

主片初始化程序

0

X

ESMM SMM 0

1

P

RR

RIS

A0=0 , D4=0 , D3=1 是OCW3的特征。 ESMM=1,SMM=0: 设置特殊屏蔽

ESMM=1,SMM=1: 清除特殊屏蔽

P=1:发查询命令 ; P=0:不发查询命令 RR=1,RIS=0: 读IRR寄存器 RR=1,RIS=1: 读ISR寄存器

可编程中断控制器8259A的原理及其应用

可编程中断控制器8259A的原理及其应用

杜蕴杰

【期刊名称】《电脑》

【年(卷),期】1994(000)011

【摘要】中断系统是计算机的核心部分,机器中的外设I/O硬中断给CPU管理微机外部设备提供了合理的控制权,使CPU可以对外部设备中断进行各种操作.外设I/O硬中断是由8259A来管理的,8259A可编程控制器允许CRU对其进行初始化编程(ICW)和写命令字编程(OCW)两种操作,在应用程序中进行不同的操作可完成特定的功能.计算机系统中的可编程中断控制器8259A是一种大规模可编程芯片,微型计算机用它来具体管理系统的外设硬中断.机器在重新启动时BIOS通过写端口20H和21H对可编程控制器进行重新初始化编程操作,将8个外设硬中断驱动程序08H-0FH分别挂接到8级硬中断请求IRQ0-IRQ7上,8组硬中断请求IRQ0-IRQ7与外部设备的对应关系如下:

【总页数】5页(P10-14)

【作者】杜蕴杰

【作者单位】无

【正文语种】中文

【中图分类】TP302.1

【相关文献】

1.8259A可编程中断控制器与8031单片机的接口技术 [J], 刘铁坤

2.可编程中断控制器8259A的开放式实验构建 [J], 刘正红

3.浅议可编程中断控制器8259A的程序设计 [J], 刘正红

4.用8259A可编程中断控制器扩展8098单片机的外中断源 [J], 郭显久

5.要编程中断控制器8259A的原理及其应用 [J], 杜蕴杰

因版权原因,仅展示原文概要,查看原文内容请购买。

微机原理8259A实验报告

实验二8259A中断控制器应用实验分析报告一、填写补充实验1-2中以下两段代码,并简述其意义:第1段:IN AL,21H_ AND AL, 0F7H _____________OUT 21H,ALIN AL,0A1H__AND AL, 0FBH______________OUT 0A1H,AL第2段:MOV AL,20HOUT 0A0H,ALOUT 20H,AL二、简述实验1-2的实验现象,分析解释其原因;结合本实验,简述中断嵌套和中断优先级的意义以及正确形成中断嵌套的基本要求。

答:实验1现象:按下一次单脉冲,显示一次字符,十次中断后停机,不再显示字符串实验2现象:分别按下两个单脉冲显示一串3和一串10,在3未显示完全时按下显示10的脉冲键,可发生中断,相反则不能发生中断,需等待一串10显示完后再显示一行3。

原因:IRQ10的中断级别高于IRQ3,所以可以在3还没有执行完时中断IRQ3,中断原程序执行IRQ10 。

中断嵌套的意义:为了让CPU及时响应更高级别的中断请求。

中断优先级的意义: CPU只能响应一个中断请求,在中断源较多的情况下,当有多个中断源同时发起中断请求时,CPU需要对多个中断源的优先级进行判断,判断出优先级最高的中断请求进行响应。

中断嵌套要求是:被中断程序的优先级低于请求程序中断的优先级。

三、抄写实验1-2中要求填写的“显示‘10’和‘空格’”的代码段NEXT10_1:MOV AX,SEG MESS10MOV DS,AXMOV DX,OFFSET MESS10MOV AH,09INT 21H ;使用INT21 – 09H实现字符串的输出‘10’CALL DELAY1 ;调用延时子程序LOOP NEXT10_1MOV DX,0DH ;调用DOS的中断功能,回车MOV AH,02HINT 21HMOV DX,0AH ;调用DOS的中断功能,换行MOV AH,02HINT 21H四、用文字简述或流程图方式,说明实验1-3中“以查询方式检测处理多中断请求”的过程。

8259工作原理

8259工作原理

8259工作原理是指8259A可编程中断控制器的工作原理。

8259A是一种用来处理中断信号的芯片,它可以管理多个设备的中断请求。

在8259A中,有8个中断请求线(IRQ0~IRQ7),这些中断

请求线可以连接到外部设备。

当一个设备需要通过中断通知CPU时,它会将相应的IRQ线拉低,8259A会将这个信号传

递给CPU。

8259A使用级联方式来管理多个设备的中断请求。

具体来说,它有一个主片和一个或多个从片。

主片连接到CPU,而从片

连接到各个外部设备。

主片负责管理整个中断系统,从片负责管理各自的设备的中断请求。

当一个设备的IRQ线被拉低时,从片会将这个信息传递给主片。

主片会根据中断请求的优先级确定要处理的中断请求,并将CPU相应的引脚拉高,通知CPU中断发生。

CPU会停止当前的工作,转而执行与中断相关的处理程序。

在8259A中,还有一些寄存器用来存储中断请求的相关信息。

这些寄存器可以被CPU读取和写入,以实现对8259A的配置

和控制。

总的来说,8259A的工作原理是通过管理中断请求线和级联连接的方式,实现外部设备与CPU之间的中断通信。

它可以在

多个设备同时发生中断时,决定中断的优先级,并通知CPU 执行相应的中断处理程序。

8259可编程的中断控制器

82598259A是一个可编程的中断控制器,应用在实时的、以中断方式进行监控的计算机系统中。

用一片8259A可以管理8个等级的中断申请。

并可再经级联扩展多至8片8259A,使得中断等级可扩展多至64级。

8259A可以作为一个I/O外围器件,用系统软件编程,它所具有的多种优先权方式可以通过主程序在任何时候进行改变或重新组织。

这意味着可以按照全系统的外围情况和要求,设计出一个完整的中断结构,用来实现优先管理、中断屏蔽以及自动中断矢量转移。

它几乎可以适合于任何一种中断控制的结构,因而得到了广泛的应用。

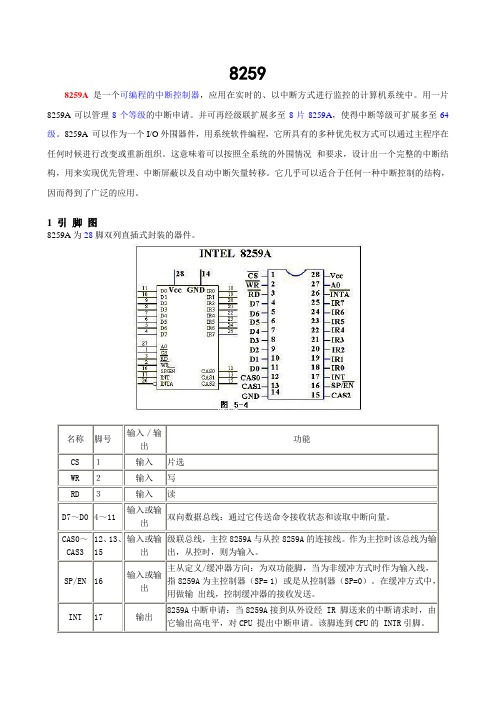

1 引脚图8259A为28脚双列直插式封装的器件。

2 内部结构其工作过程如下:第一步:当中断请求线(IR0~IR7)上有信号输入时,就把中断请求寄存器IRR相应的位置1。

第二步:当IRR的一位置1后,就会与IMR中相应的屏蔽位进行比较,如该屏蔽位为0,则请求被发送给优先级分析器;如该屏蔽位为1,则封锁该请求。

第三步:当一个中断请求被输入优先级分析器后,将由优先权分析器判定其优先权,然后向CPU 发中断申请,INT脚变高(INT联到8086的INTR)。

第四步:CPU的INTR引脚为异步状态接收,也就是它可以在任何时间(与时钟无关)接收中断。

在软件控制下利用STI指令(中断置位)或CLI(中断复位)指令可分别将CPU的“中断开放标志位”IF置位或复位,可以做到接受或不理睬在INTR上的中断申请。

第五步:假定CPU中的IF标志为1,则CPU在完成当前指令的即进入中断响应周期,这个中断响应周期将标志寄存器入栈,然后清除IF标志,关闭了中断。

再将代码段寄存器和指令指针也入栈(这是为了从中断服务程序返回),然后CPU发出第二个 INTA脉冲通知8259A,说明8086已经允许了它的中断请求。

若8086用于“最小方式”,则INTA脉冲信号为8086 INTA引脚上的信号;若8086用于“最大方式”时,则8086 LOCK脚在中断响应序列执行期间变为低电平。

中断系统和中断控制器8259A详解

微 机 原

第7章 中断系统和中断控制器8259A

理

及

应 用

7.1 中断的基本概念

∨∨

•中断:是指CPU在正常运行程序时,由于内部或外部事件 引起CPU暂时中止执行现行程序,转去执行请求CPU为其 服务的那个外设或事件的服务程序,待该服务程序执行完 后又返回到被中止的程序这样一个过程。

•中断源:能发出中断申请的外设或引起中断的原因。

IRR锁存

逻辑电路根据IMR判断 IMR对应位为0

优先权判别器PR

优

先

权

最

CPU响应中断 IF=1 CPU的INTR端

高 8259A的INT端为1

INTA 8259A

ISR相应位置1, IRR响应位清0,

送中断类型码

●若允许嵌套,PR依据ISR的状态,判断新的中断请求优先权是否高 于正在服务的中断,是则送出INT=1。 ●服务结束,8259A清除ISR响应位。

提高了CPU的利用效率。

7.1.2 中断处理过程

∧∧

微 机

1.中断过程

原

理 及

● 对于不同的微机系统,CPU中断处理的具体过程不尽相同,但是一

应 用

个完整的中断基本过程应包括五个基本过程:

∨∨

中

中

保护现场

中

中

中

断

断

请

判

断 响

断 处

断 返

开中断

求

优

应

理

回

中断处理

产指断触生令接发中或口器断电和CP信路中U确 最号有断引定高。一屏脚有的来个蔽。中那至中触每断个于断发个请中中请器中C自关保形求断P断 求 。动中护成U且 源完 断 现 中响优 。成 ; 场 断应先下 保 服;进级列 护 务入中 中 中工 断 程中断 断作 点 序断服 服 服: ; 入周务 务 务口期就 程 程地,是 序 序弹址过 结C出P程 构断U。 如执点图行,返回主程恢中关序复断。中现返断场回

总结介绍8259中断控制器

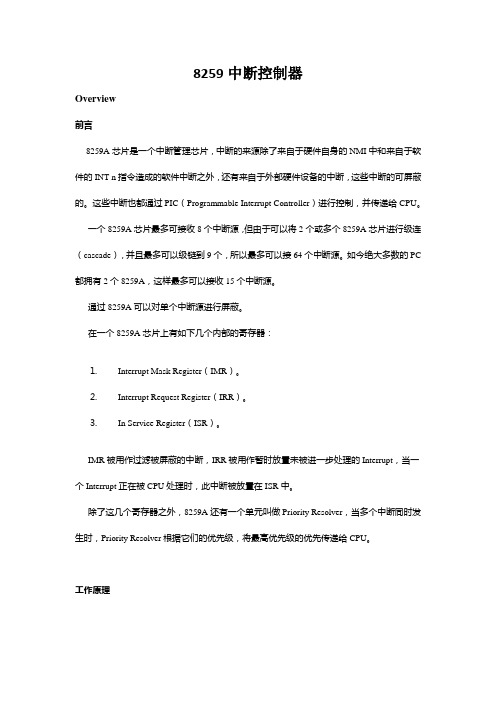

8259中断控制器Overview前言8259A芯片是一个中断管理芯片,中断的来源除了来自于硬件自身的NMI中和来自于软件的INT n指令造成的软件中断之外,还有来自于外部硬件设备的中断,这些中断的可屏蔽的。

这些中断也都通过PIC(Programmable Interrupt Controller)进行控制,并传递给CPU。

一个8259A芯片最多可接收8个中断源,但由于可以将2个或多个8259A芯片进行级连(cascade),并且最多可以级链到9个,所以最多可以接64个中断源。

如今绝大多数的PC 都拥有2个8259A,这样最多可以接收15个中断源。

通过8259A可以对单个中断源进行屏蔽。

在一个8259A芯片上有如下几个内部的寄存器:1.Interrupt Mask Register(IMR)。

2.Interrupt Request Register(IRR)。

3.In Service Register(ISR)。

IMR被用作过滤被屏蔽的中断,IRR被用作暂时放置未被进一步处理的Interrupt,当一个Interrupt正在被CPU处理时,此中断被放置在ISR中。

除了这几个寄存器之外,8259A还有一个单元叫做Priority Resolver,当多个中断同时发生时,Priority Resolver根据它们的优先级,将最高优先级的优先传递给CPU。

工作原理当一个中断请求从IR0到IR7中的某根线到达IMR时,IMR首先判断IR是否被屏蔽,如果被屏蔽,则此中断请求被丢弃;否则,则将放入IRR中。

在此中断请求不能进行下一步处理之前,它一直被放置在IRR中。

一旦发现处理中断的时机已到,Priority Resolver将从所有被放置于IRR中的中断中挑选出一个优先级最高的中断,将其传递给CPU去处理。

IR号越低的中断优先级级别越高,比如IR0的优先级是最高的。

8259A通过发送一个INTR(Interrupt Request)信号给CPU,通知CPU有一个中断到达。

8.3 可编程中断控制器8259A及其应用

8259A的工作方式( 8259A的工作方式(2)——结束中断的方式 的工作方式

注意: 注意:

级连方式下,一般不用中断自动结束方式, 级连方式下,一般不用中断自动结束方式,而用 非自动结束方式。不管用哪一种非自动结束方式, 非自动结束方式。不管用哪一种非自动结束方式, 都至少连发两次中断结束命令,一次对主片, 都至少连发两次中断结束命令,一次对主片,一 次对从片。 次对从片。

(5)数据总线缓冲器 数据总线缓冲器

是双向三态8位缓冲器,用于连接系统数据总线和 8259A 内 部 总 线 , 传 递 CPU 发 送 的 控 制 信 息 , 返 回 8259A的状态信息 的状态信息

(6)读/写控制电路 读 写控制电路

Di位为 表示 中断正在服务中;为0表示没有被服务 位为1表示 中断正在服务中; 位为 表示IRi中断正在服务中 表示没有被服务

第8章 中断系统

§8.3 可编程中断控制器8259A及其应用

第8章 中断系统

中断接口8259A是可编程中断控制器, 中断接口8259A是可编程中断控制器,用于管理 8259A是可编程中断控制器 8080/8085、8086/8088、80286/80386的可屏蔽中断 8080/8085、8086/8088、80286/80386的可屏蔽中断

8.3.3

8259A中断控制器的引脚( 8259A中断控制器的引脚(1) 中断控制器的引脚

8259A是一个使用+5V电源的28脚双列直插芯片。 8259A是一个使用+5V电源的28脚双列直插芯片。 是一个使用+5V电源的28脚双列直插芯片 中断请求输入信号,一般IR ① IR0~IR7—中断请求输入信号,一般IR0优先 级最高, 最低,但优先级可由编程改变。 级最高,IRQ7最低,但优先级可由编程改变。 INT—中断请求输出信号, CPU的INTR引脚 引脚。 ② INT—中断请求输出信号,接CPU的INTR引脚。 INTA—中断响应,由此脚接收来自CPU CPU的中断 ③ INTA—中断响应,由此脚接收来自CPU的中断 响应信号。 响应信号。 ④ CS—片选,当CS有效时,该芯片工作。 CS—片选, CS有效时 该芯片工作。 有效时, ⑤ WR—写信号,有效时CPU将命令字写入8259A。 WR—写信号,有效时CPU将命令字写入8259A CPU将命令字写入8259A。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

4

2. 与处理器接口(读写控制逻辑部分)

A0 RD* WR* CS* 0 1 0 1 × × 1 1 0 0 1 × 0 0 1 1 1 × 0 0 0 0 0 1 功能 写入ICW1、OCW2和OCW3 写入ICW2~ICW4和OCW1 读出IRR、ISR和查询字 读出IMR 数据总线高阻状态 数据总线高阻状态

17

5. 中断触发方式

边沿触发方式

8259A将中断请求输入端出现的 上升沿作为中断请求信号 中断请求端出现的高电平是有 效的中断请求信号

电平触发方式

18

6. 数据线连接方式

缓冲方式

8259A的数据线需加缓冲器予以驱动 8259A把SP*/EN*引脚作为输出端(输出允 许信号),用以锁存或开启缓冲器(enable buffer) SP*/EN*引脚为输入端(slave program) 若8259A级连,由其确定是主片(sp=1)或从 片 (sp=0)

CAS0-CAS2 : 主8259A的三条级连线CAS0~CAS2作为输出线, 连至每个从8259A的CAS0~CAS2 SP*/EN*:在非缓冲方式下,规定该8259A是主片(SP*=1)还是 从片(SP*=0) IRi : 每个从8259A的中断请求信号INT,连至主8259A的一个中断 请求输入端IR INT :主8259A的INT线连至CPU的中断请求输入端

8259A的初始化顺序

8259的初始化流程如图 (注意次序不可颠倒 )

写ICW1 写ICW2 N

级连?

Y 写ICW3 N

需ICW4?

Y 写ICW4

8259A的控制命令字

初始化8259A必须从ICW1开始

写ICW1意味着重新初始化8259A 写入ICW1后,8259A的状态如下:

清除ISR和IMR(全0); 将中断优先级设成初始状态:IR0最高,IR7最低; 设定为普通(一般)屏蔽方式; 采用非自动中断结束方式; 状态读出逻辑预置为读IRR。

ICW1——芯片控制初始化命令字

A0 0

D7 x

D6 x

D5 x

D4 1

D3 D2 LTIM x

ICW1 的标志

D1 D0 SNGL IC4

10

1. 优先权固定方式

普通全嵌套方式

8259A的中断优先权顺序固定不变,从高到低依次为IR0 、IR1、IR2、……IR7 中断请求后,8259A对当前请求中断中优先权最高的中 断IRi予以响应,将其向量号送上数据总线,对应ISR的 Di位置位,至到中断结束(ISR的Di位复位) 在ISR的Di位置位期间,禁止再发生同级和低级优先权 的中断,但允许高级优先权中断的嵌套

8259A的工作方式(理解)

普通全嵌套方式 优先权固定方式 特殊全嵌套方式 设置优先权方式 自动循环方式 优先权循环方式 特殊循环方式 自动中断结束方式 结束中断处理方式 普通中断结束方式 非自动中断结束方式 特殊中断结束方式 普通屏蔽方式 屏蔽中断源方式 特殊屏蔽方式 边沿触发方式 中断触发方式 电平触发方式 缓冲方式 数据线连接方式 非缓冲方式

注:ICW—初始化命令字,OCW—操作命令字

5

3. 中断级连

单片8259A可支持8个中断源; 采用多片8259A级连,可最多支持64个中断源。N片 8259A可以支持8*N-(N-1)个中断源 级连时只能有一片8259A为主片,其余的均为从属片; 涉及到的8259A引脚包括:

非自动中断结束方式1:普通中断结束方式EOI

非自动中断结束方式2:特殊中断结束方式SEOI

16

4. 屏蔽中断源方式

普通屏蔽方式 将IMR的Di位置1,则对应的中断IRi被屏蔽,该 中断请求不能从8259A送到CPU 如果IMR的Di位置0,则允许IRi中断产生 特殊屏蔽方式 使用场合:在执行较高级的中断服务时,希望开放 较低级的中断请求。 原理:将IMR的Di位置1,对应的中断IRi被屏蔽的 同时,使ISR的Di位置0。假定当前正在处理IR6, 先进入特殊屏蔽方式,然后设置IM6=1。这时, 除IR6外的所有中断请求均能得到响应。 特殊屏蔽方式中只能用SEOI命令结束中断。

8259A中断控制器 原理及应用 (6.3节)

8259A中断控制器

Intel 8259A是可编程中断控制器PIC 可用于管理Intel 8080/8085、8086/8088、 80286/80386的可屏蔽中断 8259A的基本功能

一片8259A可以管理8级中断,可扩展至64级 每一级中断都可单独被屏蔽或允许 在中断响应周期,可提供相应的中断向量号 8259A设计有多种工作方式,可通过编程选择

写入ICW2~ICW4和OCW1 读出IRR、ISR和查询字 读出IMR 数据总线高阻状态 数据总线高阻状态

CS# RD# WR# A0 D4 D3 0 0 0 0 0 1 0 1 0 0 1 x 1 x x 0 0 1 0 1 x x

读写操作 写OCW2 写OCW3 写ICW1 写ICW2,ICW3,ICW4,OCW1(顺序写入) 读出IRR、ISR 读出IMR

6

级连电路连接方法

系统总线 AB、DB、CB

演示

INTA A0 CS D0-D7

RD WR INT CAS0 CAS1 CAS2

INTA A0 CS D0-D7 RD WR INT

INTA A0 CS D0-D7 RD WR INT CAS0 CAS1 CAS2

8259A (从片1)

8259A (从片2)

动画

8259A对中断请求的处理过程如下:

当某IRi有效时,IRR相应位置1 若有效的IRi未被屏蔽,则向CPU发出中断请求 检测到第1个INTA*信号后,置ISRi=1,IRRi=0 检测到第2个INTA*信号后,把ISRi=1中最高优 先级的中断类型码放到DB上 若工作在AEOI方式,在第2个INTA*结束时,使 ISRi复位;否则由CPU发出EOI命令使ISRi复位

CAS0 CAS1 CAS2

8259A (主片)

SP/EN IR7 IR6 IR5 IR4 IR3 IR2 IR1 IR0

SP/EN IR7 IR6 IR5 IR4 IR3 IR2 IR1 IR0

SP/EN IR7 IR6 IR5 IR4 IR3 IR2 IR1 IR0

VCC

8259A的工作过程

中断操作编程

20

8259A内部寄存器的寻址方法

A0 RD* WR* CS* 0 1 0 1 × × 功能

需要 、A0、RD#、WR# 和 D DOCW3 1 CS# 0 0 写入ICW1 、 OCW2 4、和 3的配合

内部寄存器的访问方法如下表:

1 0 0 1 ×

0 1 1 1 ×

0 0 0 0 1

1. 中断控制

中断请求寄存器IRR

保存8条外界中断请求信号IR0~IR7的请求状态 Di位为1表示IRi引脚有中断请求;为0表示无请求 保存正在被8259A服务着的中断状态 Di位为1表示IRi中断正在服务中;为0表示没有被服务

中断服务寄存器ISR

中断屏蔽寄存器IMR

保存对中断请求信号IR的屏蔽状态 Di位为1表示IRi中断被屏蔽(禁止);为0表示允许 (与IF标志位的规定相反)

15

结束中断处理方式(续)

自动中断结束方式AEOI

在第2个INTA#结束时,由8259A使ISRi自动复位 配合全嵌套(固定)优先权方式使用 当CPU用输出指令往8259A发出普通中断结束EOI命令 时,8259A就会把所有正在服务的中断中优先权最高 的ISR位复位 配合循环优先权方式使用 CPU在程序中向8259A发送一条特殊中断结束命令, 这个命令中指出了要清除哪个ISR位

演示

ICW4——方式控制初始化命令字

非缓冲方式

19

8259A的编程

初始化编程

8259A开始工作前,必须进行初始化编程 给8259A写入初始化命令字ICW(ICW1~ICW4) 在8259A工作期间 可以写入操作命令字OCW(OCW1~OCW3)将选 定的操作传送给8259A,使之按新的要求工作 还可以读取8259A的信息,以便了解它的工作状 态

ICW3——级连控制字

A0 1

D7 S7

D6 S6

D5 S5

D4 S4

D3 S3

D2 S2

D1 S1

D0 S0

主片的级联控制字 (位映像方式)

Si=1 对应IRi线上连接了从片

D7 0 D6 0 D5 0 D4 0 D3 0 D2 ID2 D1 ID1 D0 ID0

A0 1

•

从片的级联控制字 (编码方式)

LTIM: 触发方式

=1 高电平触发 =0 上升沿触发 =1 单片 =0 级连 =1 要写ICW4(8086配合8259则此位必须为1) =0 不写ICW4(默认ICW4为全0)

SNGL: 级连控制

IC4: ICW4控制

ICW2——中断向量码基值

A0 1

D7 T7

D6 T6

INT IR4

IR5

IR6 IR7

IR6

IR7

E.

D. 特殊嵌套方式: IR4 的 中 断 被 服

务时,只封锁 IR5-的 INT ,故级别高的 IR0IR2 中断可以得到响应。 (但IR3-IR7仍被本从片 封锁)