微机原理中断处理过程

中断请求的定义微机原理

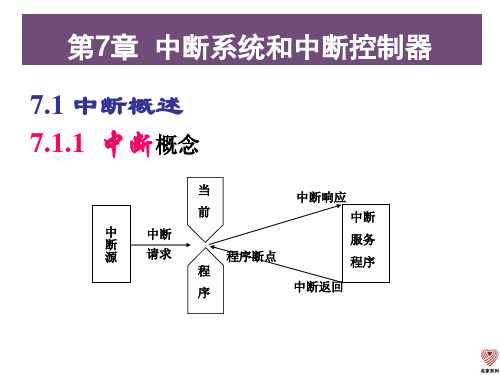

中断请求的定义微机原理中断请求(Interrupt Request,简称IRQ)是指在微机系统中,外部设备发生了某种特定的事件或状态变化时,向CPU发送中断信号,请求CPU暂停当前的工作,并跳转到相应的中断服务程序中去处理这个事件或状态变化。

在微机系统中,外设与CPU之间通过总线连接,外设发出的中断请求是通过硬件电路与总线相连的电线上的电压信号来表示的。

当外设发生了特定的事件或状态变化时,它会通过电线上的电压信号来告知CPU,这个信号就是中断请求信号。

CPU在执行当前的指令时,会不断地检测这个中断请求信号,一旦检测到了中断请求信号,就会立即中断当前的工作,进入相应的中断服务程序中去处理。

中断请求的定义实际上包括了两个方面的内容:中断源和中断服务程序。

中断源(Interrupt Source)是指可能会发出中断请求的外设,例如键盘、鼠标、硬盘等。

中断源可以是硬件设备,也可以是由软件模拟出来的虚拟设备。

中断服务程序(Interrupt Service Routine,简称ISR)是指处理中断请求的程序,当中断请求被触发时,CPU会暂停当前的工作,转去执行相应的中断服务程序。

中断服务程序通常是由操作系统负责编写的,可以根据中断源的不同设置不同的中断处理程序。

在实际应用中,不同的中断请求信号会被分配不同的优先级,高优先级的中断请求会先被处理,而低优先级的中断请求将会在高优先级中断处理完毕后再进行处理。

这种优先级的分配可以通过硬件的方式实现,也可以通过软件的方式实现。

例如,在使用8259A可编程中断控制器的系统中,可以通过设置中断控制器上的硬件引脚的优先级来实现不同中断请求的优先级控制。

中断请求的处理过程一般包括以下几个步骤:1. 当外设发生了特定的事件或状态变化时,会产生相应的中断请求信号,将该信号送入CPU。

2. CPU会不断地检测中断请求信号,如果检测到了中断请求信号,就会立即中断当前的工作,保存当前的执行现场(包括程序计数器、标识寄存器等),并跳转到相应的中断服务程序中去执行。

微机原理第7章 8086中断系统和中断控制器

3)高级中断源能中断低级的中断处理

中断嵌套 当CPU正在响应某一中断源的请求,执行为其服务的中断服务程序时, 如果有优先级更高的中断源发出请求,CPU将中止正在执行的中断服务程 序而转入为新的中断源服务,等新的中断服务程序执行完后,再返回到被 1 中止的中断服务程序,这一过程称为中断嵌套。 • 中断嵌套可以有多级,具体级数原则上不限,只取决于堆栈深度。

外部中断 非屏蔽中断 可屏蔽中断

可屏蔽中断源

CPU 中断逻辑

INTR

8259A 中断 INTA 控制器

INT N 指令

INTO 指令

除法 错误

单步 中断

IR0 IR1 IR2 IR3 IR4 IR5 IR6 IR7

外 设 中 断 源

内部中断: 除法错中断 指令中断 溢出中断 单步中断

硬件(外部)中断 非屏蔽中断请求 INT 2 NMI(17号引脚) 中 断 逻 辑 可屏蔽中断请求 中断类型号32~255 INTR(18号引脚)

中断指令 INT n N=32~255

溢出中断 INTO INT 4

断点 中断 INT 3

单步中断 (TF=1) INT 1

除法 错误 INT 0

软件(内部)中断

8086/8088中断源

1.软件中断(内部中断) 8086/8088的软件中断主要有三类共五种。 (1) 处理运算过程中某些错误的中断 执行程序时,为及时处理运算中的某些错误 ,CPU以中断方式中止正在运行的程序,提醒程 序员改错。 ① 除法错中断(中断类型号为0)。在8086 /8088 CPU执行除法指令(DIV/IDIV)时,若发现 除数为0,或所得的商超过了CPU中有关寄存器所 能表示的最大值,则立即产生一个类型号为0的 内部中断,CPU转去执行除法错中断处理程序。

微机原理与接口技术——中断系统

2、内部中断——软件中断

内部中断指由指令的执行或软件对标志寄存器中 某个标志的设置产生的中断

专用中断

指令中断

内部中断的种类

(1)除法出错中断 类型号为00H

除法出错中断既不是外部硬件产生,也不是用 软件指令产生,而是CPU自身产生的,因此0型中 断没有对应的中断指令,即指令系统中没有INT 0 这条指令。

30~3FH 40~FFH

DOS保留使用 DOS内部使用 DOS保留使用 用户自定义

DOS 可调用

1、外部中断——硬件中断

1、非屏蔽中断(NMI):不受中断标志位的控制,中断类型 号为2,所以中断向量放在0000:0008开始的4个单元中。NMI 中断一般用于紧急情况的处理,不受中断标志位IF影响 。 2、可屏蔽中断(INTR):受中断标志位的控制,IF=1, CPU才能响应INTR中断。CPU响应INTR中断时,往INTA引 脚上发两个负脉冲,外设接到第二个负脉冲后,立即往数据总 线上送出中断类型码,供CPU读取。

中断源

引起CPU中断的事件,发出中断请求的来源。

异常中断 内部中断

软件中断

异常事件引起 中断指令引起

可屏蔽中断 外部中断

非屏蔽中断

INTR中断 NMI中断

引入中断的原因

提高数据传输率; 避免了CPU不断检测外设状态的过程,提高了

CPU的利用率。 实现对特殊事件的实时响应。

中断系统

中断系统是指实现中断功能的软硬件的统称。功 能有: 正确识别中断请求,实现中断响应、中断处理

INTR

IRQ0 系统定时器 IRQ1 键盘 IRQ2 彩色/图形接口

8259A

IRQ3 保留(串口) IRQ4 串口

IRQ5 保留(LPT)

《微机原理与接口技术》习题解答7

《微机原理与接口技术》习题解答习题77.1 什么是中断?常见的中断源有哪几类?CPU响应中断的条件是什么?【解答】中断是指CPU在正常执行程序时,由于内部/外部时间或程序的预先安排引起CPU暂时终止执行现行程序,转而去执行请求CPU为其服务的服务程序,待该服务程序执行完毕,又能自动返回到被中断的程序继续执行的过程。

常见的中断源有:一般的输入/输出设备请求中断;实时时钟请求中断;故障源;数据通道中断和软件中断。

CPU响应中断的条件:若为非屏蔽中断请求,则CPU执行完现行指令后,就立即响应中断。

CPU若要响应可屏蔽中断请求,必须满足以下三个条件:①无总线请求;②CPU 允许中断;③CPU执行完现行指令。

7.2 简述微机系统的中断处理过程。

【解答】(1)中断请求:外设需要进行中断处理时,向CPU提出中断请求。

(2)中断响应:CPU执行完现行指令后,就立即响应非屏蔽中断请求。

可屏蔽中断请求,CPU若要响应必须满足三个条件。

(3)中断处理:保护现场、开中断、中断服务。

(4)中断返回:CPU执行IRET中断返回指令时,自动把断点地址从堆栈中弹出到CS 和IP中,原来的标志寄存器内容弹回Flags,恢复到原来的断点继续执行程序。

7.3 软件中断和硬件中断有何特点?两者的主要区别是什么?【解答】硬件中断由外部硬件产生,是由CPU外部中断请求信号触发的一种中断,分为非屏蔽中断NMI和可屏蔽中断INTR。

软件中断是CPU根据某条指令或者对标志寄存器的某个标志位的设置而产生的,也称为内部中断。

通常有除法出错中断、INTO溢出中断、INT n中断、断点中断和单步中断等。

两者的主要区别:硬件中断由外部硬件产生,而软件中断与外部电路无关。

7.4 中断优先级的排队有哪些方法?采用软件优先级排队和硬件优先级排队各有什么特点?【解答】软件优先级排队:各中断源的优先权由软件安排。

优点是电路比较简单,可以直接修改软件查询顺序来修改中断优先权,不必更改硬件。

微机原理实验-外部中断实验

下面是赠送的几篇网络励志文章需要的便宜可以好好阅读下,不需要的朋友可以下载后编辑删除!!谢谢!!出路出路,走出去才有路“出路出路,走出去才有路。

”这是我妈常说的一句话,每当我面临困难及有畏难情绪的时候,我妈就用这句话来鼓励我。

一定有很多人想说:“这还在北京混个什么劲儿啊!”但他每天都乐呵呵的,就算把快递送错了也乐呵呵的。

某天,他突然递给我一堆其他公司的快递单跟我说:“我开了家快递公司,你看得上我就用我家的吧。

”我有点惊愕,有一种“哎呦喂,张老板好,今天还能三蹦子顺我吗”的感慨。

之后我却很少见他来,我以为是他孩子出生了休假去了。

再然后,我就只能见到单子见不到他了。

某天,我问起他们公司的快递员,小伙子说老板去上海了,在上海开了家新公司。

我很杞人忧天地问他:“那上海的市场不激烈吗?新快递怎么驻足啊!”小伙子嘿嘿一笑说:“我们老板肯定有办法呗!他都过去好几个月了,据说干得很不错呢!”“那老婆孩子呢?孩子不是刚生还很小吗?”“过去了,一起去上海了!”那个瞬间,我回头看了一眼办公室里坐着的各种愁眉苦脸的同事,并且举起手机黑屏幕照了一下我自己的脸,一股“人生已经如此的艰难,有些事情就不要拆穿”的气息冉冉升起。

并不是说都跳槽出去开公司才厉害,在公司瞪着眼睛看屏幕就是没发展,我是想说,只有勇气才能让自己作出改变。

《拒绝平庸》里有一句话:很多时候我们为什么嫉妒别人的成功?正是因为知道做成一件事不容易又不愿意去做,然后又对自己的懒惰和无能产生愤怒,只能靠嫉妒和诋毁来平衡。

其实走出去不一定非要走到什么地方去,而是更强调改变自己不满意的现状。

有人问我那你常说要坚持,天天跑出去怎么坚持?其实要坚持的是一种信仰,而不是一个地方,如果你觉得一个地方让你活得特别难受,工作得特别憋屈,除了吐槽和压抑没别的想法,那就要考虑走出去。

就像歌词里说的:“梦想失败了,那就换一个梦想。

”不能说外面都是大好前程,但肯定你会认识新的人,有新的机会,甚至改头换面重新做人。

微机原理14162中断处理过程

8

§7.2 中断处理过程

二、CPU对中断的响应

3. 识别中断源

CPU要对中断进行处理,必须找到相应的中断服 务程序的入口地址,这就是中断源的识别。

4. 保护现场

为了不使中断服务程序的运行影响主程序的状态, 必须把断点处的相关寄存器及标志寄存器压栈保 护。

5. 执行中断服务程序

6. 恢复现场 7. 开中断及返回

2019/10/3

4

§7.2 中断处理过程

一、CPU响应中断的条件

中断允许触发器的状态可用指令CLI和 STI来改 变,下述三种情况可关闭中断:

1) 当CPU复位时,中断允许触发器处于关中 断状态;

2) 中断请求被响应后,CPU自动关中断; 3) CPU执行关中断指令CLI后,中断关闭。

2019/10/3

2019/10/3

7

§7.2 中断处理过程

二、CPU对中断的响应

CPU进入中断响应周期后,中断响应过程如下:

1. 关中断

CPU在响应中断后,发出中断响应信号INTA,同 时内部自动关中断,以禁止接受其它的中断请求。

2. 保护断点 把断点处的IP及CS值入栈保存,以备中断处理完 后能正确返回断点。

2019/10/3

四、中断优先级

17

§7.2 中断处理过程

实现方法:

将8个外 设的中断 请求触发 器组合为 一个端口, 并给这个 端口赋以 设备号 (口地址),

2019/10/3

四、中断优先级

18

§7.2 中断处理过程

四、中断优先级

然后,把各外设的中断请求信号相或后作为INTR信 号。任何外设有中断请求时,都可向CPU发出INTR 信号。CPU响应中断后,把中断寄存器的状态作为 一个输入端口读进CPU,然后逐位检测其状态,若 有中断请求就转入相应的中断服务程序,这样优先 级的级别取决于软件查询的顺序,先测试的中断源 具有较高的优先级。

微机原理iret

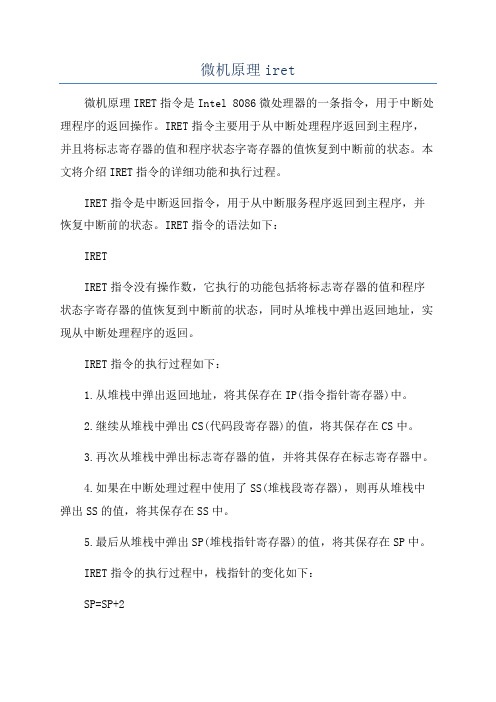

微机原理iret微机原理IRET指令是Intel 8086微处理器的一条指令,用于中断处理程序的返回操作。

IRET指令主要用于从中断处理程序返回到主程序,并且将标志寄存器的值和程序状态字寄存器的值恢复到中断前的状态。

本文将介绍IRET指令的详细功能和执行过程。

IRET指令是中断返回指令,用于从中断服务程序返回到主程序,并恢复中断前的状态。

IRET指令的语法如下:IRETIRET指令没有操作数,它执行的功能包括将标志寄存器的值和程序状态字寄存器的值恢复到中断前的状态,同时从堆栈中弹出返回地址,实现从中断处理程序的返回。

IRET指令的执行过程如下:1.从堆栈中弹出返回地址,将其保存在IP(指令指针寄存器)中。

2.继续从堆栈中弹出CS(代码段寄存器)的值,将其保存在CS中。

3.再次从堆栈中弹出标志寄存器的值,并将其保存在标志寄存器中。

4.如果在中断处理过程中使用了SS(堆栈段寄存器),则再从堆栈中弹出SS的值,将其保存在SS中。

5.最后从堆栈中弹出SP(堆栈指针寄存器)的值,将其保存在SP中。

IRET指令的执行过程中,栈指针的变化如下:SP=SP+2SP=SP+2SP=SP+2如果使用了堆栈段寄存器SP=SP+2IRET指令的执行还可能涉及到特权级的变化。

在进入中断处理程序时,处理器会将当前特权级压入堆栈中作为返回地址之前的值。

因此,在IRET指令中,如果特权级从低级别返回到高级别,那么堆栈中的特权级值会被加载到CS和SS寄存器中。

如果特权级从高级别返回到低级别,那么CS和SS寄存器的值将不会发生改变。

IRET指令的使用非常广泛,特别适用于中断处理程序的编写。

在中断处理程序中,当完成中断服务后,使用IRET指令可以方便地返回到主程序,并恢复中断前的状态。

总结:IRET指令是微处理器中的一条中断返回指令,用于从中断处理程序返回到主程序,并恢复中断前的状态。

执行IRET指令的过程涉及到返回地址、代码段、标志寄存器、堆栈段和堆栈指针的恢复。

微机原理(中断概念)

必要性及应用 中断功能便于实现 1.分时操作

CPU和外设同时工作;CPU可以通过 分时操作启动多个外设同时工作,统一 管理。大大提高了CPU的利用率,也提 高了输入、输出的速度。

2.实时处理

3.故障处理

4.主机与外设之间的速度匹配

计算机在运行过程中,往往会出现事 先预料不到的情况,或出现一些故障: 如电源突跳,存储出错,运算溢出等等。 计算机就可以利用中断系统自行处理, 而不必停机或报告工作人员。

3. 8086从0030H开始读取4字节中断处理程 序的入口地址,前两字节装入IP,后两 字节装入CS,8086执行中断处理程序。

中断向量的装入

• 中断向量的装入方法:用MOV指令 • 假设中断类型号为60H,中断服务程序的偏移地

址是1234H,段地址5678H

• MOV AX,00H • MOV ES,AX; 0段 • MOV BX,60H*4; (=180H)中断向量指针 • MOV AX,1234; 中断服务程序偏移地址 • MOV ES:[BX],AX;装入偏移地址 • MOV AX,5678H; 中断服务程序段地址 • MOV ES:[BX+2],AX;装入段地址

8086中断时序

➢ 8086对外部硬件中断请求INTR的响应:

当INTR有一高电平,即有可屏蔽中断请求。 若此时IF=1且当前指令执行完,进入中断响 应周期,处理过程如下:

1. INTA*在两个总线周期中分别发出有效信号, 在第二个周期中8086读到中断类型码,然后 乘以4,得到中断向量。

2. 下一条指令地址CS和IP入栈,标志寄存器入 栈,清除IF和TF标志位。

中断嵌套

CPU正在执行 主程序

CPU正在执行 低级中断服务

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

硬件端口:是接口电路中能被CPU直接访问的寄存器的地址 这些寄存器分别用来存放数据信息、控制信息和状态信息 ,相应的端口分别称为数据端口、控制端口和状态端口。

2020/11/14

2020/11/14

10

三:中断允许触发器为1(中断开放时)

教材224页 CPU内部有一个中断允许触发器,只有当其为1时,CPU才响 应中断!若其为0,即使INTR线上有中断请求,CPU也不响应 !(按教材讲)

IF标志位:就是控制CPU的中断状态!(开,或关) CLI指令:禁止中断发生,即关中断(IF标志位为0) STI指令:允许中断发生,即开中断(IF标志位为1)

寄存器:多个触发器构成,存储多位二进制信息

所谓锁存器,就是输出端的状态不会随输入端的状态变化而 变化,仅在有锁存信号时输入的状态被保存到输出,直到 下一个锁存信号到来时才改变。典型的锁存器逻辑电路是 D 触发器电路。锁存器多用于集成电路中,在数字电路中 作为时序电路的存储元件

2020/11/14

4

接口电路和端口

中断源 CPU

设置中断请求触发器

设置中断屏蔽触发器(拓展) 中断允许触发器为1(中断开放) 现行指令结束

CPU对中 断的响应

关中断

保留断点

保护现 场 给出中断入口,转入相应的中断服务程序 恢复现场

开中断与返回 3

概念回顾

触发器是时序逻辑电路的基本单元的组成单元,属于时序逻 辑电路!能够存储一位信号的基本单元电路称为"触发器"; 在实际的数字系统中,通常把能够用来存储一组二进制代 码的同步时序逻辑电路称为寄存器。由于触发器内有记忆 功能,因此利用触发器可以方便地构成寄存器。由于一个 触发器能够存储一位二进制码,所以把n个触发器的时钟 端口连接起来就能构成一个存储n位二进制码的寄存器。

读入数据并清 除中断请求信 号!

图8-1 设置中断请求的情况

2020/11/14

7

CPU响应中断的条件

二:设置中断屏蔽触发器(拓展 为什么?)

是指即使某个中断源发出中断请求信号,

也使该信号不起作用的措施。方法是在每个外

设的接口电路中设置一个中断屏蔽触发器,

用来控制其对应外设所发出的中断请求能否送

到CPU,只有为1时,外设的中断请求才能送至

2020/11/14

17

谢谢大家!

讲解为什么这样做! 根据教材P224页!分别论述!

(1)关中断 (2)保留断点 (3)保护现场 (4)给出中断入口,转入相应的中断服务程序 (5)恢复现场 (6)开中断与返回

2020/11/14

14

2020/11/14

图8-4 中断响应、服务及返回流程图

15

总结

8 0 8 6 的 中 断 情 况

5

CPU响应中断的条件

一 : 设 置 中 断 请 求 触 发 器 ( 教 材 ;P223 ) 对每个中断源来说, 既要能发出中断请求信 号,而且能保持这个信号, 直至CPU响应该 请求后再将其清除。 因此, 每个中断源都 要有一个中断请求触发器, 如下图中的触发 器A。

2020/11/14

6

CPU通过端口和外设进行数据交换

2020/11/14

CPU响应 中断的条件

中断源 CPU

设置中断请求触发器

设置中断屏蔽触发器(拓展) 中断允许触发器为1(中断开放) 现行指令结束

CPU对中 断的响应

关中断 保留断点 保护现场 给出中断入口,转入相应的中断服务程序 恢复现场 开中断与返回

16

中断允许寄存器IF是总的设置,IF=0则禁止一切中断请求, IF=1则允许中断请求进入。 中断屏蔽寄存器是在中断允 许即IF=1的基础上,对某些引脚的中断请求进行屏蔽的, 8259有8个中断请求输入引脚,中断屏蔽寄存器为8位,分 别对应这8个引脚,设为0则不屏蔽,该引脚的请求可以进 入;而若中断屏蔽寄存器某些位设为1的话,表示屏蔽相应 引脚的请求,该请求就不会进入8259的优先级分析器中。 若中断屏蔽寄存器设为00001111B,则IR0~IR3的请求被屏 蔽,IR4~IR7的中断请求未被屏蔽,可以进入优先级分析 器,由优先级分析器找出其中优先级最高的一个请求,进 而向CPU发出请求。

2020/11/14

11

四:现行指令结束后响应中断 CPU在现行指令结束后响应中断,即运行到最 后一个机器周期的最后一个T状态时,CPU才 采样INTR线。 教材224页(按教材讲)

其响应的流程图如下所示!

2020/11/14

12

2020/11/14

中断锁存器置1

图8-3 中断响应流程图 13

8.2.2 CPU对中断的响应

CPU! 进而又可把一组屏蔽触发器(如8个)组成

一个中断屏蔽寄存器端口, 用输出指令来控

制

其

状

态

!

具有中断屏蔽的接口电路如下!

2020/11/14

8

CPU通过端口和外设进行数据交换

WR读信号

WR写信号

设置中断屏蔽触发器的指令

2020/11/14

图8-2 具有中断屏蔽的接口电路

9

当外设发 STB→数据入锁存器, 中断请求触发器置 1→ 若没有屏蔽则产生 INTR→CPU 满足条件(允许中断; 指令 执行完) 发 INTA →(进入中断服务子程序) 读数据, 发 RD, 和地址→清中断请求触发器, 数据送 D0~D7。

微机原理中断处理过程

外部中断

8086有两条外部中断请求线 1:INTR:可屏蔽中断:简单说就是CPU可以选择响应的中

断!

2:NMI:不可屏蔽中断:简单说就是CPU必须响应的中断 !

2020/况

8 0 8 6 的 中 断 情 况

2020/11/14

CPU响应 中断的条件