用移位寄存器74LS194实现7位串行左移并行转换电路、四位环形计数器

用移位寄存器LS芯片实现扭环形计数器精编版

实验原理

本实验选用的4位双向通用移位寄存器,型号为 74LS194,其逻辑符号及引脚排列如图1所示。

其中D0、D1、D2、D3为并行输入端;Q0、Q1、Q2、 Q3为并行输出端;SR为右移串行输入端,SL为左移 串行输入端;S1、S0为操作模式控制端;CR为异步 清零端;CP为时钟脉冲输入端。

实验原理

实验原理

1)环形计数器 把移位寄存器的输出反馈到它的串行输入端,就可以进行循环

移位,如图2所示,把输出端Q3和右移串行输入端SR相连接,设初 始状态Q0Q1Q2Q3=1000,则在时钟脉冲的作用下Q0Q1Q2Q3将依次变 为0100、0010、0001、1000-----,可见它是一个具有四个有效状 态的计数器,这种类型的计数器通常称为环形计数器。图2电路可 以由各个输出端输出在时间上有先后顺序的脉冲,因此也可作为顺 序脉冲发生器。

n :代表环内包围的输出端的个数;

如果是通过二输入与非门取反馈作移入数据,则为奇数模, M=2n-1

如果是通过非门取反馈作移入数据,则为偶数模,M=2n。

步骤:

1、双向移位寄存器74LS194逻辑功能测试。

清除:先将端接+5V,检查Q端输出情况,再将端接0电平,所有Q端输 出应为0,清零后再将端接+5V。

六、注意事项

注意一定要先查导线,再开始接线。

注意通常电源均按+5V和地接入,每个芯片都需接 入一对电源,为防止遗漏,可把它定为接线的第一 步。注意电源不要接反,否则会烧坏芯片。

不可在接通电源的情况下插入或拔出芯片。

移位寄存器74LS194的清除端( CR)除了清零时将 其置 0外,其它工作状态均应置为“l”。

U3B 74LS04D

U1

2 移位寄存器及其应用

实验七移位寄存器及其应用一、实验目的1.移位寄存器74LS194的逻辑功能及使用方法;2.熟悉4位移位寄存器的应用。

二、实验预习要求1.了解74LS194的逻辑功能;2.用4位移位寄存器构成8位移位寄存器;3.了解移位寄存器构成环形计数器的方法。

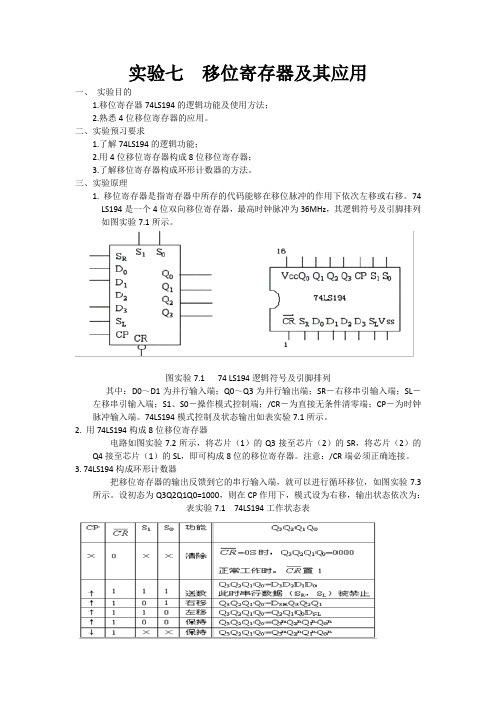

三、实验原理1. 移位寄存器是指寄存器中所存的代码能够在移位脉冲的作用下依次左移或右移。

74LS194是一个4位双向移位寄存器,最高时钟脉冲为36MHz,其逻辑符号及引脚排列如图实验7.1所示。

图实验7.1 74 LS194逻辑符号及引脚排列其中:D0~D1为并行输入端;Q0~Q3为并行输出端;SR-右移串引输入端;SL-左移串引输入端;S1、S0-操作模式控制端;/CR-为直接无条件清零端;CP-为时钟脉冲输入端。

74LS194模式控制及状态输出如表实验7.1所示。

2. 用74LS194构成8位移位寄存器电路如图实验7.2所示,将芯片(1)的Q3接至芯片(2)的SR,将芯片(2)的Q4接至芯片(1)的SL,即可构成8位的移位寄存器。

注意:/CR端必须正确连接。

3. 74LS194构成环形计数器把移位寄存器的输出反馈到它的串行输入端,就可以进行循环移位,如图实验7.3所示。

设初态为Q3Q2Q1Q0=1000,则在CP作用下,模式设为右移,输出状态依次为:表实验7.1 74LS194工作状态表2. 用74LS194构成8位移位寄存器电路如图实验7.2所示,将芯片(1)的Q3接至芯片(2)的SR,将芯片(2)的Q4接至芯片(1)的SL,即可构成8位的移位寄存器。

注意:/CR端必须正确连接。

图实验7.2 8位移位寄存器3. 74LS194构成环形计数器把移位寄存器的输出反馈到它的串行输入端,就可以进行循环移位,如图实验7.3所示。

设初态为Q3Q2Q1Q0=1000,则在CP作用下,模式设为右移,输出状态依次为:图实验7.3 环形计数器图实验7.3电路是一个有四个有效状态的计数器,这种类型计数器通常称为环形计数器。

实验八 移位寄存器及其应用

实验八移位寄存器及其应用一、实验目的1、掌握中规模4位双向移位寄存器逻辑功能及使用方法。

2、熟悉移位寄存器的应用—实现数据的串行、并行转换和构成环形计数器。

二、实验原理1、寄存器使一个具有移位功能的寄存器,是指寄存器中所存的代码能够在移位脉冲的作用下一次左移或右移。

既能左移又能右移的称为双向移位寄存器,只需要改变左、右移的控制信号便可实现双向移位要求。

根据移位寄存器存取信息的方式不同分为:串如串出、串如并出、并入串出、并入并出四种形式。

2、本实验选用的4位双向通用移位寄存器,型号为CC40194或74LS194,两者功能相同,可互换使用,其逻辑符号及引脚排列如图8-1所示。

其中D0、D1、D2、D3为并行输入端;Q0、Q1、Q2、Q3为并行输出端;S R为右移串行输入端,S L为左移串行输入端;S1、S0为操作模式控制端;C R为直接无条件清零端;CP为时钟脉冲输入端。

功能见表8-1。

3、移位寄存器的应用可构成移位寄存器形计数器;:顺序脉冲发生器;串行累加器;可用作数据转换,即把串行数据转换为并行数据等。

本实验研究移位寄存器用作环形计数器和数据的串、并行转换。

⑴环形计数器把移位寄存器的输出反馈到它的串行输入端,就可以进行循环移位,如图8—2所示,把输入端和右移串行输入端相连接,设初始状态Q0Q1Q2Q3=1000,则在时钟脉冲作用下Q0Q1Q2Q3将依次变为0100 → 0010 → 0001 → 1000→……,如表8—2所示,可见它是一个具有四个有效状态的计数器,这种类型的计数器通常称为环形计数器。

图8—2电路可以由各个输出端输出在实践上有先后顺序的脉冲,因此也可作为顺序脉冲发生器。

如果将输出与左移串行输入端相连接,即可达到左移循环移位。

⑵串行/并行转换器串行/并行转换是指串行输入的数码,经转换电路之后变成并行输出。

图8—3是用二片CC40194(74LS194)四位双向移位寄存器组成的七位串/并行数据转换电路。

实验九 移位寄存器及其应用

实验九移位寄存器及其应用一、实验目的1.掌握中规模四位双向移位寄存器的逻辑功能2.熟悉移位寄存器的应用——实现数据的串行-并行转换和构成环形计数器二、实验设备及器件1.数字电路实验箱2.74LS194(CC40194)×2,CC4011(74LS00),CC4068(74LS30)三、实验内容及步骤1.测试74LS194的逻辑功能按图9-5接线,CR、S1、S0、S L、S R、D0、D1、D2、D3、Q0、Q1、Q2、Q3分别接至逻辑电平显示器的输入插口,CP接单次脉冲源。

按表9-5测试(1)清零令CR=0,其它输入为任意状态,这时寄存器输出Q0、Q1、Q2、Q3应均为零(2)送数令1CR,S0=S1=1,送入任意四位二进制数,如D0D1D2D3=abcd,加CP脉冲,观察CP=0、CP由0→1、CP由1→0三种情况下寄存器输出状态的变化,观察寄存器输出状态变化是否发生在CP脉冲上升沿(3)左移令1CR、S1=0、S0=1,由右移串行输入端S L送入二进制数码如1111,=由CP端连续加四个CP脉冲,观察输出端情况,记录之(4)右移令1CR、S1=0、S0=1,由右移串行输入端S R送入二进制数码如0100,=连续加四个CP脉冲,观察输出,记录之(5)保存寄存器预置任意四位二进制数码abcd,然后令1CR、S1=S0=0,加=CP脉冲,观察输出,记录之表9-52、环行计数器自拟实验线路用并行送数法预置寄存器为某二进制数(如0100),然后进行右移循环,观察寄存输出,记入表9-6中表9-63、实现数据的串行-并行转换(1)串行输入-并行输出按图9-3接线,进行右移串入-并出实验,串入数码自定;改接线路用左移方式实现并行输出。

自拟表格,记录之(2)并行输入-串行输出按图9-4接线,进行右移并入-串出实验,并入数码自定。

再改接线路用左移方式实现串行输出。

自拟表格,记录之。

电子测试与实验技术:移位寄存器串并转换

∧

Q0Q 1Q2Q 3

CP D SR

74194

S0

1

S1

RD

D 0 D 1 D2 D 3 D SL

1

10 0 0

START

Q0Q1Q2Q3

1000

0100

0001

0010

2.扭环形计数器

为了增加有效计数状态,扩大计数器的模,可用 扭环形计数器。

一般来说,N位移位寄存器可以组成模2N的扭环形计 数器,只需将末级输出反相后,接到串行输入端。

∧

Q0Q 1Q2Q 3

CP

S0

D SR

74194

S1

RD

D 0 D 1 D2 D 3 D SL

清零

Q0Q1Q2Q3

1

0000

1000

0

1100

1110

0001 0011

0111

1111

3. 实现数据串、并行转换

串行/并行转换是指串行输入的数码,经转换电路之后变换成 并行输出。下图是两片74LS194四位双向移位寄存器组成的 七位串/并行数据转换电路。

实验二十三、移位寄存器

实验目的

1、熟悉中规模4位双向移位寄存 器的逻辑功能

2、用移位寄存器构成串行环行 计数器

实验原理

74LS194或CC40194 是4位双向通用移位寄存器,两者功能相 同,可互换使用,其逻辑符号及引脚排列如图所示。

∧

Q0Q 1Q2Q 3

CP

S0

74194 DSR

S1

RD

D 0 D 1 D2 D 3 DSL

11

1

01

0

↑

串入右移工 作方式

三、实验内容

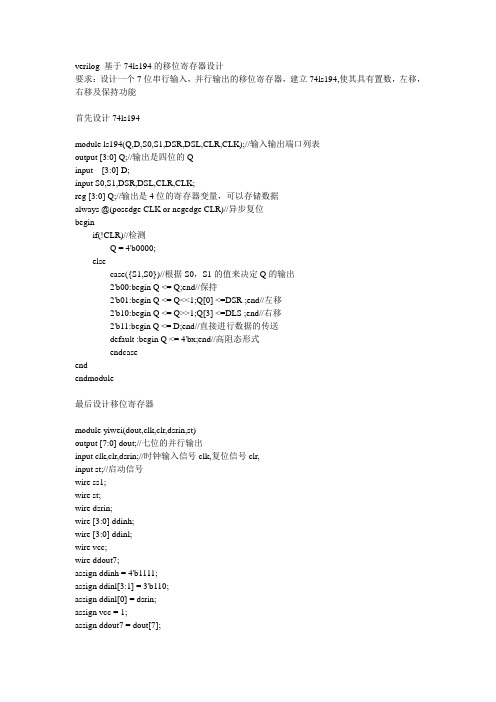

verilog 基于74ls194的移位寄存器设计

verilog 基于74ls194的移位寄存器设计要求:设计一个7位串行输入,并行输出的移位寄存器,建立74ls194,使其具有置数,左移,右移及保持功能首先设计74ls194module ls194(Q,D,S0,S1,DSR,DSL,CLR,CLK);//输入输出端口列表output [3:0] Q;//输出是四位的Qinput [3:0] D;input S0,S1,DSR,DSL,CLR,CLK;reg [3:0] Q;//输出是4位的寄存器变量,可以存储数据always @(posedge CLK or negedge CLR)//异步复位beginif(!CLR)//检测Q = 4'b0000;elsecase({S1,S0})//根据S0,S1的值来决定Q的输出2'b00:begin Q <= Q;end//保持2'b01:begin Q <= Q<<1;Q[0] <=DSR ;end//左移2'b10:begin Q <= Q>>1;Q[3] <=DLS ;end//右移2'b11:begin Q <= D;end//直接进行数据的传送default :begin Q <= 4'bx;end//高阻态形式endcaseendendmodule最后设计移位寄存器module yiwei(dout,clk,clr,dsrin,st)output [7:0] dout;//七位的并行输出input clk,clr,dsrin;//时钟输入信号clk,复位信号clr,input st;//启动信号wire ss1;wire st;wire dsrin;wire [3:0] ddinh;wire [3:0] ddinl;wire vcc;wire ddout7;assign ddinh = 4'b1111;assign ddinl[3:1] = 3'b110;assign ddinl[0] = dsrin;assign vcc = 1;assign ddout7 = dout[7];ls194 u1(.Q(dout[3:0]),.D(ddinl),.S1(ss1),.S0(vcc),.DSR(dsrin),.DSL(vcc),.CLR(clr),.CLK(clk)); ls194u2(.Q(dout[7:4]),.D(ddinh),.S1(ss1),.S0(vcc),.DSR(dout[3]),.DSL(vcc),.CLR(clr),.CLK(clk)); nand u3(ss1,ddout7,st);endmodule。

74LS194芯片资料

单脉冲的提供有两种途径:

实验目的

逻辑箱脉冲源

单脉冲

实验原理

低频信号源TTL 输出(1Hz)

实验内容

注意事项

现代电子技术实验

四、注意事项

1、出现故障应作哪些基本检查? 电源

实验目的

时钟 功能端(Cr 、S1、 S0 ) 数据输入是否正确

实验原理

实验内容

注意事项

2、实验中的环形计数器不具备自启动功能,抗 干扰能力差。改变电路连接时如进入死循环,必 须给电路重新赋初值。

实验目的

DSR

清零 置数

CP

0 1

DR

1 1

DL

1 1

Q0

0 0

Q1

0 1

Q2

0 0

Q3

0 1

实验原理

左移

实验内容

2 3

4

0 0

1

0 0

1

左移

右移

注意事项

右移 保持

5 6

1 0

1 0

现代电子技术实验

2、环形计数器的测试。首先应给寄存器置入初始 值(自拟),之后将工作状态设为对应的串行移 位,完成下表。

现代电子技术实验

移位寄存器的扩展

实验目的

实验原理

ห้องสมุดไป่ตู้

74LS194(1)

实验内容

74LS194(2)

注意事项

串行输入

构成八位右移串行移位寄存器

现代电子技术实验

2、环形计数器(又称循环移位寄存器)

把移位寄存器的串行输入端与输出端相连可以 构成环形计数器。例:DSR和Q3相连,可构成右移环 形计数器。

实验目的

n 2

0 X X

74LS194左右移位寄存器

74LS194左右移位寄存器4位移位寄存器仿真其中,3D、2D、1D、0D为并行输入端;3Q、2Q、1Q、0Q为并行输出端;R S为右移串行输入端;L S为左移串行输入端;1S、0S为操作模式控制端;R C为直接无条件清零端;CP为时钟脉冲输入端。

74LS194有5种不同操作模式:并行送数寄存;右移(方向由3Q→0Q);左移(方向由0Q→3Q);保持及清零。

1S、0S和R C端的控制作用如表3.10.1所示。

表3.10.1:输入输出功能移位寄存器应用很广,可构成移位寄存器型计数器;顺序脉冲发生器;串行累加器;可用作数据转换,即把串行数据转换为并行数据,或并行数据转换为串行数据等。

把移位寄存器的输出反馈到它的串行输入端,就可进行循环移位,如图3.10.2所示。

把输出端0Q 和右移串行输入端RS 相连接,设初始状态3Q2Q 1Q 0Q =1000,则在时钟脉冲作用下,3Q2Q 1Q 0Q 将依次变为0100→0010→0001→1000→……,可见,它是一个具有四个有效状态的计数器,这种类型的计数器通常称为环形计数器。

图3.10.2电路可以由各个输出端输出在时间上有先后顺序的脉冲,因此也可作为顺序脉冲发生器。

图3.10.2四、实验室操作实验内容:1.逻辑功能验证移位寄存器(1)将两块74LS74集成片插入IC 空插座中,按图41(a)连线,接成左移移位寄存器。

接好电源即可开始实验。

先置数据0001,然后输入移位脉冲。

置数,即把Q3、Q2、Q1、Q置成0001,按动单次脉冲,移位寄存器实现左移功能。

(2)按图42(b)连线,方法同(1)则完成右移移位功能验证。

(a)左移移位(b)右移移位图41 D触发器组成移位寄存器的实验线路图(1). 并行输入:参阅图 3.10.3,设计画出实验电路图,在THD-1型(或Dais-2B型)实验台上将实验线路搭好。

根据74LS194功能表3.10.1要求,进行并行输入实验,并填写表3.10.2。

74LS194

74LS194中规模移位寄存器作业12-18电子技术教研室数字电路电子技术教研室数字电路移位寄存器寄存器寄存器的分类一、寄存器(用四块D触发器构成)若输入:100100001、电路结构存入:10012、工作原理存数指令CPQ0Q1Q2Q3D0D1D2D31DR1DR1DR1DRRD二、移位寄存器1、左移位电路组成(从Q3向Q0移)Q0端是串行输出端;DIL是左移数据输入端;1DC1FFDQ31DC1FFCQ21DC1FFBQ11DC1FFAQ0CPDILQ0Q1Q2Q3端是并行输出端。

2、工作过程例如:要移入D0D1D2D3左移状态表Q0Q1Q2Q3DILCP顺序XXXD0XX D0D1XD0D1D2D0D1D2D34个CP过后,D0D1D2D3移入D01D12D23D34Cr:异步清零端S1,S0:工作方式控制端SL,SR:移位数据输入端D0D1D2D3:并行数据输入端Q0Q1Q2Q3:寄存器输出四位双向移位寄存器74LS194(一)逻辑符号Q0Q1Q2Q3SRD0D1D2D3SLS1S0CPCr74LS19474LS194功能表输入输出Q0Q1Q2Q30φφφφφφφ10φφφφφφ1↑φd0……d311φ0000保持d0d1d2d31QQQ1↑1φφ01φ0n1n2n1↑0φφ01φ0Q0nQ1nQ2nQQQ1↑φφφ1011n2n3n11↑φφφ100QQQ1n2n3n0RCPSRD0……D3SL1φφφφ00φ保持S1S0S1S074LS194功能表1.当Cr=0时,异步清零2.当S1S0=00时,保持3.当S1S0=01时,右移且数据从SR端串行输入4.当S1S0=10时,左移且数据从SL端串行输入5.当S1S0=11时,并行置数(二)功能Q0Q1Q2Q3SRD0D1D2D3SLS1S0CPCr74LS194CPQ1Q2Q3Q4101112d00113d1d0014d2d1d0050111(三)应用1、实现数据的串/并转换Q0Q1Q2Q3SRD0D1D2D3SLS1S0CPCr74LS194串行输入d0…d2Q1Q2Q3Q41CP11Q0Q1Q2Q3SRD0D1D2D3SLS1S0CPCr74LS194Q0Q1Q2Q3SRD0D1D2D3SLS1S0CPCr74LS194串行输入d0….d61Q1Q2Q3Q4Q5Q6Q7Q811Q0Q1Q2Q3SRD0D1D2D3SLS1S0CPCr74LS19401Q0Q1Q2Q31000010000100001M=4的环形计数器2、构成移位型计数器例、构成M=4 的环形计数器将移位寄存器的某一级输出直接反馈到第一级串行输入端Q0Q1Q2Q3SRD0D1D2D3SLS1S0CPCr74LS19401Q0Q1Q2Q3SRD0D1D2D3SLS1S0CPCr74LS1941>11000Q0Q1Q2Q300001000110011101111011100110001例:构成M=8的扭环形计数器Q0Q1Q2Q3SRD0D1D2D3SLS1S0CPCr74LS19401将移位寄存器的某一级输出取反后反馈到第一级串行输入端Q0Q1Q2Q3SRD0D1D2D3SLS1S0CPCr74LS19401Q0Q1Q2Q3SRD0D1D2D3SLS1S0CPCr74LS1941&0111Q0Q1Q2Q300001000110011101111011100110001M=7的扭环形计数器例:分析图示电路,说明其逻辑功能。

第6章 时序逻辑电路-习题答案

第六章 时序逻辑电路6-1 分析题图6-1所示的同步时序电路,画出状态图。

题图6-1解: 11221211n n n n J K Q T Q Z Q Q ====,,,,11111111212n n n n nn n nQ J Q K Q Q Q Q Q Q +=+=+=+122212n n n n Q T Q Q Q +=⊕=⊕,状态表入答案表6-1所示,状态图如图答案图6-1所示。

答案表6-1答案图6-16-2 分析题图6-2所示的同步时序电路,画出状态图。

题图6-2 解:按照题意,写出各触发器的状态方程入下:11J K A ==,21n J Q =,21K =,1212n n nQ Q Q +=,111n n Q A Q +=⊕状态表入答案表6-2所示,状态图如图答案图6-2所示。

答案表6-2答案图6-2Q 2n Q 1n Q 2n+1 Q 1n+1 Z0 0 0 1 1 0 1 1 0 1 1 1 1 1 0 0 0 0 0 1A Q 2n Q 1n Q 2n+1 Q 1n+1 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 0 0 1 1 0 0 0 1 0 1 1 0 0 1 0 0CLK D 1D 2D 3Q 3Q 2Q 1Q 2Q 3Q 1Q 1Q 2Q 3&6-3分析题图6-3所示的同步时序电路,画出状态图。

题图6-3解:按照题意,写出各触发器的状态方程入下:1112213232131n n n nn J K T J K Q Q T J Q Q K Q ========1,,, 133********n n n n n n n nQ J Q K Q Q Q Q Q Q +=+=+ 1222132n n n n nQ T Q Q Q Q +=⊕=⊕ 1111111n n n n Q T Q Q Q +=⊕=⊕=答案表6-3答案图6-36-4 在题图6-4所示的电路中,已知寄存器的初始状态Q 1Q 2Q 3=111。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

数字电子技术基础实验

实验项目:移位寄存器

班级:电气1804姓名:学号:0121811350304

上课时间:2020年6月13日

一、本项目的实验目的:

1.掌握4位双向移位寄存器的逻辑功能和使用方法;

2.熟悉用移位寄存器和计数器的应用.

二、实验内容及步骤:

1.7位串行/左移并行转换电路图:用2个移位寄存器(74LS194)和门电路(不限制)实现出7位串行/左移转换电路,其中用连续脉冲触发,选用合适的频率。

1)设计电路图:

2)分析电路的工作原理:

如图,设从左到右74LS194的输入端分别为D0-D7,对应输出端为Q0-Q7,D0-D6接“1”,D7接“0”,对应为11111110。

两S1接“1”,Q0和Q1相与再非运算,接入两S0。

左边SL接Q4,将两个74LS194级联起来,右边SL接输入,即串行输入。

开始时,由于Q0和Q1为“0”,经过变换向两S0输入“1”,又S1为“1”,Q0-Q7被置数为11111110,其中Q0和Q1相与后作为一个信号输出,即并行输出实际为1111110,7个信号。

下一个上升沿到来时,已有Q0和Q1的输出经运算向两S0输入“0”,即S1=1,S0=0,输出开始左移,设右边的输入一直是SL=1,那么输出变成1111101。

接下来一直左移,直到第一个“0”信号移到Q1,这时,输出是0111111,

Q0=1,Q1=0,向两S0输入1,又S1=1,电路重新置数为1111110。

以上为一个循环,一个循环经过7个时钟脉冲,有7个输出状态,并且输出信号左移,也实现了串行输入,并行输出,所以该电路是7位串行/左移并行转换电路。

3)清零后观察输出状态,记录输出结果填入表中。

CP Q0Q1Q2Q3Q4Q5Q6Q7功能

000000000清零

111111110置数

211111101送数

311111011

411110111

511101111

611011111

710111111

801111111

911111110置数

2.四位环形计数器:用一片移位寄存器(74LS194)及门电路(不限制)设计具

有自启动功能的、有效状态分别为1000,0100,0010,0001(Q

0Q

1

Q

2

Q

3

)的四位右

移环形计数器,其中用连续脉冲触发,选用合适的频率。

1)设计电路图:

2)状态转移图:。