CPU供电芯片datasheet(PWM部分)

SM7025 datasheet

SOP8

-7-

以上公式合并,可得到:

I D = G ID • (

从上式可以看出,IFB 电流大,ID 的电流就小;IFB 电流小,ID 的电流就大。当 IFB 的电流大于(0.23V / R2) 时,芯片会关闭 PWM,同时芯片会自动进入突发模式。

-5-

SM7025AC/DC PWM 功率开关 TOISIWV1.0

管脚图

SOP8

输出功率表

输入电压 最大电流 SOP8 12V 18V 85Vac~265Vac 150mA 150mA 180Vac~265Vac 200 mA 200 mA

注:芯片 5、6、7、8 脚为芯片散热脚,PCB Layout 过程中注意增加散热措施。

12V 典型示意电路图

4 DRAIN

2 HVDD

-3-

SM7025AC/DC PWM 功率开关 TOISIWV1.0

功能表述

R1 22Ω/2W

IN4007 L1 1mH

GND 8 GND 7 GND 6

GND

GND 5

D3 BYV26C

90~264Vac

+ RV 10D471 C1 4.7uF/400V + C2 4.7uF/400V

C4 470uF/25V C3 + 1uF/50V

+

+

1 EN

3 NC

+

N +12V

应用领域

电磁炉、电饭煲、电压力锅等 小家电产品电源

18V 典型示意电路图

L

GND 8 GND 7 GND 6 GND 5

T1

ACIN N +

SM 7025

4 DRAIN 2 HVDD 1 EN 3 NC

EUM6861 Datasheet

18VDESCRIPTIONEUM6861/A/B is a fan motor driver for the single coil brushless DC motor. With its high efficient direct PWM control mode, EUM6861/A/B controls the speed of brushless DC motor with a built in HALL IC interface. EUM6861/A/B is suitable to drive variable speed motors for personal computer’s power supply radiation fans and CPU coolers.EUM6861/A/B integrates PWM fan speed control, minimum speed mode, soft start, fan tachometer, lock protection, auto restart and Hall Bias functions. PWM mode controls fan speed in low noise and low vibration ways by adjusting RCTL voltage. EUM6861/A/B can set minimum fan speed by presetting RMIN voltage. With soft start function, EUM6861/A/B can drive motor from slow speed to fast speed in a settable time by setting the external capacitor between SS and GND. If a fan motor is stalled by the external force or obstacles, overdrive current may incur coil overheat and burning. To prevent motor from overheating, the lock protection circuit shuts down the internal power devices for a few seconds after the motor lock is detected. Then the auto restart circuit resumes to power up the internal power devices. If the lock persists, EUM6861/A/B shuts off power devices for a few seconds. The lock protection delay time is externally programmable by a capacitor. EUM6861 has built in motor rotation speed feedback (FG) output, motor rotation detection (RD) output and Hall sensor bias output.Application Circuit z Built in 18V Full-wave Motor Driver for Fan Motorz Built in Input Surge Protection, No Zener Diode Needz External Programmable Soft Start and Soft Restart Functionz Wide Input Range 3V~18V z PWM Fan Speed Controlz Programmable Minimum Fan Speed z Built in Soft Switching Function z Built in Hall Biasz Lock Protection and Auto Restartz Fan Rotation Speed Feedback FG Output (EUM6861/B)z Fan Rotation Detection RD Output (EUM6861/A)z Thermal Shutdown Protectionz Available in TSSOP-16 and TDFN-14 Packages zRoHS Compliant and 100% Lead (Pb)-Free Halogen-FreeAPPLICATIONSz Personal Computer’s Power Supply Radiation Fans and CPU CoolersFigure 1. TSSOP -16 Typical Application CircuitApplication Circuit (continued)Figure 2. TDFN-14 Typical Application Circuit Functional Block DiagramFigure 3. Functional Block DiagramPin ConfigurationsPackage TypePin Configurations Package TypePin ConfigurationsEUM6861 TSSOP-16EUM6861A TDFN-14EUM6861B TDFN-14Pin DescriptionPIN EUM6861EUM6861AEUM6861BDESCRIPTIONPGND 1,16-- Power device groundOUT2 2 1 1Power device output terminal 2. Connect OUT2 to one side ofthe motor3 - - Power supply of internal control circuitry and power devicesVCC- 3 3 Power supply of internal control circuitryRMIN 4 4 4 Motor minimum rotation speed control RCTL 5 5 5 Motor rotation speed control CPWM 6 6 6 External capacitor connection input for PWM OSC FG 7 - 7 Rotation speed feedback output RD 8 7 - Rotation detection output IN+ 9 8 8 Hall sensor positive input HB 10 9 9 Hall sensor bias output IN- 11 10 10 Hall sensor negative input SS 12 11 11 Soft start time setting terminal CT 13 13 13 Lock protection time setup input14 - - Analog control circuit groundGND - Thermal Pad ThermalPadIC groundOUT1 15 14 14Power device output terminal 1. Connect OUT1 to the otherside of the motor.PVCC - 2 2 Power supply of power devices REG - 12 12 6V regulatorOrdering InformationOrder Number Package Type Marking Operating Temperature Range-30°C to +90°C EUM6861QIR1TSSOP-16 xxxxxEUM6861-30°C to +90°C EUM6861AJIR1TDFN-14xxxxxM6861-30°C to +90°C EUM6861BJIR1TDFN-14xxxxx6861BEUM6861/A/B □□□□Lead Free Code1: Lead Free, Halogen Free 0: LeadPackingR: Tape & ReelOperating temperature rangeI: Industry StandardPackage TypeQ: TSSOPJ: TDFNPower DissipationFigure 4. TSSOP-16 PackageFigure 5. TDFN-14 PackageAbsolute Maximum Ratings (1)VCC, RD, FG , OUT1, OUT2 to GND ------------------------------------------------- -0.3V to 30V RMIN, RCTL to GND --------------------------------------------------------------------- -0.3V to 7V CPWM, SS, CT, IN+, IN-, HB to GND ---------------------------------------------- -0.3V to 6V PGND to GND ------------------------------------------------------------------------- -0.3V to +0.3V IOUT1, IOUT2----------------------------------------------------------------------------------- 1.0A IHB, IFG , IRD ------------------------------------------------------------------------------------- 10mAMaximum Junction Temperature ------------------------------------------------------------ +150°CLead Temperature (Soldering, 10sec.) ------------------------------------------------------ +300°C Package Thermal Resistance θJA (TSSOP-16) --------------------------------------------- 157°C/W Package Thermal Resistance θJA (TDFN-14) ---------------------------------------------- 110°C/W Power Dissipation P D @ T A =+25°C (TSSOP-16) ------------------------------------------ 0. 8W Power Dissipation P D @ T A =+25°C (TDFN-14) ------------------------------------------- 1.14W Storage Temperature --------------------------------------------------------------- -55°C to +150°C ESD RatingsHuman Body Mode ------------------------------------------------------------------------------- 2kVThermal Shut Down----------------------------------------------------------------------------- 180°C Recommended Operating Conditions (2)Supply V oltage VCC --------------------------------------------------------------------- 3V to 16V Threshold Input V oltage RCTL, RMIN ------------------------------------------------ 0V to 6V Hall Input V oltage Range IN+, IN- ------------------------------------------------------ 0.2V to 3VOperating Temperature Range ------------------------------------------------------ -30°C to +90°CNote (1): Stress beyond those listed under “Absolute Maximum Ratings” may damage the device. Note (2): The device is not guaranteed to function outside the recommended operating conditions.Electrical CharacteristicsSpecifications in standard type face are for T A =+25°C, and those with boldface type apply over the full operatingtemperature range T A =-30°C ~+90°C. VCC =12V unless otherwise specified.EUM6861/A/BSymbols Parameters Conditions Min. Typ. Max.UnitICC1 Rotation mode - 3.2 5ICC2 Operating current Lock protection mode - 1.6 3 mAHall Input and Hall Bias VHNHall input sensitivityZero to peak (Offset & Hysteresisincluded)10 15 mV VHB HB Output V oltage IHB =5mA1.1 1.2 1.3 mV Output VOL Output lower side saturation Io=200mA 0.10 0.13VOH Output upper side saturation Io=200mA 0.20 0.26VOL Output lower side saturation Io=500mA 0.25 - VOH Output upper side saturation Io=500mA 0.54 - VSoft Start Block ISS SS pin discharge current VSS = 3.6V 0.37 0.5 0.64μA PWM BlocksFPWM CPWM OSC frequency CP = 100pF 19 25 28 KHz VCRL CPWM low level voltage - 2 - V VCRHCPWM high level voltage-3.55-VElectrical Characteristics (continued)Specifications in standard type face are for T A =+25°C, and those with boldface type apply over the full operating temperature range T A =-30°C ~+90°C. VCC =12V unless otherwise specified.EUM6861/A/BSymbols Parameters Conditions Min. Typ. Max.UnitLock Protection Block ICT1 CT charge current VCT = 0V 1.6 2 2.3 μA ICT2 CT discharge current VCT = 4.2V 0.16 0.2 0.25μA RCT Ratio of charge current to discharge current RCT = ICT1 / ICT2 8.5 10 11 - VCTH CT high level voltage 3.54 3.9 4.2 V VCTL CT low level voltage1.78 1.8 1.82V FG & RD Signal OutputVFG FG & RD pin low voltage IFG = 5mA 0.1 - V IFGLFG & RD pin leak currentVFG = 7V5μARegulator OutputVREG Regulator Output V oltage IREG =5mA5.76.0 6.3 VApplication NotesHall Sensor ConnectionFigure 6. Hall Sensor InputsHall signal input terminals (H+、H-)Figure 7. Hall Sensor Input Voltage RangeSet Hall sensor input signal range 0.2V to 3V by adjusting the Hall input level setting resistor R1. In the case of long board wiring pattern from hall element to hall signal input terminal, connect a capacitor between IN+ and IN- to avoid noise. The amplitude of Hall input signal is recommended to be 60mV or higher due to the Hall input amplifier 20mV hysteresis. The Hall bias is 1.2V.VCC Bypass CapacitorConnect a ceramic capacitor 0.47μF or more between VCC and GND to absorb kick back voltage resulting from the high side re-circulation current.GND and PGND LineGND is connected to internal analog control circuits, and PGND is connected to power devices. Connect GND to PGND at only one place on the PCB board. PWM Oscillator FrequencyThe PWM OSC frequency is programmed by the CP capacitor. A 100pF CP sets frequency 25 KHz. The PWM OSC ramp CPWM swings between 2V to 3.55V. PWM Control Speed ModePWM control mode works by comparing the voltage of RCTL and CPWM. When RCTL is low, one side upper power device and the other side lower side power device are turned on to charge the motor coil. When RCTL is high, the upper side power device is turned off. The motor coil current is re-circulated between lower side power devices. The lower RCTL is, the bigger the output duty is. Big coil current makes motor run fast. FG output feedbacks motor rotational speed. The motor coil is charged all the time and motor speed becomes full speed when RCTL voltage is lower than 2V.Soft Start TimeConnect a capacitor between SS and GND to set soft start time. EUM6861/A/B drives a motor from slow speed to fast speed during soft start time which is set by the external capacitor between SS and GND. Floating SS pin if soft start function is not used. If motor start current is too big, please increase capacitor between SS and GND to make start time longer and start current smaller. If motor start current is too small to run, please decrease capacitor between SS and GND to make start time shorter and start current bigger.Minimum Speed ModeMinimum speed of motor is set by the RMIN voltage. When RCTL voltage is higher than RMIN voltage, the lowest duty is set by comparing RMIN and PWM oscillator ramp CPWM voltage. When minimum speed mode function is not used, connect RMIN to RCTL. If RMIN pin is connected to RCTL and the RCTL/RMIN voltage is above 3.6V, EUM6861/A/B PWM duty cycle is 0% and motor stops.Lock Protection and Auto RestartWhen the motor is locked, the EUM6861/A/B outputs will be disabled by the lock protection function. After a few seconds, the auto restart circuit will restart the motor. If the motor lockup persists, the lock protection will keep EUM6861/A/B outputs off until the lock removes. Rotation detection output RD pin is open-drain output, and RD is internally pulled down during rotation mode. When motor lock is detected, RD pin becomes high impedance. See Figure 8.Figure 8. Lock Protection and Auto RestartEUM6861/A/B Operation Truth Table(CPWM-H=CPWM > RCTL, CPWM-L=CPWM < RCTL)CT CPWM IN+ IN- OUT1 OUT2 FG RDModeL H H L LH H L L H OFFRotation (Drive)L H L L LL L H L L L OFF ONRotation (Recirculation)L H L L LH - H L L L OFF OFF Lock ProtectionPackaging InformationTSSOP-16MILLIMETERS INCHES SYMBOLSMIN. MAX. MIN. MAX.A - 1.20 - 0.047A1 0.00 0.15 0.000 0.006b 0.19 0.30 0.0070.012E1 4.40 0.173D 5.00 0.197E 6.20 6.60 0.2440.260e 0.65 0.026L 0.45 0.75 0.0180.030DS6861/A/B Ver1.2 Oct. 201010EUM6861/A/B DS6861/A/B Ver1.2 Oct. 201011TDFN-14MILLIMETERS INCHESSYMBOLS MIN. MAX. MIN.MAX.A 0.70 0.80 0.028 0.031A1 0.00 0.05 0.000 0.002b 0.20 0.35 0.008 0.014E 2.90 3.10 0.114 0.122D 3.90 4.10 0.153 0.161 D1 3.250.128 E1 1.650.065 e 0.50 0.020L 0.30 0.50 0.012 0.020。

CPU供电详细说明

一、识别CPU供电电路的元件CPU供电电路主要有 5种元件PWM芯片 MOSFET 电感电容1:PWM芯片(脉宽调制芯片)CPU供电电路指挥官ADP3228INTELCPU供电4相华硕P35/P45主板常用EPU=ADP3228华硕打磨标记改为EPUX58也用ISL6336AINTELCPU供电6相微星/技嘉P45/X58高端主板用ISL6334INTELCPU供电4相微星/技嘉P45主板常用STL6740LAMD CPU供电4相微星/华硕AM3/AM2+新主板用ISL6324AMDCPU供电4相微星/华硕/技嘉AM2+主板常用PWM芯片识别CPU核心电压,规定供电相数、调整电压和电流,指挥MOS工作 ISL6336/6334和ST L6740L支持供电相数变换(APS)2:驱动芯片(Driver-IC)驱动MOSFET工作PWM芯片通过驱动芯片驱动MOSFET工作驱动芯片型号由PWM芯片规定有的PWM芯片内部整合驱动芯片3:MOSFET大功率晶闸管(开关管/场效应管)MOSFET其实就是一个开关,开启时允许电流通过,关闭时不允许电流通过。

常用MOSFET是单颗的,封装形式有D型和Power型。

1相供电回路至少有2颗,1颗输入/1颗输出(1进1出),还有3颗(1进2出),4颗(2进2出)。

4:电感延迟电压/电流上升/下降电感的特性是当电流通过时,输出的电压缓慢上升,比如输入12V,输出是从0V慢慢上升到12V。

CPU供电就是利用电感的特性把12V降到1.xxV5:电容:滤波和蓄电池富士通固态电容日本化工固态电容电感输出的电流对电容充电,经过电容的电流被滤波,滤出一些交流成分,电流曲线更平滑。

电容可以充电/放电,就像一个大的蓄电池,存储电能。

经过电感的电流给电容充电。

当CPU负载瞬时增大,电容可以瞬时提供大电流(MOSFET和电感的反应时间较慢)。

供电电路的电容是电解电容。

以前常用的是液态铝电解电容(导电的电解液是液态的),当电容长期工作在高温状态下,电解液会热膨胀,发生爆裂。

PWM电路学习

PWM电路学习下面以CPU-core 部分电路为例来说明这部分电路,将分三个部分介绍:1)输出滤波电感的选择2)输入/输出电容的选择3) MOSFET的失效分析第一部分输出滤波电感的选择在PWM这部分电路中,我认为电感的选择非常的重要,它决定了这部分电路系统其他元件的选择和搭配,比如输入/输出电容的选择以及MOSFET的选择。

当然电感的选择是由系统的需要来决定的,在我们NOTEBOOK电路中,它主要是由PWM电路的输入电压和负载的loading来决定的。

一旦决定了PWM电路的输入电压和负载的额定电压及电流,还有电感在电路中的工作模式,就可以确定电路中需要电感值的范围,至于最终选择多大值的电感,这要根据具体选择电感的参数和设计的裕度来考量。

在这里先介绍一下电感在电路中的工作模式,用于开关电源中的电感,有两种工作模式:1)电感电流断续模式-----瞬时安匝在每个开关周期有一部分时间停留在零状态。

2)电感电流连续模式-----在一个开关周期内,电感的安匝没有停留在零的时间。

这两种不同的工作模式由于自身的特点决定了应用范围,在电感电流连续模式中,纹波电流通常非常小,线圈的交流损耗和磁芯交流损耗一般不重要,这点在notebook应用中很重要,因为低损耗代表高效率和温升小。

下面以8050MP来说明滤波电感的选择:电感值的选取The inductance value is chosen first based on a 40% ripple current assumption. The highest value of ripple current occurs at the maximum input voltage. The minimum inductance for 40% ripple current is:8050MP用25W和Vcore=1.5V的CPU,所以PWM应满足输出的最大电流Imax=25/1.5=16.7A这是CPU最大loading时需要的电流值,考虑电流的de-rating,设计时需满足的电流为Imax=16.7/80%=20.8A工作频率f是由电路设定的,FREQSET pin的电压决定IC的工作频率,由电路图可得FREQSET pin的电压:V=5*2.2/(2.2+10)=0.9V由LTC3734 SPEC 可以得出此时的工作频率为270K所以;L>(1.5*(1-1.5/19))/(270k*40%*20.8)=0.615uH 电路上用0.68uH 是在范围内.电感的选取由以下条件决定:(1) Total output ripple current(2) DC saturation current(3) Converter response time to load transient.(4) Inductor DCR value以8050MP CPU-core电路和使用IHLP-5050CE系列电感来看:1) 满足L>0.615uH,有0.68到10uH 12种可选择2) 满足最大输出电流时电感不饱和,有0.68到4.7uH 8种可选择3) 最优温度和电感功耗(DCR)的,有0.68到1.0uH所以最优的选择是0.68;0.82;1.0uH 三种.如果选择的电感值小于计算的电感值,又会出现什么样的情形呢?这要分两种情况来分析:1)选择的电感值小,但电感还是工作在电流连续模式,这样电感的输出纹波就会增大这可以从上面的公式中看出,纹波大必然会加重输出电容的负担,这就会影响系统的可靠性。

LN5R04D_Datasheet_新浩科技

最大 50 10.5

單位 uA mA V V V V

Copyright(C) 2010 Lii Semiconductor

-4-

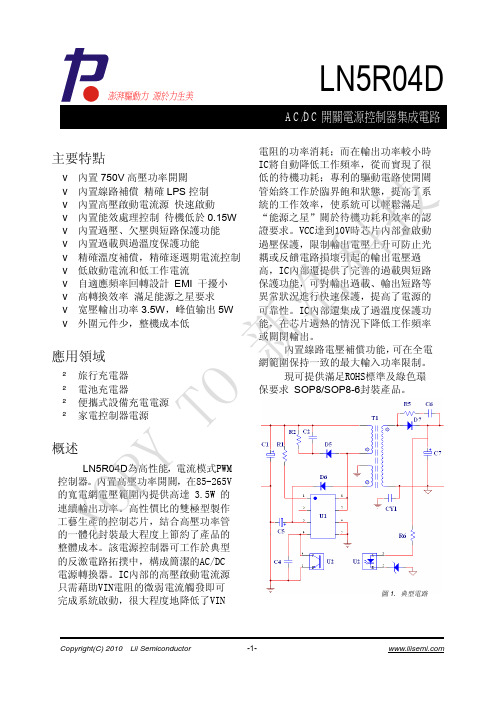

澎湃驅動力 源於力生美

LN5R04D

功能描述

1、啟動控制

系統上電時,輸入直流高壓經過 VIN

動調整和穩定。

4、VCC 過電壓保護電路

電阻進入芯片內部,產生觸發信號 IG,同 時高壓直流經過變壓器初級繞組施加到芯 片內部與 HV 端子相連的高壓電流源 ICHG 電路,IG 觸發電流源工作產生初始充電電 流 ICHG 經過內部電源管理單元對 VCC 電 容進行充電,當 VCC 電壓被充電至 8.9V 時控制電路將依次打開參考電路、振盪器 電路等,輸出驅動開始輸出脉衝打開功率 開關,芯片啟動結束,開始進入正常工作。

准,這樣將允許設計者在設計方案時不 必留有太大的餘量即可滿足較大的工作

Y 溫度範圍,提高電路的使用安全性。 XOP 最大開關電流已由芯片設定,無需

Ø 過溫度保護

IC內部集成了精確的過溫度保護功 能。在芯片內部溫度達到140℃時,熱保 護電路動作,內部拉低FB電壓。減小開 關電流的峰值,同時降低開關頻率,隨

振盪頻率 頻率隨電壓變化率 頻率隨溫度變化率

頻率回轉範圍

PWM 部分:

符號

說明

DMIN DMAX

最小開通占空比 最大開通占空比

電流限制部分:

符號

說明

ILIMIT GVCC TILD TLEB

峰值開關電流 電流抑制比 傳輸延時 前沿消隱時間

反饋部分:

XOPY 符號

說明

IFB RFB GVCC

反饋上拉電流 反饋下拉電阻 電源抑制比

Copyright(C) 2010 Lii Semiconductor

STM32F103_Datasheet_(Chinese_V4.0)

2.1 器件一览

STM32F103 增强型

表二 器件功能和配置(STM32F103xx增强型)

外设

STM32F103Tx

闪存(K字节) 32 64

RAM(K字节) 10 20

通用 定时器

高级231来自SPI11

I2C

1

1

通信 USART 2

2

USB

1

1

CAN

1

1

通用I/O端口

26

12位同步ADC

2 10通道

2.1 器件一览 ................................................................................................................................4 2.2 概述 ........................................................................................................................................5 3 管脚定义 ...........................................................................................................................................11 4 存储器映像 .......................................................................................................................................19 5 电气特性 ...........................................................................................................................................20 6 封装参数 ...........................................................................................................................................20 7 订货代码 ...........................................................................................................................................20 7.1 后续的产品系列 ..................................................................................................................21 8 版本历史 ...........................................................................................................................................21 附录A 重要提示.....................................................................................................................................22 A.1 PD0和PD1在输出模式下 .......................................................................................................22 A.2 ADC自动注入通道 .................................................................................................................22 A.3 ADC的混合同步注入+交替模式...........................................................................................22 A.4 ADC通道0 ...............................................................................................................................22

英飞凌 ICE5xSAG 第五代固定频率PWM控制器 数据表

ICE5xSAG采用 DSO-8 封装的固定频率 PWM 控制器产品亮点• 可选进入和退出待机功率电平的增强型主动突发模式,其最低待机功率小于 100 mW• 数字降频模式,提高整体系统效率 • 借助共源共栅配置实现快速启动 • 支持频率抖动和软栅极驱动,实现低 EMI • 集成误差放大器• 具备交流输入过压保护,提供全面防护 • 无铅电镀、无卤模塑化合物,符合 RoHS 标准特性• 可选进入和退出待机功率电平的增强型主动突发模式• 数字频率降低,提高整体系统效率 • 借助共源共栅配置实现快速启动• 支持 DCM (非连续导通模式)和 CCM (连续导通模式)运行,具备斜坡补偿• 支持频率抖动和软栅极驱动,实现低 EMI • 内置数字软启动• 集成误差放大器,在非隔离反激式架构中支持直接(原边)反馈• 具备交流输入过压保护、V CC 过压、V CC 欠压、过载/开路及过温保护机制,提供全面防护• 所有保护功能均处于自动重启模式 • 受限的V CC 短接至地的充电电流应用• 适用于家用电器/白色家电、电视、电脑及服务器的辅助电源• 蓝光播放器、机顶盒和 LCD/LED 显示器产品验证完全符合 JEDEC 工业应用标准要求描述ICE5xSAG 是第五代固定频率 PWM 控制器,支持共源共栅配置,并针对离线开关模式电源进行了优化。

其共源共栅配置亦可实现快速启动。

器件通过降低频率并软化栅极驱动和频率抖动,进而在低负载和 50% 负载之间实现低 EMI 效果,并提高了效率。

产品支持主动突发模式,可选进入和退出待机功率,输出电压纹波小且可控,因此可在待机模式下具备较高的灵活性和极低功耗。

此外, ICE5xSAG 有宽的供电电压工作范围 (10.0~25.5 V),功耗较低。

产品具备诸多保护功能,提供可调交流输入过压保护,可在故障情况下为电源系统提供全面防护。

凭借上述特性,第五代 ICE5xSAG 系列得以成为市面上用于固定频率反激式转换器的理想 PWM 控制器。

TL494 datasheet

测试条件 占空度为零 V (FEEDBACK) = 0.7 V

(1)除特殊申明,都是在25摄氏度下测量的

整个芯片

参数 待机电流

平均上电电流

测试条件 R T = Vref, 所有的输入输出端口全开

VCC = 15 V VCC = 40 V

VI (DEAD-TIME CTRL) = 2 V, See Figure 1

(1)除特殊申明,都是在25摄氏度下测量的

TL494C TL494I

单

MIN MAX

TYP(1)

位

2

mV

2150

nA

02.250

μA

-0 .3 1 Vcc - 2

70

V

95

dB

800

kHz

65

80

dB

0.3

0.7

mA

-2

mA

输出部分

参数

集电极偏置电流 发射极偏置电流

集电极-发射极电压 输出控制输入电流

M I3 3.3

UNIT A %

V

M IN MAX

0.3

TYP (1)

4 4.5

0.7

UNIT V m A

M IN MAX

TYP (1)

6 10 9 15

7. 5

单位

m A

m A

8

(1)除特殊申明,都是在25摄氏度下测量的

开关特性

温度 25 摄氏度

参数 上升沿时间 下降沿时间 上升沿时间 下降沿时间

1 1IN+

2 1IN-

3 FADEBACK 4

DIC 5

CT 6

RT 7

GND 8

C1

16 2IN+

GR8876 Datasheet-CN

引线温度 和 封装,锡焊, 秒 ℃ (SOP-8 DIP-8

10 ) ----------------------------------------------------------------------- 230

引线温度 所有无铅封装,锡焊, 秒 ℃ (

10 ) --------------------------------------------------------------------------- 260

3

GR8876

℃ 除非特殊说明 电气参数 (TA = +25

, VCC = 15.0V)

参数

高压供电 (HV Pin)

高压电流源 (Vcc = 0V)

关断状态下漏电流

电源电压 启动电流

工作电流(OUT pin外挂1nF电容负载), Vcomp = 0V

工作电流 外挂 电容负载 (OUT pin 1nF

前沿消隐(LEB)

功率 MOSFET 每开关一次,检测电阻上就不可避免

的产生一个开启尖峰。因此,芯片内置了 350ns 的前

2009.08 Ver. 1.2 Copyright Grenergy OPTO, Inc.

1

芯片脚位图

GR8876

顶视图

脚位描述

脚位 符号

1

RT

2

COMP

3

CS

4

GND

5

OUT

6

VCC

7

NC

8

HV

描述 外接一电阻到地设定正常工作频率 电压反馈脚,通过连接至光耦来控制占空比 电流检测脚,用来检测 MOSFET 上的电流 地 芯片的输出以驱动外部 MOSFET 电源供电输入端 空脚 将这一脚接至储能电容的正极,芯片内置的高压电流源就将为芯片提供启动电流。当 芯片启动后,高压电流源的回路就会关断以减小损耗

主板CPU的PWM供电电路路图

主板CPU的PWM供电电路路图这是一个三相供电图,Q1和Q2组成一相,Q3和Q4组成一相,Q5和Q6组成一相。

每一相都是在PWM控制IC(CS5301)的控制下,轮流导流的,而不是同时导通。

CS5301通过Gate1(H)脚输出控制Q1导通与截止,通过Gate2(L)输出控制Q2的导通与截止。

当Gate1(H)输出时,Q1导通,此时Q2截止(Gate1(L)无输出),+12V端L4及滤波电容C15和C16的储能,通过Q1释放并向L1及其后并联的滤波电容充电,L1储能。

当Q1截止Q2导通时,L1上的储能通过Q2向滤波电容充电。

一相完成一个导通截止期后,下一相再工作。

多相轮流工作的好处是,功率管有更多的休息时间,减小了发热。

有的主板为减小发热,每一相上还并联一个MOS管,或预留有并联的位置。

(发给媒体评测的板子就焊上并联管,零售的就取消了变成了预留并联位)因为CPU的供电电压为低电压(1.1-1.8V),而电源为CPU供电的电压比较高(P4为+12V,AMD大部分是+5V现在AMD也越来越多的用+12V供电了),所以Q1通过的电流比Q2要小,Q1可以取指标小点。

同样,储能电感L4的指标也比后面的L1(L2、L3)小,我们在主板实物中看到:如果是环形的L4(和L1、L2、L3外形相同),但它上面绕的线也比L1等要稀。

这也是我们在一些主板上看到MOS管大小不一样的情景。

大多数主板为了采购生产方便,Q1和Q2型号相同。

以上实质上就是一个DC-DC变换,L4及C15-16组成前级DC。

L1(L2、L3及并联的滤波电容)构成后级DC通过上面介绍,我们知道PWM供电电路必须包含前DC-DC的前级电路和DC -DC后级各相组成的电路。

根据这个特点,我们就比较好分辨出主板是几相供电了。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

DS8802A-00 May 2006All brandname or trademark belong to their owner respectively2/3/4/5-Phase PWM Controller forHigh-Density Power SupplyGeneral DescriptionThe RT8802A is a 2/3/4/5-phase synchronous buck controller specifically designed to power Intel ® / AMD next generation microprocessors. It implements an internal 8-bit DAC that is identified by VID code of microprocessor directly. RT8802A generates VID table that conform to Intel ® VRD10.x and VRD11 core power with 6.25mV increments and 0.5%accuracy.RT8802A adopts innovative time-sharing DCR current sensing technique to sense phase currents for phase current balance,load line setting and over current protection. Using a common GM to sense all phase currents eliminates offset and linearity variation between GMs in conventional current sensing methods. As sub-milli-ohm-grade inductors are widely used in modern motherboards, slight offset and linearity mismatch will cause considerable current shift between phases. This technique ensures good current balan ce in ma ss production.Other features include over current protection, programmable soft start, over voltage protection, and output offset setting.RT8802A comes to a small footprint package with VQFN-40L 6x6.Featuresz 5V Power Supplyz2/3/4/5-Phase Power Conversion with Automatic Phase Selectionz8-bit VID Interface, Supporting Intel VRD11/VRD10.x and AMD K8, K8_M2 CPUsz VR_HOT and VR_FAN Indication z Precision Core Voltage RegulationzPower Stage Thermal Balance by DCR Current Sensingz Adjustable Soft-start z Over-Voltage ProtectionzAdjustable Frequency and Typical at 300kHz per Phasez Power Good Indication z 40-Lead VQFN PackagezRoHS Compliant and 100% Lead (Pb)-FreeApplicationszIntel ® /AMD New generation microprocessor for Desktop PC and MotherboardzLow Output Voltage, High power density DC-DC ConverterszVoltage Regulator ModulesOrdering InformationPin Configurations(TOP VIEW)VQFN-40L 6x6Note :RichTek Pb-free products are :`RoHS compliant and compatible with the current require- ments of IPC/JEDEC J-STD-020.`Suitable for use in SnPb or Pb-free soldering processes.`100% matte tin (Sn) plating.VTT/EN FBRTNFB SS QRSEL VR_FAN TSENI O U TD V DR T O F SA D J T C O CI M A X I S N 1I S N 24I S N 35V I D _S E LV I D 0V I D 1V I D 2V I D 3V I D 4V I D 5V I D 6V I D 7V D DP : Pb Free with Commercial StandardRT8802AAll brandname or trademark belong to their owner respectivelyTypical Application CircuitE 1V I D 0u F x 1841 t o C 5060u F x 1051 t o C 68V D D I G NDS8802A-00 May 2006All brandname or trademark belong to their owner respectivelyFunctional Pin DescriptionVTT/EN (Pin 1)The pin is defined as the chip enable, and the VTT is applied for internal VID pull high power and power sequence monitoring.VR_Ready (Pin 2)Power good open-drain output.FBRTN (Pin 3)Feedback return pin. VID DAC and error amplifier reference for remote sensing of the output voltage.FB (Pin 4)Inverting input pin of the internal error P (Pin 5)Output pin of the error amplifier and input pin of the PWM comparator.SS (Pin 6)Connect this SS pin to GND with a capacitor to set the soft-start time interval.QRSEL (Pin 7)Quick response mode select pin. When QRSEL = GND and quick response is triggered during heavy load to light load transient, 2 channels will turn on simultaneously to prevent V OUT undershoot. When QRSEL = NC and quick response is triggered, all channels will turn on simultaneously to prevent V OUT undershoot.VR_FAN (Pin 8)The pin is defined to signal VR thermal information for external VR thermal dissipation scheme triggering.VR_HOT (Pin 9)The pin is defined to signal VR thermal information for external VR thermal dissipation scheme triggering.TSEN (Pin 10)Temperature detect pin for VR_HOT and VR_FAN.IOUT (Pin 11)Output current indication pin. The current through IOUT pin is proportional to the total output current.DVD (Pin 12)Programmable power UVLO detection input. Trip threshold is 1V at V DVD rising.RT (Pin 13)The pin is defined to set internal switching operation frequency. Connect this pin to GND with a resistor R RT to set the frequency F SW .OFS (Pin 14)The pin is defined for load line offset setting.ADJ (Pin 15)Current sense output for active droop adjusting. Connect a resistor from this pin to GND to set the load droop.TCOC (Pin 16)Input pin for setting thermally compensated over current trigger point. Voltage on the pin is compared with V ADJ . If V ADJ > V TCOC then OCP is triggered.IMAX (Pin 17)The pin is defined to set threshold of over current.ISN1 (Pin 18)Current sense negative input pin for channel 1 current sensing.ISN24 (Pin 19)Current sense negative input pins for channel 2 and channel 4 current sensing.ISN35 (Pin 20)Current sense negative input pins for channel 3 and channel 5 current sensing.3500R e 4.463F RT SW 9+=All brandname or trademark belong to their owner respectivelyFunction Block DiagramISP1 (Pin 25), I SP2 (Pin 24), ISP3 (Pin 23),ISP4 (Pin 22), ISP5 (Pin 21)Current sense positive input pins for individual converterchannel current sensing.PWM1 (Pin 26), PWM2 (Pin 27), PWM3 (Pin 28),PWM4 (Pin 29), PWM5 (Pin 30)PWM outputs for each driven channel. Connect these pins to the PWM input of the MOSFET driver. For systems which using 2/3/4 channels, pull PWM 3/4/5 pins up to high.VDD (Pin 31)IC power supply. Connect this pin to a 5V supply.VID7 (Pin 32), VID6 (Pin 33), VID5 (Pin 34), VID4 (Pin 35), VID3 (Pin 36), VID2 (Pin 37), VID1 (Pin 38),VID0 (Pin 39), VID_SEL (40)DAC voltage identification inputs for VRD10.x / VRD11 /K8 / K8_M2 . These pins are internally pulled up to VTT .GND (Bottom pad)Power ground pad of the chip.Table 1. Output Voltage Program (VRD10.x + VID6)To be continuedAll brandname or trademark belong to their owner respectivelyDS8802A-00 May All brandname or trademark belong to their owner respectivelyTo be continuedAll brandname or trademark belong to their owner respectivelyDS8802A-00 May All brandname or trademark belong to their owner respectivelyDS8802A-00 May 2006All brandname or trademark belong to their owner respectivelyTo be continuedTable 2. Output Voltage Program (VRD11)All brandname or trademark belong to their owner respectivelyTo be continuedDS8802A-00 May 2006All brandname or trademark belong to their owner respectivelyTo be continuedNote: (1) 0 : Connected to GND(2) 1 : Open(3) X : Don't CareAll brandname or trademark belong to their owner respectivelyTable 3. Output Voltage Program (K8)Note: (1) 0 : Connected to GND(2) 1 : OpenAll brandname or trademark belong to their owner respectivelyDS8802A-00 May Table 4. Output Voltage Program (K8_M2)To be continued All brandname or trademark belong to their owner respectivelyTable 4. Output Voltage Program (K8_M2)Note: (1) 0 : Connected to GND(2) 1 : Open(3) The voltage above are load independent for desktop and server platforms. For mobile platforms the voltage abovecorrespond to zero load current.All brandname or trademark belong to their owner respectivelyDS8802A-00 May Absolute Maximum Ratings (Note 1)z Supply Voltage, V DD-------------------------------------------------------------------------------------------7Vz Input, Output or I/O Voltage----------------------------------------------------------------------------------GND-0.3V to V DD+0.3V z Power Dissipation, P D @ T A= 25°CVQFN−40L 6x6--------------------------------------------------------------------------------------------------2.857Wz Package Thermal Resistance (Note 4)VQFN-40L 6x6, θJA---------------------------------------------------------------------------------------------35°C/Wz Junction T emperature------------------------------------------------------------------------------------------150°Cz Lead Temperature (Soldering, 10 sec.)--------------------------------------------------------------------260°Cz Storage T emperature Range---------------------------------------------------------------------------------−65°C to 150°Cz ESD Susceptibility (Note 2)HBM (Human Body Mode)-----------------------------------------------------------------------------------2kVMM (Machine Mode)-------------------------------------------------------------------------------------------200V Recommended Operating Conditions (Note 3)z Supply Voltage, V DD-------------------------------------------------------------------------------------------5V ± 10%z Junction T emperature Range---------------------------------------------------------------------------------−40°C to 125°Cz Ambient T emperature Range---------------------------------------------------------------------------------−40°C to 85°C Electrical Characteristics(V= 5V, T = 25°C, unless otherwise specified)To be continuedAll brandname or trademark belong to their owner respectivelyNote 1. Stresses listed as the above "Absolute Maximum Ratings"may cause permanent damage to the device. These are for stress ratings. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may remain possibility to affect device reliability.Note 2. Devices are ESD sensitive. Handling precaution recommended.Note 3. The device is not guaranteed to function outside its operating conditions.Note 4. θJA is measured in the natural convection at T A = 25°C on the four layers high effective thermal conductivity test board of JEDEC 51-7 thermal measurement standard.All brandname or trademark belong to their owner respectivelyDS8802A-00 May All brandname or trademark belong to their owner respectivelyTypical Operating CharacteristicsFrequency vs. R RT01002003004005006007000102030405060708090100R RT (kٛ)F r e q u e n c y (k H z )(k ΩGM0501001502002503003504004500255075100125150175200ISN (uA)P o s i t i v e D u t y (n s )Output Voltage vs. Temperature1.2481.251.2521.2541.2561.2581.261.2621.264-2020406080100Temperature O u t p u t V o l t a g e (V )(°C)Frequency vs. Temperature304306308310312314316318320322-2020406080100Temperature F r e q u e n c y (k H z )(°C)Power On from DVDDVD(1V/Div)Time (1ms/Div)V OUT (1V/Div)SS (1V/Div)PHASE 3(10V/Div)Power Off from DVDDVD (1V/Div)Time (1μs/Div)V OUT (1V/Div)SS (1V/Div)PHASE 3(10V/Div)DS8802A-00 May 2006All brandname or trademark belong to their owner respectivelyPower On with OCPSS (2V/Div)Time (500μs/Div)PWM (5V/Div)VR_Ready (1V/Div)V OUT 1V/Div)Output Short CircuitSS (2V/Div)Time (1ms/Div)PWM (5V/Div)VR_Ready (1V/Div)V OUT (1V/Div)Power On from VCC12VCC12(10V/Div)Time (1ms/Div)V OUT (1V/Div)SS (1V/Div)PHASE 3(10V/Div)Power Off from VCC12VCC12(10V/Div)Time (1ms/Div)V OUT (1V/Div)SS (1V/Div)PHASE 3(10V/Div)Power Off from VCC5VCC5(5V/Div)Time (25ms/Div)V OUT (1V/Div)SS (1V/Div)PHASE 3(10V/Div)Power On from VCC5VCC5(5V/Div)Time (1ms/Div)V OUT (1V/Div)SS (1V/Div)PHASE 3(10V/Div)All brandname or trademark belong to their owner respectivelyDynamic VIDV OUT(200mV/Div)Time (50μs/Div)VID0(500mV/Div)Dynamic VIDV OUT(200mV/Div)Time (50μs/Div)VID0(500mV/Div)OVPSS (2V/Div)Time (10μs/Div)PWM (5V/Div)VR_Ready (1V/Div)FB (1V/Div)V OUT DroopV OUT (20mV/Div)Time (2μs/Div)I OUT (40A/Div)V OUT OvershootTime (2μs/Div)V OUT (20mV/Div)I OUT (40A/Div)21DS8802A-00 May 2006All brandname or trademark belong to their owner respectivelyApplications InformationRT8802A is a multi-phase DC/DC controller specifically designed to deliver high quality power for next generation CPU. RT8802A controls a special power-on sequence &monitors the thermal condition of VR module to meet the VRD11 requirement. Phase currents are sensed by innovative time-sharing DCR current sensing technique for channel current balance, droop tuning, and over current protection. Using one common GM amplifier for current sensing eliminates offset errors and linearity variation between GMs. As sub-milli-ohm-grade inductors are widely used in modern mother boards, slight mismatch of GM amplifiers offset and linearity results in considerable current shift between phases. The time-sharing DCR current sensing technique is extremely important to guarantee phase current balance in mass production.Converter Initialization, Phase Selection, and Power Good FunctionThe RT8802A initiates only after 3 pins are ready: VDD pin power on reset (POR), VTT/EN pin enabled, and DVD pin is hig her than 1V. VDD POR is to make sure RT8802A is powered by a voltage for normal work. The rising threshold voltage of VDD POR is 4.2V typically. At VDD POR, RT8802A checks PWM3, PWM4 and PWM5 status to determine phase number of operation. Pull high PWM3for two-phase operation; pull high PWM4 for three-phase operation; pull high PWM5 for four-phase operation. The unused current sense pins should be connected to GND or left floating.VTT/EN acts as a chip enable pin and receives signal from FSB or other power management IC.DVD is to make sure that ATX12V is ready for drivers to work normally. Connect a voltage divider from ATX12V to DVD pin as shown in the Typical Application Circuit. Make sure that DVD pin voltage is below its threshold voltage before drivers are ready and above its threshold voltage for minimum ATX12V during normal operation.If any one of VDD, VTT/EN, and DVD is not ready, RT8802A keeps its PWM outputs high impedance and the companion drivers turn off both upper and lower MOSFETs. After VDD, VTT/EN, and DVD are ready,RT8802A initiates its soft start cycle that is compliantwith Intel ® VRD11 specification as shown in Figure 1. A time-variant internal current source charges the capacitor connected to SS pin. SS voltage ramps up piecewise linearly and locks VID_DAC output with a specified voltage drop. Consequently, V CORE is built up according to VID_DAC output and meet Intel ® VRD11 requirement.VR_READY output is pulled high by external resistor when V CORE reaches VID_DAC output with 1~2ms delay. An SS capacitor about 47nF is recommend for VRD11compliance.Voltage ControlCPU V CORE voltage is Kelvin sensed by FB and FBRTN pins and precisely regulated to VID_DAC output by internal high gain Error Amplifier (EA). The sensed signal is also used for power good and over voltage function. The typical OVP trip point is 170mV above VID_DAC output. RT8802A pulls PWM outputs low and latches up upon OVP trip to prevent damaging the CPU. It can only restart by resetting one of VDD, DVD, or VTT/EN pin.RT8802A supports Intel VR D10.x, VRD11, AMD K8 and AMD K8_M2 VID specification.The change of VID_DAC output at VID on the fly is also smoothed by capacitor connected to SS pin.Consequently, Vcore shifts to its new position smoothly as shown in Figure 2.Figure 1. Timming Diagram During Soft Start Interval22DS8802A-00 May 2006 All brandname or trademark belong to their owner respectivelyConsequently, the sensing current I X is proportional to inductor current I LX and is expressed as :The sensed current I X is used for current balance and droop tuning as described as followe d. Since all phases share one common GM, GM offset and linearity variation effect is eliminated in practical applications. As sub-milli-ohm-grade inductors are widely used in modern mother boards,slight mismatch of GM amplifiers offset and linearity results in considerable current shift between phases. The time-sharing DCR current sensing technical is extre mely important to guarantee phase current balance in mass production.Phase Current BalanceThe sampled and held phase current I X are summed and averaged to get the averaged current . Each phase current I X then is compared with the averaged current.The difference between I X and is injected to corresponding PWM comparator. If phase current I X is smaller than the averaged current , RT8802A increases the duty cycle o f corresponding phase to increase the phase current accordingly and vice vers a.XI XI Figure 2. Vcore Response at VID on the Fly V COREVID7PWM4DCR Current SensingRT8802A adopts an innovative time-sharing DCR current sensing technique to sense the phase currents for phase current balance (phase thermal balance) and load line regulation as shown in Figure 3. Current sensing amplifier GM samples and holds voltages VCx across the current sensing capacitor Cx by turns in a switching cycle.According to the Basic Circuit Theory, ifFigure 3DCRxI VCx then Cx Rx DCRxLx LX×=×=CSNXLXX R DCRx I I ×=I XI23DS8802A-00 May 2006All brandname or trademark belong to their owner respectivelyIfWith other phase kept unchanged, this phase would share (R PX +Rx)/R PX times current than other phases. Figure 6and 7 show different current ratio setting for the power stage when Phase 4 is programmed 2 times current than other phases. Figure 8 and 9 compare the above current ratio setting results.Output Voltage Offset FunctionTo meet Intel ® requirement of initial offset of load line,RT8802A provides programmable initial offset function.External resistor R OFS and voltage source at OFS pingenerate offset current , where V OFS is 1V typical. One quarter of I OFS flows through R FB1 as shown in Figure 4. Error amplifier would hold the inverting pin equal to V DAC - V ADJ . Thus output voltage is subtracted from V DAC - V ADJ for a constant offset voltage.A positive output voltage offset is possible by connecting R OFS to VDD instead of to GND. Please note that when R OFS is connected to VDD, V OFS is V DD − 2V typically and half of I OFS flows through R FB1. V CORE is rewritten as :Current Ratio SettingCurrent ratio adjustment is possible as described below.It is important for achieving thermal balance in practical application where thermal conditions between phases are not identical. Figure 5 shows the application circuit of GMfor current ratio requirement. According to Basic Circuit TheoryFigure 7. GM1~3 Setting for current ratio functionFigure 6. GM4 Setting for current ratio functionFigure 4. Load Line and Offset FunctionFigure 5OFSOFSOFS R VI =OFSFB1ADJ DAC CORE R V V V −−=OFSFB1ADJ DAC CORE R R V V V + −=DCRxI 1R Rx CxR SRx R Rx R VCx LX PXPX PXPX ××++××+=DCRxI R Rx R VCx thenCx )//R (R DCRx L LX PXPXPX X X××+=×=V OUTV I OFS24DS8802A-00 May 2006All brandname or trademark belong to their owner respectivelyFigure 8Current Ratio Function051015202530350153045607590I OUT (A)I L (A )Figure 9Current Balance Function05101520253035020406080100120I OUT (A)I L (A )Figure 10Load Line without dead zone at light loads1.231.241.251.261.271.281.291.31.31510152025I OUT (A)V C O R E (V )Dead Zone EliminationRT8802A samples and holds inductor current at 50%period by time-sharing sourcing a current I X to R CSN . At light load condition when inductor current is not balance,voltage VCx across t he sensing capacitor would be negative. It needs a negative I X to sense the voltage.However, RT8802A CANNOT provide a negative I X and consequently cannot sense negative inductor current. This results in dead zone of load line performance as shown in Figure 10. Therefore a technique as shown in Figure 11 is required to eliminate the dead zone of load line at light load condition.Referring to Figure 11, I X is expressed as :where I LX_50% is the of inductor current at 50% period. To make sure RT8802A could sense the inductor current,right hand side of Equation (1) should always be positive:Since R CSN >> DCRx in practical application, Equation (2)could be simplified as :Figure 11. Application circuit o f GM(2)(1)CSNLX_50%CSN2LX_50%CSN2OUT X R DCRx I R DCRx I R VI ×+×+=0R DCRx I R DCRx I R VCSNLX_50%CSN2LX_50%CSN2OUT ≥×+×+CSNLX_50%CSN2OUT R DCRx I R V×≥OUT25DS8802A-00 May 2006All brandname or trademark belong to their owner respectivelyFor example, assuming the negative inductor current is I LX_50% = −5A at no load, then for R CSN 330Ω, R ADJ = 160Ω, V OUT = 1.300VR CSN2 ≤ 85.8k ΩChoose R CSN2 = 82k ΩFigure 10 shows that dead zone of load line at light load is eliminated by applying this technique.VR_HOT & VR_FAN SettingOver Current ProtectionThermally compensated total current OCPV TCOC is compared with V ADJ . If V ADJ > V TCOC then OCP is triggered.Figure 12Figure 15Load Line Setting and Thermal Compensation V ADJ = Sum(I X ) x R ADJ = (DCR x R ADJ / R CSN ) x I OUT = LL x I OUTV OUT = V DAC − V ADJ = V DAC − LL x I OUT LL = DCR(PTC) x R ADJ (NTC) / R CSNDCR is the inductor DCR which is a PTC resistance.ΩΩ×−≥3301m 5A R 1.3V CSN2Q1Q2Q3V CC VR ADJFigure 14. R ADJ Connection for Thernal CompensationV 0.28 x V 0.33 x V 0.39 x V Figure 13. VR_HOT and VR_FAN Signal vs TSEN Voltage If R ADJ is connected as in Figure 14, R ADJ = R1 + (R2//R NTC ), which is a negative temperature correlated resistance. By properly selecting R1 and R2, the positive temperature coefficient of DCR can be canceled by the negative temperature coefficient of R ADJ . Thus the load line will be thermally compensated.Phase current OCPRT8802A uses an external resistor R IMAX connected to IMAX pin to generate a reference current I IMAX for overcurrent protection :where V IMAX is typical 1.0V . OCP comparator compares each sensed phase current I X with this reference current as shown in Figure 16. Equivalently, the maximum phase current I LX(MAX) is calculated as below:IMAXIMAXIMAX R VI =LX CSNXIMAX IMAX XCSNX X LX(MAX)IMAX IMAXIMAX X(MAX)IMAXX(MAX)R V3DCR R I I R V23I 23I I 21I31××=×=×===OC26DS8802A-00 May 2006 All brandname or trademark belong to their owner respectivelyError Amplifier CharacteristicFor fast response of converter to meet stringent output current transient response, RT8802A provides large slew rate capability and high gain-bandwidth performance.Figure 20. Gain-Bandwidth Measurement by signal Adivided by signal BFigure 19. EA Falling Transient with 10pF Loading ;Slew Rate = 8V/μsFigure 18. EA Rising Transient with 10pF Loading ;Slew Rate = 10V/μsDesign Procedure Suggestiona. Output filter pole and zero (Inductor, output capacitor value & ESR).b. Error amplifier compensation & saw-tooth wave amplitude (compensation network).c. Kelvin sense for V CORE .Current Loop Settinga. GM amplifier S/H current (current sense component DCR, ISP X and ISN X pin external resistor value).b. Over-current protection trip point (R IMAX resistor).VRM Load Line Settinga. Droop amplitude (ADJ pin resistor).b. No load offset (R CSN )c. DAC offset voltage setting (OFS pin & compensation network resistor).CH1:(500mV/Div)CH2:(2V/Div)EA Rising Slew RateTime (250ns/Div)V COMPV FBCH1:(500mV/Div)CH2:(2V/Div)EA Falling Slew RateTime (250ns/Div)V COMPV FBI X I OC I X I OC I X I OC I X I OC Figure 17Phase current OCP and total current OCP with thermal compensationFigure 16. Over Current Comparator+-1/3 I X 1/2 I IMAXOCP Comparatord. Temperature coefficient compensation(TSEN externalresister & thermistor, resistor between ADJ and GND.)Power Sequence & SSDVD pin external resistor and SS pin capacitor.PCB Layouta.Kelvin sense for current sense GM amplifier input.b.Refer to layout guide for other items.All brandname or trademark belong to their owner respectivelyDS8802A-00 May 27RICHTEK TECHNOLOGY CORP. Headquarter5F, No. 20, Taiyuen Street, Chupei City Hsinchu, Taiwan, R.O.C.Tel: (8863)5526789 Fax: (8863)5526611RICHTEK TECHNOLOGY CORP.Taipei Office (Marketing)8F-1, No. 137, Lane 235, Paochiao Road, Hsintien City Taipei County, Taiwan, R.O.C.Tel: (8862)89191466 Fax: (8862)89191465Email: marketing@28DS8802A-00 May 2006 All brandname or trademark belong to their owner respectively V-Type 40L QFN 6x6 Package。