wire和reg的区别

武汉理工大学华夏学院EDA复习题答案

1、IEEE标准的硬件描述语言是Verilog HDL和VHDL共同点是:能够形式化地抽象表示电路的行为和结构;支持逻辑设计中层次与范围的描述:可借用高级语言的精巧结构来简化电路行为的描述:具有电路仿真与验证机制以保证设计的正确性;支持电路描述由高层到低层的综合转换;硬件描述与实现工艺无关;便于文档管理;易于理解和设计重用。

不同点:Verilog HDL是一种非常容易掌握的硬件描述语言,而VHDL掌握起来就比较困难。

2、把功能经过验证的、可综合的、实现后电路结构总门数在5000门以上的Verilog HDL模型称之为“软核”。

把在某一种现场可编程门阵列(FPGA)器件上实现的、经验证是正确的、总门数在5000门以上电路结构编码文件称为“固核”。

把在某一种专用集成电路工艺的(ASIC)器件上实现的、经验证是正确的、总门数在5000门以上电路结构版图掩膜称为“硬核”。

3、什么叫综合?通过综合产生的是什么?通过综合工具把行为级描述的模块通过逻辑网表自动转化为门级形式的模块叫综合。

综合由EDA工具来完成。

产生的是由与门,或门和非门组成的加法器,比较器等组合逻辑。

产生的模块很容易与某种工艺的基本元件逐一对应起来,再通过布局布线工具自动地转变为某种工具工艺的电路布线结构。

4、仿真可以在几层面上进行?每个层面的仿真有什么意义?分别为:前仿真,逻辑网表仿真,门级仿真和布线后仿真。

前仿真,逻辑网表仿真,门级仿真:可以调试和验证逻辑系统的设计和结构准确与否,并发现问题及时修改。

布线后仿真:分析设计的电路模块的运行是否正常。

5、模块由描述接口和描述逻辑功能两部分组成。

6、端口分为三种:输入口、输出口、输入/输出口。

7、reg型和wire型变量的差别是什么?reg型变量是寄存器型变量,wire型变量是连线型变量。

两者根本性的差别在于reg型变过量有个寄存器来存放变量,这个值只有变量发生改变时才会改变否则保证原来的值不变,wire型变量的值不是确定的值。

Verilog中assign语句讲解

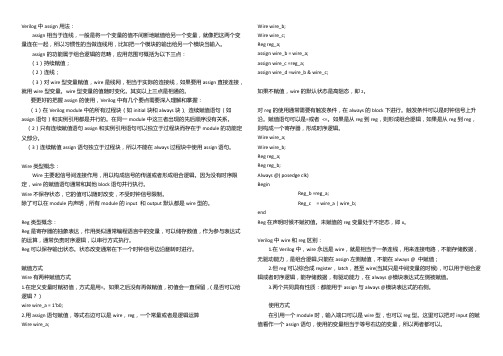

Verilog中assign用法:assign相当于连线,一般是将一个变量的值不间断地赋值给另一个变量,就像把这两个变量连在一起,所以习惯性的当做连线用,比如把一个模块的输出给另一个模块当输入。

assign的功能属于组合逻辑的范畴,应用范围可概括为以下三点:(1)持续赋值;(2)连线;(3)对wire型变量赋值,wire是线网,相当于实际的连接线,如果要用assign直接连接,就用wire型变量。

wire型变量的值随时变化。

其实以上三点是相通的。

要更好的把握assign的使用,Verilog中有几个要点需要深入理解和掌握:(1)在Verilog module中的所有过程块(如initial块和always块)、连续赋值语句(如assign语句)和实例引用都是并行的。

在同一module中这三者出现的先后顺序没有关系。

(2)只有连续赋值语句assign和实例引用语句可以独立于过程块而存在于module的功能定义部分。

(3)连续赋值assign语句独立于过程块,所以不能在always过程块中使用assign语句。

Wire类型概念:Wire主要起信号间连接作用,用以构成信号的传递或者形成组合逻辑。

因为没有时序限定,wire的赋值语句通常和其他block语句并行执行。

Wire不保存状态,它的值可以随时改变,不受时钟信号限制。

除了可以在module内声明,所有module的input 和output默认都是wire型的。

Reg类型概念:Reg是寄存器的抽象表达,作用类似通常编程语言中的变量,可以储存数值,作为参与表达式的运算,通常负责时序逻辑,以串行方式执行。

Reg可以保存输出状态。

状态改变通常在下一个时钟信号边沿翻转时进行。

赋值方式Wire有两种赋值方式1.在定义变量时赋初值,方式是用=。

如果之后没有再做赋值,初值会一直保留,(是否可以给逻辑?)wire wire_a = 1’b0;2.用assign语句赋值,等式右边可以是wire,reg,一个常量或者是逻辑运算Wire wire_a;Wire wire_b;Wire wire_c;Reg reg_a;assign wire_b = wire_a;assign wire_c =reg_a;assign wire_d =wire_b & wire_c;如果不赋值,wire的默认状态是高阻态,即z。

Verilog中assign语句讲解

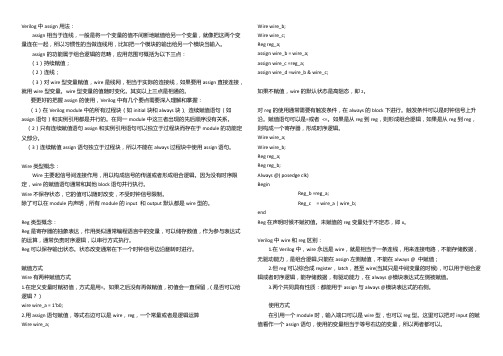

Verilog中assign用法:assign相当于连线,一般是将一个变量的值不间断地赋值给另一个变量,就像把这两个变量连在一起,所以习惯性的当做连线用,比如把一个模块的输出给另一个模块当输入。

assign的功能属于组合逻辑的范畴,应用范围可概括为以下三点:(1)持续赋值;(2)连线;(3)对wire型变量赋值,wire是线网,相当于实际的连接线,如果要用assign直接连接,就用wire型变量。

wire型变量的值随时变化。

其实以上三点是相通的。

要更好的把握assign的使用,Verilog中有几个要点需要深入理解和掌握:(1)在Verilog module中的所有过程块(如initial块和always块)、连续赋值语句(如assign语句)和实例引用都是并行的。

在同一module中这三者出现的先后顺序没有关系。

(2)只有连续赋值语句assign和实例引用语句可以独立于过程块而存在于module的功能定义部分。

(3)连续赋值assign语句独立于过程块,所以不能在always过程块中使用assign语句。

Wire类型概念:Wire主要起信号间连接作用,用以构成信号的传递或者形成组合逻辑。

因为没有时序限定,wire的赋值语句通常和其他block语句并行执行。

Wire不保存状态,它的值可以随时改变,不受时钟信号限制。

除了可以在module内声明,所有module的input 和output默认都是wire型的。

Reg类型概念:Reg是寄存器的抽象表达,作用类似通常编程语言中的变量,可以储存数值,作为参与表达式的运算,通常负责时序逻辑,以串行方式执行。

Reg可以保存输出状态。

状态改变通常在下一个时钟信号边沿翻转时进行。

赋值方式Wire有两种赋值方式1.在定义变量时赋初值,方式是用=。

如果之后没有再做赋值,初值会一直保留,(是否可以给逻辑?)wire wire_a = 1’b0;2.用assign语句赋值,等式右边可以是wire,reg,一个常量或者是逻辑运算Wire wire_a;Wire wire_b;Wire wire_c;Reg reg_a;assign wire_b = wire_a;assign wire_c =reg_a;assign wire_d =wire_b & wire_c;如果不赋值,wire的默认状态是高阻态,即z。

Verilog中assign语句讲解

Verilog中assign用法:assign相当于连线,一般是将一个变量的值不间断地赋值给另一个变量,就像把这两个变量连在一起,所以习惯性的当做连线用,比如把一个模块的输出给另一个模块当输入。

assign的功能属于组合逻辑的范畴,应用范围可概括为以下三点:(1)持续赋值;(2)连线;(3)对wire型变量赋值,wire是线网,相当于实际的连接线,如果要用assign直接连接,就用wire型变量。

wire型变量的值随时变化。

其实以上三点是相通的。

要更好的把握assign的使用,Verilog中有几个要点需要深入理解和掌握:(1)在Verilog module中的所有过程块(如initial块和always块)、连续赋值语句(如assign语句)和实例引用都是并行的。

在同一module中这三者出现的先后顺序没有关系。

(2)只有连续赋值语句assign和实例引用语句可以独立于过程块而存在于module的功能定义部分。

(3)连续赋值assign语句独立于过程块,所以不能在always过程块中使用assign语句。

Wire类型概念:Wire主要起信号间连接作用,用以构成信号的传递或者形成组合逻辑。

因为没有时序限定,wire的赋值语句通常和其他block语句并行执行。

Wire不保存状态,它的值可以随时改变,不受时钟信号限制。

除了可以在module内声明,所有module的input 和output默认都是wire型的。

Reg类型概念:Reg是寄存器的抽象表达,作用类似通常编程语言中的变量,可以储存数值,作为参与表达式的运算,通常负责时序逻辑,以串行方式执行。

Reg可以保存输出状态。

状态改变通常在下一个时钟信号边沿翻转时进行。

赋值方式Wire有两种赋值方式1.在定义变量时赋初值,方式是用=。

如果之后没有再做赋值,初值会一直保留,(是否可以给逻辑?)wire wire_a = 1’b0;2.用assign语句赋值,等式右边可以是wire,reg,一个常量或者是逻辑运算Wire wire_a;Wire wire_b;Wire wire_c;Reg reg_a;assign wire_b = wire_a;assign wire_c =reg_a;assign wire_d =wire_b & wire_c;如果不赋值,wire的默认状态是高阻态,即z。

virilog语法总结

1、verilog特点:★区分大小写,所有关键字都要求小写★不是强类型语言,不同类型数据之间可以赋值和运算★ //是单行注释可以跨行注释★描述风格有系统级描述、行为级描述、RTL级描述、门级描述,其中RTL级和门级别与具体电路结构有关,行为级描述要遵守可综合原★门级描述使用门级模型或者用户自定义模型UDP来代替具体基本元件,在IDE中针对不同FPGA器件已经有对应的基本元件原语verlog语法要点2、语句组成:★ module endmodule之间由两部分构成:接口描述和逻辑功能描述★ IO端口种类: input output inout★相同位宽的输入输出信号可以一起声明, input[3:0] a,b; 不同位宽的必须分开写★内部信号为reg类型,内部信号信号的状态: 0 1 x z, 3‘bx1=3’bxx1 x/z会往左扩展 3‘b1=3’b001 数字不往左扩展★逻辑功能描述中常用assign描述组合逻辑电路,always既可以描述组合逻辑电路又可以描述时序逻辑电路,还可以用元件调用方法描述逻辑功能★ always之间、assign之间、实例引用之间以及它们之间都是并行执行,always内部是顺序执行3、常量格式: <二进制位宽><‘><进制><该进制的数值>:默认进制为10进制默认位宽为32位位宽是从二进制宽度角度而言的由位宽决定从低位截取二进制数2’hFF=2‘b11,通常由被赋值的reg变量位宽决定parameter常用于定义延迟和变量位宽,可用常量或常量表达式定义4、变量种类: wire reg memory① IO信号默认为wire类型,除非指定为reg类型(reg和wire 的区别)wire可以用作任何输入输出端口wire包括input output inoutwire不带寄存功能assign赋值语句中,被赋值的信号都是wire类型assign之所以称为连续赋值,是因为不断检测表达式的变化reg类型可以被赋值后再使用,而不是向wire一样只能输出reg类型变量初始值为xalways模块里被赋值的信号都必须定义为reg类型,因为always 可以反复执行,而reg表示信号的寄存,可以保留上次执行的值reg类型变量与integer变量不同,即使赋负值,实质上也是按二进制无符号数存储的,integer是有符号数verilog中所有内部信号都是静态变量,因为它们的值都在reg中存储起来② memory型只有一维数组,由reg型变量组成memory初始化只能按地址赋值,不能一次性赋值1*256的memory写法: reg mema[255:0] mema[3]=0; 不同位宽的变量之间赋值,处理之前都以被赋值的变量位宽为准扩展或截取A[a:b] 无论a b谁大,a总是实际电路的信号高位,b总是实际电路的信号低位算术运算中如果有X值则结果为Xfor循环中的变量另外定义成integer,因为它不是实际信号,有正负;reg则以无符号数存在5、运算符(其他简单的书上有自己看)== 和!=只比较0、1,遇到z或x时结果都为x (x在if中算做假条件),结果可能是1、0、x===和!==比较更加苛刻,包括x和z的精确比较,结果可能是0、1 &&的结果只有1‘b1或1’b0两种, A&A的结果位宽则是与A相同的{1,0}为 64‘h100000000,所以拼接运算中各信号一定要指定位宽移位运算左移将保留 4'b1000<<1等于5'b10000,右移则舍弃 4'b0011等于4'b0001数字电路里位运算应用普遍,包括按位逻辑运算、移位运算、拼接运算、缩减运算6、非阻塞式赋值<=与阻塞式赋值=(比较)阻塞:在同一个always过程中,后面的赋值语句要等待前一个赋值语句执行完,后面的语句被该赋值语句阻塞非阻塞:在同一个always过程中,非阻塞赋值语句是同时进行的,排在后面的语句不会被该赋值语句阻塞<=:块结束后才能完成赋值块内所有<=语句在always块结束时刻同时赋值<=右边各变量的值是上一次时钟边沿时,这些变量当时的值用于描述可综合的时序电路=:=语句结束之后过程always才可能结束在always过程中,begin end块内按先后顺序立即赋值,在fork join内同时赋值(可能造成冲突)与assign连用描述组合电路begin end中阻塞的含义:begin ...@(A) B=C...; end 如果A事件不发生则永远不能执行下去,被阻塞了由于时钟的延时(往往在ps级),多个always(posedge)之间究竟谁先执行是个未知数使用八原则:(1)时序电路建模时,采用非阻塞赋值(2)锁存器电路建模时,采用非阻塞赋值。

第5章-Verilog语言要素

5.3.2 Variable型

variable型变量必须放在过程语句(如initial、always)中,通 过过程赋值语句赋值;在always、initial等过程块内被赋值的 信号也必须定义成variable型。 variable型(以前叫register型)是数据存储单元的抽象,但不 能表示真正的硬件,相当于计算机高级语言中的变量。 常用variable型变量:

整数(integer)

Examples:

8'b11000101 //位宽为八位的二进制数11000101

8'hd5

//位宽为八位的十六进制数d5;

5'O27

//5位八进制数

4'D2

//4位十进制数2

4'B1x_01

//4位二进制数1x01

5'Hx

//5位x(扩展的x),即xxxxx

4'hZ

//4位z,即zzzz

assign larger=(a>b);

assign equal=(a==b);

assign less=(a<b);

endmodule

【例5.4】 采用参数定义的二进制计数器

module count_w(en,clk,reset,out);

input clk,reset,en; parameter WIDTH=8;

◆ 整数

◆ 实数

◆ 字符串

整数(integer)

整数按如下方式书写:

+/-<size> '<base><value> 即 +/-<位宽>'<进制><数字> size 为对应二进制数的宽度;base为进制;value是 基于进制的数字序列。 进制有如下4种表示形式: ◆ 二进制(b或B) ◆ 十进制(d或D或缺省) ◆ 十六进制(h或H) ◆ 八进制(o或O)

Verilog综合时wire与reg如何防止被优化

shared]Verilog综合时wire与reg如何防止被优化(1)2009-11-29 14:14Abstract撰寫Verilog時,雖然每個module都會先用ModelSim或Quartus II自帶的simulator仿真過,但真的將每個module合併時,一些不可預期的『run-time』問題可能才一一浮現,這時得靠SignalTap II來幫忙debug。

Introduction使用環境:Quartus II 8.0 + DE2-70 (Cyclone II EP2C70F896C6N)實際使用SignalTap II時,會發現有些reg與wire可以觀察,有些又無法觀察,在(原創) 如何使用SignalTap II觀察reg值? (IC Design) (Quartus II) (SignalTap II) (Verilog)中,我利用將reg接到top module的方式來觀察reg,雖然可行,但老實說並不是很好的方式。

當初有網友發表評論,說這是因為reg被Quartus II優化掉不見了,導致無法使用SignalTap II觀察,本文整理出完整的reg與wire觀察方法。

觀察reg如同(原創) 如何使用SignalTap II觀察reg值? (IC Design) (Quartus II) (SignalTap II) (Verilog)的範例,我再重複一次。

SSignalTapII_register_not_preserve.v / Verilog1/*2(C) OOMusou 2008 34Filename : SignalTapII_register_not_preserve.v5Compiler : Quartus II 8.06Description : Demo how to preserve register with SingalTap II7Release : 10/17/2008 1.08*/910module SignalTapII_register_not_preserve (11input iCLK,12input iRST_N13 );1415reg [3:0] cnt;1617always@(posedge iCLK, negedge iRST_N) begin18if (!iRST_N)19 cnt <= 4'h0;20else21 cnt <= cnt + 4'h1;22end2324endmodule這是個很簡單的計數器,我故意讓cnt不做output,而想用SignalTap II去觀察cnt這個reg的值。

Verilog中assign语句讲解

Verilog中assign用法:assign相当于连线,一般是将一个变量的值不间断地赋值给另一个变量,就像把这两个变量连在一起,所以习惯性的当做连线用,比如把一个模块的输出给另一个模块当输入。

assign的功能属于组合逻辑的范畴,应用范围可概括为以下三点:(1)持续赋值;(2)连线;(3)对wire型变量赋值,wire是线网,相当于实际的连接线,如果要用assign直接连接,就用wire型变量。

wire型变量的值随时变化。

其实以上三点是相通的。

要更好的把握assign的使用,Verilog中有几个要点需要深入理解和掌握:(1)在Verilog module中的所有过程块(如initial块和always块)、连续赋值语句(如assign语句)和实例引用都是并行的。

在同一module中这三者出现的先后顺序没有关系。

(2)只有连续赋值语句assign和实例引用语句可以独立于过程块而存在于module的功能定义部分。

(3)连续赋值assign语句独立于过程块,所以不能在always过程块中使用assign语句。

Wire类型概念:Wire主要起信号间连接作用,用以构成信号的传递或者形成组合逻辑。

因为没有时序限定,wire的赋值语句通常和其他block语句并行执行。

Wire不保存状态,它的值可以随时改变,不受时钟信号限制。

除了可以在module内声明,所有module的input 和output默认都是wire型的。

Reg类型概念:Reg是寄存器的抽象表达,作用类似通常编程语言中的变量,可以储存数值,作为参与表达式的运算,通常负责时序逻辑,以串行方式执行。

Reg可以保存输出状态。

状态改变通常在下一个时钟信号边沿翻转时进行。

赋值方式Wire有两种赋值方式1.在定义变量时赋初值,方式是用=。

如果之后没有再做赋值,初值会一直保留,(是否可以给逻辑?)wire wire_a = 1’b0;2.用assign语句赋值,等式右边可以是wire,reg,一个常量或者是逻辑运算Wire wire_a;Wire wire_b;Wire wire_c;Reg reg_a;assign wire_b = wire_a;assign wire_c =reg_a;assign wire_d =wire_b & wire_c;如果不赋值,wire的默认状态是高阻态,即z。

varglobal数据类型

varglobal数据类型Verilog中共有19种数据类型。

基本的四种类型: reg型、wire型、integer型、parameter 型。

其他类型:large型、medium型、small型、scalared型、time 型、tri型、trio型、tril型、triand型、trior型、trireg型、vectored型、wand型和wor型。

这14中数据类型除time外都与基本逻辑单元建库有关。

A、常量(1)数字整数,整型常量即整常数有以下4种进制表示形式:1)二进制(b或B);2)十进制(d或D);3)十六进制(h或H);4)八进制(o或O)。

数字表达式分为三种:1)<位宽><进制><数字>,这是最完整的形式。

2)<进制><数字>,数字的位宽采用默认位宽(不同的机器系统不同,至少32位)。

3)<数字>,采用默认进制(十进制)。

示例:(位宽指的是时间所占位数,而不是指十六进制有几位。

如示例二,每一位十六进制数字需要4位二进制数字表示,所以2位十六进制的位宽为8)8'b10101100 //位宽为8的二进制数字101011008'ha2 //位宽为8的十六进制数字a2x值和z值:在数字电路中,x代表不定值,z代表高阻值。

一个x可以定义十六进制的4位,八进制的3位。

z的表示方式同x相同,另外z亦可以用“?”来表示。

(case块中用得较多)4'b10x0 //位宽为4的二进制数从低位数起第二位为不定值4'b101z //位宽为4的二进制数从低位数起第一位为高阻值12'dz //位宽为12的10进制数,其值为高阻值(形式一)12'd? //位宽为12的10进制数,其值为高阻值(形式二)8'h4x //位宽为8的十六进制数,其低4位为不定值负数:在位宽前面加一个减号,减号必须在数字定义表达式的最前面。

verilog基本语法之always和assign

verilog基本语法之always和assignalways和assign的作⽤⼀、语法定义assign,连续赋值。

always,敏感赋值。

连续赋值,就是⽆条件全等。

敏感赋值,就是有条件相等。

assign的对象是wire,always的对象是reg。

这就是语法约束。

⼆、功能差异assign对应电路下连线操作。

always对应插⼊敏感控制连线。

这⾥容易混淆的就是assign综合的⼀定是组合电路,但是always综合的不⼀定是时序电路。

always的敏感列表使⽤*号就可以等效综合为组合电路。

如果使⽤的是电平触发,也使会综合成相应的组合电路。

只有出现边沿触发时,才会综合成时序电路。

⽽时序电路,基础就是时钟和使能两个关键信号。

时钟在always模块中不再出现(时钟信号在敏感信号作⽤下的值⼀直相等,没有使⽤在内部的意义,当然可以转化后使⽤)。

⽽对于使能信号,则是会有⼀个if判断语句,⽽且处于第⼀优先级。

这就是异步复位。

如果不在敏感列表⽽处于第⼀优先级,则是同步复位信号。

从上⾯的描述可以看到:always可以实现两种电路,是不是可以不⽤assign来实现设计?理论上可以,但是会加⼤设计的难度。

⾸先要明确的是,always只能对reg变量赋值,这导致wire变量赋值困难。

如果没有assign,每个wire变量都要加⼊⼀个reg缓冲。

可以简单理解:开始时只有always,可以实现基本的功能,然后将其中的组合逻辑提取出来构成assign。

同时引⼊了wire。

也就是assign是always的补充(只是⽅便理解,没有根据)。

三、实际应⽤使⽤assign和always构建加法器:always@(*)begina<=b+c;endassign a=b+c;四。

拓展在上⾯的学习中可以看到,reg和wire的作⽤也是语法的重要区别。

以后有时间可以去区别。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

wire和reg的区别

每次写verilog代码时都会考虑把一个变量是设置为wire类型还是reg类型,

因此把网上找到的一些关于这方面的资料整理了一下,方便以后查找。

wire表示直通,即只要输入有变化,输出马上无条件地反映;reg表示一定

要有触发,输出才会反映输入。

不指定就默认为1位wire类型。专门指定出wire类型,可能是多位或为使

程序易读。wire只能被assign连续赋值,reg只能在initial和always中赋值。wire

使用在连续赋值语句中,而reg使用在过程赋值语句中。

在连续赋值语句中,表达式右侧的计算结果可以立即更新表达式的左侧。

在理解上,相当于一个逻辑之后直接连了一条线,这个逻辑对应于表达式的右侧,

而这条线就对应于wire。在过程赋值语句中,表达式右侧的计算结果在某种条件

的触发下放到一个变量当中,而这个变量可以声明成reg类型的。根据触发条件

的不同,过程赋值语句可以建模不同的硬件结构:如果这个条件是时钟的上升沿

或下降沿,那么这个硬件模型就是一个触发器;如果这个条件是某一信号的高电

平或低电平,那么这个硬件模型就是一个锁存器;如果这个条件是赋值语句右侧

任意操作数的变化,那么这个硬件模型就是一个组合逻辑。

输入端口可以由wire/reg驱动,但输出端口只能是wire;输出端口可以使

wire/reg类型,输出端口只能驱动wire;若输出端口在过程块中赋值则为reg型,

若在过程块外赋值则为net型。用关键词inout声明一个双向端口, inout端口不能

声明为reg类型,只能是wire类型;输入和双向端口不能声明为寄存器类型。

简单来说硬件描述语言有两种用途:1、仿真,2、综合。

对于wire和reg,也要从这两个角度来考虑。

*********************************************************************

************

从仿真的角度来说,HDL语言面对的是编译器(如Modelsim等),相当于软件

思路。

这时:

wire对应于连续赋值,如assign

reg对应于过程赋值,如always,initial

*********************************************************************

************

从综合的角度来说,HDL语言面对的是综合器(如DC等),要从电路的角度来

考虑。

这时:

1、wire型的变量综合出来一般是一根导线;

2、reg变量在always块中有两种情况:

(1)、always后的敏感表中是(a or b or c)形式的,也就是不带时钟边沿的,综

合出来还是组合逻辑

(2)、always后的敏感表中是(posedge clk)形式的,也就是带边沿的,综合出来

一般是时序逻辑,会包含触发器(Flip-Flop)

在设计中,输入信号一般来说你是不知道上一级是寄存器输出还是组合逻辑输

出,那么对于本级来说就是一根导线,也就是wire型。而输出信号则由你自己

来决定是寄存器输出还是组合逻辑输出,wire型、reg型都可以。但一般的,整

个设计的外部输出(即最顶层模块的输出),要求是寄存器输出,较稳定、扇出

能力也较好