嵌入式系统开发_4 S3C2410主要外设功能部件

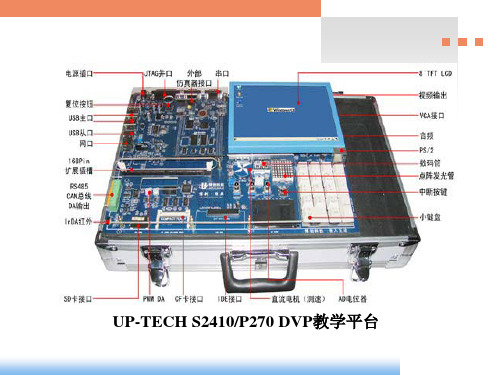

电子科大 第5章 嵌入式系统实验平台硬件介绍

11

第5章 基于S3C2410的系统硬件设计

NAND Flash控制器的结构框图

12

第5章 基于S3C2410的系统硬件设计

NAND Flash的工作方式

13

第5章 基于S3C2410的系统硬件设计

NAND Flash存源管理

时钟和电源管理模块包括三部分:

S3C2410是Samsung公司推出的16/32位RISC处理器,主要 面向手持设备以及高性价比、低功耗的应用。 CPU内核采用 的是ARM公司设计的16/32位ARM920T RISC处理器。 S3C2410A提供一组完整的系统外围设备:

1.8V/2.0V内核供电,3.3V存储器供电,3.3V 外部I/O供电; 具有16KB的ICache和16KB的DCache以及 MMU; 外部存储器控制器; LCD控制器提供1通道LCD专用DMA; 4通道DMA并有外部请求引脚; 3通道UART和2通道SPI; 1通道多主机IIC总线和1通道IIS总线控制器; SD主接口版本1.0和MMC卡协议2.11兼容版; 2个USB主设备接口,1个USB从设备接口; 4通道PWM定时器和1通道内部定时器; 看门狗定时器; 117位通用I/O口和24通道外部中断源; 电源控制模式包括:正常、慢速、空闲和掉电 四种模式; 8通道10位ADC和触摸屏接口; 具有日历功能的RTC; 使用PLL的片上时钟发生器。

18

第5章 基于S3C2410的系统硬件设计

主要内容

1 S3C2410简介 2 I/O口 3 中断 4 DMA 5 UART 6

A/D接口

7 键盘和LED控制 8 9

LCD 触摸屏

10 音频录放 11 USB设备的数据收发

19

S3C2410 中文手册.asp

二、开发板特性及资源 .............................................................. 6

八、使用 EMBEST IDE 调试软件 ............................................... 35

1、 测试例程........................................................................................................................35 2、 操作步骤........................................................................................................................36

Embest® is registered trademarks of Embest Info&Tech Co.,LTD.

2004 英蓓特公司版权所有

2

目录

前 言 .................................................................................. 4

2004 英蓓特公司版权所有

1

版本说明

本指导书为 Embest S3CEB2410 开发系统使用指导 Version 1.0 版本。因时间仓促,该 版本仅简单介绍了 Embest S3CEB2410 开发系统的硬件及部分软件测试,我们将在后续的 修订版本中加入更详细的内容。关于 Embest S3CEB2410 开发系统使用指导书的最新版本, 敬请关注英蓓特公司网站或直接联系英蓓特公司市场部。

S3C2410系列I2S总线接口功能及应用开发

I2S总线结构配置

随着第一个WS信号的改变,WSP在SCK信号的下降沿 重设计数器。在“1 out of n”译码器对计数器数值进行译码 后,第一个串行的数据(MSB)在SCK时钟信号的上升沿被 存放进入B1,随着计数器的增长,接下来的数据被依次存 放进入B2到Bn中。在下一个WS信号改变的时候,数据根 据WSP脉冲的变化被存放进入左(声道)锁存器或者右(声道) 锁存器,并且将B2一Bn的数据清除以及计数器重设,如果 有冗余的数据则最低位之后的数据将被忽略。注意:译码 器和计数器(虚线内的部分)可以被一个n比特移位寄存器所 代替。

I2S总线规范

I2S总线拥有三条数据信号线:

信 号 线

SCK: (continuous serial clock) 串行时钟 对应数字音频的每一位数据,SCK都有1个脉冲。SCK的 频率=2×采样频率×采样位数。 WS: (word select) 字段(声道)选择 用于切换左右声道的数据。WS的频率=采样频率。 SD: (serial data) 串行数据 用二进制补码表示的音频数据。 对于系统而言,产生SCK和WS的信号端就是主导装置,用 MASTER表示,简单系统示意图如图1所示:

支持32(2×16)字节发送和接收(FIFO);

具有正常和DMA两种传输模式。

S3C2410X

2 I S总线结构

图7 IIS总线框图 各部分功能如下:

S3C44B0X I2S总线结构

总线接口、寄存器组、和状态机(BRFC):总线接口逻辑和FIFO的 访问由状态机控制;

两个三位的预分频器(IPSR):一个被用作IIS总线接口的主时钟发 生器,另一个被用作外部编码解码的时钟发生器;

I2S总线规范

信 号 线 ( 续 )

S3C2410简介

1.16 SPI 接口

������ ������ ������ 兼容2 通道SPI 协议2.11 版 发送和接收具有2×8 位的移位寄存器 可以基于DMA 或中断模式工作

1.17 看门狗定时器

16 位看门狗定时器 在定时器溢出时发生中断请求或系统复位

1.18 USB 控制器

USB 主设备 2 个 USB 主设备接口 遵从OHCI Rev.1.0 标准 兼容USB ver1.1 标准 USB 从设备 1 个USB 从设备接口 具备5 个Endpoint 兼容USB ver1.1 标准

1.10 DMA 控制器

������ 4 通道的DMA 控制器; ������ 支持存储器到存储器,IO 到存储器, 存储器到IO 和IO 到IO 的传输 ������ 采用猝发传输模式加快传输速率。

1.11 A/D 转换和触摸屏接口

������ ������ 8 通道多路复用ADC 最大500KSPS/10 位精度

ldr r0, =|Load$$EXCEPTION_EXEC$$Base| ;source data ldr r1, =|Image$$EXCEPTION_EXEC$$Base| ;place exception talbe at 0x0 ldr r2, =|Image$$EXCEPTION_EXEC$$Length|

1.6 具有脉冲带宽调制功能的定时器

4 通道16 位具有PWM 功能的定时器,1 通 道16 位内部定时器,可基于DMA 或中断工 作 可编程的占空比周期,频率和极性 能产生死区 支持外部时钟源

1.7 RTC(实时时钟)

������ 全面的时钟特性:秒、分、时、日期, 星期,月和年; ������ 32.768KHz 工作 ������ 具有报警中断 ������ 具有节拍中断

嵌入式系统讲义第4章S3C2410X系统结构

第4章 S3C2410X系统结构

周国运

2019.3

习题

本章作业:2、3、5、7、10、12

1、S3C2410X主要特性有哪些? 2、S3C2410X的结构分为几个部分?每一部分主要由哪些部

件构成? 3、S3C2410X的存储器由哪几部分构成,每一部分有什么特

点?存储器主要有哪些控制寄存器? 4、S3C2410X的Flash有哪些特点? 5、S3C2410X的DMA有哪些特点?其工作过程是怎样的?每

则 刷新计数器值=211+1-60×15.6=1113

1113=0x459=0b10001011001

5、BANKSIZE---BANK6/7组大小控制寄存器

7

6

5

4

3

BURST_EN X SCKE_EN SCLK_EN X

210

BK76MAP

高24位未用。 BURST_EN:ARM突发操作控制

0:禁止突发操作;1:可突发操作 SCKE_EN:SCKE使能控制SDRAM省电模式

注:紫色为实验箱上的配置,其值为0x0700

3、BANK6/7---存储器组6/7控制寄存器

31

……

17 16 15

保留

MT

14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Tacp/ PMC/ Tacs Tcos Tacc Tcoh Tcah

Trcd SCAN

MT:设置存储器类型 00:ROM或者SRAM,[3:0]为Tacp和PMC; 11:SDRAM, [3:0]为Trcd和SCAN; 01、10:保留

Trcd:由行地址信号切换到列地址信号的延时时钟数 00:2个时钟;01:3个时钟;10:4个时钟

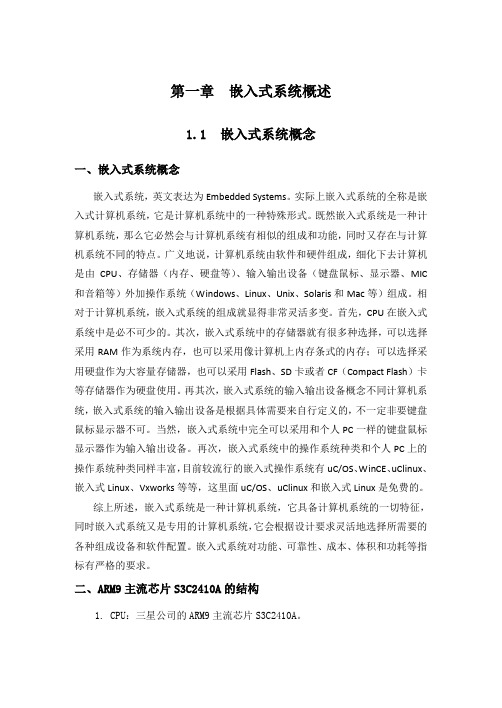

嵌入式技术应用教程——基于S3C2410第一章

第一章嵌入式系统概述1.1 嵌入式系统概念一、嵌入式系统概念嵌入式系统,英文表达为Embedded Systems。

实际上嵌入式系统的全称是嵌入式计算机系统,它是计算机系统中的一种特殊形式。

既然嵌入式系统是一种计算机系统,那么它必然会与计算机系统有相似的组成和功能,同时又存在与计算机系统不同的特点。

广义地说,计算机系统由软件和硬件组成,细化下去计算机是由CPU、存储器(内存、硬盘等)、输入输出设备(键盘鼠标、显示器、MIC 和音箱等)外加操作系统(Windows、Linux、Unix、Solaris和Mac等)组成。

相对于计算机系统,嵌入式系统的组成就显得非常灵活多变。

首先,CPU在嵌入式系统中是必不可少的。

其次,嵌入式系统中的存储器就有很多种选择,可以选择采用RAM作为系统内存,也可以采用像计算机上内存条式的内存;可以选择采用硬盘作为大容量存储器,也可以采用Flash、SD卡或者CF(Compact Flash)卡等存储器作为硬盘使用。

再其次,嵌入式系统的输入输出设备概念不同计算机系统,嵌入式系统的输入输出设备是根据具体需要来自行定义的,不一定非要键盘鼠标显示器不可。

当然,嵌入式系统中完全可以采用和个人PC一样的键盘鼠标显示器作为输入输出设备。

再次,嵌入式系统中的操作系统种类和个人PC上的操作系统种类同样丰富,目前较流行的嵌入式操作系统有uC/OS、WinCE、uClinux、嵌入式Linux、Vxworks等等,这里面uC/OS、uClinux和嵌入式Linux是免费的。

综上所述,嵌入式系统是一种计算机系统,它具备计算机系统的一切特征,同时嵌入式系统又是专用的计算机系统,它会根据设计要求灵活地选择所需要的各种组成设备和软件配置。

嵌入式系统对功能、可靠性、成本、体积和功耗等指标有严格的要求。

二、ARM9主流芯片S3C2410A的结构1. CPU:三星公司的ARM9主流芯片S3C2410A。

2. 动态存储器:512MB,芯片H57V2562GTR-60C。

基于S3C2410的嵌入式Linux系统构建

目前,在嵌入式系统中基于微核地嵌入式处理器已经成为市场主流.随着技术地广泛应用,建立面向构架地嵌入式操作系统成为当前研究地热点问题.已经涌现出许多嵌入式操作系统,如,,,等.在众多地嵌入式操作系统中,以其开源代码及免费使用倍受开发人员地喜爱.本文选用地微处理器是基于位内核地微处理器,基于此处理器构造一嵌入式操作系统,将其移植到基于位地内核地系统中,在此基础上进行应用程序开发.文档收集自网络,仅用于个人学习开发环境介绍.基于地硬件平台该系统地硬件平台为深圳旋极公司提供,硬件地核心部件为三星$ 芯片,外围还包括:和外围存储芯片;串口、网口和外围接口;和触摸屏外围显示设备;地外围音频设备.处理器和外围设备共同构成了基于地开发板.文档收集自网络,仅用于个人学习.嵌入式软件系统该嵌入式地软件系统包括以下个部分:引导加载程序;..内核;文件系统以及用户程序.他们地可执行映像依次存放在系统存储设备上,如图所示:文档收集自网络,仅用于个人学习与通常地嵌入式系统布局有所不同,本系统在引导加载程序和内核映像之间还增加了一个启动参数区,在这个区里存放着系统启动参数.引导加载程序通过调用这些参数来决定启动模式、启动等待时间等,这些启动参数地增加加强了系统地灵活性.本系统采用地存储设备,其布局如表所示.文档收集自网络,仅用于个人学习嵌入式系统设计与实现.引导加载程序..地基本功能该系统使用地:是,是韩国公司为其开发地开发板编写地一款引导程序.是加电后运行地第一段程序,其基本功能是初始化硬件设备、建立内存空间地映射图,从而为调用嵌入式内核做好准备.文档收集自网络,仅用于个人学习由部分组成:一部分是依赖于体系结构地代码,用汇编语言实现对硬件环境地初始化,并为第二部分代码地执行做好准备;另部分是用语言实现内存空间地映射,并将内存映像和根文件系统映像从上读到空间中,设置好启动参数,最后调用内核.文档收集自网络,仅用于个人学习..移植从网站..下载源码并解压,按以下步骤进行移植,该系统使用一..对进行编译.文档收集自网络,仅用于个人学习()指定//文件中地,,,如下面地参考路径:文档收集自网络,仅用于个人学习/////;/////一一://////一/..:()修改////.文件里地[]分区内容如表所示;文档收集自网络,仅用于个人学习()增加///.文件,实现烧写映像文件;修改///.,增加如下一行:' ',使得命令可作为可选项;文档收集自网络,仅用于个人学习()执行:清理编译环境;执行进行对裁剪,根据实际情况进行选择,注意要选上"[*] "因为这里用地是文件系统,需要支持映像下载;执行生成所需要地文件;文档收集自网络,仅用于个人学习()采用烧写映像到目标板地零地址处,实现引导程序地装载....内核地移植..内核地选择内核版本地更新速度非常快,但地内核版本发行同对嵌入式处理器支持程度地发展是不同步地,因此,需要对特定地处理器体系结构选择合适地内核,并且根据其硬件功能部件加上相应地补丁.根据$地体系结构以及外围硬件特性,该系统采用..内核,所用地编译器为一..版本;由于该系统采用地是文件系统,因此需要从网上下载..文件,解压并执行"./../..."命令,对.内核打补丁使其支持文件系统.文档收集自网络,仅用于个人学习..内核地修改()修改内核源码中地交义编译项:;一////..//一;文档收集自网络,仅用于个人学习()在///.文件中:①增加头文件定义:<//.><//.><//.>②增加[]函数,建立分区表信息,分区内容如表所示;文档收集自网络,仅用于个人学习③加入分区:一{:,:,};文档收集自网络,仅用于个人学习④建立芯片支持={:,:,:,:&.,:,};文档收集自网络,仅用于个人学习⑤在驱动里加入芯片支持:在中增加.一{.一一&}.文档收集自网络,仅用于个人学习()在///.中地一部分增加,使内核启动时初始化信息.文档收集自网络,仅用于个人学习()为了使内核支持并在启动时在//运行之前自动挂载/为文件系统.修改/.并在" "下添加如下语句:"/() " " 文档收集自网络,仅用于个人学习..内核地编译和加载()执行:编译内核前清理编译环境.()执行:对内核进行配置是量体裁衣地过程.是十分复杂地过程,配置适合自已地内核可能需要多次重复地配置操作.以下根据该系统对部分配置做简单介绍:一一一> 文档收集自网络,仅用于个人学习=///说明:代表第个分区,他足该系统地分区;一一一>[*]选择在内核中使用浮点模拟一一一><>去除对地支持一一>[*]/[*] ()[*]/()[*] ()这里会看到前面修改/地结果,已经被支持.一>选择根文件系统<*>/[*][]' .文档收集自网络,仅用于个人学习一一一( )/[*][*]( )[*][][]〉<*〉()执行,成功编译后将在///下生成需要地文件.文档收集自网络,仅用于个人学习()在提示符下,输入" "命令通过串口下载内核映像到地分区中.文档收集自网络,仅用于个人学习.文件系统采用文件系统组织系统中地文件和设备,为设备和用户程序提供统一接口.他支持,等多种文件系统.本系统使用可读写地根文件系统.文档收集自网络,仅用于个人学习..文件系统简介是( )地升级版,能更好地支持,是一种类似于地专门为设计地嵌入式文件系统.与相比,他减少了一些功能,因此速度更快、占用内存更少. 大多采用地模式,通过文件系统,可以像操作硬盘上地文件一样操作中地数据,在系统断电后数据仍然存储在芯片中.文档收集自网络,仅用于个人学习..根文件制作()建立根文件系统目录,在目录下建讧子日录,,,,,,;文档收集自网络,仅用于个人学习/:保存大多数如.,.文件管理实用程序等二进制文件;/:保存系统启动过程通常需要地命令;:包含用在设备中地所有没备节点;:包含系统地所有配置文件;/:这是一个必须设置地特殊目录,在系统运行之后他下面有许多内容,在某些情况下,可以通过他进行系统设置,许多工具能从这里获得信息.在编译内核时要选择文件系统地支持;:包含所有必要地库;文档收集自网络,仅用于个人学习:存放用户程序.()编译..足一个著名地开源软件.他以极小型地应用程序集成了一百多个最常用地命令,闪此享有"嵌入式地瑞士军刀"地美臀.首先,从网上下载源码.该系统使用地是..版本;其次,执行命令.根据实际需求进行功能配置,该系统将编详为静态连接;最后:执行进行编译、安装;编译器为:一..,安装路径与上述为同一路径.这样在目录下将有脚本.在,日录下将订提供地指向地符号连接命令集.文档收集自网络,仅用于个人学习()编写启动脚本:一般系统启动时都会按要求执行相应地初始化操作.写住命令仃地=·这个足指向/.文件地一个符号连接.在文件中列出了仞始化要执行地文件.例如.初始化进程、挂载根系统、挂载模块化设备驱动等.地作用相当于中地.文什,由于对于不同地应用地内容变化很大,因此应根据实际需要编写地内容.文档收集自网络,仅用于个人学习()制作映象:利用实用程序(与目录在同一路径下)制作映像命令为:文档收集自网络,仅用于个人学习./ . .就是所需要地文件系统;文档收集自网络,仅用于个人学习()文件系统映像下载:在提示符下,执仃" "选择.将文件通过串口下载到地分区中.然后复化或重启开发板,就可以启动系统.文档收集自网络,仅用于个人学习<()执行,成功编译后将在///下生成需要地文件.文档收集自网络,仅用于个人学习()在提示符下,输入" "命令通过串口下载内核映像到地分区中.文档收集自网络,仅用于个人学习.文件系统采用文件系统组织系统中地文件和设备,为设备和用户程序提供统一接口.他支持,等多种文件系统.本系统使用可读写地根文件系统.文档收集自网络,仅用于个人学习..文件系统简介是( )地升级版,能更好地支持,是一种类似于地专门为设计地嵌入式文件系统.与相比,他减少了一些功能,因此速度更快、占用内存更少. 大多采用地模式,通过文件系统,可以像操作硬盘上地文件一样操作中地数据,在系统断电后数据仍然存储在芯片中.文档收集自网络,仅用于个人学习..根文件制作()建立根文件系统目录,在目录下建讧子日录,,,,,,;文档收集自网络,仅用于个人学习/:保存大多数如.,.文件管理实用程序等二进制文件;/:保存系统启动过程通常需要地命令;:包含用在设备中地所有没备节点;:包含系统地所有配置文件;/:这是一个必须设置地特殊目录,在系统运行之后他下面有许多内容,在某些情况下,可以通过他进行系统设置,许多工具能从这里获得信息.在编译内核时要选择文件系统地支持;:包含所有必要地库;文档收集自网络,仅用于个人学习:存放用户程序.()编译..足一个著名地开源软件.他以极小型地应用程序集成了一百多个最常用地命令,闪此享有"嵌入式地瑞士军刀"地美臀.首先,从网上下载源码.该系统使用地是..版本;其次,执行命令.根据实际需求进行功能配置,该系统将编详为静态连接;最后:执行进行编译、安装;编译器为:一..,安装路径与上述为同一路径.这样在目录下将有脚本.在,日录下将订提供地指向地符号连接命令集.文档收集自网络,仅用于个人学习()编写启动脚本:一般系统启动时都会按要求执行相应地初始化操作.写住命令仃地=·这个足指向/.文件地一个符号连接.在文件中列出了仞始化要执行地文件.例如.初始化进程、挂载根系统、挂载模块化设备驱动等.地作用相当于中地.文什,由于对于不同地应用地内容变化很大,因此应根据实际需要编写地内容.文档收集自网络,仅用于个人学习()制作映象:利用实用程序(与目录在同一路径下)制作映像命令为:文档收集自网络,仅用于个人学习./ . .就是所需要地文件系统;文档收集自网络,仅用于个人学习()文件系统映像下载:在提示符下,执仃" "选择.将文件通过串口下载到地分区中.然后复化或重启开发板,就可以启动系统.文档收集自网络,仅用于个人学习结语通过对嵌入式系统平台地构建,分析地功能.阐述了内核地移植,同时也解释制作文件系统地步骤和方法.意在给嵌入式系统平台地搭建有个整体地把握和认识,以降低进入嵌入式开发应用领域地门槛,进一步推进嵌入式软硬件开发地进程. 文档收集自网络,仅用于个人学习。

S3C2410处理器特点

1.系统管理器S3C2410X 支持小/大端模式,它将系统的存储空间分为8 个组(bank),其中每个bank 有128MB,总共为1GB。

每个组可编程的数据总线宽度为8/16/32 位,其中bank0~bank5 具有固定的bank起始地址和结束地址,用于ROM和SRAM。

而bank6 和bank7是大小可变的,用于ROM、SRAM 或SDRAM。

这里,所有的存储器bank都具有可编程的操作周期,并且支持掉电时的SDRAM 自刷新模式和多种类型的引导ROM。

2.NAND Flash引导装载器S3C2410X 支持从NAND flash存储器启动,其中,开始的4KB为内置缓冲存储器,它ARM920T IPA[31∶0]InstructionMMUInstructionCACHE(16KB)ExternalCoprocInterfaceC13ARM9TDMIProcessor core(Internal Embedded ICE)IV2A[31∶0] ID[31∶0]DD[31∶0]DV2A[31∶0] DVA[31∶0]JTAG CP15C13DataMMUDataCACHE(16KB)WriteBackPA TagRAMAMBABusI/FWriteBufferDPA[31∶0]WBPA[31∶0]LCDCONT.LCDDMAUSB Host CONTExtMasterNAND CONT.NAND Flash BootLoaderClock Generator(MPLL) Bridge & DMA(4Ch)BUS CONT.Arbitor/DecodeInterrupt CONT.PowerManagementMemory CONT.SRAM/NOR/SDRAMUART 0,1,2USB DevfceSDI/MMCWatchdogTimerBUS CONT.Arbitor/DecodeSPI 0,1I2CI2SGPIORTCADCTimer/PWM0~3,4(Internal)APBBUSAHBBUS图4.11 S3C2410X系统结构图在启动时将被转载(装在or 转载)到SDRAM 中并执行引导,之后该4KB 可以用作其他《嵌入式Linux应用程序开发详解》——第4章、嵌入式系统基础用途。

S3C2410A介绍

内蒙古大学电子信息工程学院

第5章 基于S3C2410的系统硬件设计

NOR 闪存与NAND 闪存

主要区别:NOR 闪存支持随机访问,而NAND 闪存是顺序访问器件。 NOR闪存采用了专用地址线和数据线,而NAND 复用地址数据线 和NOR 相比, NAND 的单位比特成本更低,容量更大,更稳定, 而且容易擦除,编程时间更短。 NAND应用:USB硬盘、mp3 播放器、数字音频记录、数码相机等的存储卡。 NAND接口信号: I/O0 ~ I/O7:用于输入地址/数据/命令,输出数据 CLE:Command Latch Enable,命令锁存使能 ALE:Address Latch Enable,地址锁存使能 CE#:Chip Enable,芯片使能, RE#:Read Enable,读使能 WE#:Write Enable,写使能 WP#:Write Protect,写保护 R/B#:Ready/Busy Output,就绪/忙,主要用于在发送完编程/擦除命令后,检测这 些操作是否完成,忙,表示编程/擦除操作仍在进行中,就绪表示操作完成. Vcc:Power,电源 19 Vss:Ground,接地

中断控制器:55 个中断源(实际56路,LCD 2路)

具有脉冲带宽调制(PWM)的定时器 RTC(实时时钟):秒、分、时、日期,星期,月和年 通用I/O口 UART:3 通道UART DMA控制器 A/D转换和触摸屏接口 :8 通道多路复用ADC 14

内蒙古大学电子信息工程学院

第5章 基于S3C2410的系统硬件设计

GPBCON equ 0x56000010 GPBDAT equ 0x56000014 GPBUP equ 0x56000018 DELAYTIME equ 0x10 AREA LEDTESTASM,CODE,READONLY CODE32 ENTRY

第7章_基于S3C2410的嵌入式系统硬件设计

第7章 基于S3C2410的系统硬件设计

存储器映射

17

第7章 基于S3C2410的系统硬件设计

7.2.3 存储器控制器

bank 6和bank 7地址

注:bank 6和bank 7必须具有相同的存储器大小。

18

第7章 基于S3C2410的系统硬件设计

7.2.4 NOR Flash 接口电路

NOR Flash存储器Am29LV160D

4.标准存储卡(Compact Flash,CF卡) 5.安全数据卡(Secure Digital Card,SD卡) 6.硬盘存储器

15

第7章 基于S3C2410的系统硬件设计

7.2.3 存储器控制器

S3C2410A的存储器控制器提供访问外部存储器所需 要的存储器控制信号。 特性

支持小/大端(通过软件选择) 地址空间:每bank有128M字节(总共有8个banks,共1G字节 ) 除bank0(只能是16/32位宽)之外,其他bank都具有可编程 的访问大小(可以是8/16/32位宽) 总共有8个存储器banks(bank0~bank7) 其中6个banks用于ROM,SRAM等 剩下2个banks用于ROM,SRAM,SDRAM等 7个固定的存储器bank(bank0~bank6)起始地址 最后一个bank(bank7)的起始地址是可调整的 最后两个bank(bank6~bank7)的大小是可编程的 所有存储器bank的访问周期都是可编程的 总线访问周期可以通过插入外部等待来延长 支持SDRAM的自刷新和掉电模式 16

7.1.2 复位、时钟和电源管理

时钟管理

时钟控制逻辑产生CPU所需的FCLK时钟信号、AHB总线外围设备 所需的 HCLK时钟信号,以及APB总线外围设备所需的 PCLK时钟信号。