微型计算机技术课后习题及答案

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

4.1 用下列芯片构成存储系统,各需要多少个RAM芯片?需要多少位地址作为片外地址译码?设系统位20位地址线,采用全译码方式

(1)512×4b RAM构成16KB的存储系统

1、首先进行位的扩展,存储系统一般以字节为单位进行存储,所以需要两个512×4位的RAM来达到系统要求的一个字节的字长,两个为一组。

2、接着进行字的扩展,因系统要求为16KB,那16KB个字,需要16KB/512bit=32(组)。

3、芯片个数=位扩展*字扩展=32*2=64(个)。

1、因2的9次方=512,所以,片内地址位数=9(位);

2、片外地址译码位数=地址线总数-片内地址译码位数=20-9=11(位)

(2)1024×1b RAM构成128KB的存储系统需要128KB/1K*8=1024片;片外地址译码需10位地址线(3)2k×4b RAM构成64KB的存储系统需要64KB/2K * 2=64片;片外地址译码需9位地址线(4)64k×1b RAM构成256KB的存储系统需要256KB/64K * 8位= 32片;片外地址码需4位地址线

4.2 现有一个钟存储芯片容量为512×4b,若要用它实现4KB的存储容量,需要多少这样的存储芯片?每片芯片需要多少条寻址线?而4KB存储系统最少需要多少条寻址线?

4KB/ 512×4b= 16,需要16片,每片芯片需9条寻址线,4KB存储系统最少需12条寻址线

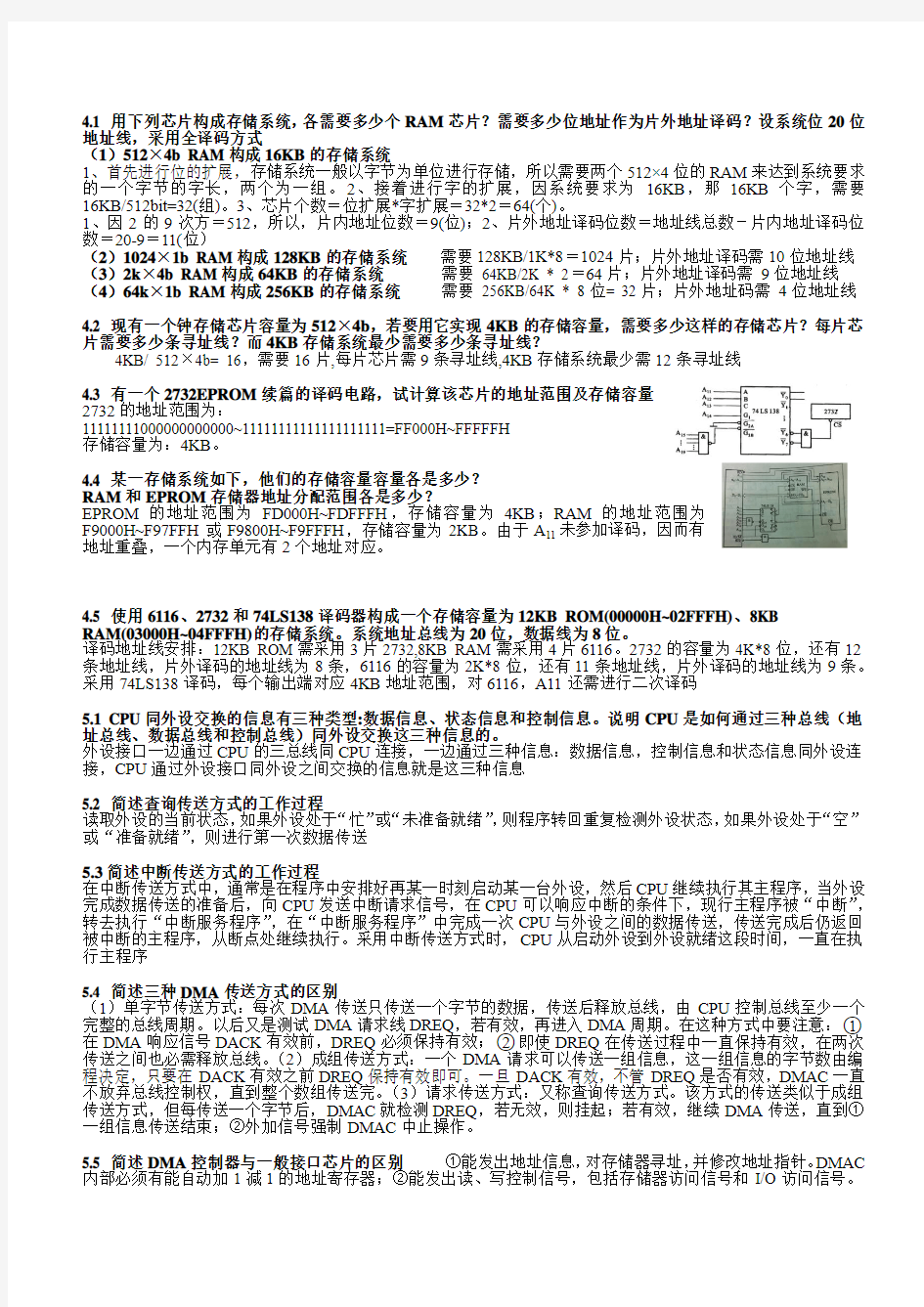

4.3 有一个2732EPROM续篇的译码电路,试计算该芯片的地址范围及存储容量

2732的地址范围为:

11111111000000000000~11111111111111111111=FF000H~FFFFFH

存储容量为:4KB。

4.4 某一存储系统如下,他们的存储容量容量各是多少?

RAM和EPROM存储器地址分配范围各是多少?

EPROM的地址范围为FD000H~FDFFFH,存储容量为4KB;RAM的地址范围为

F9000H~F97FFH或F9800H~F9FFFH,存储容量为2KB。由于A11未参加译码,因而有

地址重叠,一个内存单元有2个地址对应。

4.5 使用6116、2732和74LS138译码器构成一个存储容量为12KB ROM(00000H~02FFFH)、8KB

RAM(03000H~04FFFH)的存储系统。系统地址总线为20位,数据线为8位。

译码地址线安排:12KB ROM需采用3片2732,8KB RAM需采用4片6116。2732的容量为4K*8位,还有12条地址线,片外译码的地址线为8条,6116的容量为2K*8位,还有11条地址线,片外译码的地址线为9条。采用74LS138译码,每个输出端对应4KB地址范围,对6116,A11还需进行二次译码

5.1 CPU同外设交换的信息有三种类型:数据信息、状态信息和控制信息。说明CPU是如何通过三种总线(地址总线、数据总线和控制总线)同外设交换这三种信息的。

外设接口一边通过CPU的三总线同CPU连接,一边通过三种信息:数据信息,控制信息和状态信息同外设连接,CPU通过外设接口同外设之间交换的信息就是这三种信息

5.2 简述查询传送方式的工作过程

读取外设的当前状态,如果外设处于“忙”或“未准备就绪”,则程序转回重复检测外设状态,如果外设处于“空”或“准备就绪”,则进行第一次数据传送

5.3简述中断传送方式的工作过程

在中断传送方式中,通常是在程序中安排好再某一时刻启动某一台外设,然后CPU继续执行其主程序,当外设完成数据传送的准备后,向CPU发送中断请求信号,在CPU可以响应中断的条件下,现行主程序被“中断”,转去执行“中断服务程序”,在“中断服务程序”中完成一次CPU与外设之间的数据传送,传送完成后仍返回被中断的主程序,从断点处继续执行。采用中断传送方式时,CPU从启动外设到外设就绪这段时间,一直在执行主程序

5.4 简述三种DMA传送方式的区别

(1)单字节传送方式:每次DMA传送只传送一个字节的数据,传送后释放总线,由CPU控制总线至少一个完整的总线周期。以后又是测试DMA请求线DREQ,若有效,再进入DMA周期。在这种方式中要注意:○1在DMA响应信号DACK有效前,DREQ必须保持有效;○2即使DREQ在传送过程中一直保持有效,在两次传送之间也必需释放总线。(2)成组传送方式:一个DMA请求可以传送一组信息,这一组信息的字节数由编程决定,只要在DACK有效之前DREQ保持有效即可。一旦DACK有效,不管DREQ是否有效,DMAC一直不放弃总线控制权,直到整个数组传送完。(3)请求传送方式:又称查询传送方式。该方式的传送类似于成组传送方式,但每传送一个字节后,DMAC就检测DREQ,若无效,则挂起;若有效,继续DMA传送,直到①一组信息传送结束;②外加信号强制DMAC中止操作。

5.5 简述DMA控制器与一般接口芯片的区别①能发出地址信息,对存储器寻址,并修改地址指针。DMAC 内部必须有能自动加1减1的地址寄存器;②能发出读、写控制信号,包括存储器访问信号和I/O访问信号。

5.6画出查询传送方式输出数

6.1 根据接口电路功能,简要说明I/O接口电路应包括哪些电路

据的流程图单

(1)实现CPU与外设之间的数据传送——数据端口

(2)在程序查询的I/O方式中,便于CPU与接口电路或外设之间用应答方

式

来交换信息——控制命令寄存器和状态寄存器

(3)在中断传送的I/O方式中,必须提供各种中断控制功能——中断控制逻

辑

(4)具有选择接口电路中不同端口的功能——地址译码器

(5)能对地址译码器选中的端口实现读写操作——读写控制逻辑。

6.2 扼要说明8255A工作在方式0和方式1的区别

方式0可以工作于无条件传送方式,也可工作于查询传送(条件传送)方式,可由用户选择PCL和PCH中各一条线作为PA口和PB口的联络信号线,方式0不能工作于中断传送方式;方式1可以工作于查询传送方式和中断传送方式,芯片规定了PC口中6条线作为PA 口和PB口同外设之间的联络信号线以及同CPU之间的中断请求线。

6.3试说明8255A在方式1输入时的工作过程

当外设准备好数据,在传送数据的同时,送出一个选通信号STB,8255A的A口数据锁存器在STB,下降沿控制下降数据锁存。8255A向外设送出高电平的IBF,表示锁存数据已完成,暂时不要再传送数据

6.4 试说明8255A在方式1输出时的工作过程

当输出缓冲器满信号OBF为高电平时,CPU执行输出指令,CPU输出的数据送入8255AA口,并使INTR复位,OBF置为低电平,通知输出设备CPU已把数据输出到了8255A的A口,输出设备接到OBF信号有效后,发ACK有效,ACK下降沿将OBF置为1,ACK上升沿表示输出设备已从8255A指定端口取走数据,此时若INTE=1,则INTR被置为高电平,向CPU申请中断,CPU可采用中断方式输出下一个数据。CPU也可通过查询OBF信号,若OBF=1,CPU输出下一个数据给8255A,即用查询方式传送数据。

6.5 8255A的3个端口在使用时有什么区别

通常端口A或B作为输入输出的数据端口(端口A还可以作为双向数据端口),而端口C作为控制或状态信息的端口,它在"方式"字的控制下,可以分成两个4位的端口。每个端口包含一个4位锁存器。它们分别与端口A 和B配合使用,可用以作为控制信号输出,或作为状态信号输入。

6.6 说明8251A引脚信号中RTS、CTS、DTS和DSR的作用

DTR这是一个通用的输出信号,可由命令字的位1置“1”而变为有效,用以表示CPU准备就绪

DSR这是一个通用的输入信号,用以表示调制解调器或外设的数据已准备好

DTS此信号用于通知调制器,CPU已准备好发送,它可由命令字的位5置“1”而变为有效

CTS这是调制解调器或其他外设送到8251A中的调制解调器信号。当其有效时,表示允许USART传送数据

6.7 什么是8251A的方式指令字和命令指令字?对两者在串行通信中的写入流程进行说明

方式指令字:指定8251A为异步方式还是同步方式,并按照其通信方式约定帧数据格式。

命令指令字:命令的作用是确定8251A的实际操作,迫使8251A进行某种操作或处于某种工作状态,以便接收或发送数据

6.8 异步通信中,异步的含义是什么?

发送器和接收器不共享共用的同步信号,也不在数据中传送同步信号

6.9 8251A的状态字哪几位和引脚信号有关?状态位T X RDY和引脚信号T X RDY有什么区别,他们在系统设计中有什么用处

状态寄存器的1、2、6位分别与8251A引脚RxRDY,TxE,SYNDET上的信号有关。状态位TxRDY和引脚信号TxRDY上的信号不同,状态位TxRDY不受输出信号CTS和控制位TxEN的影响。而引脚TxRDY必须在数据缓冲区为空,CTS为低电平且TxEN为高电平时,才为1

6.10 8251A芯片控制信号CS和C/D的功能

CS:片选输入。该引脚输入低电平时,芯片可以和CPU传输数据,反之芯片的8个数据引脚处于悬空状态

C/D:一个决定CPU对芯片读/写内容的控制输入。如果输入为高电平,CPU对芯片就是写控制字或读状态字,反之读/写内容就是数据