微机原理课后题答案(5_7章)

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

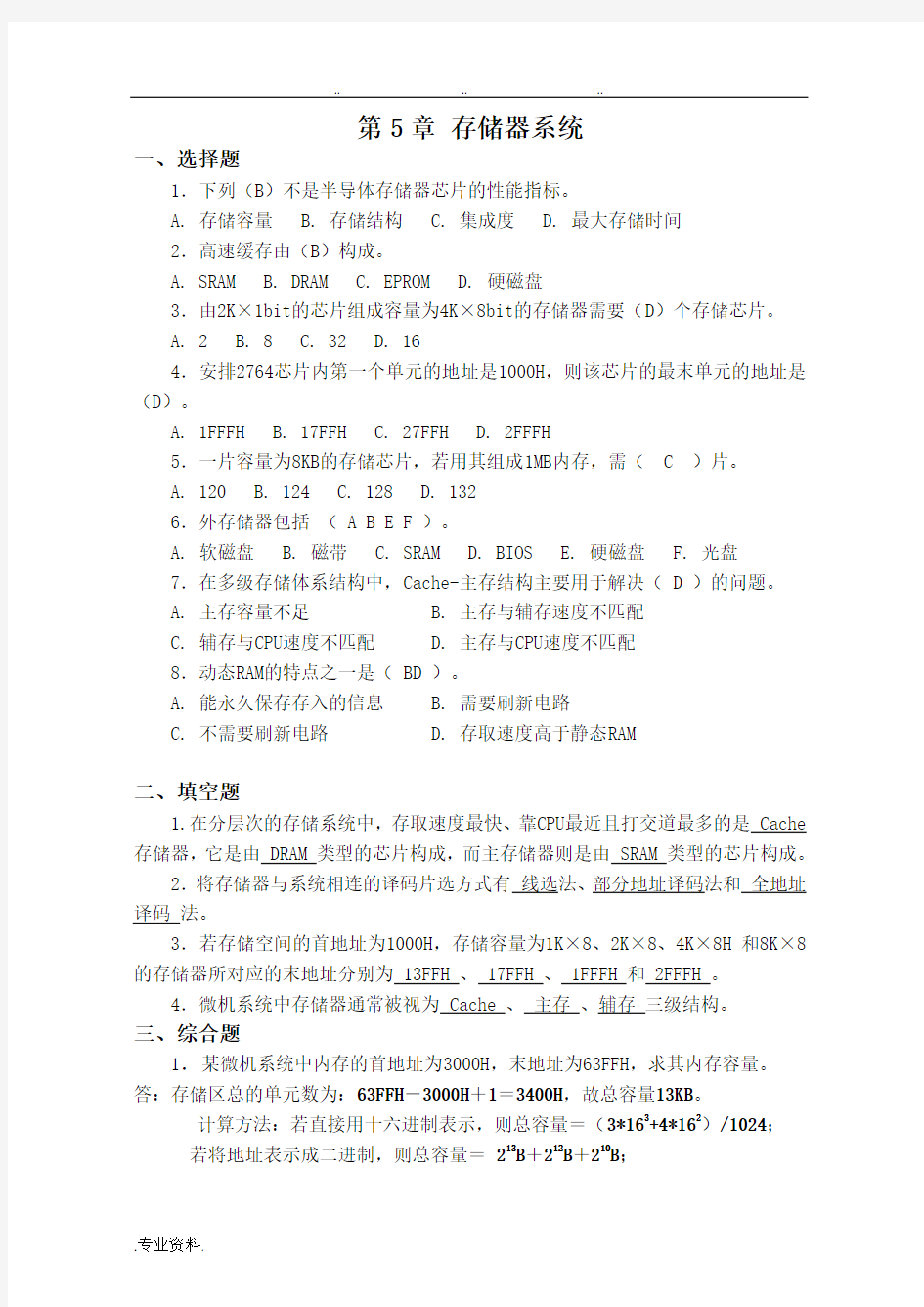

第5章存储器系统

一、选择题

1.下列(B)不是半导体存储器芯片的性能指标。

A. 存储容量

B. 存储结构

C. 集成度

D. 最大存储时间

2.高速缓存由(B)构成。

A. SRAM

B. DRAM

C. EPROM

D. 硬磁盘

3.由2K×1bit的芯片组成容量为4K×8bit的存储器需要(D)个存储芯片。

A. 2

B. 8

C. 32

D. 16

4.安排2764芯片内第一个单元的地址是1000H,则该芯片的最末单元的地址是(D)。

A. 1FFFH

B. 17FFH

C. 27FFH

D. 2FFFH

5.一片容量为8KB的存储芯片,若用其组成1MB内存,需( C )片。

A. 120

B. 124

C. 128

D. 132

6.外存储器包括( A B E F )。

A. 软磁盘

B. 磁带

C. SRAM

D. BIOS

E. 硬磁盘

F. 光盘

7.在多级存储体系结构中,Cache-主存结构主要用于解决( D )的问题。

A. 主存容量不足

B. 主存与辅存速度不匹配

C. 辅存与CPU速度不匹配

D. 主存与CPU速度不匹配

8.动态RAM的特点之一是( BD )。

A. 能永久保存存入的信息

B. 需要刷新电路

C. 不需要刷新电路

D. 存取速度高于静态RAM

二、填空题

1.在分层次的存储系统中,存取速度最快、靠CPU最近且打交道最多的是 Cache 存储器,它是由 DRAM 类型的芯片构成,而主存储器则是由 SRAM 类型的芯片构成。

2.将存储器与系统相连的译码片选方式有线选法、部分地址译码法和全地址译码法。

3.若存储空间的首地址为1000H,存储容量为1K×8、2K×8、4K×8H 和8K×8的存储器所对应的末地址分别为 13FFH 、 17FFH 、 1FFFH 和 2FFFH 。

4.微机系统中存储器通常被视为 Cache 、主存、辅存三级结构。

三、综合题

1.某微机系统中内存的首地址为3000H,末地址为63FFH,求其内存容量。答:存储区总的单元数为:63FFH-3000H+1=3400H,故总容量13KB。

计算方法:若直接用十六进制表示,则总容量=(3*163+4*162)/1024;

若将地址表示成二进制,则总容量=213B+212B+210B;

2.下图为SRAM6116芯片与 8088系统总线的连接图。

(1)写出6116芯片的存储容量;

(2)分析每片6116所占的内存地址范围。

答:

(1)6116芯片的存储容量是

2k*8bit

(2)第一片6116的内存地址

范围是F1000H~F17FFH

第二片6116的内存地址

范围是F1800H~F1FFFH

3.利用6264芯片,在8088

系统总线上实现20000H-

23FFFH的内存区域,试画出连接电路图。

答:

4.如图所示,IBM-PC/XT计算机扩展槽上与存储器连接的总线信号为20根地址线A19~A0,8根数据线D7~D0以及存储器读写信号MEMR和MEMW。使用这些信号扩展1片27256(32K×8 EPROM)和1片62256(32K×8 RAM)。要求EPROM的起始地址为C8000H,RAM紧随其后,使用74LS138(3-8译码器),采用全地址译码方式。

(1

。

(2)写出各片存储器的地址范围。

答:地址范围27512:C8000~CFFFFH, 62512:D0000H~D7FFFH

5.设某系统中的数据总线宽度为8bit ,地址总线宽度为16bit 。若采用4K ×4的RAM 芯片组成16KB 的存储系统。问:

(1)共需多少片4K ×4的RAM 芯片?这些芯片应分成多少组?每组多少片? 答:共需8片RAM 芯片,分成4组,每组2片。

(2)该存储系统至少需要多少根地址总线?其中多少根低位地址线用于片内自A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

D6 D5 D4 D3 D2 D1 D0

D7 MEMR

MEMW A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

D6 D5 D4 D3 D2 D1 D0

D7 MEMR MEMW

选(译码)?

答:至少需要14根地址总线,其中12根低位地址线用于片内自选。

(3)设该存储系统从0000H开始占用一段连续地址空间,试给出每组芯片占用的地址范围。

答:0000~0FFFH 1000~1FFFH 2000~2FFFH 3000~3FFFH

第6章输入输出与中断技术

一、单项选择题

1.8086CPU在执行IN AL,DX指令时,DX寄存器的内容输出到( A )上。

A. 地址总线

B. 数据总线

C. 存储器

D. 寄存器

2.在CPU与外设进行数据传送时,下列( C )方式可提高系统的工作效率。

A. 无条件传送

B. 查询传送

C. 中断传送

D. 前三项均可

3.外部设备的端口包括( ABC )。

A. 数据端口

B. 状态端口

C. 控制端口

D. 写保护口

4.CPU 在数据线上传输的信息可能是( ABC )。

A. 数据

B. 状态

C. 命令

D. 模拟量

5.PC/XT机对I/O端口的寻址方式有( AF )。

A. 端口直接寻址

B. 寄存器寻址

C. 基址寻址

D. 变址寻址

E. 寄存器相对寻址

F. DX 间接寻址

6.PC机在和I/O端口输入输出数据时,I/O数据须经( AE )传送。

A. AL

B. BL

C. CL

D. DL

E. AX

F. BX

G. CX

H. DX

7.程序查询I/O的流程总是按( B )的次序完成一个字符的传输。

A. 写数据端口,读/写控制端口

B.读状态端口,读/写数据端口

C. 写控制端口,读/写状态端口

D. 随I/O接口的具体要求而定。

8.在CPU与外设之间设计接口电路的目的主要有(ABCD)。

A. 解决驱动能力问题

B. 控制数据传输速度

C. 完成数据形式转换

D. 负责CPU与外设的联络

9.8086CPU工作在总线请求方式时,会让出( D )。

A. 地址总线

B. 数据总线

C. 地址和数据总线

D. 地址、数据和控制总线

10.CPU响应INTR引脚上来的中断请求的条件之一是( B )。

A. IF =0

B. IF =1

C. TF =0

D. TF =1

11.断点中断的中断类型码是( C )。

A. 1

B. 2

C. 3

D. 4

12.执行指令IRET后弹出堆栈的寄存器先后顺序为( B )。

A. CS、IP、Flags

B. IP、CS、Flags

C. Flags、CS、IP

D. Flags、IP、CS

13.若8259A工作在优先级自动循环方式,则IRQ4的中断请求被响应并且服务完毕后,优先权最高的中断源是( B )。

A. IRQ3

B. IRQ5

C. IRQ0

D. IRQ4

14.PC/XT机中若对从片8259A写入的ICW2是70H,则该8259A芯片的IRQ6的中断类型码是( B )。