new实验六(序列信号发生器)

实验8 序列信号发生器

实验8 序列信号发生器实验目的:1. 熟悉掌握EDA软件工具Multisim 的仿真测试应用。

2. 熟悉序列信号发生器的工作原理。

3. 学习序列信号发生器的设计方法。

实验仪器设备与主要器件:实验箱一个;双踪示波器一台;稳压电源一台;函数发生器一台。

4位十进制加法计数器74LS160;4位二进制加法计数器74LS161。

8选1数据选择器74LS251、74LS152、74LS151。

实验内容:1. 用计数器74LS160设计一个7位巴克码(0100111)的产生电路,画出电路时序图。

用示波器观察电路输出的波形。

实验原理:先设计计数器。

由于序列长度为7,所以选用74LS160设计一个八进制计数器。

现采用置零法,有效状态为0000~0110,所以=。

然后设计组合输出电路。

令计数器计数过程中每一状态的输出符合给定序列要求,用8选一数据选择器74LS251.实现逻辑函数,且数据选择器的数据输入端所置数为:D0D1D2D3D4D5D6D7 0100111*实验电路:实验分析:如电路图所示,将计数器的输出QCQBQA作用于数据选择器的地址输入端,于是,每计一个数,数据选择器就输出一个预先置好的数据。

当CP信号持续不断地加到计数器上,QCQBQA的状态(也即74LS251的地址输入代码)按0000~0110的顺序不断循环,对应的输出也不断地循环:0100111实验结果与现象:2. 设计灯光控制逻辑电路。

要求红、绿、黄三种颜色的灯在时钟信号作用下按表2—8—2规定的顺序转换状态。

表中,1表示“亮”,0表示“灭”。

CP顺序红绿黄0 0 0 01 1 0 02 0 1 03 0 0 14 1 1 15 0 0 16 0 1 07 1 0 08 0 0 0实验原理:先设计计数器。

从表2—8—2可以看出三个序列信号的序列长度为8,所以选用74LS160设计一个八进制计数器。

现采用置零法,有效状态为0000~0111,所以=。

实验六 DDS信号发生器设计

实验五DDS信号发生器设计一.实验目的:学习利用EDA技术和FPGA实现直接数字频率综合器DDS的设计。

二.实验设备:1.电脑,quartus ii 集成开发环境2.GX_SOPC_EP3C10_EDK系统三.实验实训要求1.使用quartus ii 集成开发环境完成直接数字频率综合器DDS的设计2.利用GX_SOPC_EP3C10_EDK系统和电脑完成实验并观察波形四.实验原理:参考6.12节。

图6-72是根据图6-71的基本DDS原理框图作出的电路原理图的顶层设计,其中相位累加器的位宽是32。

图中共有六组元件模块和一些接口,说明如下:图6-72 DDS信号发生器顶层原理图(1) 32位加法器ADDER32。

由LPM_ADD_SUB宏模块构成。

设置了2级流水线结构,使其在时钟控制下有更高的运算速度和输入数据稳定性。

(2) 32位寄存器DFF32。

由LPM_FF宏模块担任。

ADDER32与DFF32构成一个32位相位累加器,其高8位A[31..24]作为波形数据ROM的地址。

(3) 正弦波形数据ROM。

正弦波形数据ROM模块sin_8X8的地址线和数据线位宽都是8位。

这就是说,其中的一个周期的正弦波数据有256个,每个数据有8位。

其输出可以接一个8位的高速DAC。

ROM中的MIF数据文件可用专用软件工具获得,这里不再深入探讨。

(4) 频率控制字输入B[20..17]由计数器CNT4B产生。

本来的频率控制字是32位的,但为了方便实验验证,把高于20和低于17的输入位预先设置成0或1。

频率控制字B[31..0]与由DAC[7..0]驱动的DAC 的正弦信号频率的关系,可以由公式CLK out f B f 322]0..31[ 算出。

其中f out 为DAC 输出的正弦波信号频率,f clk 是CLK 的时钟频率,直接输入是50MHz ,接入锁相环后可达到更高频率。

频率上限要看DAC 的速度。

如果接高速DAC ,如10位的5651,输出速度可达180MHz 。

序列发生器实验设计举例

1

1

d d

1

D1=Q1’

Q3Q2 Q1

1 1

Q3Q2 Q1

d d

D2=Q3’Q2’Q1+Q2Q1’

1

Q3Q2 Q1

d d

1

D3=Q3Q1’+Q2Q1

1 1

1

d d

1

Z= Q3’Q2’+Q1

• 构成实际电路时,用与门(74LS08)和或门 构成实际电路时,用与门 和或门(74LS32) 和或门 触发器(74LS175)实现,具体电路如下: 实现, 及D触发器 触发器 实现 具体电路如下:

Qn*=Dn

原状态 Q3 Q2 Q1 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 0 0 0 ┇

次态 Q3*Q2*Q1* 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 0 0 0 0 0 1 ┇

输出 Z 1 1 0 1 0 1 1 ┇

激励值 D3 D2 D1 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 0 0 0 0 0 1 ┇

Hale Waihona Puke • 正沿触发4D触发器CLR 0 1 1 CP x ↑ 0或1 功能 清零(Q=0) 接数(Q=D) 保持

• 正与门和正或门

功能: 功能:Y=A·B 四 2输入与门 输入与门

功能: 功能:Y=A+B 四 2输入或门 输入或门

实验十二 110101序列发生器

实验要求: 实验要求: 电路用D触发器 触发器( )、2输入与门 电路用 触发器(74LS175)、 输入与门 )、 )、2输入或门 (74LS08)、 输入或门(74LS32)实现。 )、 输入或门( )实现。 用同步Gray码模6计数器产生 计数器产生110101序列。 序列。 用同步 计数器产生 序列 状态变化为: 状态变化为: 000→001→011→010→110→100 要求设计出相应的电路图。 要求设计出相应的电路图。

信号发生器实验步骤

信号发生器实验步骤引言:信号发生器是电子实验中常用的仪器,用于产生各种类型的电信号。

本文将介绍信号发生器的实验步骤,包括设备准备、连接电路、调节参数等内容,帮助读者了解如何正确使用信号发生器进行实验。

一、设备准备1. 确保信号发生器处于关闭状态,插上电源线并连接到电源插座。

2. 检查信号发生器的各个连接端口是否干净、无杂质,并确保连接线的接头良好。

3. 确认所需的信号发生器的型号和规格,并查看相关的使用说明书,了解该型号的功能和操作方法。

二、连接电路1. 根据实验需要,选择适当的连接电路。

可以根据实验要求使用BNC连接器、万用表、示波器等设备连接信号发生器。

2. 将信号发生器的输出端口与所需的电路连接。

根据实验要求选择合适的连接线,并将其插入相应的接口。

3. 确保连接稳固可靠,避免因接触不良或松动而导致实验失败。

三、调节参数1. 打开信号发生器的电源开关,待其启动完成后,进入信号发生器的设置界面。

2. 根据实验要求选择所需的信号类型,如正弦波、方波、三角波等,并设置相应的频率、幅度等参数。

3. 根据实验要求调整信号发生器的输出电压和电流,确保其符合实验需求。

4. 可根据实验需要设置信号的偏置电压、相位差等参数。

5. 若需要连续输出信号,可设置信号发生器的连续输出功能。

四、观察实验结果1. 将实验电路连接到示波器或其他测量设备上,观察信号发生器输出信号的波形、频率、幅度等参数。

2. 根据实验需要,可以调整信号发生器的参数,比如频率、幅度等,观察信号的变化情况。

3. 使用示波器等设备对信号进行测量和分析,比如测量信号的峰值、频谱等信息。

五、实验注意事项1. 在进行实验前,要确保实验环境安全可靠,避免因电路连接错误或设备故障而导致意外事故。

2. 在调节信号发生器参数时,应注意逐步调节,避免突然改变参数值导致电路或设备的损坏。

3. 在使用示波器等设备进行测量时,要注意选择适当的量程和耦合方式,以获取准确的测量结果。

12.3 序列信号发生器的设计

——Design Sequential Circuits with MSI blocks序列信号发生器:能循环产生一组特定的串行数字序列信号的电路。

序列的长度:序列信号的位数。

如:序列为00011,则序列长度为5。

☐ 使用环形计数器设计 ☐ 使用扭环计数器设计特殊类型1000 0100 001000011101 1110 01111011常用状态图0000 1000 001100011100 111011110111常用状态图序列状态之间很有规律☐ 使用D 触发器设计☐ 使用计数器 + 数据选择器设计; ☐ 用移位寄存器 + 反馈电路设计(逻辑门 or 译码器 or 数据选择器)☐ 用计数器 + PROM 设计任意类型例:用D 触发器设计一个 110100 序列信号发生器时序电路的不同状态对应输出序列中的各位。

S 0 /Y=1 S 1 /Y=1 S 2 /Y=0 S 3 /Y=1S 4 /Y=0S 5 /Y=01. 画状态转换图大体思路:1.实现序列信号一个周期之内的波形2.将此波形循环再现☐序列信号长度为 L ,则取 L 个不同的状态☐每个状态下时序电路的输出就是序列信号中的一位。

方法1:利用D 触发器2. 状态编码S 0 —— 000 , S 3 —— 011 S 1 —— 001 , S 4 —— 100 S 2 —— 010 , S 5 —— 1013. 状态转换真值0 0 00 0 1 0 1 0 0 1 1 1 0 0 1 0 10 0 1 0 1 0 0 1 1 1 0 0 1 0 1 0 0 0Q 2Q 1Q 0 Q 2 n+1 Q 1 n+1Q 0n+1Y1 1 0 1 0 04.卡诺图化简D 0=Q 0’D 1=Q 2’Q 1’Q 0+Q 1Q 0’XX11 0 0 1 00 01 11 10 0 1Q 1Q 0 Q 2X1 0 1 0 00 01 11 10 0 1Q 1Q 0 Q 2XX10 1 0 0 00 01 11 10 0 1Q 1Q 0Q 2D 2=Q 2Q 0’+Q 1Q 0XX0 1 1 1 00 01 11 10 0 1Q 1Q 0 Q 2Y=Q 2’Q 1’+Q 1Q 05. 电路实现(略)6. 检查无关项000001010011100101110111时序电路可以自启动。

EDA实验报告实验三:序列信号发生器与检测器设计++++

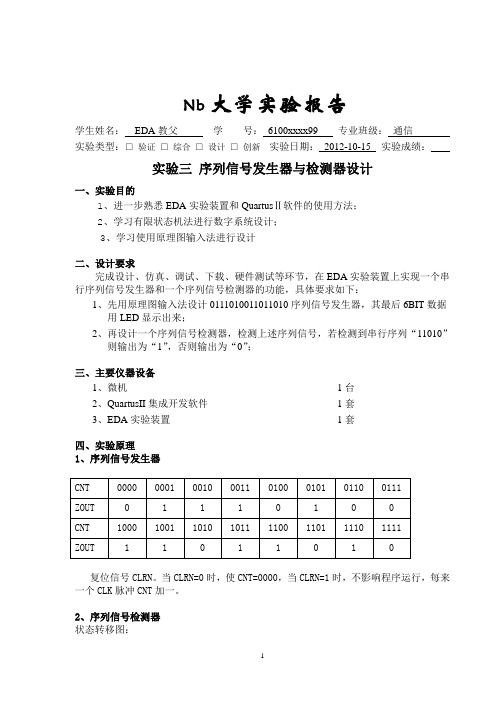

Nb大学实验报告学生姓名:EDA教父学号:6100xxxx99 专业班级:通信实验类型:□验证□综合□设计□创新实验日期:2012-10-15 实验成绩:实验三序列信号发生器与检测器设计一、实验目的1、进一步熟悉EDA实验装置和QuartusⅡ软件的使用方法;2、学习有限状态机法进行数字系统设计;3、学习使用原理图输入法进行设计二、设计要求完成设计、仿真、调试、下载、硬件测试等环节,在EDA实验装置上实现一个串行序列信号发生器和一个序列信号检测器的功能,具体要求如下:1、先用原理图输入法设计0111010011011010序列信号发生器,其最后6BIT数据用LED显示出来;2、再设计一个序列信号检测器,检测上述序列信号,若检测到串行序列“11010”则输出为“1”,否则输出为“0”;三、主要仪器设备1、微机1台2、QuartusII集成开发软件1套3、EDA实验装置1套四、实验原理1、序列信号发生器复位信号CLRN。

当CLRN=0时,使CNT=0000,当CLRN=1时,不影响程序运行,每来一个CLK脉冲CNT加一。

2、序列信号检测器状态转移图:五、实验步骤1、信号发生器1)建立工作库文件夹,输入设计项目VHDL代码,如下:L I B R A R Y I E E E;U S E I E E E.S T D_L O G I C_1164.A L L;U S E I E E E.S T D_L O G I C_A R I T H.A L L;U S E I E E E.S T D_L O G I C_U N S I G N E D.A L L;E N T I T Y X L S I G N A L16_1I SP O R T(C L K,C L R N:I N S T D_L O G I C;L E D:B U F F E R S T D_L O G I C_V E C T O R(5D O W N T O0);L E D O U T:O U T S T D_L O G I C_V E C T O R(5D O W N T O0);Z O U T:O U T S T D_L O G I C);E N D X L S I G N A L16_1;A R C H I T E C T U R E o n e O F X L S I G N A L16_1I SS I G N A L C N T:S T D_L O G I C_V E C T O R(3D O W N T O0);S I G N A L Z R E G:S T D_L O G I C;--S I G N A L C N T8:S T D_L O G I C_V E C T O R(2D O W N T O0);B E G I Np r o c e s s(c l K)b e g i nc a s e c n t i sW H E N"1000"=>L E D<="101001";W H E N"1001"=>L E D<="010011";W H E N"1010"=>L E D<="100110";W H E N"1011"=>L E D<="001101";W H E N"1100"=>L E D<="011011";W H E N"1101"=>L E D<="110110";W H E N"1110"=>L E D<="101101";W H E N"1111"=>L E D<="011010";W H E N"0000"=>L E D<="110100";W H E N"0001"=>L E D<="101001";W H E N"0010"=>L E D<="010011";W H E N"0011"=>L E D<="100111";W H E N"0100"=>L E D<="001110";W H E N"0101"=>L E D<="011101";W H E N"0110"=>L E D<="111010";W H E N"0111"=>L E D<="110100";W H E N O T H E R S=>L E D<=N U L L;E N D C A S E;E N D P R O C E S S;P R O C E S S(C L K,C L R N)B E G I NI F(C L R N='0')T H E N C N T<="0000";E L S EI F(C L K'E V E N T A N D C L K='1')T H E NC N T<=C N T+'1';E N D I F;E N D I F;E N D P R O C E S S;P R O C E S S(C N T)B E G I NW H E N"0000"=>Z R E G<='0';W H E N"0001"=>Z R E G<='1';W H E N"0010"=>Z R E G<='1';W H E N"0011"=>Z R E G<='1';W H E N"0100"=>Z R E G<='0';W H E N"0101"=>Z R E G<='1';W H E N"0110"=>Z R E G<='0';W H E N"0111"=>Z R E G<='0';W H E N"1000"=>Z R E G<='1';W H E N"1001"=>Z R E G<='1';W H E N"1010"=>Z R E G<='0';W H E N"1011"=>Z R E G<='1';W H E N"1100"=>Z R E G<='1';W H E N"1101"=>Z R E G<='0';W H E N"1110"=>Z R E G<='1';W H E N"1111"=>Z R E G<='0';W H E N O T H E R S=>Z R E G<='0';E N D C A S E;E N D P R O C E S S;Z O U T<=Z R E G;L E D O U T<=L E D;e n d o n e;2)对其进行波形仿真,如下图:2、信号检测器1)建立工作库文件夹,输入设计项目VHDL代码,如下:LIBRARY IEEE ;USE IEEE.STD_LOGIC_1164.ALL;ENTITY SCHK ISPORT(DIN, CLK, CLR : IN STD_LOGIC;ss : OUT STD_LOGIC_VECTOREND SCHK;ARCHITECTURE behav OF SCHK ISSIGNAL Q : INTEGER RANGE 0 TO 5 ;SIGNAL D : STD_LOGIC_VECTOR(5 DOWNTO 0);BEGIND <= "11010" ;PROCESS( CLK, CLR )BEGINIF CLR = '1' THEN Q <= 0 ;ELSIF CLK'EVENT AND CLK='1' THENCASE Q ISWHEN 0=> IF DIN = D(4) THEN Q <= 1 ; ELSE Q <= 0 ; END IF ;WHEN 1=> IF DIN = D(3) THEN Q <= 2 ; ELSE Q <= 0 ; END IF ;WHEN 2=> IF DIN = D(2) THEN Q <= 3 ; ELSE Q <= 2 ; END IF ;WHEN 3=> IF DIN = D(1) THEN Q <= 4 ; ELSE Q <= 0 ; END IF ;WHEN 4=> IF DIN = D(0) THEN Q <= 5 ; ELSE Q <= 2 ; END IF ;WHEN OTHERS => Q <= 0 ;END CASE ;END IF ;END PROCESS ;PROCESS( Q )BEGINIF Q = 5 THEN ss <= "1" ;ELSE ss <= "0" ;END IF ;END PROCESS ;END behav ;3)将其转换成可调用元件如图:3.序列信号检测器顶层文件1)调用序列信号发生器和序列信号检测器元件,建立工作库文件夹,输入设计项目原理图如下图:2)对总体进行波形仿真,如下图:4.管脚邦定六、实验心得只能copy到这,后面的自己写吧!DSFKLSD;GKJLSJDFG;LKSD;LG。

6位序列计数型序列信号发生器的设计过程

6位序列计数型序列信号发生器的设计过程《6位序列计数型序列信号发生器的设计过程》设计一个6位序列计数型序列信号发生器,就像是在构建一个有着独特规则的小世界。

这就好比你要搭建一个特别的乐高城堡,每一块积木都有它的作用和位置。

对于这个信号发生器,首先得有一个计数器。

这个计数器就像是城堡的基石,它决定着整个系统的节奏。

如果把整个信号发生器想象成一场音乐会,计数器就是那个打节拍的鼓手,稳定而有规律地跳动着。

计数器的位数是6位,这就像是有6个不同的鼓手,每个鼓手都负责一个独特的节奏部分。

那怎么让这个计数器工作起来呢?就需要一些逻辑电路了。

逻辑电路像是连接每个鼓手的指挥棒,告诉他们什么时候该敲,怎么敲。

比如说与门、或门、非门这些基本的逻辑门电路,它们组合起来就像一群小精灵,在背后悄悄地操控着计数器的每一步。

这些逻辑门电路就像一群厨师在厨房忙碌,不同的门电路做着不同的操作,加调料(处理信号),搅拌(组合信号)之类的。

在设计的时候,要确定序列的类型。

这有点像确定城堡的风格是欧式还是中式。

是要产生一个递增的数字序列呢,还是随机变化的序列?这决定了后续逻辑电路的搭建方式。

如果是递增序列,就像是沿着一条直路稳步向前走,每一步都清晰明了;如果是随机序列,那就像是在迷宫里穿梭,充满了不确定性。

接下来是要考虑如何把计数器的输出转化为我们想要的序列信号。

这就好比把鼓手打出的节奏转化成一段美妙的旋律。

这里可能会用到一些编码器或者解码器之类的电路元件。

编码器就像是一个翻译官,把计数器那种简单的计数语言转化成复杂的序列信号语言;解码器则相反,像是一个解读员,把复杂的序列信号还原成计数器能理解的计数形式。

在整个设计过程中,还不能忘了电源的问题。

电源就像城堡的能量源泉,没有它,整个系统就瘫痪了。

要确保电源能够稳定地为各个电路元件提供足够的电力,就像确保城堡里的每个人都能分到足够的食物一样。

测试也是非常重要的一环。

这就像是在城堡建成之后,要检查每个角落是否牢固。

序列发生器实验设计举例——实验

Qn*=Dn

现态

Q3 1 0 0 0 ┇

次态 Q3*Q2*Q1* 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 0 0 0 0 0 1 ┇

输出 Z 1 1 0 1 0 1 1 ┇

激励值 D3 D2 D1 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 0 0 0 0 0 1 ┇

Q3Q2 Q1

1

1

d d

1

D1=Q1’

Q3Q2 Q1

1

d

1

Q3Q2 Q1

d

D2=Q3’Q2’Q1+Q2Q1’

d 1 d

Q3Q2 Q1

1

D3=Q3Q1’+Q2Q1

1 1

1

d d

1

Z= Q3’Q2’+Q1

• 构成实际电路时,用与门(74LS08)和或门(74LS32) 及D触发器(74LS175)实现,具体电路如下:

序列发生器的设计

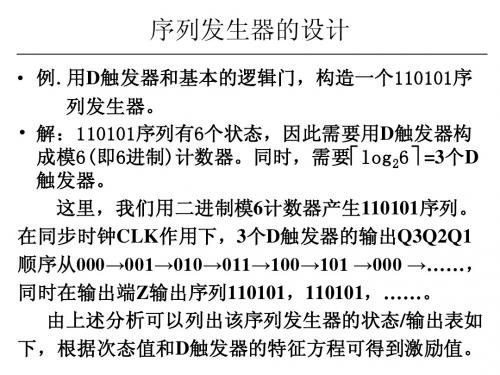

• 例.用D触发器和基本的逻辑门,构造一个110101序 列发生器。 • 解:110101序列有6个状态,因此需要用D触发器构 成模6(即6进制)计数器。同时,需要 log26 =3个D 触发器。 这里,我们用二进制模6计数器产生110101序列。 在同步时钟CLK作用下,3个D触发器的输出Q3Q2Q1 顺序从000→001→010→011→100→101 →000 →……, 同时在输出端Z输出序列110101,110101,……。 由上述分析可以列出该序列发生器的状态/输出表如 下,根据次态值和D触发器的特征方程可得到激励值。

Qn*=Dn

现态

Q3 Q2 Q1 0 0 0 0 0 1 0 1 1 0 1 0 1 1 0 1 0 0 0 0 0 ┇