uvm实战-学习笔记

uvm_hdl_force用法

uvm_hdl_force用法UVM(Universal Verification Methodology)是一种基于SystemVerilog的验证方法学,用于验证硬件设计的正确性。

UVM提供了一系列的类和方法,其中一个重要的方法是`uvm_hdl_force`。

在这篇文章中,我们将详细讨论`uvm_hdl_force`的用法。

`uvm_hdl_force`是一个UVM的方法之一,用于在仿真运行时操纵信号值。

通过使用`uvm_hdl_force`,我们可以强制将一个信号的值设置为指定的值,从而模拟特定的测试用例场景。

下面是`uvm_hdl_force`的定义:```systemverilogfunction void uvm_hdl_force (ref bit hdl, bit force, bit value);````uvm_hdl_force`接受三个参数:- `hdl`:被强制操纵的信号的句柄;- `force`:一个`bit`值,表示是否对信号进行强制操纵;- `value`:一个`bit`值,指定被强制操纵的信号值。

`hdl`参数是一个引用,因此无需在使用`uvm_hdl_force`之前显示地声明信号。

它可以是从UVM测试环境中的任何一个组件内部访问的信号。

通过使用`ref`关键字,我们可以将信号的引用传递给`uvm_hdl_force`。

下面是一个使用`uvm_hdl_force`的示例代码:```systemverilogmodule dut (input logic clk, input logic reset, output logic data_out);//...endmoduleclass my_test extends uvm_test;//...function void run_phase(uvm_phase phase);forkbegin// Force the reset signal// Wait for 10 clock cycles;// Release the reset signal// Wait for 20 clock cycles;// Force some data values;endjoinendfunctionendclassmodule testbench;//...my_test test;//...end//...endmodule```在上面的例子中,我们假设存在一个DUT(Design Under Test)模块,其中有一个时钟信号`clk`,一个复位信号`reset`和一个数据输出信号`data_out`。

异步fifo的uvm验证原理

异步fifo的uvm验证原理异步FIFO(First-In-First-Out,先进先出)是一种常用的数据缓冲区结构,常用于解决不同速率的数据传输问题。

UVM (Universal Verification Methodology,通用验证方法学)是一种系统级验证方法学,用于验证硬件设计。

在UVM中,对异步FIFO的验证需要对FIFO的功能和时序进行验证。

以下是异步FIFO的UVM验证原理:1. 创建FIFO模型:首先,需要创建一个FIFO模型,包括FIFO的输入端口和输出端口,以及FIFO的内部数据存储器。

可以使用SystemVerilog语言创建FIFO模型。

2. 编写验证环境:在UVM中,需要编写一个验证环境(testbench),用于生成测试用例,驱动输入数据到FIFO中,并验证FIFO的输出数据是否符合预期。

验证环境包括以下组件:- 驱动(driver):负责将测试向量输入到FIFO中。

- 监视器(monitor):监控FIFO的输出数据,并将其与预期结果进行比较。

- 预测器(predictor):根据输入数据预测FIFO的输出结果。

- 生成器(generator):生成各种测试用例。

3. 设置时序约束:对于异步FIFO的验证,需要设置时序约束,以确保FIFO的输入和输出数据能够按照预期的时序要求进行传输。

时序约束包括FIFO的读写时钟频率和时钟间隔等参数。

4. 进行功能验证:验证FIFO的功能,包括数据的读写操作是否正确,数据的顺序是否符合FIFO原则等。

可以通过在测试用例中使用不同的输入数据和读写操作顺序来验证FIFO的功能。

5. 进行时序验证:验证FIFO的时序,包括输入数据的时序要求是否满足,输出数据的时序是否符合预期。

可以通过在测试用例中使用不同的时序生成输入数据来验证FIFO的时序。

6. 进行性能验证:验证FIFO的性能,包括写入速率和读出速率是否满足要求,以及FIFO的深度是否足够。

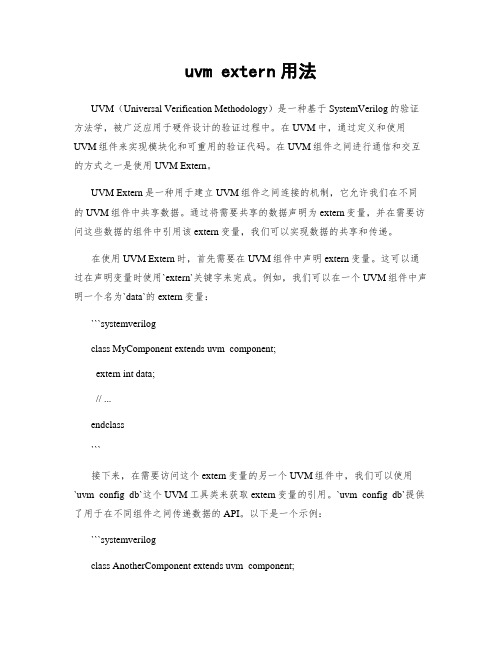

uvm extern用法

uvm extern用法UVM(Universal Verification Methodology)是一种基于SystemVerilog的验证方法学,被广泛应用于硬件设计的验证过程中。

在UVM中,通过定义和使用UVM组件来实现模块化和可重用的验证代码。

在UVM组件之间进行通信和交互的方式之一是使用UVM Extern。

UVM Extern是一种用于建立UVM组件之间连接的机制,它允许我们在不同的UVM组件中共享数据。

通过将需要共享的数据声明为extern变量,并在需要访问这些数据的组件中引用该extern变量,我们可以实现数据的共享和传递。

在使用UVM Extern时,首先需要在UVM组件中声明extern变量。

这可以通过在声明变量时使用`extern`关键字来完成。

例如,我们可以在一个UVM组件中声明一个名为`data`的extern变量:```systemverilogclass MyComponent extends uvm_component;extern int data;// ...endclass```接下来,在需要访问这个extern变量的另一个UVM组件中,我们可以使用`uvm_config_db`这个UVM工具类来获取extern变量的引用。

`uvm_config_db`提供了用于在不同组件之间传递数据的API。

以下是一个示例:```systemverilogclass AnotherComponent extends uvm_component;int data;// ...function void build_phase(uvm_phase phase);super.build_phase(phase);if (!uvm_config_db#(int)::get(this, "", "data", data))`uvm_fatal("DATA_NOT_FOUND", "Failed to get the data usinguvm_config_db")endfunction// ...endclass```在上述代码中,`uvm_config_db#(int)::get`函数用于从之前声明的extern变量中获取data的值,并将其存储在AnotherComponent的data变量中。

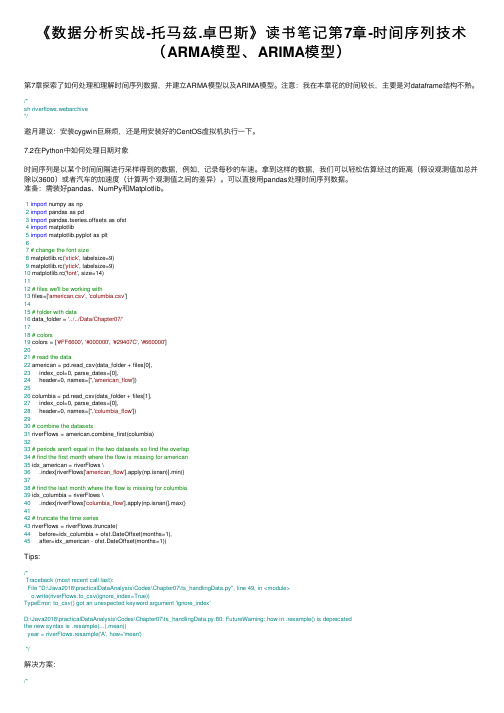

《数据分析实战-托马兹.卓巴斯》读书笔记第7章-时间序列技术(ARMA模型、ARIMA模型)

《数据分析实战-托马兹.卓巴斯》读书笔记第7章-时间序列技术(ARMA模型、ARIMA模型)第7章探索了如何处理和理解时间序列数据,并建⽴ARMA模型以及ARIMA模型。

注意:我在本章花的时间较长,主要是对dataframe结构不熟。

/*sh riverflows.webarchive*/邀⽉建议:安装cygwin巨⿇烦,还是⽤安装好的CentOS虚拟机执⾏⼀下。

7.2在Python中如何处理⽇期对象时间序列是以某个时间间隔进⾏采样得到的数据,例如,记录每秒的车速。

拿到这样的数据,我们可以轻松估算经过的距离(假设观测值加总并除以3600)或者汽车的加速度(计算两个观测值之间的差异)。

可以直接⽤pandas处理时间序列数据。

准备:需装好pandas、NumPy和Matplotlib。

1import numpy as np2import pandas as pd3import pandas.tseries.offsets as ofst4import matplotlib5import matplotlib.pyplot as plt67# change the font size8 matplotlib.rc('xtick', labelsize=9)9 matplotlib.rc('ytick', labelsize=9)10 matplotlib.rc('font', size=14)1112# files we'll be working with13 files=['american.csv', 'columbia.csv']1415# folder with data16 data_folder = '../../Data/Chapter07/'1718# colors19 colors = ['#FF6600', '#000000', '#29407C', '#660000']2021# read the data22 american = pd.read_csv(data_folder + files[0],23 index_col=0, parse_dates=[0],24 header=0, names=['','american_flow'])2526 columbia = pd.read_csv(data_folder + files[1],27 index_col=0, parse_dates=[0],28 header=0, names=['','columbia_flow'])2930# combine the datasets31 riverFlows = bine_first(columbia)3233# periods aren't equal in the two datasets so find the overlap34# find the first month where the flow is missing for american35 idx_american = riverFlows \36 .index[riverFlows['american_flow'].apply(np.isnan)].min()3738# find the last month where the flow is missing for columbia39 idx_columbia = riverFlows \40 .index[riverFlows['columbia_flow'].apply(np.isnan)].max()4142# truncate the time series43 riverFlows = riverFlows.truncate(44 before=idx_columbia + ofst.DateOffset(months=1),45 after=idx_american - ofst.DateOffset(months=1))Tips:/*Traceback (most recent call last):File "D:\Java2018\practicalDataAnalysis\Codes\Chapter07\ts_handlingData.py", line 49, in <module>o.write(riverFlows.to_csv(ignore_index=True))TypeError: to_csv() got an unexpected keyword argument 'ignore_index'D:\Java2018\practicalDataAnalysis\Codes\Chapter07\ts_handlingData.py:80: FutureWarning: how in .resample() is deprecatedthe new syntax is .resample(...).mean()year = riverFlows.resample('A', how='mean')*/解决⽅案:/*# year = riverFlows.resample('A', how='mean')year = riverFlows.resample('A').mean()# o.write(riverFlows.to_csv(ignore_index=True))o.write(riverFlows.to_csv(index=True))*/原理:⾸先,我们引⼊所有必需的模块:pandas和NumPy。

uvm中copy函数和print

uvm中copy函数和printCopy函数和Print函数是UVM中两个常用的函数,它们在测试环境设计和调试过程中起着重要的作用。

本文将分别介绍这两个函数的使用方法和注意事项。

一、Copy函数Copy函数是UVM中用于复制对象的函数,通过该函数可以创建一个与原对象具有相同属性和行为的新对象。

Copy函数的使用非常灵活,可以用于复制各种类型的对象,包括UVM组件、配置对象、序列、事务等。

Copy函数的基本语法如下:```systemverilogfunction new_object = original_object.clone();```其中,original_object为原对象,new_object为复制后的新对象。

在使用Copy函数时,需要注意以下几点:1. Copy函数只能用于可复制的对象,即该对象的类必须实现了UVM 的clone方法。

2. 复制后的新对象与原对象之间是相互独立的,它们之间的修改互不影响。

3. Copy函数只会复制对象的属性和行为,不会复制对象的状态。

如果需要复制对象的状态,可以使用UVM的重载函数clone_with方法。

4. 复制后的新对象与原对象的类型相同,但它们是两个独立的对象,可以在不同的环境或测试用例中使用。

二、Print函数Print函数是UVM中用于打印信息的函数,通过该函数可以在运行过程中输出调试信息、日志等。

Print函数可以输出各种类型的信息,包括字符串、整数、浮点数、数组等。

Print函数的基本语法如下:```systemverilog`uvm_info("TAG", "Message", UVM_MEDIUM);```其中,TAG为打印信息的标签,Message为要输出的信息,UVM_MEDIUM为信息的级别。

在使用Print函数时,需要注意以下几点:1. 打印信息的标签可以自定义,一般用于区分不同模块或功能的信息。

(转)UVM验证方法学之一验证平台

(转)UVM验证⽅法学之⼀验证平台在现代IC设计流程中,当设计⼈员根据设计规格说明书完成RTL代码之后,验证⼈员开始验证这些代码(通常称其为DUT,Design Under Test)。

验证⼯作主要保证从设计规格说明书到RTL转变的正确性,它包括但不限于以下⼏点:DUT的⾏为表现是否与设计规格说明书中的要求⼀致DUT是否实现了设计规格说明书中的所有功能DUT对于异常状况的反应是否与设计规格说明书中的⼀致DUT是否⾜够稳健,能够从异常状态恢复到正常的⼯作模式图1 验证发现DUT中的bug随着芯⽚规模的增⼤,验证占整个芯⽚设计流程的⽐例越来越⼤,验证的⼯作量已经占到整个SoC研发周期的70%到80%。

因此,提⾼芯⽚验证的效率已变得⾄关重要。

快速搭建⼀个强⼤、⾼效、灵活、可扩展性好的验证平台是芯⽚成功的关键。

1 UVM代表了验证⽅法学的发展⽅向验证是服务于设计的,⽬前来说,主流的设计语⾔有两种:Verilog和VHDL。

伴随着IC的发展,涌现出了多种验证语⾔,如Vera、e、SystemC、SystemVerilog等。

其中,SystemVerilog刚⼀推出就受到了热烈欢迎,SystemVerilog是⼀个Verilog的扩展集,它既完全兼容Verilog,⼜具有所有⾯向对象语⾔的特性:封装、继承和多态,同时,还为验证提供了⼀些独有的特性,如产⽣带约束(constraint)的随机激励。

在基于SystemVerilog的验证⽅法学中,主要有以下三种:VMM(Verification Methodology Manual),这是Synopsys在2006年推出的; VMM中集成了寄存器解决⽅案RAL(Register Abstraction Layer)。

当OVM出现后,⾯对OVM的激烈竞争,VMM已经开源OVM(Open Verification Methodology),由Cadence和Mentor于2008年推出;从⼀开始就是开源的。

uvm callback机制

uvm callback机制UVM是一种基于SystemVerilog的验证方法学,它提供了一种面向对象的方式来组织测试环境和测试用例,使得验证工程师可以更加高效地编写测试代码。

其中,UVM Callback机制是UVM中非常重要的一部分,它可以帮助我们在不改变被测设计的情况下,对其进行各种各样的功能扩展和验证。

什么是UVM Callback机制?UVM Callback机制是指在UVM中,我们可以通过注册回调函数的方式,将一些函数与UVM中的特定事件相关联。

当这些事件发生时,UVM会自动调用相应的回调函数,以执行我们所需的操作。

这种机制可以帮助我们在测试过程中,自动化地完成一些任务,优化测试流程,提高测试效率。

UVM Callback机制的应用场景UVM Callback机制可以应用于各种不同的场景,下面列举几个常见的应用场景:1. 监控信号在UVM中,我们可以通过注册回调函数的方式,监控特定的信号。

当这些信号发生变化时,回调函数会被自动调用,以执行我们所需的操作。

例如,我们可以注册回调函数来检测数据传输的开始和结束,以便我们可以在测试过程中对数据进行分析和处理。

2. 覆盖率统计在UVM中,我们可以使用回调函数来统计测试覆盖率。

当测试环境中的某个信号或寄存器被访问时,回调函数会被调用,以记录测试的覆盖情况。

这种方法可以帮助我们更好地了解测试的进展情况,以及测试的有效性。

3. 动态生成测试用例在UVM中,我们可以使用回调函数来动态生成测试用例。

当某个事件发生时,回调函数会被调用,以生成一个新的测试用例。

这种方法可以帮助我们更好地覆盖设计的各个方面,以及更好地发现设计中的潜在问题。

4. 预处理测试数据在UVM中,我们可以使用回调函数来预处理测试数据。

当测试数据被加载到测试环境中时,回调函数会被调用,以对数据进行处理和转换。

这种方法可以帮助我们更好地准备测试数据,以及更好地与被测设计进行交互。

UVM Callback机制的实现方法在UVM中,我们可以使用uvm_callback类来实现回调机制。

uvm_hdl_force用法

uvm_hdl_force用法UVM(Universal Verification Methodology)是一种硬件验证方法学,它提供了一种系统级、可重用、多层次和多接口的验证器件设计以及验证的标准框架。

UVM作为一个开放的验证方法学,提供了一套验证类库,用于创建可重用的验证环境和测试套件。

在UVM中,UVM HDL(Hardware Description Language)力量是一种调试和验证技术,它允许用户在仿真期间强制修改设计中的信号值。

在这种情况下,UVM HDL力量允许用户在测试过程中设置、清除或变更信号属性,以便观察特定情况下的设计行为。

UVM HDL力量的主要目的是优化验证环境,便于调试和检测设计中的潜在问题。

UVM HDL力量可以通过uvm_hdl_force函数来实现。

该函数是UVM中提供的一个任务,用于在任何模拟时间点上强制改变设计中的信号值。

```verilogfunction void uvm_hdl_force(input int unsigned ref, i);```其中,ref参数指定信号的句柄(handle),i参数指定要强制设置的值。

使用uvm_hdl_force函数时,通常将其包装在自定义的任务或函数中。

这样可以更好地组织测试用例和测试环境,并提高代码的可重用性。

下面是一个示例,展示了如何使用uvm_hdl_force函数将信号设置为特定的值:```verilogtask force_signal;beginforkautomatic int ref;ref = $sformatf("top.dut.my_signal");// Force signal value to 1// Continue with other tasks//...join_noneendendtask```在上面的示例中,首先使用$sformatf函数来构建信号的句柄(handle),指定要强制修改的信号为“top.dut.my_signal”。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

《UVM实战(卷1)》学习笔记看了第1/2/3/4/5/6/8/9.1这几个章节。

第一章是综述,第二章是一个具体的例子,学习笔记从第三章相关内容开始。

我个人觉得UVM重要的部分(特点的部分):1)factory机制(overrideconfig_db)2)TLM传递3)phase机制4)sequence-sequencer以及virtualseq/sqr内容中的截图基本来自于UVM源代码、书自带的例子和《uvm1.1应用指南及源代码分析》这个PDF里的。

需要结合书(第3也uvm_void常用的是item,当发现有常用的transaction-level向signal-level的转换。

uvm_driver需要参数(REQRSP),比uvm_component增加了几个成员。

重要的是seq_item_port和req/rsp.(src/comps/uvm_driver.svh)monitor/scoreboard派生自uvm_monitor和uvm_scoreboard,但是uvm_monitor和uvm_scoreboard并没有在uvm_component基础上做扩展。

src/comps/uvm_monitor.svh因为driver和envmacro1)对于2)对于对于`uvm_component_utils(类名)uvm_component里的成员也可以像uvm_object里成员一样,用field_automation机制。

field_automation机制:对于uvm_object派生类来说,field_automation机制让对象自动有的copycompareprintpackunpack等函数,简化了实现uvm_component派生类里一些function/task的工作量对于uvm_component派生类来说,field_automation机制最重要的是可以在build_phase中自动获取uvm_config_db#()::set()的数值(必须加super.build_phase(phase))----也就是不用写uvm_config_db#()::get()注意:field_automation的macro的类型要和uvm_config_db的参数类型一致:如下示例代码,field_intvsuvm_config_db#(bit[47:0])这个时候super.build_phase()是不起作用的。

想要起作用的话,需要用clone=new+copy 源代码中可以看到clone 函数一上来会做一次create ,然后调copy 函数src/base/uvm_object.svh3.2UVM 的树形结构uvm_component 的new/create 要注意第一个参数是名字,第二个参数是parent 指针。

UVM 真正的树根是“uvm_top ”.根据上面这个树结构,可以看出一个个component 的parent 是什么。

uvm_top 的parent 是null 。

当一个component 在实例化的时候,如果parent 参数设成null ,那么parent 参数会被仿真器自动设置成uvm_root 的实例uvm_top.在6.6.1章节里也提到了,sequence 在uvm_config_db#()::get ()的时候,第一个参数设成“null ”,实际就是 0/1两种情况1有217bit 中bit0✍✍packbit9UVM_ALL_ON 是‘UVM_ALL_ON|UVM_NO_PACK 这样就会忽略掉packbit这个ps 的更合理一些。

然后crc_error 是3.4UVM打印信息控制get_report_verbosity_level()set_report_verbosity_level(UVM_HIGH)只对当前调用的component起作用set_report_verbosity_level_hier(UVM_HIGH)对当前及下面所有的component起作用simv+UVM_VERBOSITY=UVM_HIGH命令行方式------我觉得用这个就可以了重载打印信息:set_report_severity_override(UVM_WARNING,UVM_ERROR);上述函数都是在connect_phase及后面的phase使用设置UVM_ERROR到达一定数量结束仿真设置在都是4set的1)2)3)调用setconfig_db(6.6.1章节)。

使用如下函数调试config_dbcheck_config_usage()print_config(1/0)这两个函数在connect_phase函数中调simv+UVM_CONFIG_DB_TRACE注意:第二个参数设置错误不会报错!!-------config_db机制务必要注意参数的书写。

第4章UVM中的TLM1.0通信TLM是TransactionLevelModeling缩写这章要搞清楚portexportimpfifo以及几种操作function/task和对应component中要实现的function/task下面的箭头方向都是控制流的方向,不是数据流方向。

我觉得作为一个VMM用户会觉得TLM有点难理解,总想用VMM_CHANNEL去套,结果把自己搞晕。

像port等其实是调imp所在component的task/function.我看UVM源代码里有一个uvm_seq_item_pull_port的class,它的基类是uvm_port_base.在uvm_driver的成员seq_item_port就是这个类型的。

与它对应的是uvm_seq_item_pull_imp,uvm_sequencer的成员seq_item_export 就是这种类型。

在my_agent.sv中会connect它们。

4.2端口互连port是动作的发起者,export是动作接收者,但是需要以一个imp来结束。

;而完以后,之分)。

transport 连接用connect函数实现,从名字就可以看出来,这个必须在connect_phase中调。

4.3通信方式这节应该是本章重点。

实际使用中用analysis_port✍analysis_imp还是port✍tlm_analysis_fifo✍port可以根据实际情况自己决定。

analysis_port(analysis_export)可以连接多个imp(一对多的通信)✍✍put和get系列端口与相应imp的通信通常是一对一的(可以一对多,但是本书没有给出一对多的例子4.2.1章节有介绍)。

analysis_port(analysis_export)更像是一个广播analysis_port(analysis_export)没有阻塞和非阻塞的概念。

它是一个广播,不等与它相连的其他端口的响应。

analysis_port(analysis_export)必须连的imp是analysis_imp.analysis_imp所在的component必须定义个write 的function---------注意:是function代码示例:4.3.1示例代码的analysis_port文件夹componentC和B的代码基本一致。

env的connect_phase函数里做connect:component中有多个imp的时候,如何实现write函数?4.3.2给的例子中,scoreboard有两个imp,分别从output_agent和reference-model的analysis_port获取transaction,然后做compare.这个时候需要用:`uvm_analysis_imp_decl(_标记)这个macro,然后“write”函数变成“write_标记()”函数,analysis_port所在component不用变,还是调write()函数即可。

代码示例如下:使用macro声明来实现port中直接的时候用for循环。

第5章UVM验证平台的运行5.1phase机制所有的phase如下图:中间绿色的是taskphase,两头青色的是functionphasecomponent的实例化是在build_phase中完成,object的实例化可以在任何phase完成。

functionphase中除了build_phase都是“自下而上”的执行----这里的上下是指的树结构中的上下。

-------build_phase 是“自上而下”同层次的兄弟关系的component,buildphase执行顺序是根据new时候name的字典序–5.1.3章节对于叔侄关系的component,buildphase执行顺序是深度优先。

例如前面UVM树中,“scb”和“i_agt.drv”,因为i_agt在scb前面,会执行完i_agt,然后drv\mon\sqr,然后o_agt,然后mon,然后才是scb。

所有component的同一个runtimephase是同时开始的。

-----也就是说会等其他component的上一个phase结束才开始当前phase。

super.build_phase(phase)一定要加,其他phase的super….可以不用加.phase之间可以跳转。

例如在正常工作的时候,发生了的reset,那么应该是main_phase跳转到reset_phase.例如:5.1.7章节的示例代码jump导致1)在2)3)控制推荐在5.2.2注意用给在test的objection5.3第6sequencer1)2)需要3)4)启动sequence(一般在case的build_phase中)上述变化反映到代码中,如图6.1.2章节的示例代码下图中有两种方法实现my_sequencersequence的启动方式(3种):1)在case的main_phase中:注意要设置cseq的staring_phase。

我觉得书上6-5代码清单里有两个地方写的不合理,一个是start的参数应该是sqr的路径,另外是少了设置starting_phase2)注意在case的build_phase中3)更推荐用下面这种方式:sequence被启动后,会自动执行sequence的bodytask(以及pre_bodymid_bodypost_body)在同一个sequencer上可以启动多个sequence,因为启动了多个,所以不能设置default_sequnce了,需要用上面第一种方法来启动sequence.---------但是sequence的嵌套可以解决这个问题(上层sequence做default_sequence6.4章节)sequence可以用uvm_do_priuvm_do_pri_with等macro来设置优先级priority,当一个sequencer上有多个sequence 的时候,这个优先级就有意义了。