美信DIY设计大赛,Xilinx 28nm开发板等你试用!

Silicon Labs 无线连接技术讨论系列 - 夏季系列说明书

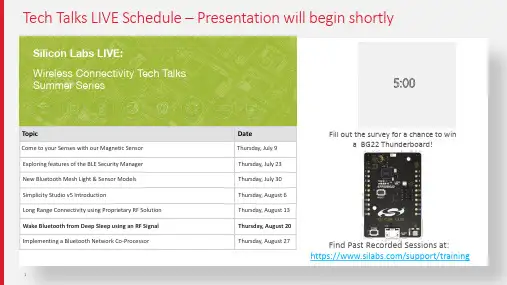

Tech Talks LIVE Schedule –Presentation will begin shortlyFind Past Recorded Sessions at: https:///support/trainingFill out the survey for a chance to wina BG22Thunderboard!TopicDateCome to your Senses with our Magnetic Sensor Thursday, July 9Exploring features of the BLE Security Manager Thursday, July 23New Bluetooth Mesh Light & Sensor Models Thursday, July 30Simplicity Studio v5 IntroductionThursday, August 6Long Range Connectivity using Proprietary RF Solution Thursday, August 13Wake Bluetooth from Deep Sleep using an RF Signal Thursday, August 20Implementing a Bluetooth Network Co-ProcessorThursday, August 27Silicon Labs LIVE:Wireless Connectivity Tech Talks Summer SeriesWELCOMESilicon Labs LIVE:Wireless Connectivity Tech TalksSummer SeriesWake Bluetooth from Deep Sleep using an RF Signal August 20th, 2020David SeymourRF (Radio Frequency). What is it?§Radio frequency is the oscillation rate of an alternating electric current or voltage or of a magnetic, electric or electromagnetic field or mechanical system in the frequency range from around 20 kHz to around 300 GHz.Wikipediahttps:///wiki/Radio_wave2.4GHz Protocol Field DayRF Transfer of PowerModulation. What is it?Frequency modulation (FM) is the encoding of information in a carrier-wave by varying the instantaneous frequency of the wave.Amplitude modulation (AM ) the amplitude (signal strength) of the carrier wave is varied in proportion to that of the message signal being transmitted.By Berserkerus -Own work, CC BY-SA 2.5xG22 Block DiagramPeripheral Reflex SystemEnergy Management VoltageRegulatorBrown-outDetectorDC-DCConverterPower-on ResetVoltageScalingCPU and Memory ARM Cortex-M33with DSP, FPU &TrustZone512 kB FlashDebug Interface 32kB RAM LDMAControllerEM4ShutoffEM1SleepEM0RunEM2Deep SleepEM3StopFeatureavailabledown toEnergy ModeSerial Interfaces 2x USART2x I2C1x EUSART2-ch 16-bitPDMTimers and Triggers5x Timer/CounterLow EnergyTimerRTC WatchdogBackup RTCI/O PortsExternalInterruptUp to 26GPIOPin Reset GPIOWakeup32-bit BusRadioProp. 2.4 GHz RadioCortex-M0+Integrated0/6 dBm PARadio CryptoRFSenseSecurityAES-128/256,SHA-1/2ECCSecure Boot RTSLSecure DebugTRNGClock ManagementHigh FreqCrystal OscHigh FreqRC OscFast StartupRC OscUL Freq RCOscLow FreqCrystal OscPrecision LFRC OscAnalog Modules12-bit,1Msps ADCTemp.SensormAuAnACurrentRF Sense (classic) Series 0 & 1 devicesSelective RF Sense (Series 2 xG22) device Wake-upRF Sense AnalogySleeping at very low power+=Async Noise Awake and using energy+=Sleeping at very low powerAsync NoiseOrOOK with Wrong Sync WordStill sleeping like baby at very low powerSleeping at very low power+=OOK with Correct Sync Word Awake and using energyReference Manual ReviewOOK (On/Off Keying) Modulation1kHz signalManchester-codedPreamble 10101010DataDEDataCADataFBDataADData is 1 byte with option for being 2/3 or 4 bytesThe “data” is your custom sync word (secret key)Preamble is 8-bitsData Sheet ReviewExtending Battery Life in Bluetooth ApplicationsLocation ServicesData TransferConnected to a phone at 2000ms intervalAdvertising 10 bytes every 2000msUsing 2M PHY and transmitting 10 Byte / packet TX at 0dBm and 3 using channelsAverage current: 4.2μAAverage current: 4.7μA5+ years on CR203210+ years on a CR2354S e l ec t i v e R F S e n s e w i l l e x t e nd b a t te r y l if e t i m eRF Transfer of Powerhttps:///wiki/Radio_waveRF Sense (Classic) Mode §In Legacy (Energy Detection) mode, EFR32xG22 RF Sense is fully compatible with the feature in Series 1 devices§The EFR32 has the ability to sense the presence of RF Energy above -20 dBm within 2.4 GHz band§This triggers an event if that energy is continuously present for certain durations of time §The EFR series of energy-friendly radios have the ability to wake themselves upon detecting of RF signal.POR orwakeup5 seconds advertisingEM4 SleepWSTK+BG22 Radio BoardSelective RF Sense Mode –Series 2 EFR32xG22Receive Side: Selective RF Sense mode mitigates the unfiltered nature of RF Sense. Instead of simply detecting energy for a given time period, it detects "a pattern of energy" -which is essentially an On-Off Keying (OOK) packet. The packet is Manchester-coded and uses a fixed 1 kbps bitrate, 1 Byte preamble, and 1-4 Byte sync word.Transmit Side: This packet can be transmitted by any OOK-capable device, including all EFR32 wireless MCUs (Series 1 and Series 2). EFR32 radios transmit this packet on 2.4 GHz.POR or wakeup5 seconds advertisingEM4 Sleep5 seconds advertisingWakeupOOK PacketEnter Select ModeTXRXRF Sense Selective Mode Test SetupTXRXThunderboard Sense 2OrThunderboard BG22WSTK +BG22 Radio BoardBG22: Optimized for Battery Powered Bluetooth LESecure Bluetooth 5.2 SoCs forHigh-Volume ProductsRadioBluetooth 5.2+6 dBm TX*-99 dBm RXAoA & AoDUltra-Low Power3.6mA Radio TX2.6mA Radio RX1.4uA EM2 with 32kB RAM 0.54uA in EM4RTC in EM4World Class Software Bluetooth 5.2 Bluetooth mesh LPN Direction Finding Compact Size5x5 QFN40 (26 GPIO)4x4 QFN32 (18 GPIO)4x4 TQFN32 (18 GPIO)ARM Cortex-M33with TrustZone 76.8 MHzFPU and DSP352/512kB of flash32kB RAMPeripherals Fit for Purpose2x USART, 2x I2C, 2x PDM and GPIO12-bit ADC (16 channels)RFSENSE wake-on radioBuilt-in temperature sensor with +/-1.5 o C 32kHz, 500ppm PLFRCOSecurityAES128/256,SHA-1, SHA-2 (256-bit) ECC (up to 256-bit), ECDSA and ECDH True Random Number Generator (TRNG) Secure boot with RTSLSecure debug with lock/unlockRAIL API Supported FeaturesData pathManagement pathMemory Manager Abstraction•Allocate/Free Memory CBs •Begin/End Write Memory eventsRadio Configuration •Radio Init •Set Protocol•Set Automatic TX/RX Transitions•Packet/Frame configuration •Channel configuration •Bit Rate configuration •Symbol Rate configuration •PA tune configuration •RF Sense configuration •Load custom configuration •RF Idle/Extended Idle •Get Radio Entropy •Get VersionRadio Timings•Set/Get time base•Start/Stop timerTX•Configuration •Data Load •Start TX•Set TX Power •Get TX Status •TX eventsRX•Configuration •Start/Schedule RX •Get RSSI•Start/Poll/Get Average RSSI •RX eventsAuto ACK•Configuration •Enable/Disable•Pause/Resume/Cancel •Load/Use ACK Buffer •StatusRadio Calibration•Calibration Init •Calibration Start •Calibration Status •Calibration eventsRadio Diagnostic •BER Start/Stop/GetStatus •Direct Mode Configuration •Set/Get Tune •Start/Stop Stream •Start/Stop TX TonePre-TX•Schedule TX •CCA-CSMA •CCA-LBT•Set CCA thresholdAddress Filtering•Configuration•Enable/Disable/Reset Filter •Enable/Disable Address •Set Filter Address •IsEnabledBLE Specific•Init/De-init BLE•Set PHY Modes (1Mbps, 2Mbps, w/ Viterbi)•Set channel RF parameters802.15.4 Specific•Init/De-init 802.15.4•Set Short/Long Address •Set PanId/Coordinator •Set Promiscuous Mode •Data request callbackEFR32 HAL (interrupt handlers)FIFO Management •Data Configuration •Reset FIFO•Enable/Disable RX FIFO •Set/Get RX/TX FIFO Thresholds •Write TX FIFO •Read RX FIFO •FIFO eventsht t p s ://d o c s .s il a b s .c o m /r a i l /l a t e s t /g r o u p -r f -s e n s ehttps:///rail/latest/group-rf-senseFunctions§Accurate & dynamic pricing matching§Interactive product guides & promotions§Centralized pricing & inventory management§Energy efficiency with FG22§Extend battery life with 0.5µA in EM4 mode§RFSENSE with selective OOK preventing false wake-up events§Best-in-class embedded security§Arm® TrustZone®§Secure boot§Secure debug with lock/unlock§Hardware Cryptographic Acceleration§True Random Number Generator compliant withNIST/AIS§Single chip implementation reduce attack vectorsand simplifies design§Enables autonomous RF system wake-up§Works in all energy modes down to EM4§Continuously monitors the spectrum for RF signals §Enables radio transceiver only when required§Operational modes§Standard: Wakeup on detection of 2.4 GHz RF energy §Selective: Wakeup based on Synch-word§Customer-configurable On-Off Keying packet§Prevents false detections from interferers§Allows Selective wake-up of certain devices§Two configurable detection thresholds§Wake-up triggered above -19 dBm or -28 dBm§Wake-up not triggered below -26 dBm or -40 dBmUse-case 2: Asset Tracking On-Demand10 feet10 feet1,000’s of Tag’s present§Waking a product to access wirelessly using SmartDevice§OOK Selective RF Sense with unique key word adds security to who can wake up the product§Adding application level Public/Private key as next level of security and authentication §Use SmartDevice to control, monitor, update, configure, active, and moreUse-case 3: Equipment AccessReferences§KBA RFSense§RFSense Selective on §https:///bluetooth/latest/code-examples/stack-features/system-and-performance/waking-from-deep-sleep-using-rf-sense§https:///documents/public/application-notes/an1244-migration-efr32-families.pdf §Describes an enhancement to RF Sense now available on the EFR32xG22§https:///documents/public/user-guides/ug409-railtest-users-guide.pdfDemonstration Time –4:13§Silicon Labs Dane Taylor -Channel Product Marketing Manager§Quick video to demo RF Sense (classic) and Selective RF Sense (new)The Largest Smart Home Developer EventS E P T E M B E R9 –1 0, 2 0 2 0Immerse yourself in two days of technical training designedespecially for engineers, developers and product managers.Learn how to"Work With" ecosystems including Amazon and Google and join hands-on classes on how tobuild door locks, sensors, LED bulbs and more.Don't miss out, register today!w o r k s w i t h.s i l a b s.c o m 31Thank you…..Questions?。

EDA技术实验讲义

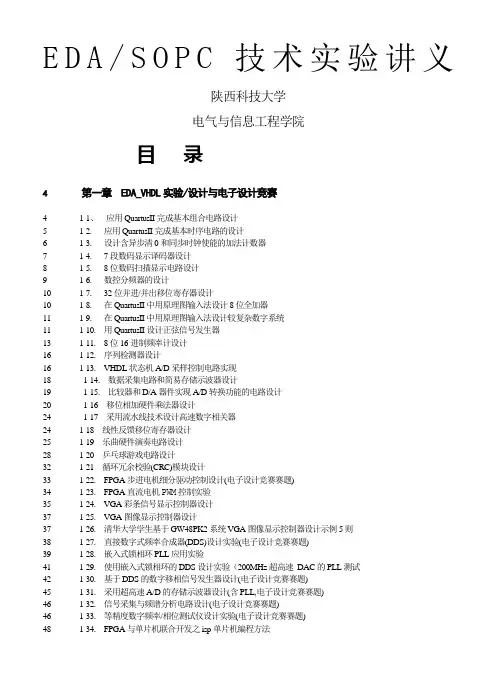

E D A/S O P C技术实验讲义陕西科技大学电气与信息工程学院目录4第一章 EDA_VHDL实验/设计与电子设计竞赛4 1-1、应用QuartusII完成基本组合电路设计5 1-2. 应用QuartusII完成基本时序电路的设计6 1-3. 设计含异步清0和同步时钟使能的加法计数器7 1-4. 7段数码显示译码器设计8 1-5. 8位数码扫描显示电路设计9 1-6. 数控分频器的设计10 1-7. 32位并进/并出移位寄存器设计10 1-8. 在QuartusII中用原理图输入法设计8位全加器11 1-9. 在QuartusII中用原理图输入法设计较复杂数字系统11 1-10. 用QuartusII设计正弦信号发生器13 1-11. 8位16进制频率计设计16 1-12. 序列检测器设计16 1-13. VHDL状态机A/D采样控制电路实现18 1-14. 数据采集电路和简易存储示波器设计19 1-15. 比较器和D/A器件实现A/D转换功能的电路设计20 1-16 移位相加硬件乘法器设计24 1-17 采用流水线技术设计高速数字相关器24 1-18 线性反馈移位寄存器设计25 1-19 乐曲硬件演奏电路设计28 1-20 乒乓球游戏电路设计32 1-21 循环冗余校验(CRC)模块设计33 1-22. FPGA步进电机细分驱动控制设计(电子设计竞赛赛题)34 1-23. FPGA直流电机PWM控制实验35 1-24. VGA彩条信号显示控制器设计37 1-25. VGA图像显示控制器设计37 1-26. 清华大学学生基于GW48PK2系统VGA图像显示控制器设计示例5则38 1-27. 直接数字式频率合成器(DDS)设计实验(电子设计竞赛赛题)39 1-28. 嵌入式锁相环PLL应用实验41 1-29. 使用嵌入式锁相环的DDS设计实验(200MHz超高速DAC的PLL测试42 1-30. 基于DDS的数字移相信号发生器设计(电子设计竞赛赛题)45 1-31. 采用超高速A/D的存储示波器设计(含PLL,电子设计竞赛赛题)46 1-32. 信号采集与频谱分析电路设计(电子设计竞赛赛题)46 1-33. 等精度数字频率/相位测试仪设计实验(电子设计竞赛赛题)48 1-34. FPGA与单片机联合开发之isp单片机编程方法49 1-35. 测相仪设计(电子设计竞赛赛题)50 1-36. PS/2键盘鼠标控制电子琴模块设计50 1-37. PS/2鼠标与VGA控制显示游戏模块设计50 1-38. FPGA_单片机_PC机双向通信测频模块设计50 1-39. 10路逻辑分析仪设计(电子设计竞赛赛题)51 1-40. IP核:数控振荡器NCO应用设计52 1-41. IP核:FIR数字滤波器应用设计53 1-42. IP核:FFT应用设计53 1-43. IP核:CSC VGA至电视色制互转模块应用设计54 1-44. IP核:嵌入式逻辑分析仪SignalTapII调用55 1-45. USB与FPGA通信实验56第二章 SOPC/EDA设计实验I56 2-1 用逻辑锁定优化技术设计流水线乘法器实验57 2-2 用逻辑锁定优化技术设计16阶数字滤波器实验59 2-3 基于DSP Builder的FIR数字滤波器设计实验60 2-4 基于DSP Builder的IIR数字滤波器设计实验60 2-5 基于DSP Builder的DDS与数字移相信号发生器设计实验62 2-6 m序列伪随机序列发生器设计实验63 2-7 巴克码检出器设计实验65 2-8 RS码编码器设计实验65 2-9 正交幅度调制与解调模型设计实验67 第三章 SOPC/EDA设计实验II67 3-1 基于MATLAB/DSP Builder DSP可控正弦信号发生器设计72 3-2 32位软核嵌入式处理器系统Nios开发实验73 3-3 设计一个简单的SOPC系统74 3-4 简单测控系统串口接收程序设计74 3-5 GSM短信模块程序设计75 3-6 基于SOPC的秒表程序设计77 3-7 Nios Avalon Slave外设(PWM模块)设计78 3-8 Nios Avalon Slave外设(数码管动态扫描显示模块)设计79 3-15 DMA应用和俄罗斯方块游戏设计79第四章 SOPC/EDA设计实验III ( NiosII系统设计 ) 79 4-1、建立NIOSII嵌入式处理器硬件系统87 4-2、NIOSII软件设计与运行流程94 4-3、加入用户自定义组件设计100 4-4、加入用户自定义指令设计103 4-5、FLASH编程下载104 4-6、设计DSP处理器功能系统104 4-7、AM调制电路设计105第五章液晶接口实验105 5-1 GDM12864A液晶显示模块接口开发111 5-2 HS162-4液晶显示模块与单片机的接口114 5-3 G240-128A液晶显示模块的接口115第六章 CPU及其结构组件设计实验115 6-1 复杂指令CPU设计122 6-2 8051/89C51单片机核于FPGA中实现实验124第七章模拟EDA实验124 7-1 模拟EDA实验及其设计软件使用向导(PAC _Designer使用)124 7-2 基于ispPAC80的5阶精密低通滤波器设计126 7-3 基于ispPAC10的直流增益为9的放大器设计129附录:GW48 EDA/SOPC主系统使用说明129 第一节:GW48教学系统原理与使用介绍,132 第二节:实验电路结构图137 第三节:超高速A/D、D/A板GW-ADDA说明138 第四节:步进电机和直流电机使用说明138 第五节:SOPC适配板使用说明139 第六节:GWDVPB电子设计竞赛应用板使用说明141 第七节:GWCK/PK2/PK3系统万能接插口与结构图信号/与芯片引脚对照表第一章EDA_VHDL实验/设计与电子设计竞赛1-1. 应用QuartusII完成基本组合电路设计(1) 实验目的:熟悉QuartusⅡ的VHDL文本设计流程全过程,学习简单组合电路的设计、多层次电路设计、仿真和硬件测试。

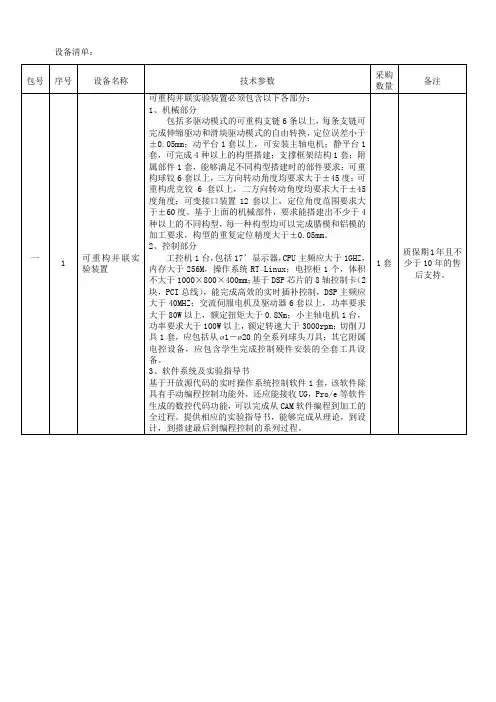

设备清单

教学机器人

硬件组成:

1)机电系统:高强度ABS地盘;锌合金齿轮头,差轮传动,最快速度≥1M/S。

2)能源系统:标准电压约7V,高能量锂电池,可在线充电。

3)传感器:2个分辨率≥30脉冲转的光电编码器,2个光敏传感器,2个红外发射传感器,1个红外接受传感器,1个声音传感器,1套碰撞传感器。至少可检测8个方向。

3套

质保期1年且不少于10年的售后支持。

2

双DSP电机教学实验系统

系统包括双DSP电机教学实验系统、电机驱动模块和24V直流无刷电机。

(1)DSP基本系统

TMS320F2812-高性能32位定点DSP,主频150MHz,SRAM-基本配置64K×16位,内部Flash-128K×16位,串行512字节EEPROM,实时时钟RTC,片内16路12bit分辨率A/D,外部扩展4通道12bit分辨率,量程10v D/A,16路专用于电机控制的PWM接口,看门狗电路、电源监视、上电和手动复位,2路编程可选的RS232/RS422/RS485,1路CAN总线扩展接口,1路符合2.0标准的USB2.0高速接口;

8)提供RJ45标准以太网接口,实现视频服务器或网络摄像机功能;

9)支持脱机与PCI接口两种工作模式,PCI接口工作模式可实现多板工作;

10)具有嵌入式ESAM加密模块,可更有效地保护用户的知识产权。

11)实现对云台控制。

(2)软件平台

1)提供各种测试程序源代码:存储器、UART、视频输入/输出、音频输入/输出、IDE硬盘接口、10/100M以太网接口(提供TCP/IP协议库)、ESAM嵌入式安全加密模块、RTC实时时钟、数字I/O、Boot上电自举等各种硬件功能模块的测试程序;

2、控制部分

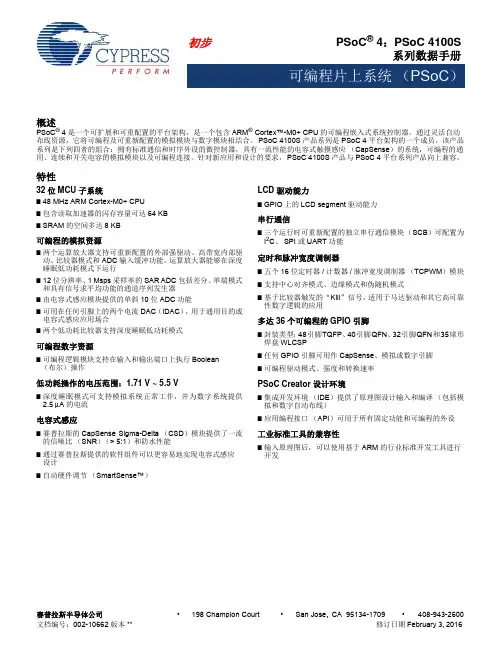

赛普拉斯半导体 PSoC

初步PSoC® 4:PSoC 4100S系列数据手册可编程片上系统(PSoC)概述PSoC® 4是一个可扩展和可重配置的平台架构,是一个包含ARM® Cortex™-M0+ CPU的可编程嵌入式系统控制器。

通过灵活自动布线资源,它将可编程及可重新配置的模拟模块与数字模块相结合。

PSoC4100S产品系列是PSoC 4平台架构的一个成员。

该产品系列是下列四者的组合:拥有标准通信和时序外设的微控制器,具有一流性能的电容式触摸感应(CapSense)的系统,可编程的通用、连续和开关电容的模拟模块以及可编程连接。

针对新应用和设计的要求,PSoC 4100S产品与PSoC 4平台系列产品向上兼容。

特性32位MCU子系统■48 MHz ARM Cortex-M0+ CPU■包含读取加速器的闪存容量可达64 KB■SRAM的空间多达8 KB可编程的模拟资源■两个运算放大器支持可重新配置的外部强驱动、高带宽内部驱动、比较器模式和ADC输入缓冲功能。

运算放大器能够在深度睡眠低功耗模式下运行■12位分辨率、1 Msps采样率的SAR ADC包括差分、单端模式和具有信号求平均功能的通道序列发生器■由电容式感应模块提供的单斜10位ADC功能■可用在任何引脚上的两个电流DAC(IDAC),用于通用目的或电容式感应应用场合■两个低功耗比较器支持深度睡眠低功耗模式可编程数字资源■可编程逻辑模块支持在输入和输出端口上执行Boolean(布尔)操作低功耗操作的电压范围:1.71 V ~ 5.5 V■深度睡眠模式可支持模拟系统正常工作,并为数字系统提供2.5 A的电流电容式感应■赛普拉斯的CapSense Sigma-Delta(CSD)模块提供了一流的信噪比(SNR)(> 5:1)和防水性能■通过赛普拉斯提供的软件组件可以更容易地实现电容式感应设计■自动硬件调节(SmartSense™)LCD驱动能力■GPIO上的LCD segment驱动能力串行通信■三个运行时可重新配置的独立串行通信模块(SCB)可配置为I2C、SPI或UART功能定时和脉冲宽度调制器■五个16位定时器/计数器/脉冲宽度调制器(TCPWM)模块■支持中心对齐模式、边缘模式和伪随机模式■基于比较器触发的“Kill”信号,适用于马达驱动和其它高可靠性数字逻辑的应用多达36个可编程的GPIO引脚■封装类型:48引脚TQFP、40引脚QFN、32引脚QFN和35球形焊盘WLCSP■任何GPIO引脚可用作CapSense、模拟或数字引脚■可编程驱动模式、强度和转换速率PSoC Creator设计环境■集成开发环境(IDE)提供了原理图设计输入和编译(包括模拟和数字自动布线)■应用编程接口(API)可用于所有固定功能和可编程的外设工业标准工具的兼容性■输入原理图后,可以使用基于ARM的行业标准开发工具进行开发目录功能定义 (4)CPU和存储器子系统 (4)系统资源 (4)模拟模块 (5)固定功能数字模块 (5)GPIO (6)特殊功能外设 (6)引脚布局 (7)引脚的备用功能 (9)电源 (11)模式1:1.8 V到5.5 V外部电源 (11)模式2:1.8 V ± 5%外部电源 (11)开发支持 (12)文档 (12)在线支持 (12)工具 (12)电气规范 (13)最大绝对额定值 (13)器件级规范 (13)模拟外设 (17)数字外设 (25)存储器 (28)系统资源 (28)订购信息 (31)封装 (33)封装图 (34)缩略语 (36)文档惯例 (38)测量单位 (38)修订记录 (39)销售、解决方案和法律信息 (40)全球销售和设计支持 (40)产品 (40)PSoC®解决方案 (40)赛普拉斯开发者社区 (40)技术支持 (40)图1. 框图PSoC 4100S器件能够为硬件和固件的编程、测试、调试和跟踪提供广泛的支持。

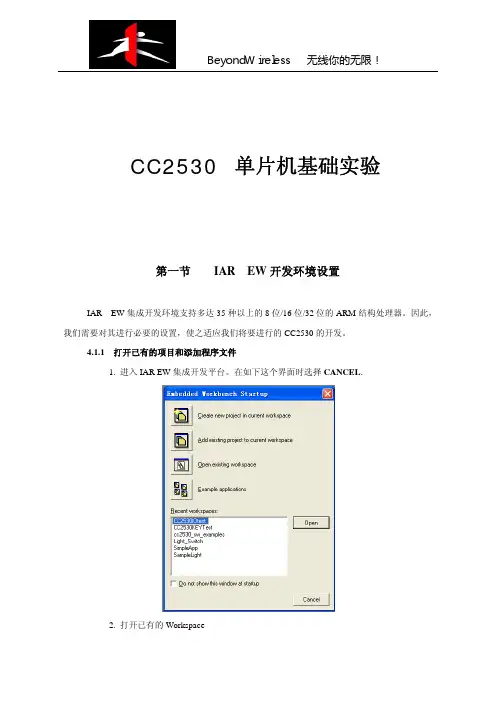

CC2530-MDK中文使用说明_基础实验例程

选择 test.c。

菁扬科技 & 翎跃电子

BeyondWireless 无线你的无限!

点击保存。可以看到左边 Workspace 栏的内容发生了变化。

此时输入源代码进行编程。点击 4.1.3 设置工程选项参数

即可。

菁扬科技 & 翎跃电子

BeyondWireless 无线你的无限!

设置好 Workspace 名称,点击 包括 Warnnig 和 Error。

编译信息显示程序有 Error

即可开始编译。编译信息将会显示在屏幕下方,

菁扬科技 & 翎跃电子

BeyondWireless 无线你的无限!

同时在源程序文件界面下也用 符号标识出来 根据提示信息修改正确,重新编译,编译通过,界面如下:

}

/*****************************************

//按键动作记录函数

*****************************************/

uchar KeyScan(void)

{

if(KEY1 == 1) //高电平有效

{

Delay(100); //检测到按键

void InitIO(void);

//初始化 LED 控制 IO 口函数

/****************************

//延时

*****************************/

void Delay(uint n)

菁扬科技 & 翎跃电子

BeyondWireles键动作 //定义变量记录按键次数

菁扬科技 & 翎跃电子

BeyondWireless 无线你的无限!

断言语法总结

断言assertion被放在verilog设计中,方便在仿真时查看异常情况。

当异常出现时,断言会报警。

一般在数字电路设计中都要加入断言,断言占整个设计的比例应不少于30%。

以下是断言的语法:1. SV A的插入位置:在一个.v文件中:module ABC ();rtl 代码SV A断言endmodule注意:不要将SV A写在enmodule外面。

2. 断言编写的一般格式是:【例】断言名称1:assert property(事件1) //没有分号$display("........",$time); //有分号else$display("........",$time); //有分号断言名称2:assert property(事件2)$display("........",$time);else$display("........",$time);断言的目的是:断定“事件1”和“事件2”会发生,如果发生了,就记录为pass,如果没发生,就记录为fail。

注意:上例中没有if,只有else,断言本身就充当if的作用。

上例中,事件1和事件2可以用两种方式来写:(1) 序列块: sequence name;。

;endsequence(2) 属性块:property name;。

;endsequence从定义来讲,sequence块用于定义一个事件(砖),而property块用于将事件组织起来,形成更复杂的一个过程(楼)。

sequence块的内容不能为空,你写乱字符都行,但不能什么都没有。

sequence也可以包含另一个sequence, 如:sequence s1;s2(a,b);endsequence //s1和s2都是sequence块sequence块和property块都有name,使用assert调用时都是:“assert property(name);”在SV A中,sequence块一般用来定义组合逻辑断言,而property一般用来定义一个有时间观念的断言,它会常常调用sequence,一些时序操作如“|->”只能用于property就是这个原因。

Seal(海豹)5000 系列 FPGA 数据手册说明书

Seal(海豹)5000系列FPGA数据手册西安智多晶微电子有限公司XIAN Intelligent Silicon Technology 西安市高新区科技二路72号西安软件园西岳阁102室邮编710075文档修订历史日期版本修订内容2021.07 1.0 1.首次发布。

2021.07 1.1 1.修改9.9节错字2.修改表9-9。

2021.08 1.2 1.修正1.1章节2.修正表1.1目录1器件概述 (6)1.1特性 (7)1.2器件资源 (3)1.3器件平面布置图(F LOORPLAN) (3)2体系结构概述 (6)2.1可编程逻辑块和查找表(LUT),(PLB)和片(S LICE) (6)2.2S LICES (7)2.3逻辑阵列模块 (13)3嵌入式存储器模块(Embedded RAM Block, ERB) (15)3.1概述 (15)3.2存储器模式 (17)3.3时钟模式 (21)3.4设计考量 (22)4嵌入式乘法器(Embedded Multiplier Block) DSP (23)4.1嵌入式乘法器模块概述 (23)4.2体系结构 (24)4.3操作模式 (26)4.4DSP应用 (28)5可编程I / O缓冲器 (29)5.1I/O单元 (29)5.2I/OB单元特性 (30)5.3I/O标准 (32)5.4I/O模块(BANK) (33)5.5高速I/O接口 (34)6I/O逻辑(IOL) (39)6.1输入寄存器模块 (39)6.2三态寄存器模块 (41)7时钟架构 (43)7.1S EAL 30K与不同容量器件系列时钟架构综合对比 (43)7.2全局时钟分布 (43)7.3边沿时钟(E DGE C LOCK) (45)7.4PLL (46)8千兆收发模块(Gigabit Transceivers) (47)8.1发送器(T RANSMITTER) (48)8.2接收器(R ECEIVER) (49)8.3环形振荡器锁相环(CPLL)与谐振振荡器锁相环(QPLL) (50)9器件编程 (53)9.1概述 (53)9.2配置模式及接口 (54)9.3JTAG模式 (56)9.4SCM模式 (56)9.5SSPI模式 (57)9.6SCPU模式 (59)9.7MSPI模式 (60)9.8JTAG-SPI (62)9.9重配置 (62)9.10软错误检测、修复(SEC) (64)9.11D AISY-CHAIN (66)9.12节约功耗模式 (68)9.13安全性设置 (69)9.14压缩及解压(C OMPRESSION AND D E-COMPRESSION) (69)10模数转换器(Analog-to-Digital Converter ADC) (70)11微控制单元(Microcontroller Unit MCU) (71)11.1MCU系统架构图 (71)11.2MCU时钟架构 (72)11.3MCU中断信号 (72)11.4AHB矩阵 (73)12一次性可编程存储器(eFuse) (74)12.1EFUSE存储数据功能 (74)12.2读写EFUSE流程 (74)13DDR2/3存储控制模块 (75)14PCI Express (PCIe) (79)15Double Data Rate SDRAM接口支持 (80)15.1DDR存储器的DQS组 (80)15.2利用DDRDLL调控DQS延迟与控制模块(DQSBUF) (80)15.3DDRDLL (82)16合封DDR2 SDRAM (83)17直流电气特性 (87)17.1器件允许的极限工作条件 (87)17.2推荐工作范围 (87)17.3热插拔电气参数 (88)17.4直流特性 (88)17.5静态电流 (88)17.6编程与擦除电流 (89)17.7ESD,LATCHUP (89)17.8IOB单端直流特性 (89)17.9IO差分直流特性 (90)17.10BLVDS直流特性 (91)17.11LVPECL直流特性 (91)17.12MIPI直流特性 (91)17.13MCU直流特性 (92)17.14千兆直流特性 (92)18交流电气特性 (93)18.1PLL交流电气特性 (93)18.2时钟交流特性 (93)18.3内部串并/并串时序参数 (94)18.4片内晶振输出频率 (94)18.5EFB交流参数 (94)18.6千兆PLL时钟特性 (95)18.7千兆发送器交流特性 (95)18.8千兆接收器交流特性 (95)19器件编号说明 (96)1器件概述西安智多晶微电子有限公司的Seal(海豹)5000系列FPGA器件(下称“本系列FPGA”),建立在一个优化、高性能28nm工艺基础之上。

ESP32-S3-WROOM-1、ESP32-S3-WROOM-1U 技术规格书说明书

ESP32-S3-WROOM-1ESP32-S3-WROOM-1U技术规格书2.4GHz Wi-Fi(802.11b/g/n)+Bluetooth®5(LE)模组内置ESP32-S3系列芯片,Xtensa®双核32位LX7处理器Flash最大可选16MB,PSRAM最大可选8MB36个GPIO,丰富的外设板载PCB天线或外部天线连接器ESP32-S3-WROOM-1ESP32-S3-WROOM-1U版本1.2乐鑫信息科技版权©20231模组概述1.1特性CPU 和片上存储器•内置ESP32-S3系列芯片,Xtensa ®双核32位LX7微处理器(支持单精度浮点运算单元),支持高达240MHz 的时钟频率•384KB ROM •512KB SRAM •16KB RTC SRAM •最大8MB PSRAM Wi-Fi•802.11b/g/n•802.11n 模式下数据速率高达150Mbps •帧聚合(TX/RX A-MPDU,TX/RX A-MSDU)•0.4µs 保护间隔•工作信道中心频率范围:2412~2484MHz蓝牙•低功耗蓝牙(Bluetooth LE):Bluetooth 5、Bluetooth mesh•速率支持125Kbps 、500Kbps 、1Mbps 、2Mbps •广播扩展(Advertising Extensions)•多广播(Multiple Advertisement Sets)•信道选择(Channel Selection Algorithm #2)•Wi-Fi 与蓝牙共存,共用同一个天线外设•GPIO 、SPI 、LCD 、Camera 接口、UART 、I2C 、I2S 、红外遥控、脉冲计数器、LED PWM 、USB 1.1OTG 、USB Serial/JTAG 控制器、MCPWM 、SDIO 主机接口、GDMA 、TWAI ®控制器(兼容ISO 11898-1)、ADC 、触摸传感器、温度传感器、定时器和看门狗模组集成元件•40MHz 集成晶振•最大16MB Quad SPI flash 天线选型•板载PCB 天线(ESP32-S3-WROOM-1)•通过连接器连接外部天线(ESP32-S3-WROOM-1U)工作条件•工作电压/供电电压:3.0~3.6V •工作环境温度:–65°C 版模组:–40~65°C –85°C 版模组:–40~85°C –105°C 版模组:–40~105°C认证•RF 认证:见证书•环保认证:RoHS/REACH 测试•HTOL/HTSL/uHAST/TCT/ESD1.2描述ESP32-S3-WROOM-1和ESP32-S3-WROOM-1U是两款通用型Wi-Fi+低功耗蓝牙MCU模组,搭载ESP32-S3系列芯片。

(整理)单片机最小系统设计

第4章单片机最小系统设计制作训练内容提要在电子竞赛设计中,单片机作为系统的控制核心广泛应用。

本章介绍了单片机最小系统电路板、通用键盘显示电路、液晶显示模块、A/D及D/A转换等单元电路设计及其程序设计。

知识要点:单片机最小系统,可编程键盘和显示器的接口电路,MDLS点阵字符型液晶显示模块,点阵图形型液晶显示模块,A/D与D/A,程序设计。

教学建议: 本章的重点是掌握单片机最小系统与接口电路的设计与制作。

建议学时数为8学时。

单片机最小系统在竞赛中可以选用成品。

但单片机作为竞赛作品中的核心部件,软件编程训练可以利用单片机开发系统进行培训,通过对单片机最小系统硬件的设计制作,可以使学生加深对单片机的了解。

液晶显示模块采用成品,接口电路与程序设计是训练的重点。

A/D与D/A等电路需要进行设计制作。

设计制作的产品可以作为子系统或者模块保留备用。

训练中要求学生完成电原理图、印制板图、装配图、实际制作、电路调试、设计总结报告。

4.1 单片机最小系统设计制作4.1.1 单片机最小系统电路板硬件设计单片机最小系统电路板可选用AT89C51、AT89C52等DIP-40封装的单片机作为MCU。

系统包括时钟电路,复位电路,扩展了片外数据存储器和地址锁存器。

系统还设置了8个并行键盘S1~S4,S6~S9,6个共阳极LED数码管LED1~LED6。

系统无需扩展程序存储器,用户可根据系统程序大小选择片内带不同容量闪存的单片机,例如PHILIPS半导体公司推出的P89C66X Flash单片机,其片内Flash ROM容量最大可达64KB。

系统还提供基于8279的通用键盘显示电路、液晶显示模块、A/D及D/A转换等众多外围器件和设备接口。

单片机最小系统原理框图如图4.1.1所示。

最小系统电路原理图如图4.1.2所示。

LED数码管和并行键盘电路原理图如图4.1.3所示。

图4.1.1单片机最小系统原理框图图4.1.2 单片机最小系统电原理图图4.1.3 LED数码管和并行键盘电路原理图单片机时钟信电路原理图如图4.1.4所示。

xilinxvivadozynq7000入门笔记_图文

IP Integrator flow1.创建RTL工程2.创建IP Integrator Block Design3.添加zynq 处理器ip中搜索zynq,添加zynq7 Processing System,其中的BFM版本为先前的IP处理器版本。

鼠标右键点击FIXED_IO和DDR接口,选择make external,连接到芯片外部。

但此时处理是完全未经过配置的,双击处理器进行配置。

自动添加的外部接口:(参考ug585文档)FIXED_IO, 是专用的内部固化的外设IO,作用?54个MIO口,DDR_VRN,DDR_VRP: DDR DCI voltage reference pins, refer to UG933, Zynq-7000 AP SoC PCB Design and Pin Planning Guide.PS_SRSTB: Debug system reset, active Low. Forces the system to enter a reset sequence.PS_CLK: System reference clockPS_PORB: Power on reset, active lowDDR接口,处理器ddr内存寻址接口;M_AXI_GP0_ACLK,M_AXI_GP0,在PS-PL Configuration中可取消对GP Master AXI Tnterface的选择FCLK_CLK0:PL Pabric Clocks,不使用可在Clock Configuration 中disable。

FCLK_RESET0_N:时钟复位使能,可在General中disable 。

4.配置processing System,配置处理器内部控制模块的详细功能与特性查看:Soc Technical Reference manual/support/documentation/user_guides/ug585-Zynq-7000-TRM.pdf通用配置:(1)MIO配置:Bank0与Bank1分区的IO对应FPGA处理器可配置的IO,由硬件决定电平还是芯片已经指定电平?由硬件决定。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

美信DIY设计大赛,Xilinx最新28nm ZED开发板等你尝鲜试用!

当记忆的“碎片”永远保持鲜绿,谁还能记得一张张泛黄老照片背后沧桑的岁月,胶片时代的结束,

代表的不仅是数字化对模拟无情的冲击,也印证了数模混合信号时代来临的势不可挡。

28nm FPGA--数模混合技术的新宠,突破重重工艺和技术挑战,将模拟系统与可编程逻辑紧密结

合,打造完美混合信号平台,实现模拟世界与数字世界的完美对接。

在即将到来的2012之夏,美信公司携最新28nm FPGA开发平台与强大的模拟、混合信号产品打

造的DIY设计大赛火热来袭!参加这次大赛,你将:

1. 成为国内首批亲身体验ZED开发板的工程师。尝鲜不容错过!ZED(Zynq Evaluation and

Development)这款基于Zynq设计的FPGA开发板会带给你诸多惊喜--28nm 技术并嵌入工业级标准

ARM Contex-A9双核,赛灵思最新软件平台的支持,让硬件设计,可以轻松实现,给你提供一个强

大的开发平台!

2. 美信公司强大的产品库供你选择。经性能对比,在最“潮”的ZED开发板中,电源、电压基准、

时钟发生器(RTC)、系统管理IC等核心器件均采用美信公司产品,可见美信产品与ZED开发板的

匹配度非同一般。同时,美信公司也尽其所能为此次大赛提供强劲的外围器件支持,助你打造完美

的技术方案,模拟你的世界!

28nm FPGA的后现代生活什么惊喜?等你发现,由你主导!

报名教程:

1.注册成为美信社区会员,完善个人信息,在美信社区论坛的“美信DIY设计大赛讨论区”版块

中发表新帖:写明项目题目+项目简介完成报名。

切记,请大家在发帖时,从发帖类型中选择“美信DIY设计大赛”分类;

大赛日程表

2012年5月28 日-2012年7月15日 方案提交(方案模板参见附件1)

2012年7月16日-2012年7月31日 方案筛选,从提交的设计方案中筛选出50

个合格方案

2012年8月1日-2012年9月16日 项目设计及项目提交(设计方案完整版、

程序完整版、项目演示视频连接,项目报

告书参考附件2)

2012年9月17日-2012年9月30日 大赛评奖及颁奖

第一阶段:2012年5月28日-2012年7月15日(提交参赛方案)

1. 在大赛讨论区中完成报名后,进行项目方案设计,完成后将完整设计方案发送至竞赛联系邮箱

contest_maxim@eefocus.com,方案模板参见附件1

注意啦:项目中用到的模拟、电源芯片须采用美信公司产品,有样片支持的美信产品均在可选择范

围内,大家要在方案设计中明确列出用到的美信产品名称和数量,便于之后的样片申请顺利进行。

第二阶段:2012年7月16日-2012年7月31日(方案初选)

1.根据提交的方案描述,竞赛委员会将从所有的参赛队中挑选出50组参赛队进入决赛;

2. 方案预选完成后将于7月31日在大赛页面及BBS中公布名单

第三阶段:2012年8月1日—2012年9月16日(系统设计 & 项目完善)

1. 通过预选的参赛者在规定的时间范围内(8月1日~8月3日)到美信竞赛样片申请专用通道 ,

以与非网提供的项目编号以及竞赛标识完成美信相关芯片的申请,承办方会将ZED开发板寄送

给通过预选的参赛队;

2. 设计过程中,参赛者可以从“美信DIY设计大赛讨论区”获得在线技术支持;

3. 设计完成以后工程师将最终设计方案、程序完整版、项目演示视频连接发到竞赛联系邮箱,方

案提交可参考附件2项目报告书模板

第四阶段:2012年9月17日—2012年9月30日(评选 & 颁奖)

1. 竞赛委员会将从50支参赛队提交的最终设计方案以及其他相关项目资料中做出评选结果,于9

月30日将获奖者名单公布于大赛页面及BBS 中,并完成颁奖

评选规则

项目评选将综合考虑项目创新性、实用性以及项目资料完善度几项因素

竞赛联系邮箱:contest_maxim@eefocus.com

竞赛在线技术支持及讨论专区:美信DIY设计大赛讨论区

官方报名地点:美信DIY设计大赛