EDA练习及答案

eda考试试卷及答案

eda考试试卷及答案EDA考试试卷及答案一、单项选择题(每题2分,共20分)1. EDA技术主要应用于以下哪个领域?A. 教育B. 电子设计自动化C. 医疗D. 交通答案:B2. 在EDA软件中,以下哪个不是设计输入的基本方法?A. 原理图输入B. 文本输入C. 手绘输入D. 硬件描述语言输入答案:C3. 以下哪个不是数字逻辑电路设计的基本步骤?A. 逻辑功能设计B. 电路原理图设计C. 电路仿真测试D. 机械结构设计答案:D4. 在EDA技术中,VHDL和Verilog HDL属于以下哪种类型的硬件描述语言?A. 行为级描述B. 结构级描述C. 数据流描述D. 寄存器传输级描述答案:A5. 在EDA设计中,以下哪个工具主要用于PCB布局和布线?A. 仿真软件B. 原理图编辑器C. 逻辑综合工具D. PCB设计软件答案:D6. 以下哪个不是EDA设计中的测试验证方法?A. 功能仿真B. 时序仿真C. 硬件仿真D. 软件仿真答案:D7. 在EDA设计中,以下哪个不是FPGA的配置方式?A. 在系统编程B. 串行配置C. 并行配置D. 网络配置答案:D8. 在EDA设计中,以下哪个不是可编程逻辑器件?A. PALB. PLAC. FPGAD. TTL集成电路答案:D9. 在EDA设计中,以下哪个不是逻辑优化的目标?A. 减少逻辑门数量B. 减少功耗C. 提高电路速度D. 增加电路复杂度答案:D10. 在EDA设计中,以下哪个不是PCB设计需要考虑的因素?A. 信号完整性B. 电源完整性C. 电磁兼容性D. 机械强度答案:D二、多项选择题(每题3分,共15分)11. EDA技术可以应用于以下哪些领域?(多选)A. 通信B. 计算机C. 消费电子D. 工业控制答案:ABCD12. 在EDA设计中,以下哪些是常见的仿真工具?(多选)A. ModelSimB. Quartus IIC. ISED. MATLAB答案:AD13. 在EDA设计中,以下哪些是常见的FPGA品牌?(多选)A. XilinxB. AlteraD. Cypress答案:ABCD14. 在EDA设计中,以下哪些是PCB设计需要考虑的因素?(多选)A. 信号完整性B. 电源完整性C. 电磁兼容性D. 成本控制答案:ABCD15. 在EDA设计中,以下哪些是可编程逻辑器件?(多选)A. PALB. PLAC. CPLD答案:ABC三、判断题(每题1分,共10分)16. EDA技术可以提高电路设计的效率和准确性。

EDA考试题题库及答案

EDA考试题题库及答案一、选择题1.一个项目的输入输出端口是定义在(A)A、实体中;B、结构体中;C、任何位置;D、进程中。

2.QuartusII中编译VHDL源程序时要求(C)A、文件名和实体可以不同名;B、文件名和实体名无关;C、文件名和实体名要相同;D、不确定。

3.VHDL语言中变量定义的位置是(D)A、实体中中任何位置;B、实体中特定位置;C、结构体中任何位置;D、结构体中特定位置。

4.可以不必声明而直接引用的数据类型是(C)A、STD_LOGIC;B、STD_LOGIC_VECTOR;C、BIT;D、ARRAY。

5.大规模可编程器件主要有FPGA、CPLD两类,下列对FPGA结构与工作原理的描述中,正确的是(C)A、FPGA全称为复杂可编程逻辑器件;B、FPGA是基于乘积项结构的可编程逻辑器件;C、基于SRAM的FPGA器件,在每次上电后必须进行一次配置;D、在Altera公司生产的器件中,MAX7000系列属FPGA结构。

6.下面不属于顺序语句的是(C)A、IF语句;B、LOOP语句;C、PROCESS语句;D、CASE语句。

7.VHDL语言是一种结构化设计语言;一个设计实体(电路模块)包括实体与结构体两部分,实体体描述的是(A)A、器件外部特性;B、器件的内部功能;C、器件的综合约束;D、器件外部特性与内部功能。

8.进程中的信号赋值语句,其信号更新是(C)A、按顺序完成;B、比变量更快完成;C、在进程的最后完成;D、都不对。

9.在EDA工具中,能完成在目标系统器件上布局布线软件称为(C)A、仿真器B、综合器C、适配器D、下载器10.VHDL常用的库是(A)A、IEEE;B、STD;C、WORK;D、PACKAGE。

11.在VHDL中,用语句(D)表示clock的下降沿。

A、clock'EVENT;B、clock'EVENT AND clock='1';C、clock='0';D、clock'EVENT AND clock='0'。

《EDA涉爆粉尘》测试题

《EDA涉爆粉尘》测试题废渣/钛屑应使用以下哪种容器盛装存储? [单选题]吨袋木箱金属容器桶盖打孔的金属容器(正确答案)以下哪种物品不能与废渣/钛屑在同一区域内存放? [单选题]化学品易燃品易爆品以上都是(正确答案)DDG废渣可以和以下哪种废渣/钛屑混装储存? [单选题]CNC钛丝裁切废渣扒皮钛屑不可与其他废渣/钛屑混装(正确答案)EDA管控区域都有配备灭火器与消防沙等应急处置物质,当钛渣发生起火时应使用以下哪种灭火器? [单选题]ABC类灭火器D类灭火器(正确答案)泡沫灭火器水基型灭火器废渣/钛屑暂存区应满足()条件。

[单选题]通风良好(正确答案)潮湿阴暗密闭空间以上都不是废渣/钛屑暂存区如需动火作业,需申请()动火作业证。

[单选题] 一级二级三级禁止动火作业(正确答案)废渣应优先采用以下哪种方式储存更为安全? [单选题]水泡储存机械压块(正确答案)露天储存晒干储存下面不能够引起燃烧爆炸危险的粉尘有哪个:() [单选题]镁铝粉尘面粉植物纤维粉尘无机硅酸盐类粉尘(水泥粉尘等)(正确答案)不产生可燃粉尘的设备是:() [单选题]量测制程(正确答案)DDG机裁切机毛化机钛渣充分燃烧起来的温度有多少摄氏度? [单选题]500 摄氏度1000摄氏度2000摄氏度6500摄氏度(正确答案)废钛渣线边存储点,应()小时内转移至暂存仓 [单选题]812(正确答案)2448非乙类废渣存储仓,废渣将优先采用()小时清运时限转运至有资质的厂商回收处理。

[单选题]24(正确答案)364860废渣/钛屑储存区域应独立建设,并远离()等人员密集场所。

[单选题]生产区域宿舍区域生活区域以上都是(正确答案)以下哪几种清洁工具符合EDA管控要求? [单选题]植物棕毛扫把、木质垃圾铲、铜铲、铜刷(正确答案)塑料扫把、塑料垃圾铲、铁铲工业级防爆吸尘器、塑料毛刷、抹布以上都是打磨、抛光、切割、研磨产生的粉尘可通过以下哪种方式降低安全隐患? [单选题] 湿抛(正确答案)干抛干式过滤器以上都可镁铝合金粉尘遇研磨剂时,会产生:() [单选题]铝蒸气镁蒸气氢气(正确答案)水蒸气一般常见潜在的点火源指? [单选题]明火、焊接、切割打磨、电火花、静电摩擦生热、机械冲击以上都是(正确答案)火柴及打火机禁止带入燃爆粉尘车间; [判断题]对(正确答案)错为便于清理空间内部粉尘,使用气枪吹扫; [判断题]对错(正确答案)灭火器材放置区域不能出现堆放物品遮挡,以免影响应急使用。

eda考试题及答案

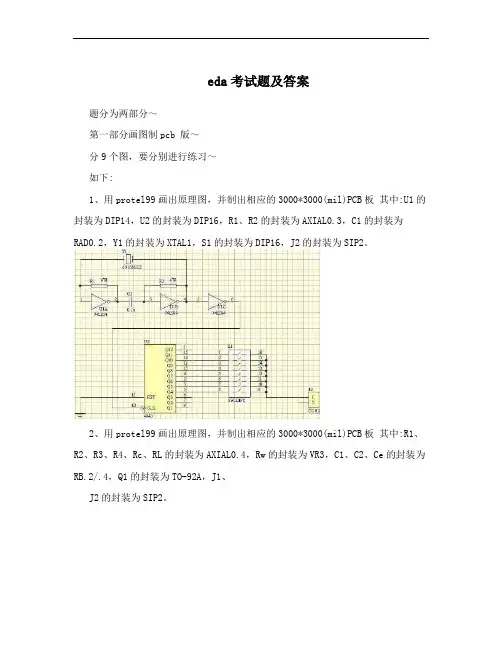

eda考试题及答案题分为两部分~第一部分画图制pcb 版~分9个图,要分别进行练习~如下:1、用protel99画出原理图,并制出相应的3000*3000(mil)PCB板其中:U1的封装为DIP14,U2的封装为DIP16,R1、R2的封装为AXIAL0.3,C1的封装为RAD0.2,Y1的封装为XTAL1,S1的封装为DIP16,J2的封装为SIP2。

2、用protel99画出原理图,并制出相应的3000*3000(mil)PCB板其中:R1、R2、R3、R4、Rc、RL的封装为AXIAL0.4,Rw的封装为VR3,C1、C2、Ce的封装为RB.2/.4,Q1的封装为TO-92A,J1、J2的封装为SIP2。

3、用protel99画出原理图,并制出相应的2000*2000(mil)PCB板其中:R1、R2、R3的封装为AXIAL0.4,R的封装为VR2,UA741的封装为DIP8,JP1、JP2的封装为SIP2。

4、用protel99画出原理图,并制出相应的3000*3000(mil)PCB板其中:R1、R2、R3、R4、R5、R6、R7的封装为AXIAL0.4,U1、U2、DS1的封装为DIP16。

5、用protel99画出原理图,并制出相应的2000*2000(mil)PCB板其中:U1、U2的封装为DIP14,J1、J2的封装为SIP2。

6、用protel99画出原理图,并制出相应的2000*2000(mil)PCB板其中:U1的封装为DIP16,U2、U3的封装为DIP14, J2的封装为SIP3。

7、用protel99画出原理图,并制出相应的2000*3000(mil)PCB板其中:R1、R2、R3、R4、R5、R6、R7的封装为AXIAL0.4,Rw的封装为VR3,U1的封装为DIP8, J1的封装为SIP2。

8、用protel99画出原理图,并制出相应的2000*2000(mil)PCB板其中: U1的封装为DIP16,U2的封装为DIP14,J1的封装为SIP6。

eda考试及答案

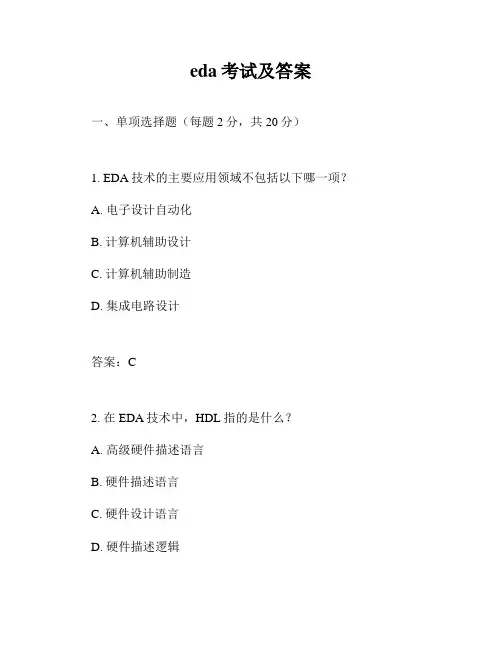

eda考试及答案一、单项选择题(每题2分,共20分)1. EDA技术的主要应用领域不包括以下哪一项?A. 电子设计自动化B. 计算机辅助设计C. 计算机辅助制造D. 集成电路设计答案:C2. 在EDA技术中,HDL指的是什么?A. 高级硬件描述语言B. 硬件描述语言C. 硬件设计语言D. 硬件描述逻辑答案:B3. 以下哪个不是EDA软件的主要功能?A. 电路仿真B. 电路优化C. 电路布局D. 电路测试答案:D4. 在EDA设计流程中,哪个步骤是用于验证电路设计的逻辑功能是否正确?A. 综合B. 布局C. 功能仿真D. 布线答案:C5. 以下哪个是用于描述数字电路行为的硬件描述语言?A. VHDLB. VerilogC. C语言D. Java答案:A6. 在EDA设计中,哪个步骤涉及到将高级硬件描述语言转换为门级网表?A. 综合B. 功能仿真C. 布局D. 布线答案:A7. 以下哪个不是EDA设计中的测试向量?A. 静态测试向量B. 动态测试向量C. 随机测试向量D. 人工测试向量答案:D8. 在EDA设计中,哪个步骤是用于优化电路的性能和面积?A. 综合B. 布局C. 布线D. 优化答案:D9. 以下哪个是EDA设计中的可编程逻辑器件?A. FPGAB. ASICC. CPLDD. 以上都是答案:D10. 在EDA设计中,哪个步骤涉及到将电路设计映射到实际的物理芯片上?A. 综合B. 布局C. 布线D. 封装答案:C二、多项选择题(每题3分,共15分)11. EDA技术可以应用于以下哪些领域?A. 通信系统设计B. 计算机系统设计C. 消费电子产品设计D. 汽车电子系统设计答案:ABCD12. 在EDA设计流程中,以下哪些步骤是必要的?A. 功能仿真B. 综合C. 布局D. 布线答案:ABCD13. 以下哪些是硬件描述语言的特点?A. 可读性强B. 可移植性好C. 可扩展性好D. 可维护性好答案:ABCD14. 在EDA设计中,以下哪些因素会影响电路的性能?A. 电路的逻辑复杂度B. 电路的布局C. 电路的布线D. 电路的优化答案:ABCD15. 以下哪些是可编程逻辑器件的优势?A. 可重构性B. 灵活性高C. 开发周期短D. 成本低答案:ABCD三、判断题(每题2分,共10分)16. EDA技术可以提高电路设计的效率和准确性。

EDA选择题(含答案)解析

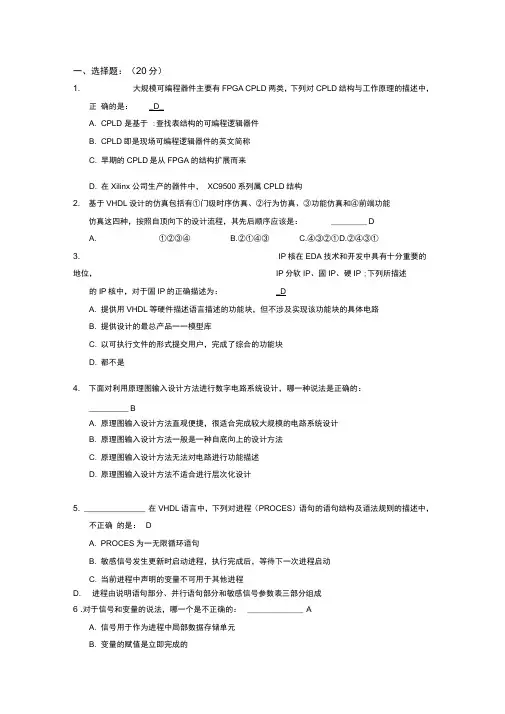

一、选择题:(20分)1. 大规模可编程器件主要有FPGA CPLD两类,下列对CPLD结构与工作原理的描述中,正确的是:_D_A. CPLD 是基于 :查找表结构的可编程逻辑器件B. CPLD即是现场可编程逻辑器件的英文简称C. 早期的CPLD是从FPGA的结构扩展而来D. 在Xilinx 公司生产的器件中,XC9500系列属CPLD结构2. 基于VHDL设计的仿真包括有①门级时序仿真、②行为仿真、③功能仿真和④前端功能仿真这四种,按照自顶向下的设计流程,其先后顺序应该是:_________ DA. ①②③④B.②①④③C.④③②①D.②④③①3. IP核在EDA技术和开发中具有十分重要的地位,IP分软IP、固IP、硬IP ;下列所描述的IP核中,对于固IP的正确描述为:_DA. 提供用VHDL等硬件描述语言描述的功能块,但不涉及实现该功能块的具体电路B. 提供设计的最总产品一一模型库C. 以可执行文件的形式提交用户,完成了综合的功能块D. 都不是4. 下面对利用原理图输入设计方法进行数字电路系统设计,哪一种说法是正确的:_________ BA. 原理图输入设计方法直观便捷,很适合完成较大规模的电路系统设计B. 原理图输入设计方法一般是一种自底向上的设计方法C. 原理图输入设计方法无法对电路进行功能描述D. 原理图输入设计方法不适合进行层次化设计5. _____________ 在VHDL语言中,下列对进程(PROCES)语句的语句结构及语法规则的描述中,不正确的是:DA. PROCES为一无限循环语句B. 敏感信号发生更新时启动进程,执行完成后,等待下一次进程启动C. 当前进程中声明的变量不可用于其他进程D. 进程由说明语句部分、并行语句部分和敏感信号参数表三部分组成6 .对于信号和变量的说法,哪一个是不正确的:______________ AA. 信号用于作为进程中局部数据存储单元B. 变量的赋值是立即完成的C. 信号在整个结构体内的任何地方都能适用D. 变量和信号的赋值符号不一样7.________________________________ 下列状态机的状态编码,方式有“输出速度快、难以有效控制非法状态出现”这个特点。

EDA技术习题集及答案

第一章 EDA概述一、填空题1.2000年推出的Pentium 4微处理器芯片的集成度达——万只晶体管。

2.一般把EDA技术的发展分为——、——和——三个阶段。

3.在EDA发展的——阶段,人们只能借助计算机对电路进行模拟、预测,以及辅助进行集成电路版图编辑、印刷电路板(PcB)布局布线等工作。

4.在EDA发展的——阶段,人们可以将计算机作为单点设计工具,并建立各种单元库,开始用计算机将许多单点工具集成在一起使用。

5.EDA设计流程包括——、——、——和——四个步骤。

6.EDA的设计验证包括——、——和——三个过程。

7.EDA的设计输入主要包括——、——和———。

8.文本输入是指采用——进行电路设计的方式。

9.功能仿真是在设计输入完成之后,选择具体器件进行编译之前进行的逻辑功能验证,因此又称为——。

10.时序仿真是在选择了具体器件并完成布局、布线之后进行的时序关系仿真,因此又称为——或——。

11.当前最流行的并成为1EEE标准的硬件描述语言包括————和——。

12.采用PLD进行的数字系统设计,是基于芯片的设计或称之为——的设计。

13.硬件描述语言HDL给PLD和数字系统的设计带来了更新的设计方法和理念,产生了目前最常用的并称之为——的设计法。

14.EDA工具大致可以分为——、——、———、———和——等五个模块。

15.将硬件描述语吉转化为硬件电路的重要工具软件称为——————。

二、单项选择题1.将设计的系统或电路按照EDA开发软件要求的某种形式表示出来,并送入计算机的过程称为( )。

①设计输入②设计输出③仿真④综合2.一般把EDA技术的发展分为( )几个阶段。

①2 ②3 ③4 ④53.AHDL属于( )描述语言。

①普通硬件②行为③高级④低级4.vHDL属于( )描述语言。

①普通硬件②行为③高级④低级5.包括设计编译和检查、逻辑优化和综合、适配和分割、布局和布线,生成编程数据文件等操作的过程称为( )。

EDA考试复习试题及答案

EDA考试复习试题及答案EDA考试复习试题及答案一、选择题:(20分)1.下列是EDA技术应用时涉及的步骤:A.原理图/HDL文木输入;B.适配;C.时序仿真;D.编程下载;E.硬件测试;F.综合请选择合适的项构成基于EDA软件的FPGA/CPLD设计流程:A—___ F __ — __ B_f _____ C __ f D—___ E ___2.PLD的可编程主要基于A. LUT结构或者B.乘积项结构:请指出下列两种可编程逻辑基于的可编程结构:FPGA 基于___ A_____CPLD 基于___ B_____3.在状态机的具体实现时,往往需要针对具体的器件类型来选择合适的状态机编码。

对于A. FPGAB. CPLD两类器件:一位热码状态机编码方式适合于—A—器件;顺序编码状态机编码方式适合于—B—器件;4.下列优化方法中那两种是速度优化方法:—B_、_D_A.资源共享B.流水线C.串行化D.关键路径优化单项选择题:5.综合是EDA设计流程的关键步骤,综合就是把抽象设计层次中的一种表示转化成另一种表示的过程;在下面对综合的描述中,_D_是错误的。

A.综合就是将电路的高级语言转化成低级的,可与FPGA/CPLD的基本结构相映射的网表文件;B.为实现系统的速度、面积、性能的要求,需要对综合加以约束, 称为综合约束;C.综合可理解为,将软件描述与给定的'硬件结构用电路网表文件表示的映射过程,并且这种映射关系不是唯一的。

D.综合是纯软件的转换过程,与器件硬件结构无关;6.嵌套的IF语句,其综合结果可实现—D—oA.条件相与的逻辑B.条件相或的逻辑C.条件相异或的逻辑D.三态控制电路7.在一个VHDL设计中Idata是一个信号,数据类型为std_logic_vector,试指出下而那个赋值语句是错误的。

DA.idata<= “00001111” ;B.idata<=b>, 0000_llir,;C.idata<=X v AB” ;D.idataOB” 21” ;8.在VHDL语言中,下列对时钟边沿检测描述中,错误的是_D_oA. ifclk' eventandclk= 1 thenB.iff811ing_edge(elk) thenC.ifelk' eventandclk= O thenD.ifclk' stableandnotclk= T then9.请指出AlteraCyclone系列中的EP1C6Q240C8这个器件是属于A. ROMB. CPLDC. FPGAD. GAL二、EDA名词解释,(10分)写出下列缩写的中文(或者英文)含义:1.ASIC专用集成电路2.FPGA现场可编程门阵列3.CPLD复杂可编程逻辑器件4.EDA电子设计自动化6. S0C单芯片系统。

eda习题与答案

eda习题与答案

EDA习题与答案

探索性数据分析(EDA)是数据科学中的一项重要技能,通过对数据进行可视化和统计分析,可以帮助我们更好地理解数据的特征和规律。

在实际应用中,我们经常会遇到各种EDA习题,下面就让我们一起来看看一些常见的EDA习题及其答案。

1. 习题:对一组学生的考试成绩进行EDA,包括成绩的分布、平均分、及格率等统计指标。

答案:首先,我们可以绘制成绩的直方图,以了解成绩的分布情况。

然后计算平均分和及格率,可以通过描述性统计方法来实现。

最后,我们还可以使用箱线图来展示成绩的离散程度和异常值情况。

2. 习题:分析一组房屋价格数据,探索价格的变化趋势和影响因素。

答案:首先,我们可以绘制价格随时间变化的折线图,以了解价格的趋势。

然后可以使用相关系数分析价格与其他因素(如面积、地段、装修等)的关系。

最后,可以利用散点图和回归分析来探讨价格与各种因素之间的关联性。

3. 习题:分析一组销售数据,探索销售额的季节性变化和产品销售额的贡献比例。

答案:首先,可以使用折线图或柱状图来展示销售额随时间的变化情况,以了解销售额的季节性变化。

然后,可以计算各个产品在总销售额中的贡献比例,以了解产品销售情况的分布。

通过以上习题及其答案的分析,我们可以看到EDA在实际应用中的重要性和灵活性。

通过对数据进行可视化和统计分析,我们可以更好地理解数据的特征和

规律,为后续的数据建模和决策提供有力支持。

因此,掌握好EDA技能对于数据科学从业者来说至关重要。

EDA练习题

1. 用EDA技术进行电子系统设计的目标是最终完成专用集成电路(asic)或印制电路板(pcb)的设计与实现。

2. 可编程器件分为简单PLD 和复杂PLD 。

3. 简要说明仿真时阻塞赋值与非阻塞赋值的区别。

答:阻塞式赋值:是一种理想化的数据传输,是立即发生的,不存在任何的延时行为。

表述方式目标变量名=驱动表达式;非阻塞式赋值:是比较真实的电路赋值和输出,因为它从综合的角度考虑到了延时和并行性。

表述方式目标变量名<=驱动表达式;4. 试用Verilog HDL描述一个带进位输入、输出的8位全加器。

端口:A、B为加数,CI为进位输入,S为和,CO为进位输出。

module ADDER8B (A,B,CI,CO,S);output [7:0] S; output CO;input [7:0]A,B; input CI;assign {CO,S} = A + B + CI;endmodule1. 随着EDA技术的不断完善与成熟,自顶向下的设计方法更多的被应用于Verilog HDL 设计当中。

2.写出下列缩写的中文含义:ASIC:专用集成电路RTL:寄存器传送FPGA:现场可编程门阵列CPLD:复杂可编程逻辑器件EDA:电子设计自动化IP:知识产权核3. module AAA( a ,b );input [6:0] b ;定义七位二进制b为输入端口output a ;定义一位二进制a为输入端口reg[2:0] sum; 定义三位二进制sum为寄存器类型integer i; 定义一位二进制i为整数类型reg a 定义一位二进制a为寄存器类型always @ (b) 定义以b为敏感信号的过程语句begin 开始块语句sum = 0; 给sum赋值为0for(i = 0;i<=6;i = i+1) 次数为7的for循环语句if(b[i]) sum = sum+1; 查询并记录二进制数b中含1的数目并赋值给sumif(sum[2]) a = 1; 当sum值大于等于4时a赋值为1else a = 0; 当不满足上述情况时a赋值为0end 结束块语句endmodule 模块结束语句本程序的逻辑功能是:7人投票表决器4. 编写一个带异步清零、异步置位的D触发器。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

EDA技术试卷

一、填空题

1、某一纯组合电路输入为in1,in2和in3,输入出为out,则该电路描述中always的事

件表达式应写为always@(in1,in2,in3 );若某一时序电路由时钟clk信号上升沿触发,同步

高电平复位信号rst清零,该电路描述中always的事件表达是应该写为always

@( posedge clk )。

2、在模块中对任务进行了定义,调用此任务,写出任务的调用 mytast(f,g,m,n,p) 。

task mytast; 要求:变量的传递关系如下

output x,y; m——a,n——b,p——c,x——f,y——g

input a,b,c;

„„.

endtask

3、if(a) out1<=int1; 当a= 1 执行out1<=int1

else out1<=int2; 当a= 0 执行out1<=int2

4、4’ b1001<<2= 4’b100100 ,4’ b1001>>2= 4’b0010 。

5、下面程序中语句5、6、7、11是 并行 执行,语句9、10是 顺序 执行

1 module M(„„);

2 input „„. ;

3 output „„;

4 reg a,b„„;

5 always@(„„..)

6 assign f=c&d;

7 always@(„„..)

8 begin

9 a=„„.;

10 b=„„.;

end

11 mux mux1(out,in0,in1);

Endmodule

二、选择题:

1、下列标示符哪些是合法的(B )

A、$time B、_date C、8sum D、mux#

2、如果线网类型变量说明后未赋值,起缺省值是(D )

A、x B、1 C、0 D、z

3、现网中的值被解释为无符号数。在连续赋值语句中,assign addr[3:0]=-3;addr被赋予

的值是( A )

A、4’b1101 B、4’b0011 C、4’bxx11 D、4’bzz11

4、reg[7:0] mema[255:0]正确的赋值是(A )

A、mema[5]=3’ d0, B、8’ d0; C、1’ b1; D、mema[5][3:0]=4’ d1

5、在code模块中参数定义如下,请问top模块中d1模块delay1、delay2的值是( D )

module code(x,y); module top;

paramee delay1=1,delay2=1; …………….

……………………………… code #(1,5) d1(x1,y1);

endmodule endmodule

A、(1,1) B、(5,5) C、(5,1) D、(1,5)

6、“a=4’ b11001,b=4’ bx110”选出正确的运算结果(B )

A、a&b=0 B、a&&b=1 C、b&a=x D、b&&a=x

7、时间尺度定义为timescale 10ns/100ps,选择正确答案(C )

A、时间精度10ns B、时间单位100ps C、时间精度100ps D、时间精度不确定

8、若a=9,执行$display(“current value=%0b,a=%0d”,a,a)正确显示为(B )

A、current value=1001,a=09 B、current vale=1001,a=9

C、1001,9 D、current vale=00„001001,a=9

9、aways begin #5 clk=0;#10 clk=~clk;end产生的波形( A )

A、占空比1/3 B、clk=1 C、clk=0 D、周期为10

10、在Verilog中定义了宏名 `define sum a+b+c 下面宏名引用正确的是(C )

A、out=’sum+d; B、out=sum+d; C、out=`sum+d; D、都正确

三、简答题

1、always语句和initial语句的关键区别是什么?能否相互嵌套?(5分)

always语句是循环语句,initial只执行一次。它们不能嵌套。

2、画出下面程序综合出来的电路图。(7分)

always@(posedge clk)

begin

q0<=~q2;

q1<= q0;

q2<= q1;

end

3、HA模块程序如下,写出引用HA模块描述FA模块的Verilog程序。(7分)

module HA(A,B,S,C);

input A,B;

output S,C;

assign {C,S}=A+B;

endmodule

module FA(A,B,Ci,Co,S);

input A,B,Ci;

output Co,S;

wire Sl,C1,C2;

HA a(A,B,Sl,C1);

HA b(Sl,Ci,C2,S);

assign Co=C1|C2;

endmodule

4、写出下面程序中变量x,y,cnt,m,q的类型(5分)

Assgin x=y;

always@(posegde clk)

begin

cnt=m+1;

q=~q;

end

四、编程题

1、设计一奇偶校验位生成电路,输入八位总线信号bus,输出及校验位odd,偶校

验位even。

2、设计一个带复位端且对输入时钟clk进行二分频模块,并画出仿真波形。

设计要求:复位信号为同步、高电平有效,时钟的下降沿触发

3、设计一带异步复位端、异步置数段(低电平有效)的四位加法计数器,时钟clk

上升沿有效),复位信号clr,置数信号load、输入数据data、输出qout。并画出仿

真波形。

五题答案1. module parity(even,odd,bus);

output even,odd;

input[7:0] bus; //奇同偶异

assign even=^bus;//偶校验用异或

assign odd=^~bus;//奇校验用同或

endmodule

2. module m2(out,clk,reset);

input reset,clk;

output out;

reg out;

always @(negedge clk)

begin

if(reset)

out<=0;

else

out<=~out;

end

endmodule

3. module adder_4(qout,clr,clk,load,data);

output[3:0] qout;

input[3:0] data;

input load,clr,clk;

reg[3:0] qout;

always @(posedge clk or negedge load or negedge clk)

begin

if(!load)

x为wire型

y为reg或wire型

cnt为reg型

m为reg或wire型

q为reg型

仿真波形

qout<=data;

else if(!clr)

qout<=0;

else qout<=qout+1;

end

endmodule