基于LMX41的低相噪频率源的设计

一种S波段频率源的设计与实现

频率 后 ,首 先 通过 预 引 比例 因 子P 、B 频 器 。得 到分 频 以后 的反 馈信 经A 分

号 ,输入 到锁 相器 ,与分频 以后 的标 准 频率源 信 号在 鉴相 器 中比较 ,输 出

相 位差 不再 随时 间变化 ,这 时误 差 电压 为一 固定 值 ,环路 进入 锁 定状态 。

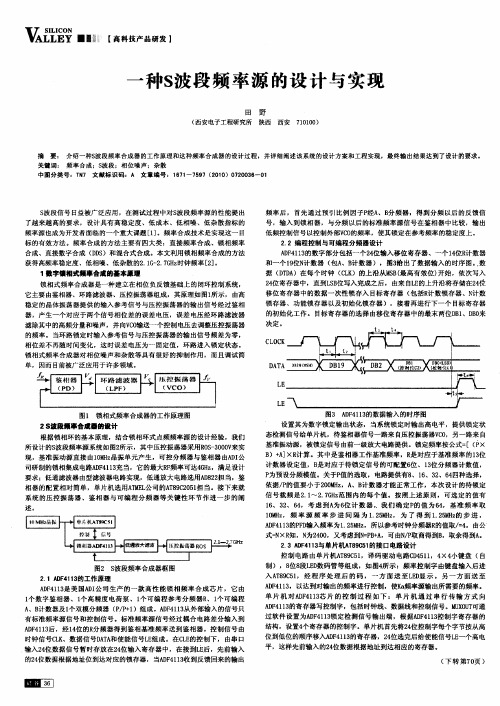

2位 寄存器 中 ,直 ̄L B 写入 完成之 后 ,由来 自L 的上升 沿将存储 在2位 4 J IS位 E 4

移位 寄存 器 中的数 据 一次性 锁 存入 目标 寄存 器 ( 包括 R 计数锁 存器 、N 计数 锁存 器 、功 能锁存 器 以及初 始 化锁存 器 ) ,接着 再进行 下 一个 目标 寄存器 的初 始化 工作 。 目标 寄存 器 的选择 由移 位 寄存器 中的最末 两 位D I B 来 B、D O

述。

图3 A F l3 D4 1的数 据输入 的 时序 图

设 置其 为数 字锁 定输 出状 态 ,当系统 锁定 时输 出高 电平 ,提供 锁定状 态检 测信号 给单 片机 ,待鉴相 器信 号一 路来 自压控 振荡器V O C ,另 一路来 自

基准振 动源 ,被 锁定信 号 由前 一级 放大 电路提 供 。锁 定频 率按 公式= P [( × B A ×R 算 。其 中是鉴 相 器工 作基 准频 率 ,R )+ ] 计 是对应 于 基准 频率 的 1位 3 计数 器设 定值 ,B 对应 于待 锁定 信 号的可 配置 6 、1位 分频器 计 数值 , 是 位 3

V A

一 【科产研 】 黧 高技品发

一

种s 段 频 率 源 的设 计 与实 现 波

基于LMX2594的K波段频率源的设计与实现

基于LMX2594的K波段频率源的设计与实现胡格;王志鹏;文继国【摘要】介绍了一种K波段频率源的设计方法.本文采用LMX2594数字锁相环芯片,并用C8051F330单片机对锁相环芯片进行操作,然后再倍频的方法实现了实现了该K波段频率源的设计.该频率源具有频率稳定度高,相位噪声低,杂散低等优点.测试结果表明该频率源的相位噪声为-90dBc@1kHz,-98dBc@10kHz;输出功率大于10dBm,可以满足系统的各项要求.【期刊名称】《电子世界》【年(卷),期】2018(000)017【总页数】3页(P119-121)【关键词】K波段;频率源;锁相环;相位噪声;杂散【作者】胡格;王志鹏;文继国【作者单位】成都信息工程大学;成都信息工程大学;成都信息工程大学【正文语种】中文1 引言频率源是现代微波通信系统的重要功能单元,在收发射机、雷达、通信、电子对抗和检测仪器等电子设备中被广泛应用,它的性能直接影响整个通信系统的性能[1]。

随着雷达等信息技术的发展,对频率源的稳定性、相位噪声、杂散和体积等性能指标提出了越来越高的要求[2]。

频率源的设计方法有直接频率合成、锁相环频率合成、直接数字频率合成、PLL+DDS频率合成[3-4]。

本文所设计与实现的点频源是通过采用锁相环频率合成技术产生一个点频率然后放大再通过倍频,最后滤波得到我们最终所需的信号。

图1 LMX2594功能框图2 锁相环的工作原理LMX2594是德州仪器生产的一款较高性能的宽带合成器,能产生10MHz至15GHz 范围内的任何频率,其显著特点是实现非常低的带内噪声和集成抖动。

高速N分频器没有预分频器,能够有效减少杂散的数量和振幅。

还有一个可减轻整数边界杂散的可编程输入乘法器。

LMX2594可以是单端输入输出,也可以是差分输入输出。

参考信号先由管脚 OSCINM 或 OSCINP 进入芯片,经过倍频,R分频器,然后再送到鉴相器。

鉴相器的输出经过电荷泵后由管脚CPOUT 输出至外部的环路滤波器,滤波后再经过管脚VTUNE来控制VCO,VCO信号经过一个可编程的N分频器来控制需要的频率,最后通过RFOUT输出。

基于ADF4106的低噪声频率合成器的设计

度 、高稳度 参 考输 入频 率信 号 ,该信 号送 入参 考分

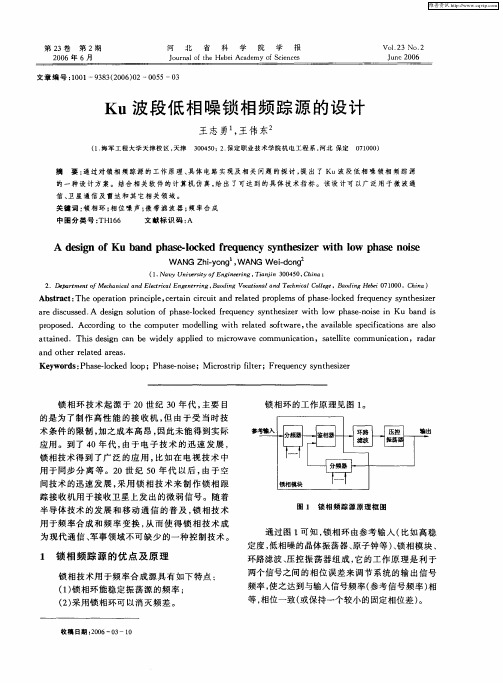

1锁 相 环 原 理

锁 相 环 式 频 率 合 成 是 目前 应 用 最 广 的 一种 频

频器 进行 分频 , 所得信 号 与来 自 VC 的信 号 ( 将 O 经 过 M 分频 后 ) 在鉴 相器 进 行鉴相 , 相器 输 出为相 鉴 位 误 差 信 号 ,经 环 路 滤 波 器 滤 除 高 频 分 量 和 噪 声

・ 2・ 6

现代 导航

21 0 2在

图 1 典 型 锁相 环 原 理框 图

时频 率起 伏 , 的相 位噪 声将 严重 影 响 P L的 正常 大 L

2锁相环 相位 噪声分析

在 实 际应 用 中 ,衡 量 频率合 成 器 的重要 指标就 是输 出信 号 的相位 噪声 。相位 噪声 是指在 各 种 随机

21 0 2年 2月第 1 期

现代 导航

・ 1 6 ・

基于 AD 4 0 F 16的低噪声 频率合成器 的设计

张霄云 ,张永利 2

( 中 国 电子 科 技 集 团 公 司 第 二 十 研 究 所 , 西 安 7 06 ;2 空 军 驻 西 安 地 区军 事 代 表 室 , 西 安 7 0 6 ) 1 10 8 10 8

率 合 成方 式 。它利用 锁 相环 路相 位锁 定 的原 理 ,将 输 出频率 锁 定在参 考 频率 倍频 上 。锁相 环 路相 当 于

收 稿 日期 :2 1-20 。 0 11.7

后 ,输 出直流 电压 去控 制 VC 的振 荡频 率 ,使之 O 输 出所 需的频 率 , 同时达 到锁 相 的 目的 。

用AD9912实现的多功能低相噪信号发生器

用AD9912实现的多功能低相噪信号发生器陈少雄;林盛鑫;陈冰儿【期刊名称】《东莞理工学院学报》【年(卷),期】2022(29)3【摘要】随着无线电通信技术的发展,移动通信、雷达等系统对信号源的要求越来越高,而频率范围宽,高稳定性、相位噪声低的信号源一直是通信领域研究热点,传统的信号源已经无法满足当前电子技术领域研究的需求。

为了研究多功能低相噪信号发生器,采用了直接数字频率合成(Direct Digital Synthesizer,DDS)技术,DDS具有生成频率范围宽、频率分辨率高的特点,广泛应用于信号源电路中[1]。

基于DDS的多功能低相噪信号源,能够支持点频和扫频输出两种模式,产生1 Hz~400 MHz的正弦信号,实现频率范围宽、高稳定性、相位噪声低、控制方便的信号输出。

经测试,200 MHz时,频偏100 kHz,相位噪声为-60.14 dBc/Hz。

结合DDS技术与单片机技术实现DDS多功能信号源,控制方便,便于观察,产生的正弦波信号波形光滑、相位噪声低,可通过进一步提高频率和幅度,加入调相功能,应用于相关设备中。

【总页数】5页(P20-24)【作者】陈少雄;林盛鑫;陈冰儿【作者单位】东莞理工学院电子工程与智能化学院【正文语种】中文【中图分类】TN710【相关文献】1.基于 Qt/Embedded 的多功能信号发生器设计与实现2.基于FPGA与单片机的多功能信号发生器的设计与实现3.基于LabVIEW多功能信号发生器的设计与实现4.基于FPGA的多功能信号发生器设计与实现5.10 GHz 低相噪扩频时钟发生器的设计与实现因版权原因,仅展示原文概要,查看原文内容请购买。

一种自适应的宽频信号源系统设计和实现

一种自适应的宽频信号源系统设计和实现徐飞;李天煜;吕婧;肖钟凯;张国平【摘要】主要介绍了一种宽频带、相位噪声低、杂散抑制度高的频率合成系统.该设计使用了频率合成芯片ADF4351和高速可编程芯片FPGA来完成自适应控制,不仅实现了输出频率范围35 MHz~4.400 GHz、功率可调范围为-4 dBm~5 dBm的低相噪稳定的频率源,同时还实现了对全频带频率的转换时间和跳频范围的智能控制.【期刊名称】《微型机与应用》【年(卷),期】2016(035)008【总页数】3页(P48-50)【关键词】自适应;宽频带;频率合成;ADF4351;FPGA【作者】徐飞;李天煜;吕婧;肖钟凯;张国平【作者单位】桂林电子科技大学电子工程与自动化学院,广西桂林541004;中国科学院深圳先进技术研究院,广东深圳518055【正文语种】中文【中图分类】TN743随着无线通信的不断发展,对频率源的频率稳定度、频谱纯度、频率范围以及输出频率点数的要求也越来越高 [1]。

本设计与传统的频率合成系统相比,在实现输出频带范围大、低相噪、稳定的频率源的基础上,通过智能控制完成了一种自适应的宽频信号源的输出,可根据不同的频段来选择分辨率和频率转换时间以及输出功率的大小;同时简化了电路设计,降低了成本。

频率合成器的优劣直接影响系统的性能。

常用的频率合成方式有直接模拟频率合成(DAS)、直接频率合成(DDS)及锁相频率合成(PLL)。

DAS电路频率转换时间短且频率间隔小,但由于使用了大量的混频、分频、倍频和滤波,使得频率合成器体积大、成本高、结构复杂、容易产生杂散分量且难于抑制;DDS电路分辨率高、频率切换速度快,但是受Nyquist采样定理的限制,目前很难做到较高频率的输出,输出频谱也比较杂散[1]。

而锁相环技术具有输出频率高、频率稳定度高、频谱纯、寄生杂波小以及噪声低等优点,但频率切换之间速度会比较慢[2]。

这就需要在频率源质量和频率切换之间做一个折中的选择,在保证频谱质量的前提下,如何最大限度地缩短频率切换时间。

Ku波段低相噪锁相频踪源的设计

关键词 : 相环 ; 位噪声 ; 带滤波器 ; 率合成 锁 相 微 频

中 图分 类 号 : 1 6 TH 6 文献标识码 : A

A e in o a d p a e lc e r q e c y h ie t o p s o s d sg fKu b n h s -o k d f e u n y s nt e z rwih lw ha e n ie s

锁 相技 术得 到 了广 泛 的应 用 , 比如 在 电视 技 术 中

锁 相 环的工 作原 理见 图 1 。

用 于 同步 分 离 等 。2 0世 纪 5 0年 代 以后 , 于空 由 间技术 的迅 速发 展 , 用 锁 相 技 术 来 制作 锁 相 跟 采

பைடு நூலகம்

踪 接 收机 用于接 收卫 星 上发 出的微 弱信 号 。随着 半导体 技术 的 发展 和移 动 通 信 的普 及 , 相技 术 锁 用于频 率合 成 和频 率 变 换 , 而 使 得 锁 相 技术 成 从 为现 代通 信 、 军事领 域不可 缺 少 的一种 控制 技术 。

Absr c : e o e a in prncp e c ra n cr u ta d r lt d pr plmso a el c d f e u nc yn h sz r ta t Th p r t i i l , e t i ic i n e a e o e fph s —o ke r q e y s t e ie o

J n 0 6 u e2 0

文章 编 号 :0 1 3 3 2 0 ) 2~ 0 5 3 1 0 —9 8 ( 0 6 0 0 5 —0

Ku波段 低 相 噪锁 相 频 踪 源 的设 计

王 志 勇 王 伟 东 ,

S波段低相噪捷变频频率综合器设计

S波段低相噪捷变频频率综合器设计摘要:介绍了一种s波段低相噪捷变频频率综合器设计方法。

由于采用dds+pll的方式使此频率综合器相噪优于-115dbc/hz@1khz,跳频时间小于5us。

关键词:雷达频率综合器低相噪捷变频 dds pll中图分类号:tn77 文献标识码:a 文章编号:1007-9416(2012)11-0138-021、引言频率合成(frequency synthesis)是指以一个或多个参考频率源为基准,在某一频段内,综合产生并输出多个工作频率点的过程。

基于这个原理制成的频率源称为频率综合器(frequency synthesizer)。

频率综合器被人们喻为众多电子系统的“心脏”。

现代战争是争夺电子频谱控制权的战争,频率综合器产生的高质量电子频谱就显得尤为关键;在空间通信、雷达测量、遥测遥控、射电天文、无线电定位、卫星导航和数字通信等先进的电子系统中一个高度稳定的频率综合器对该系统的性能起着决定性的作用;频率综合器在跳频通信系统中也是必不可少的。

本文介绍了一种雷达频率综合器的设计方法,采用dds作为混频锁相环参考源的方案,得到s频段输出信号。

2、技术指标和设计方案频率综合器主要技术指标见表1。

设计方案主要由参考源模块、梳频模块和移频模块3部分构成,如图1所示。

2.1 参考源模块本方案中采用dds产生移频模块的参考信号,通过改变dds的输出频率即改变移频环的参考信号频率来实现最终输出信号的频率步进。

dds输出(140~217.5)mhz作为移频环的参考信号,其频率步进2.5mhz。

移频环鉴相频率(140~217.5)mhz,采用高鉴相频率不仅有利于通过pll的低通特性滤除鉴相频率杂散,而且可以将环路带宽设计更宽以实现捷变频指标。

此设计若采用单环锁相实现,频率步进设计为2.5mhz,即鉴相频率采用2.5mhz,通过与前方案中最小鉴相频率140mhz相比较,可以明显看出,不仅由鉴相频率泄露带来的杂散难以抑制,而且无法满足6us跳频时间的要求。

基于HP41511的微波低噪声放大器的设计

收 稿 日期 : 0 9 0 —1 20 —9 4

放 大器 的增 益 定 义为放 大器 输 出功 率 与输 入

ed c 2 1 . 电 子 元 器 件 壶 用 6 c  ̄ n 0 03 9

.

第 1卷 2

第3 期

电 予元 器 件 焘 用

Elcr n cC mp n n & D v c p l ain e t i o o e t o e ie A p i t s c o

仿 真时 ,可将 噪声 系数 、放大 器增益 、稳 定 系数全 部加 入优化 目标 中进行优 化 .并通 过对带

第l卷 2

期 20第 3 0 年月 1 3

趣谛参尝

V1 o o1N. . 3 2

Ma .2 1 r 00

d i 03 6 /i n1 6 - 7 52 1 .3 2 o: .9 9 .s .5 3 4 9 .0 0 . 2 1 js 00

基于H 4 51 P 1 1的微波低 噪声放 大器 的设计

讯 设 备制 造商 的 普遍 追求 ,而这也 同时对 系统 的

接 收灵 敏度 提 出 了更 高 的要求 。

噪声 系数 的定 义为 放 大器输 入 信 噪 比与输 出 信 噪 比的比值 ,即 : 忙 () 2

1 微 波低 噪声 放 大 器 的 作 用

一

对单级 放 大器而 言 ,其 噪声 系数 的计算 为 :

定接 收 机噪 声 系数 的关 键部 件则 是 处 于接 收机 最 前端 的低 噪声 放大器 。 图 l 示 是 接 收机 射 频 前 端 的原 理 框 图 。 由 所

图 1 见 , 低 噪 声 放 大 器 的 主 要 作 用 是 放 大 天 线 可

对 多级放 大器 .其 噪声 系数 的计 算应 为 : 忙 ^ 1 A 一 )/ 1 ( 乃 1 GG+ +( 1 G+ Ⅳ 一 )/ l2…… () 4 其 中ⅣF 第n 放 大器 的噪声 系数 ,G 为 第n n 为 级

直接数字频率合成低频信号源的设计与实现

难 以集 成 化 且 成 本 高 。间 接 合 成 法 的 核 心是 锁 相 环 技

修 改 稿 收 到 日期 :0 0—0 21 6—2 9。

第一作 者邹 尔宁 , ,9 6年 生 ,9 8年毕 业 于北京航 空 学 院分 院 自 女 15 17

术 , 了合 成 所 需 要 的频 率 , 要 采用 多种 形 式 的锁 相 为 需

Abta t Drc dgt rq ec y tei D S)fa rsa v nae f ih rslt n,p aecniuu p nf q ec w t igad sr c: i t iilf u n ysnhss( DF e a e et e d a t so g eoui u g h o h s o t o su o r un ys i hn n n e c

+ [

丑一 ,

图 1 DDF S原 理 图

Fi 1 Prncp e o g. i il fDDFS

高于其他频段 的频率 覆 盖系数 , 一般 的 R C振 荡器 或 L c振荡器都无法达到… 。随着计算机技术 的发 展 , 数

字技 术 已广 泛 应 用 于 各 类 电 子 测 量 仪 表 , 接 数 字 频 直

正 弦样本 , 需要 一 个容 量 为 2的 计 数器 , 还 以此 得 到 2

推荐-简易低频信号源设计 精品

摘要信号发生器是指产生所需参数的电测试信号的仪器。

按信号波形可分为正弦信号,函数信号,脉冲信号和随机信号发生器等四大类。

信号发生器又称信号源或振荡器。

在生产实践和科技领域中有着广泛的应用。

各种波形曲线均可以产生三角函数方程式来表示。

能够产生多种波形,如三角波、锯齿波,正弦波等。

该设计方案提出的是利用单片机作为控制器,用中断查表法完成波形数据的输出,再用D/A转换器输出规定的波形信号。

方波信号直接由单片机的端口输出。

结合功能要求情况,使用单片机作为控制器,使用DAC0832作为D/A转换器。

功能按键使用单片机的3个端口。

使能输出频率有较好的稳定性,元器件比较常见,价格低廉,电路设计方便。

关键字:单片机D/A转换器低频信号源AbstractSignal generator is to produce the required parameters of electrical test instruments of signals. Waveforms can be divided into sinusoidal signal function signals, pulse and random signal generator and other four categories. Signal generator, also known as the signal source or oscillator. In production and has been widely used in the fields of science and technology. Various waveforms can produce trigonometric equations. Can produce a variety of wave, triangle wave, sawtooth wave, sine wave, and so on. The design options are used as controller, interrupt table look-up method plete the output waveform data, and d/a converters output signals provided. Square wave output directly from the port. bined with functional requirements, using as controller, DAC0832 is used as a d/a converter. Function key use the 3 ports. Enabled output frequency has a better stability, more mon ponents and low price, and circuit design. Keywords: monolithic d/a converter for low frequency signal generator目录1.2.14.5.2 正弦波查找表5 调试及性能分析小结参考文献 (14)附录 (15)1 任务描述1.1设计主要内容及要求基于单片机的简易低频信号源的设计。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于LMX41的低相噪频率源的设计

频率合成器是现代通信系统中一个重要组成部分,在数字通信、卫星通信、遥测遥控、雷达、导航等领域有着广泛应用。

文中介绍了锁相频率合成技术的基本原理和性能指标,给出了一种利用LMX2541实现频率合成器的硬件结构和实现方法,并对其主要指标进行了测试,测试结果显示其具有低相位噪声、低杂散和结构简单的特点,满足了设计指标的要求。

标签:频率合成器锁相环相位噪声LMX2541

Abstract :Frequency synthesizer is the key part of modem communications systems ,which are widely used in digital communications,satellite communications,TT&C,radar,navigation and other fields. The basic principle and performance standard of PLL frequency synthesizer are introduced in this paper.A hardware structure for realizing frequency synthesizer based on LMX2541 and implementation methords are given. From the measured results,we can see that the frequency synthesizer has characteristics of low phase noise,low spurious and simple stucture,which satisfy the design requirments of the index.

Keywords:frequency synthesizer;PLL;phase noise;LMX2541

一、引言

频率源可在雷达中用作本振信号或作为数据处理的采样时钟等,在雷达领域有着重要的作用。

相位噪声和杂散是衡量频率源的两个重要指标[1]。

频率源的设计主要有三种技术:直接频率合成技术、直接数字频率合成技术和锁相式频率合成技术。

本文基于LMX2541锁相环芯片设计出一种低相噪低杂散的频率源,实验结果表明该频率源的设计取得了理想的效果。

LMX2541芯片[2]由NS推出的一款超低噪、高度集成的频率合成器。

频率源指标:输出2600MHz;输出功率大于15dBm;杂散抑制不小于-60dBc;相噪小于-100dBc/Hz@10KHz,-120dBc/Hz@1MHz。

锁相环频率合成技术是一种相位负反馈技术,通过比较输入基准频率与经过分频器N的输出频率,通过与两输入信号相位差成正比的误差电压控制压控振荡器的输出频率,使其经过分频器N后的频率与输入的频率与输入基准频率相等。

一个基本的锁相环主要由鉴相器、环路滤波器和压控振荡器三个基本部分组成。

LMX2541芯片有12个寄存器,包含有多个分频系数寄存器、锁定检测寄存器和电荷泵寄存器等。

数据写入采用的是SPI总线形式,时序图如图1所示。

CLK为来自单片机Attiny13的时钟信号,在CLK的第一个上升沿时,DATA 为高电平开始写入,LE为写使能,低电平有效。

DATA先输入数据,最后再输入4位寄存器值,在每一个时钟的上升沿,数据被送入芯片,高位数据先进。

二、锁相式频率合成器电路设计

基于LMX2541芯片的频率源技术方案设计如下图2所示。

2.控制电路设计

对芯片的CLK、DATA、LE控制时,选用Attiny13芯片,其为A VR RISC 结构的低功耗8位CMOS微控制器。

VCC为数字电路的电源,供电+3.3V;端口B为6位双向I/O口,有可编程的内部上拉电阻。

PB3、PB4、PB0以及PB1分别接LMX2541芯片的CLK、DATA、LE以及Ftest/LD管脚;RESET是复位输入引脚,持续时间超过最小门限时间的低电平将引起系统复位。

三、频率合成器指标测试

频率合成器测试指标包括相位噪声与输出功率,在测试电路中,选用Agilent-E4447A频谱仪,频率范围为3Hz~42.98GHz,采用频谱仪的对数曲线功能,用其测量输出信号的输出功率以及在10KHz与1MHz频偏下的相位噪声。

频率源输出2600MHz,功率为16.3dBm,10KHz处相噪为-109dBc/Hz,1MHz 处相噪为-132dBc/Hz,输出功率及相位噪声频谱图如下图3所示。

四、实验结果与分析

由测量结果可以看出无论是在10KHz处还是在1MHz处,频率源输出功率与相位噪声均满足系统指标要求。

参考文献

[1]潘玉剑,张晓发,袁乃昌.基于HMC830的低相噪低杂.散频率源的设计[J]. 电子设计,2011,10(6):180-183.

[2]LMX2541,Datasheet. Ultra-Low Noise PLL Frequency Synthesizer With integrated VCO.National Semiconductor.

作者介绍:尚善学,男,(1988-),山东日照人,燕山大学,电子与通信工程,工学硕士,助理工程师。

赵羽,男,(1986-),陕西咸阳人,西安电子科技大学,电子信息工程专业,本科,助理工程师。