NIOS II Core Board

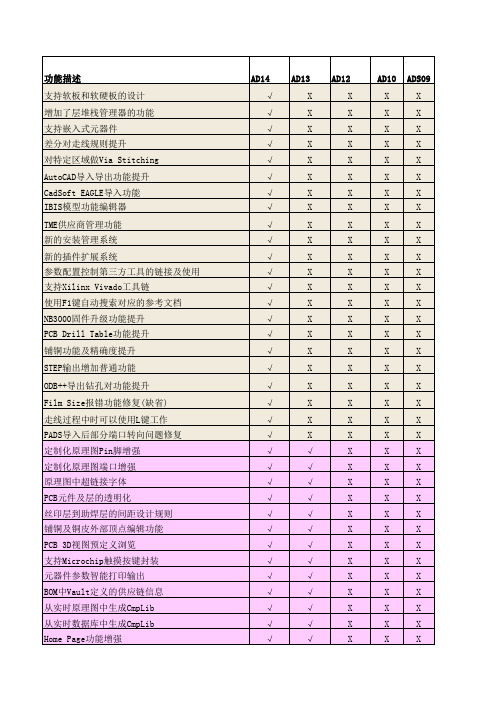

AD14版本对比

√ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √

√ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √

√ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √

√ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √

√ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √

√ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √ √

ADS09 X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X

按器件位置定义原理图位号 多边形覆盖区 原理图设计中字体编辑功能增强 TSK3000支持断点调试功能 Wishbone SPI核心增强 从VHDL文件中创建原理图符号 将元器件参数添加在生成的PDF中的可选项 将3D Body转化为STEP模型 ActiveBOM 实时钻孔图表 PCB设计视图 用表达式定义输出文件名 交互式布线长度计算修复 排孔阵列功能增强 基于Vault的仿真模型 器件定义中添加仿真模型 从实时原理图库中生成仿真模型 从数据库中生成仿真模型 器件库(CmpLib)功能增强 项管理器功能增强 从Vault中批量下载项 定义过期Vault项功能 项目生命周期和版本的重命名 定义Vault中项的初始版本ID Vault搜索功能增强 从Vault面板中直接拖置元器件 Altium Vault Server管理员功能增强 Altium Vault Server集成的供应链管理 Altium Vault Server从内部供应链中设置ODBC Altium Vault Server许可文件可视状态信息 Altium Vault Server登陆用户可视状态信息 SEGGER J-Link 调试器的支持 http client/server 以及JSON服务的支持 规则批量删除 Xilinx ISE v14.3, Lattice Diamond 2.0.1, Altera QuartusII 以及 NiosII version 12.0 Outputjob输出IDF格式的文件 交互式选择中的自动缩放 加强的PCB连接线的颜色控制 subversion 1.7 版本的支持 Air Gap 宽度设置的支持 Vault对于代理服务器的支持

QuartusII1

(1)在QuartusII界面中选择File—Convert Programming Files ,打开Convert Programming Files 对话框,参照图3.50,从Programming File type 下拉列表框中选择编程文件的类型为JTAJ indirect Configuration file。

(2)在Configuration device下拉列表框图中根据实际设计选择被变成目标器件,对于MagicSOPC选择EPCS16。

(3)在file name 文本框中,输入或浏览选择JIC文件名和存放路径。

(4)在Input files to convert栏中单击Flash loader,使其高亮。

(5)单击“Add Device...”打开select Device对话框,如图3.51所示。

(6)参照图3.51选择器件类型和型号。

对于MagicSOPC,器件类型请选择CycloneII。

(7)对于MagicSOPC,器件型号请选择EP2C35F672C8,然后单击OK,关闭选择其对话框。

(8)参照图3.52,在Input files to convert栏中单击SOF Data,使其高亮。

(9)单击打开select input file对话框。

(10)对话框中选择要进行转换的SOF文件,然后单击“打开”按钮。

(11)选择完输入文件后,会在SOF Data下面出现要被转换的输入SOF文件,如图3.53所示。

单击SOF Data下的输入SOF文件使其高亮。

(12)参照图3.53,单击打开SOF File Properties(SOF文件属性)对话框。

(13)选择Compression,然后单击OK,由于MagicSOPC采用EPCS16来配置EP2C53,所以这里必须选择压缩。

(14)在Convert Programming Files对话框中单击OK,开始进行转换。

通过上述步骤,即可完成SOF文件到JIC文件转换。

sopc开发环境的使用

• 设置好软件运行 的硬件环境属性后, 便可进行编译、链 接和调试、运行程 •对用户程序进行 序。 编译,生成可执 行文件*.elf。 • 接 下 来 在 IDE 的 指令集仿真器(ISS) 上仿真软件和运行/ 调试软件。 • 在目标板上反 复调试软件。

下载配置文件到 FPGA器件

在目标板上 下载可执行 软件到 Nios II系统

SOPC开发流程和开发工具

软件开发

软件开发使用Nios II IDE,它是一个基于Eclipse IDE架构的集成 开发环境,它包括: GNU开发工具(标准GCC编译器,连接器,汇编器和 makefile工具等); 基于GDB的调试器,包括软件仿真和硬件调试; 提供用户一个硬件抽象层HAL; 提供嵌入式操作系统MicroC/OS-II和LwTCP/IP协议栈的支持; 提供帮助用户快速入门的软件模板; 提供Flash下载支持(Flash Progrmmer 和QuartusII Programmer)

软 件 开 发 也 可 以 在 SOPC Builder 生成系统模块后立 即进行!与传统软件开发类 似,唯一不同在于系统是自 己定制的,所受局限小!

NiosII内核 &标准外设

打开SOPC Builder 定义和生成系统

定制指令&定 制外设逻辑

自定义的 功能模块

集成SOPC生 成的系统到 Quartus II工程

打开SOPC Builder 定义和生成系统

定制指令&定 制外设逻辑

自定义的 功能模块

集成SOPC生 成的系统到 Quartus II工程

Altera的 LPM模块

硬件抽象层 (HAL)&外设 驱动程序

使用Nios II IDE开发软件

基于SOPC+的MP3+编解码器的设计与实现

分类号密级UDC学 位 论 文基于SOPC的MP3编解码器的设计与实现作者姓名:尚淼洪指导教师:李晶皎教授东北大学信息科学与工程学院申请学位级别:硕士学科类别:工学学科专业名称:计算机软件与理论论文提交日期:2008年6月论文答辩日期:2008年6月学位授予日期:2008年7月答辩委员会主席:高福祥评阅人:东北大学2008年6月A Thesis for the Degree of Master in Computer Software and TheoryDesign and Implementation of MP3 codec basedon SOPCby Shang MiaohongSupervisor: Professor Li JingjiaoNortheastern UniversityJune 2008独创性声明本人声明,所呈交的学位论文是在导师的指导下完成的。

论文中取得的研究成果除加以标注和致谢的地方外,不包含其他人己经发表或撰写过的研究成果,也不包括本人为获得其他学位而使用过的材料。

与我一同工作的同志对本研究所做的任何贡献均己在论文中作了明确的说明并表示谢意。

学位论文作者签名:日期:学位论文版权使用授权书本学位论文作者和指导教师完全了解东北大学有关保留、使用学位论文的规定:即学校有权保留并向国家有关部门或机构送交论文的复印件和磁盘,允许论文被查阅和借阅。

本人同意东北大学可以将学位论文的全部或部分内容编入有关数据库进行检索、交流。

作者和导师同意网上交流的时间为作者获得学位后:半年□一年□一年半□两年□学位论文作者签名:导师签名:签字日期:签字日期:基于SOPC的MP3编解码器的设计与实现摘 要目前国内外针对MP3编解码器的研究主要着重基于单片机的音频编解码,这样的系统有局限性,主要是扩展功能差,功耗大,很多主流功能都不兼容。

在应用需求的牵引和IT技术的推动下,基于SOPC系统的开发在音频编解码处理领域的应用也日益增多。

DE2-70 Control Panel提示“Fail to query board name”错误

在连接LTM的时候需要把一幅bmp位图加载到flash中,但是使用DE2-70 Control Panel确出现"Fail to query board name",问题原因提示没有下载sof文件,于是按照提示在下载DE2_70_Control_Panel.sof,然后再连接但是还是提示,说缺少了nios2的elf 文件,于是在网上help了下,发现altera论坛里有人解决了这个问题。

实际上真正有用的就是第四点了,首先打开nios2 shell command (在C:\altera\90\nios2eds目录下)打开后他显示默认目录在C:\altera\90\nios2eds\examples下,于是把nios2的elf文件DE2_70_Control_Panel_ssram.elf拷贝到此目录下后,进行nios2下载工作,也就是第四点了,在显示ok后就没问题了,可以打开Control Panel进行相应的操作了。

DE2-70 Control Panel "Fail to query board name"I have the same problem with quartusII 7.2..Quote:1) load the .sof manually using programmer tool.2) use nios2 shell command :"H:\altera\90\nios2eds\Nios II Command Shell.bat"3) in this console window, go to the Control_panel directory (the path hase the form /cygdrive/<niosdrive/.....4) execute : nios2-download DE2_70_Control_Panel_ssram.elf -cUSB-Blaster[USB-0] -r -g4 remark) I can put this line in file (example toto) and after call "bash toto" in the console.补充:在遇到问题时请事先检查,是否为系统中的安全软件造成的原因,比如360,以及一些防火墙软件。

Cyclone II EP2C5(8)启蒙板说明书V2.2

Cyclone II EP2C5/8 启蒙板说明书 Cyclone II EP2C5/8 Start Board User Manual Version 2.1 Copyright © 线路人生|Circuitry Life 线路人生|Circuitry Life 版本修订记录 Version 1.0 2.0 2.1 2.2 Author zhiyuh zhiyuh zhiyuh Zhiyuh Data 2009‐6‐3 2009‐6‐12 2009‐07‐09 2009‐08‐22 Cyclone II EP2C5/8 Start Board Description First draft. 根据 Rev.B 电路图修改相关内容,并补充各电路 与 FPGA 之间的引脚连接定义。

增加兼容设计方面的解释内容,完善部分 BOM。

修改首页图片,BOM 增加备注。

备注:关于修订的说明 ~ 2 ~ 线路人生|Circuitry Life Cyclone II EP2C5/8 Start Board 目录 1. 模块介绍 ........................................................................................................................... 4 1.1 1.2 模块主要功能 ............................................................................................................ 4 模块适用范围 ............................................................................................................ 4 2. 包装清单 ........................................................................................................................... 4 2.1 2.2 模块包装清单 ............................................................................................................ 4 安装说明 .................................................................................................................... 4 3. 硬件说明 ........................................................................................................................... 5 3.1 电路说明 .................................................................................................................... 5 FPGA 芯片及主要外围电路............................................................................... 5 电源电路 ............................................................................................................ 7 存储器电路 ........................................................................................................ 8 板载 LED 测试电路 .......................................................................................... 13 IO、控制线和总线引出接口 .......................................................................... 14 . 硬件的其它说明 .............................................................................................. 15 3.1.1. 3.1.2. 3.1.3. 3.1.4. 3.1.5. 3.1.6. 3.2 3.3 4. 5. 6. 7. 器件清单(BOM) ................................................................................................. 15 . 电路板相关尺寸参数 .............................................................................................. 17 使用注意事项 ................................................................................................................. 17 技术支持 ......................................................................................................................... 18 硬件原理图 ..................................................................................................................... 18 其它备注 ......................................................................................................................... 18 ~ 3 ~ 线路人生|Circuitry Life Cyclone II EP2C5/8 Start Board 1. 模块介绍 1.1 模块主要功能 数字系统和 SOPC 设计在广大学生和爱好者中已经形成了一定的学习氛围和规模,但市 场上的开发板和学习板良莠不齐,为此线路人生|Circuitry Life 特设计了本模块,中文名为 “Cyclone II EP2C5/8 启蒙板” ,英文名为“Cyclone II EP2C5/8 Start Board” 。

Altium Designe各版本功能对比

功能分类功能描述AD15AD14AD13AD12AD10ADS09ADW09ADS08AD6.999SE

FRONT-END 前端设计装配变量和板级元件标号的图形编辑功能üüüüüü

SIMetrix/SIMPLIS的信号仿真引擎的支持üüüüüüüüü信号完整性示例增强üüüüüüüüüIBIS模型功能编辑器üü

PCB xSignals高速信号对定义ü

顶层底层焊盘可自定义阻焊外扩ü

优化铺铜的处理方式ü

支持放置OLE物件(Excel,word)ü

支持矩形孔的放置ü

2D/3D的视角分离ü

重组并优化了导入导出选项ü

支持软板和软硬板的设计üü增加了层堆栈管理器的功能üü支持嵌入式元器件üü差分对走线规则提升üü对特定区域做Via StitchingüüAutoCAD导入导出功能提升üüCadSoft EAGLE导入功能üüPCB Drill Table功能提升üü。

EDA(电子设计自动化)教程

➢ Used to Ensure Hardware/Software Version

Synchronization

➢ Simple 2 read-only register peripheral containing

hardware ID tags.

• Register 1 contains random number

• Register 2 contains time and date when system was

generated in SOPC Builder

➢ Can be checked at runtime to ensure that the software to

be downloaded matches the hardware image

▪ Support for DDR/DDR2 in SOPC Builder GUI ➢ With burst adapter • Sequential master to interleaved slave enhancement ➢ Separate READ/Write duplex slaves • Automatically matches address of read/write slaves • Arbitration logic connects read/write masters to both slaves

7

7.1 Nios Ⅱ嵌入式处理器简介

▪ Nios II提供3种不同的内核,以满足系统对不同性能和成本的需求。

表7-2 Nios Ⅱ系列处理器的成员

最高性能的优化

平衡性能和尺寸

最小逻辑占用的优化

8

7.1 Nios Ⅱ嵌入式处理器简介

NIOS性能

175

Cyclone III LS (3)

EP3CLS70F484C7

135

100

140

Cyclone III (3)

EP3C40F324C6

175

145

215

Cyclone II

EP2C20F484C6

140

110

195

Cyclone

EP1C20F400C6

135

120

175

Arria® II GX

■ Timer

f The MIPS reports were obtained using the MIPS* (*Dhrystones 2.1 benchmark). You can download the Dhrystones 2.1 benchmark software from the Nios II Embedded Processor Design Examples page on the Altera website. For more information about the Dhrystones 2.1 benchmark software, refer to the readme.txt file which is included in the Dhrystones 2.1 benchmark design example.

Table 2. MIPS for Nios II Processor System (Note 1) (Part 1 of 2)

Device Family

Device Used

Nios II/f

Stratix V (1)

5SGXMA3H2F35C2

283

功能集概述

P P

Altium Designer提供多种许可证的选择,让用户可以更方便的按需选择.无论用户是一个大型设计团队的一员,还是负责咨询的工程师,Altium Designer都能满足创新,和让工程师保持竞争力的一切需 要,并用全新的方法进行产品的设计. Custom Board Implementation让用户从概念到制造,在一个单一的环境里跨越硬件,软件和可编程器件(FPGA)完成设计.如果需要从事基础的设计,用户可以选择Custom Board Front-End Design.软 设计1许可证同时提供Altium的NanoBoard以支持即选即用的可编程硬件设计方案.

Altium Designer 功 能 集 概 述

Soft Design*

Custom Board Front-End Design

Custom Board Implementation

DXP平台 原理图 - 浏览器 PCB - 浏览器 CAM 文件 - 浏览器 原理图 - Soft Design 编辑 仿真 - VHDL NanoBoard 支持 FPGA 设计 FPGA 处理器内核 处理器内核嵌入式工具 FPGA可编程仪器 JTAG软器件支持 JTAG硬件器件支持 IP核心设计的复用 导入/导出 原理图 - 编辑

P P P P P P P P P P P P P P

P P P P P P P P P P P P P P P P

P P P P P P P P P P P P P P P P

4682CN FSS 0709 S09 02 Copyright 2010 Altium Limited

全系列软件开发工具-支持32-bit处理器的C编译器/组装器/源代码调试器/仿真器. 即插即用的软件平台搭建器支持硬件更容易 可用于远程接入的预综合FPGA即用仪器,包括定制仪器,终端模拟器,数字I/O,交点转化,逻辑分析仪,频率发生器,计数器和 应用控制面板 实时连接到软器件,如虚拟仪器和运行在 FPGA内的处理器 对任意 JTAG 器件进行交互式引脚状态监控 支持对第三方FPGA的IP核心和开发以及对IP库的复用 支持对OrCAD,Allegro,PADS,DxDesigner,Cadstar,P-CAD, CircuitMaker,Protel以及更多的软件生成的设计和库数据的导入和导出 所有原理图文档和库文件编辑功能,网表生成