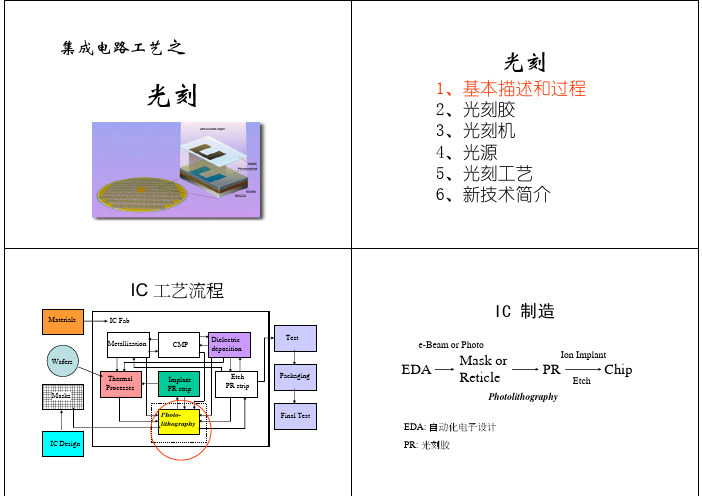

硅集成电路工艺——光刻与刻蚀

集成电路工艺-光刻

光刻胶的对比度光刻胶区分掩模上亮区和暗区的能力。

(光刻胶上从曝光区到非曝光区过渡的陡度)焦深(DOF)Chemical Clean RinseDrySpindlePR dispenser nozzleTo vacuum pumpSpindleTo vacuum pumpPR dispenser nozzlePR suck back旋转涂布SpindleTo vacuum PR dispenser nozzlePR suck back 旋转涂布SpindleTo vacuum PR dispenser nozzlePR suck backSpindleTo vacuum pumpPR dispenser nozzlePR suck back SpindleTo vacuum pumpPR dispenser nozzlePR suck back旋转涂布SpindleTo vacuum PR dispenser nozzlePR suck back 旋转涂布SpindleTo vacuum PR dispenser nozzlePR suck back旋转涂布PR dispenser PR suck back nozzleWaferChuck Spindle To vacuum pump旋转涂布PR dispenser PR suck back nozzleWaferChuck Spindle To vacuum pump旋转涂布PR dispenser PR suck back nozzleWaferChuck Spindle To vacuum pump去边 (EBR)• 光刻胶扩散到硅片的边缘和背面 • 在机械搬送过程中光刻胶可能回剥落成为微粒 • 正面和背面去边 EBR • 正面光学去边 EBR去边(EBR)• 光刻胶扩散 到硅片的边 缘和背面• 在机械搬送 过程中光刻 胶可能回剥 落成为微粒• 正面和背面 去边 EBR• 正面光学去 边 EBRSolventEBR: Edge Bead RemovalWaferChuck Spindle To vacuum pump匀胶后烘前的硅片WaferChuck SpindleTo vacuum pump去边SolventWaferChuck SpindleTo vacuum pump光学去边Photoresist WaferChuck Spindle• 对准和曝光后 • 硅片边缘曝光 (WEE) • 显影使曝光过的光刻胶溶解显影Edge PR removedPatterned photoresist WaferChuck SpindleTo vacuum pump烘烤系统Wafer HeaterVacuum Hot plate热板Heated N 2Wafers Heater Convection oven对流式烘箱 红外线烘箱MW Source PhotoresistWaferChuck VacuumMicrowave oven微波烘箱匀胶后烘• 使光刻胶中的大部分溶剂蒸发。

08工艺-刻蚀

Si

氮化硅和垫层氧化剥离

(c)

(e)

RCA 清洗

• 1960年, 年 Kern and Puotinen 在RCA开发 • IC fabs中最常用的清洗工艺 • SC-1溶液:NH4OH:H2O2:H2O按1:1:5到1:2:7 的比例配制并且温度在7 70 - 80 °C,用于去除 颗粒沾污. • SC-2 SC 2 溶液: 溶液 HCl:H2O2:H2O 按 1:1:6 到 1:2:8 比 例配制并且温度在 70-80 ° C ,用于去除无机 沾污。 沾污 • 去离子水冲洗 • HF 浸洗或 HF 蒸汽腐蚀去除自然氧化层

– – – – 硅片的清洗 无图形的薄膜去除 如氮化硅和钛的去除 无图形的薄膜去除,如氮化硅和钛的去除。 测试硅片的薄膜去除和清洗。 应用于 CVD膜质量的控制 (缓冲氧化层刻蚀 剂或BOE)

旋转甩干

SiO2的湿法刻蚀

• 氢氟酸溶液 (HF),极高的选择比。 • 通常用缓冲剂或去离子水稀释减少刻 蚀速率

垫层氧化 氮化硅 P-型衬底 垫层氧化,氮化硅淀积和图案形成

Si Si 生长SiO2/SiN 刻蚀 SiN/SiO2/Si

氮化硅 p+ P-型衬底

SiO2 p+

+ p 隔离掺杂

(a)

氧化 + CVD USG

(b)

去掉 SiN/SiO2 USG

LOCOS 局部氧化 SiO2 p+ P-型衬底 p+ 鸟嘴

硅化物退火

湿法去除钛

湿法刻蚀优缺点

• 高选择比 • 相对便宜的设备 • 批处理,高产出 批处理 高产出 • • • • 各向同性的形貌 不能形成3微米以下的图形 化学剂用量大 化学剂的危害性

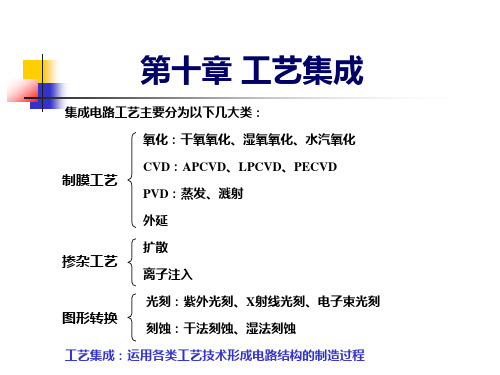

硅集成电路工艺基础10

4、自对准结构和接触

自对准技术是利用单一掩模版在硅片上形成多层自对准结构的技术, 不仅工艺简化,且消除了多块掩模版之间的对准容差。随着器件特征 尺寸的不断缩小,自对准技术已经成为一种常用的工艺方法。 最早发展起来和最常用的自对准技术是源漏的自对准注入(也称为 硅栅自对准),即在多晶硅栅的掩蔽下自对准地进行源漏区的杂质注 入,并同时完成多晶硅栅的杂质注入。 自对准的多晶硅栅避免了采用铝栅时多次光刻引起的栅极错位。

法在上面淀积一层SiO2。 各向异性腐蚀CVD SiO2层以后,只剩下侧墙部分。 在SiO2侧墙保护下腐蚀Si3N4和SiO2层直至露出硅,然后 再去除CVD SiO2侧墙 ,形成由Si3N4和SiO2层包围的平台。 进行沟道阻挡层注入和场SiO2层生长。 最后去除Si3N4和缓冲SiO2层。

10.1、集成电路中的隔离

10.1.1 MOS集成电路中的隔离 自隔离:MOSFET源、漏极的导电类型相同,并与衬底导电类型相反,

所以MOSFET本身就被pn结隔离,即自隔离(self-isolated)。 源漏电流只有在导电沟道形成后才能形成,只要相邻晶体管之间不存在 导电沟道,相邻晶体管间便不会存在显著的电流。 只要维持源-衬底pn结和漏-衬底pn结的反偏,MOSFET便能维持自隔离。 MOS集成电路的晶体管之间不需要pn结隔离,可大大提高集成度。

达到在硅片上选择性保留厚氧化层的目的。

10.1.2 双极集成电路中的隔离

在传统的双极集成电路中的隔离主要是采用结隔离,结隔离已经成为 双极集成电路的标准埋收集极工艺的重要组成部分。

在外延层上淀积SiO2并进行光刻和刻蚀,去除光刻胶露出隔离区上的Si, 随后进行硼扩散,形成p型隔离区。在硅衬底上形成了许多由反偏p-n结隔 离开的孤立的外延岛。 由于需要扩透整个n型层,因此硼的隔离扩散是双极工艺中最费时的。

半导体工艺原理----刻蚀工艺(2013.5.13)(贵州大学)

⑦ 掩模版透光区存在灰尘或黑斑,曝光时局部胶膜末曝光,显影时 被溶解,腐蚀后产生 针孔。

第三十九页,共41页。

针孔

① 氧化硅薄膜表面有外来颗粒,使得涂胶时胶膜与基片表面未充分 沾润,留有未覆盖的小区域,腐蚀时产生针孔。

② 光刻胶中含有固体颗粒,影响曝光效果,显影时剥落,腐蚀时产生 针孔。

但Si-N键的键结强度介于Si-O和Si- Si之间,因此,刻蚀速度

以SiO2为最快, Si3N4其次,多晶硅最慢。 如以CHF3的等离子体作为刻蚀气体, SiO2/Si的选择性在10

以上,Si3N4/Si的选择性在3-5, SiO2/ Si3N4的选择性在

2-4 。

第三十二页,共41页。

(3)多晶硅化物(Polysilicon)的刻蚀

金属,可以采用CF4、SF6、Cl2、HCl2等都可以用来 作为硅化金属的RIE的反应气体。

对多晶硅的刻蚀采用氟化物将导致等方向性的刻蚀,而 Polycide 的刻蚀必须采用各向异性,因此采用氯化物

较好,有 Si, HCL2, SiCl4等。

第三十四页,共41页。

(4)铝及铝合金的刻蚀

铝和铝合金是现在半导体制造过程中普遍采用的导体材 料,铝合金主要采用铝-硅铜合金(防止尖刺和电迁 移),来作为半导体元件的导电层材料。

性离子对衬底的物理轰击和化学反应双重作用刻蚀。具有溅射刻 蚀和等离子刻蚀两者的优点,同时兼有各向异性和选择性好的优 点。目前,RIE已成为VLSI工艺中应用最广泛的主流刻蚀技术。

第三十页,共41页。

(1)二氧化硅的刻蚀

采用的气体为C2 4F SiF4 2O SiO2 2CF2 SiF4 2CO

增加等离子体中的氧含量,将导致Si/SiO2的选择性变差。增

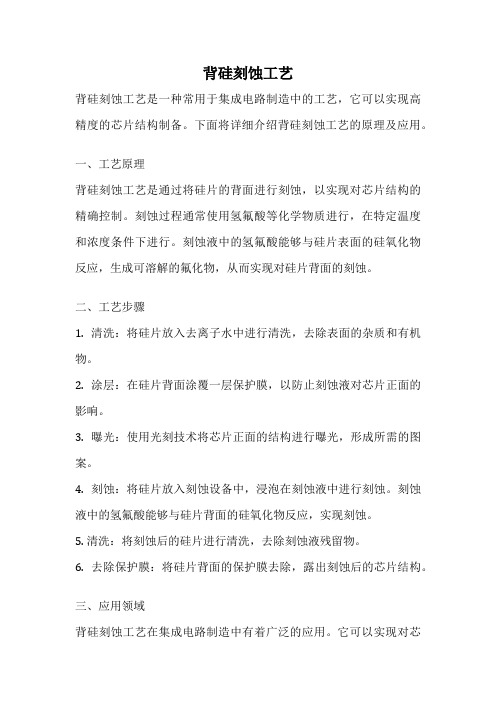

背硅刻蚀工艺

背硅刻蚀工艺

背硅刻蚀工艺是一种常用于集成电路制造中的工艺,它可以实现高精度的芯片结构制备。

下面将详细介绍背硅刻蚀工艺的原理及应用。

一、工艺原理

背硅刻蚀工艺是通过将硅片的背面进行刻蚀,以实现对芯片结构的精确控制。

刻蚀过程通常使用氢氟酸等化学物质进行,在特定温度和浓度条件下进行。

刻蚀液中的氢氟酸能够与硅片表面的硅氧化物反应,生成可溶解的氟化物,从而实现对硅片背面的刻蚀。

二、工艺步骤

1. 清洗:将硅片放入去离子水中进行清洗,去除表面的杂质和有机物。

2. 涂层:在硅片背面涂覆一层保护膜,以防止刻蚀液对芯片正面的影响。

3. 曝光:使用光刻技术将芯片正面的结构进行曝光,形成所需的图案。

4. 刻蚀:将硅片放入刻蚀设备中,浸泡在刻蚀液中进行刻蚀。

刻蚀液中的氢氟酸能够与硅片背面的硅氧化物反应,实现刻蚀。

5. 清洗:将刻蚀后的硅片进行清洗,去除刻蚀液残留物。

6. 去除保护膜:将硅片背面的保护膜去除,露出刻蚀后的芯片结构。

三、应用领域

背硅刻蚀工艺在集成电路制造中有着广泛的应用。

它可以实现对芯

片背面的结构制备,例如背面电极、背面通孔等。

同时,背硅刻蚀工艺还可用于形成背面反射层,提高光电器件的效率。

此外,背硅刻蚀工艺还可以用于刻蚀硅片背面的缺陷,提高硅片的质量。

背硅刻蚀工艺是一种重要的集成电路制造工艺,它可以实现对芯片背面结构的精确制备。

在当前的半导体技术发展中,背硅刻蚀工艺的应用将会越来越广泛。

通过不断优化工艺参数和设备性能,背硅刻蚀工艺将能够实现更高精度的芯片制备,推动集成电路技术的发展。

第三章-光刻与刻蚀

38

nH2O 1.44

涂胶工艺步骤-显影(Development)

显影液溶解部分光刻胶: 正胶显影液通常使用弱碱性的溶剂; 最常用的是四甲基氢铵(TMAH); 将掩膜上的图形转移到光刻胶上; 三个基本步骤:显影-清洗-干燥;

在光刻版上进行图形修正, 来补偿衍射带来的光刻图 形变形。

32

光学临近修正

33

分辨率增强技术

34

表面反射的影响

避免表面高度差; 表面平整化;

35

表面反射的影响

36

表面反射的影响

光刻胶下加减反膜

37

浸没式曝光

增加数值孔径:

DNA n sin

R k1 DNA

=193 nm, k1=0.3:

光刻胶对可见光不敏感,对紫外光敏感;

9

光刻胶/抗蚀剂(Photoresist)

光刻胶的类型: 正胶:曝光区化合物吸收光子,聚合物分裂为短链,易于溶于显 影液中 --曝光区易溶解 负胶:曝光区感光化合物吸收光能而使聚合物分子发生交联,难 溶于显影液中 --曝光区不溶解

区别: 正胶:分辨率好,易去除,成本高; 负胶:黏附性好,聚合区/非聚合区可溶性差别大,分辨率低,去除难;

54

刻蚀

Etching

《大规模集成电路制造工艺》

55

图形的形成I

56

图形的形成II

57

描述刻蚀工艺参数

刻蚀速率:

刻蚀前厚度-刻蚀后厚度 刻蚀速率 刻蚀时间

500nm通过干氧方法生长的SiO2,在BOE溶液中刻蚀30s, 剩下厚度为450nm:

第八章光刻与刻蚀工艺

8.1 光刻工艺流程

2.涂胶Spin Coating ①对涂胶的要求:粘附良好,均匀,薄厚适当 胶膜太薄-针孔多,抗蚀性差; 胶膜太厚-分辨率低(分辨率是膜厚的5-8倍) ②涂胶方法:浸涂,喷涂,旋涂√

Photoresist Spin Coater

EBR: Edge bead removal边缘修复

8.6.6 投影式曝光

利用光学系统,将光刻版的图形投影在硅片上。

8.6.6 投影式曝光

优点:光刻版不受损伤, 对准精度高。 缺点:光学系统复杂, 对物镜成像要求高。 用于3μm以下光刻。

分步重复投影光刻机--Stepper

采用折射式光学系统和4X~5X的缩小透镜。 光刻版: 4X~5X; 曝光场:一次曝光只有硅片的一部分; 采用了分步对准聚焦技术。

h 2 2m E

a. E给定:m↑→ΔL↓→R↑,即R离子 > R电子 b. m给定:E↑→ΔL↓→R↑

8.3 光刻胶的 基本属性

1)光刻胶类型:正胶和负胶 ①正胶:显影时,感光部分 溶解,未感光部分不溶解; ②负胶:显影时,感光部分 不溶解,不感光部分溶解。

正胶(重氮萘醌)的光分解机理

负胶(聚乙烯醇肉桂酸脂)的光聚合机理

8.1 光刻工艺流程

③影响显影效果的主要因素: ⅰ)曝光时间; ⅱ)前烘的温度与时间; ⅲ)胶膜的厚度; ⅳ)显影液的浓度; ⅴ)显影液的温度; ④显影时间适当 t太短:可能留下光刻胶薄层→阻挡腐蚀SiO2(金属) →氧化层“小岛”。 t太长:光刻胶软化、膨胀、钻溶、浮胶 →图形边缘破坏。

第八章 光刻与刻蚀工艺

掩模版

掩膜版的质量要求 若每块掩膜版上图形成品率=90%,则 6块光刻版,其管芯图形成品率=(90%)6=53%; 10块光刻版,其管芯图形成品率=(90%)10=35%; 15块光刻版,其管芯图形成品率=(90%)15=21%; 最后的管芯成品率当然比其图形成品率还要低。 掩膜版尺寸:①接触式和接近式曝光机:1∶1 ②分步重复投影光刻机(Stepper): 4∶1;5∶1;10∶1

十大步骤详解芯片光刻的流程!

十大步骤详解芯片光刻的流程!在集成电路的制造过程中,有一个重要的环节——光刻,正因为有了它,我们才能在微小的芯片上实现功能。

现代刻划技术可以追溯到190年以前,1822年法国人Nicephore niepce在各种材料光照实验以后,开始试图复制一种刻蚀在油纸上的印痕(图案),他将油纸放在一块玻璃片上,玻片上涂有溶解在植物油中的沥青。

经过2、3小时的日晒,透光部分的沥青明显变硬,而不透光部分沥青依然软并可被松香和植物油的混合液洗掉。

通过用强酸刻蚀玻璃板,Niepce在1827年制作了一个d’Amboise主教的雕板相的复制品。

Niepce的发明100多年后,即第二次世界大战期间才第一应用于制作印刷电路板,即在塑料板上制作铜线路。

到1961年光刻法被用于在Si上制作大量的微小晶体管,当时分辨率5um,如今除可见光光刻之外,更出现了X-ray和荷电粒子刻划等更高分辨率方法。

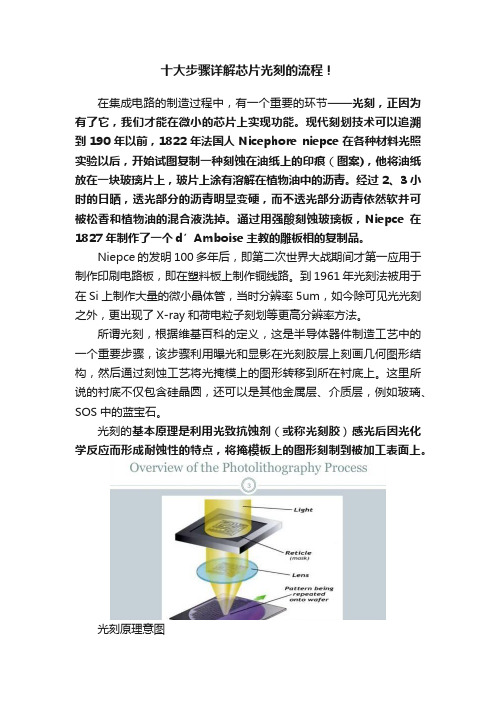

所谓光刻,根据维基百科的定义,这是半导体器件制造工艺中的一个重要步骤,该步骤利用曝光和显影在光刻胶层上刻画几何图形结构,然后通过刻蚀工艺将光掩模上的图形转移到所在衬底上。

这里所说的衬底不仅包含硅晶圆,还可以是其他金属层、介质层,例如玻璃、SOS中的蓝宝石。

光刻的基本原理是利用光致抗蚀剂(或称光刻胶)感光后因光化学反应而形成耐蚀性的特点,将掩模板上的图形刻制到被加工表面上。

光刻原理意图光刻不是一个简单的过程,它要经历很多步骤:光刻的工序下面我们来详细介绍一下光刻的工序:1.清洗硅片(Wafer Clean)清洗硅片的目的是去除污染物去除颗粒、减少针孔和其它缺陷,提高光刻胶黏附性基本步骤:化学清洗——漂洗——烘干。

硅片经过不同工序加工后,其表面已受到严重沾污,一般讲硅片表面沾污大致可分在三类:A. 有机杂质沾污:可通过有机试剂的溶解作用,结合超声波清洗技术来去除。

B. 颗粒沾污:运用物理的方法可采机械擦洗或超声波清洗技术来去除粒径≥ 0.4 μm颗粒,利用兆声波可去除≥ 0.2 μm颗粒。