Candence原理图库设计指南

原理图库设计

一,工具及库文件目录结构

目前公司EDA库是基于Cadence设计平台,Cadence提供Part Developer库开发工具供大家建原理图库使用。

Cadence 的元件库必具备如下文件目录结构为:

Library----------cell----------view(包括Sym_1,Entity,Chips,Part-table)

Sym_1:存放元件符号

Entity:存放元件端口的高层语言描述

Chips:存放元件的物理封装说明和属性

Part-table:存放元件的附加属性,用于构造企业特定部件

我们可以通过定义或修改上述几个文件的内容来创建和修改一个元件库,但通过以下几个步骤来创建元件库则更直观可靠一些。

二,原理图库建库参考标准

1,Q/ZX 04.104.1电路原理图设计规范-Cadence元器件原理图库建库要求

该标准规定了元件库的分类基本要求和划分规则,元器件原理图符号单元命名基本要求和规则,元器件原理图符号单元图形绘制基本要求和规则。

2,Q/ZX 04.125 EDA模块设计规范

此标准规定了全公司基于Cadence设计平台的EDA模块库的设计标准。

3,Q/ZX 73.1151 EDA库管理办法

此标准规定了公司统一的基于Cadence设计平台的元器件原理图库,封装库,仿真库和相应PCBA DFM评审辅助软件V ALOR的VPL库及相应的元器件资料的管理办法。从此标准中我们可以知道VPL建库流程,建库过程的各项职责以及VPL库的验证,维护等管理办法。4,Q/ZX 73.1161 EDA模块库管理办法

此标准规定了全公司基于Cadence设计平台的EDA模块库的管理办法。

三,原理图库建库step by step

第一步,建库准备

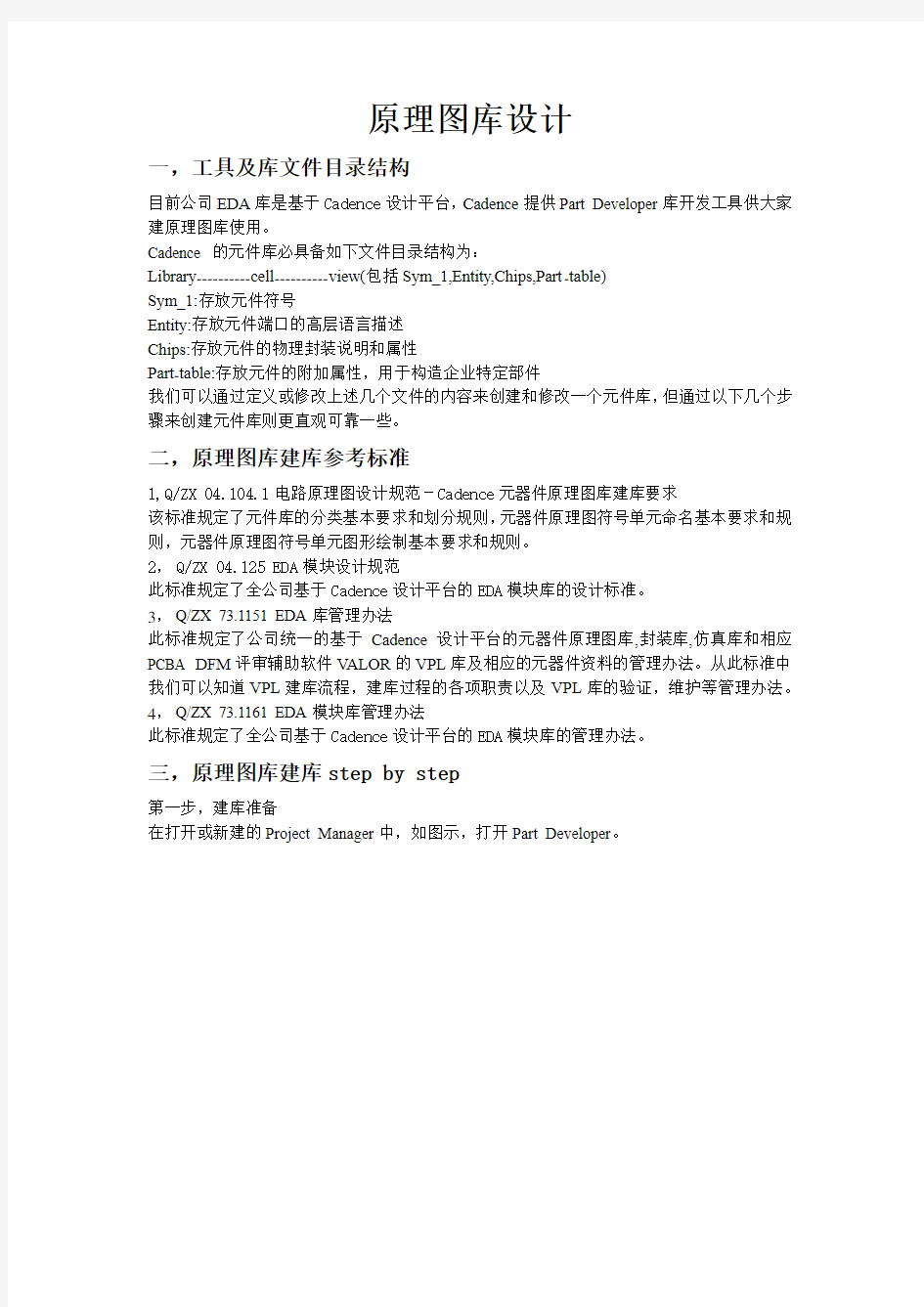

在打开或新建的Project Manager中,如图示,打开Part Developer。

然后出现如下画面,

点击new cell

开始建库

注意建库过程中的

各项运行提示出现

在此处

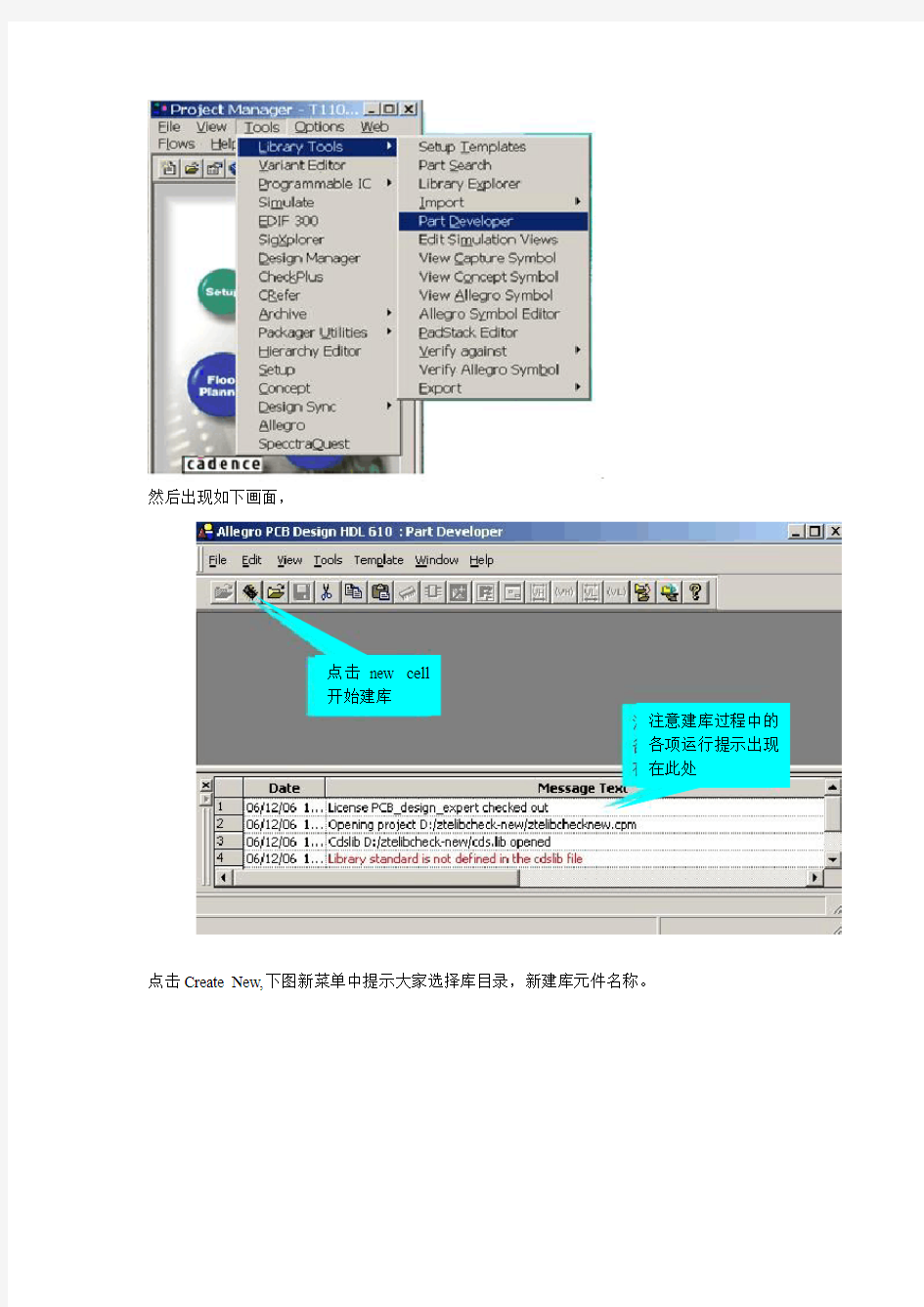

点击Create New,下图新菜单中提示大家选择库目录,新建库元件名称。

原理图库的建库界面上分别出现Packages,Symbols,Part Table Files三大主要部份,如下图。

第二步,加入封装相关信息

点击Packages,按右键,选择New,出现如下画面,在General界面中输入下图所示几个关键点。

在Package Pin这个界面上可以录入逻辑管脚,物理管脚,及两者的映射关系。选择pins->add ,进入逻辑管脚

定义界面Add Pin,如下图,按照元件手册决定管脚名称及逻辑方向,低电平有效的管脚名后加上“*”号,点击ADD即可加入新的管脚。

(注:不论是标量或矢量管脚,均可采用集体输入,如在Pin Names栏可输入A1-A8, 1C-16C) 选择Footprint->Add physical pins mannully,加入物理管脚,加物理管脚时注意一定要核对

封装库,保证物理管脚与封装库内的管脚号一致,不可凭想象。

逻辑管脚和物理管脚都输入后,利用map命令把两者按照元件资料映射正确,如下图。

当管脚数量大到图库超过A4纸时,需要把图库分成几个SYMBOL,这就要求在定义管脚映射的时候增加相应的Functions/Slots,如下图。

第三步,创建元件图形符号图

逻辑脚定义和与映射好后,在上图中选择Generate Symbols,即可生成相应的SYMBOL,如下图。

公司的原理图库设计规范要求,对单个SYMBOL的图库,要求在General Properties内加入$LOCATION 和PATH,

NEEDS NO SIZE, PART_NAME四个属性,如上图。对划分成多个SYMBOL的多管脚器件,还需要加入SPLIT_INST,CDS_LMAN_SPLIT_NUMBER,TEXT四个属性,如下图。

隐含电源和地管脚时还需要增加POWER_GROUP属性,但规范要求电源和地管脚必须展开在图形中,并且不能做成总线形式,在Symbol Pins界面中,利用Expand命令可以把电源管地管脚按位展开。如下图。

在Concept-HDL中编辑符号图形时,系统自动将栅格设置为0.05 2, 意思是跟踪栅格50mil,显示栅格100mil,

最好别更改这个默认值,否则在原理图设计时,会遇到麻烦。

五.创建Part-table文件

Part-table文件用于灵活构造部件以满足用户不同需要。例如我们可以在Part-table文件中重定义JEDEC_TYPE和ALT_SYMBOLS替代曾经加入过的封装信息。

在Part Developer主界面点击Part Table Files,右键选择New后进入Ptf Editor,如下图。

在Header对话框内分别可定义Key属性,Injected属性,Global属性。在Part Rows对话框

内中定义部件的属性值。

Part-table文件是一个ASCII文件,任何文本编辑器均可编写或修改该文件,注意文件内容必须符合图例格式。

Example:

FILE_TYPE = MULTI_PHYS_TABLE;

PART 'AD704'

CLASS=IC

{================================================================================== ======}

:VENDOR_PART_NUMBER(OPT) = PART_NUMBER | JEDEC_TYPE |

DESCRIPTION ;

{================================================================================== ======}

'AD704AR'(!) = '12100068' | 'SO16-300' | 'Vcc(max)+18V,CMRR>94.0dB,SR>0.15V/us'

'AD704AN'(!) = '12100069' | 'SO16-150' | 'Vcc(max)+18V,CMRR>94.0dB,SR>0.15V/us'

END_PART

END.

在制作Part-table文件时,最好是引用其他人的Part-table文件来修改以节省设计时间。六.验证原理图符号库

完成符号库设计后,在Part Developer 界面选择Tools->Verify,对元件库进行检查,如果没有报错,则此元件库创建基本成功了,为了验证此元件库是否可用,我们可以新创建一个Project,打开Concept-HDL,在原理图页中调入新做的零件打包看是否能成功把元件符号转成PCB封装。

原理图标准化

原理图设计标准化 目的:增强原理图可看性,可继承性。使原理设计清晰化,模块化。减少因原理升级,电路更改以及设计工作交接而导致的错误。 说明:一份完整的原理图不仅仅包括所设计的电路,同时还应该包括整个原理图的索引页,架构框图,电源分配表,时钟分配图,reset信号分配图,GPIO信号使用说明,历史修改记录等内容。前期EE工程师因没有标准而在设计工程中间过多的是依靠个人习惯来画原理图,给继承和维护带来了不便。希望此文件能对大家后续的原理设计有所帮助。 内容: 1、原理设计内容标准化; 首页:索引页,包含整个原理图的页面名称和页码,项目名称,版本; 第二页:架构框图,对整个原理设计的框架做一个说明,包括主要芯片名称,支持的处理器类型,扩展槽名称和数量,主要接口名称和数量,VRM方 案; 第三页:时钟分配图,包括时钟芯片规格,名称,各个时钟的频率,对应在时钟芯片的PIN脚,时钟走向(分配给哪个芯片或哪个扩展槽使用)。包括 芯片外接晶振的型号。 第四页:电源分配方案表(图),包括主板上各电源的大小,负载,转换方式,转换芯片名称(可在设计过程中补充),原理图中的电源网络名称。 第五页:reset&power on信号分配图,包括reset & power on信号的产生,走向 第六页:GPIO,SMBUS说明,包括主板上南桥芯片,SUPER I/O芯片或者其他芯片的GPIO的特殊功能说明,输入输出类型,电源类型等信息。扩展 槽的选择信号,中断信号,请求信号的分配等。 第七页:原理设计页面 …… ……电压测试点,heatsink及挂钩,光学定位点,螺丝孔等…… 倒数第二页: 尾页:rework history,包括每个版本的修改信息 2、原理图页面命名标准化 原则:页面命名应尽可能的包括本页的设计内容,简洁明了,清晰易懂。具体由EE工程师根据设计内容自行确定 3、信号网络命名标准化,电路设计模块化,尽可能参考intel网络命名规范。 网络名称前面加信号功能分类: 如:FSB_XXX HI_XXX DMI_XXX

OrCAD Capture CIS Cadence原理图绘制

OrCADCaptureCIS(Cadence原理图绘制) 1,打开软件........................................ 2,设置标题栏..................................... 3,创建工程文件................................... 4,设置颜色........................................ 2.制作原理库.......................................... 1,创建元件库...................................... 2,修改元件库位置,新建原理图封库................. 3,原理封装库的操作............................... 3.绘制原理图.......................................... 1.加入元件库,放置元件............................ 2.原理图的操作.................................... 3.browse命令的使用技巧 ........................... 4.元件的替换与更新................................ 4.导出网表............................................ 1.原理图器件序号修改.............................. 2.原理图规则检查.................................. 3.显示DRC错误信息................................ 4.创建网表........................................ 5.生成元件清单(.BOM)..................................

Cadence原理图绘制流程

第一章设计流程 传统的硬件系统设计流程如图1-1所示,由于系统速率较低,整个系统基本工作在集中参数模型下,因此各个设计阶段之间的影响很小。设计人员只需要了解本阶段的基本知识及设计方法即可。但是随着工艺水平的不断提高,系统速率快速的提升,系统的实际行为和理想模型之间的差距越来越大,各设计阶段之间的影响也越来越显著。为了保证设计的正确性,设计流程也因此有所变动,如图1-2所示,主要体现在增加了系统的前仿真和后仿真。通过两次仿真的结果来预测系统在分布参数的情况下是否能够工作正常,减少失败的可能性。 细化并调整以上原理图设计阶段的流 程,并结合我们的实际情况,原理图设计 阶段应该包括如下几个过程: 1、 阅读相关资料和器件手册 在这个阶段应该阅读的资料包括,系统的详细设计、数据流分析、各器件手册、器件成本等。 2、 选择器件并开始建库 在这个阶段应该基本完成从主器件到各种辅助器件的选择工作,并根据选择结果申请建库。 3、 确认器件资料并完成详细设计框图 为保证器件的选择符合系统的要求,在这一阶段需要完成各部分电路具体连接方式的设计框图,同时再次确认器件的相关参数符合系统的要求,并能够和其他器件正确配合。 4、 编写相关文档 这些文档可以包括:器件选择原因、可替换器件列表、器件间的连接框图、相关设计的来源(参考设计、曾验证过的设计等),参数选择说明,高速连接线及其它信息说明。 5、 完成EPLD 内部逻辑设计,并充分考虑可扩展性。

在编写相关文档的的同时需要完成EPLD内部逻辑的设计,确定器件容量及连接方式可行。 6、使用Concept-HDL绘制原理图 7、检查原理图及相关文档确保其一致性。 以上流程中并未包括前仿真的相关内容,在设计中可以根据实际情况,有选择的对部分重要连线作相关仿真,也可以根据I/O的阻抗,上升下降沿变化规律等信息简单分析判断。此流程中的各部分具体要求、注意事项、相关经验和技巧有待进一步完善。

Cadence 原理图库设计

Cadence原理图库设计 一.工具及库文件目录结构 Cadence提供Part Developer库开发工具供大家建原理图库使用。 Cadence 的元件库必具备如下文件目录结构为: Library----------cell----------view(包括Sym_1,Entity,Chips,Part-table) Sym_1:存放元件符号 Entity:存放元件端口的高层语言描述 Chips:存放元件的物理封装说明和属性 Part-table:存放元件的附加属性,用于构造企业特定部件 我们可以通过定义或修改上述几个文件的内容来创建和修改一个元件库,但通过以下几个步骤来创建元件库则更直观可靠一些。 二.定义逻辑管脚 在打开或新建的Project Manager中,如图示,打开Part Developer。 然后出现如下画面, 点击Create New,下图新菜单中提示大家选择库路径,新建库元件名称及器件类型。

点击ok后,Part Developer首先让大家输入元件的逻辑管脚。一个原理图符号可以有标量管脚和矢量管脚。 标量管脚在符号中有确定位置,便于检查信号与管脚的对应,但矢量管脚却可使原理图更简洁,适用于多位 总线管脚。 点击上图中的Edit,编辑器会让我们对首或尾带有数字的字符串的多种输入方式(A1; 1A; 1A1)进行选择,一但选定,编辑器即可对同时具有数字和字母的管脚输入进行矢量或标量界定。 管脚名首尾均不带数字的字符串如A; A1A则自动被识别为标量管脚。 按照元件手册决定管脚名称及逻辑方向,选择是否为低电平有效,点击ADD即可加入新的管脚。 (注:不论是标量或矢量管脚,均可采用集体输入,如在Pin Names栏可输入A1-A8, 1C-16C)

Cadence从原理图到PCB

Cadence从原理图到PCB的流程图: 一.原理图 1.建立工程 2.绘制原理图 3. 生成网络表(Net List): 在画板的时候需要导入网络表,在这之前可以为元件自动编号,在工程管理界面下选中.dsn文件,然后选Tools—Annotate;再进行DRC检测。DRC之后可以尝试去生成网络表了,在工程管理界面下,选Tools--Create Netlist, 二.PCB 1. 打开PCB Editor,在弹出的对话框中选择Allegro PCB Design GXL(legacy),然后点击Ok进入PCB编辑器。接下来就是利用向导建立电路板了,包括确定板子的大小、层数、形状等等参数。 File-new 在弹出的对话框中的Drawing Type选择Board(wizard),然后确定文件名,Browse存盘路径等,最后点Ok进入向导。

注意:板子的路径应该和前面生成网表的路径保持一致。 2.导入网络表 接上一个步骤,将网络表导入到刚建好的PCB中。 在此之前还有一个很重要的工作要做,就是指定PCB封装的路径。点击Setup--User Preferences,在弹出对话框中的Categories中选中Design_paths,分别为padpath和psmpath指定路径,即将PCB元件封装路径添加到padpath和psmpath中,以告知Allegro从指定的路径寻找封装。

元件的PCB封装需要自己做或是直接用别人做好的,封装准备好后往PCB 中导入网络表,点击File--Import--Logic,在Import directory中指定在原理图部分生成的网络表文件路径,其他设置使用默认值即可,点击Import Cadence即可导入网络表。 3.叠层设计,规则设定,布局布线 暂时简单描述下元件的放置,布局,布线,具体的叠层设计,设计规则等后面再详细补充

Cadence Capture输出带属性的PDF原理图设置步骤

Cadence Capture 输出带属性的PDF 原理图设置步骤 作者:Myedacn 2016-01-06 1.准备工作 需要安装两个工具,一个是虚拟打印机,一个是脚本运行工具 1.1虚拟打印机安装 官方推荐Adobe Acrobat ,但是这个是需要购买授权的,所以推荐安装免费开源的工具PDFCreator ,可以从网上下载到该工具。https://www.360docs.net/doc/2a17157315.html,/可以下载到最新版本的软件。 按照提示进行安装,安装完成后,可以看到打印机列表里面多了一个虚拟打印机 记住这个打印机的名称,后面会用到。1.2安装脚本运行工具基于Adobe 、PostScript 及可移植文档格式(PDF )的页面描述语言等而编译成的免费软件GhostScript 可以在官网下载到最新版本https://www.360docs.net/doc/2a17157315.html,/按照提示进行安装,安装完成后记住安装路径,比如:C:\Program Files (x86)\gs\gs9.09\bin\gswin32c.exe 后面会用到。2.修改配置文件 打开Cadence Capture 安装目录,比如: C:\Cadence\SPB_16.6\tools\capture\tclscripts\capUtils 找到文件:capPdfUtil.tcl 用文本编辑器打开此文件: 找到以下位置进行修改: set ::capPdfUtil::mPSDriver "PDFCreator " 把默认的Adobe 打印机修改为PDFCreator 修改打印机安装程序位置,红色字体位置所示 set ::capPdfUtil::mPSToPDFConverterList { { "PDFCreator " {{C:\Program Files\PDFCreator\PDFCreator.exe }/N /q /o M y e d a c n 出品

原理图设计规范手册

XXXXXXXXXX电气有限公司 原理图设计规范手册 文件编号:AMN-Q01-2014 编写:日期:2014-02-11 审核:日期:2014-02-11

批准:日期:2014-02-11 2014年02月10发布2014年2月10日实施 二次回路接线 二次回路接线图包括原理图、平面布置图、屏背面安装接线图、端子排和小母线布置图。二次接线的原理接线图分为归总式原理图和展开式原理图。 二次回路的最大特点是其设备、原件的动作严格按照设计的先后顺序进行,其逻辑性很强,所以读原理图时只需按一定规律进行,便会显得条理清楚,易懂易记。 设计的方法遵循(六先六后): ⑴“先一次,后二次”; ⑵“先交流,后直流”; ⑶“先电源,后接线”; ⑷“先线圈,后触点”; ⑸“先上后下”; ⑹“先左后右” 1.1二次设备的选择 二次回路保护设备的选择

1.1.1熔断器的配置 ⑴控制和保护回路熔断器的配置 Ⅰ.同一安装单位的控制、保护和自动装置一般合用一组熔断器。 Ⅱ.当一个安装单位内只有一台断路器时(如35kV或110kV出线),只装一组熔断器。 Ⅲ.当一个安装单位有几台断路器时(如三绕组变压器各侧断路器),各侧断路器的控制回路分别装设熔断器。 Ⅳ.对其公用的保护回路,应根据主系统运行方式决定接于电源侧断路器的熔断器上或另行设置熔断器。 Ⅴ.发电机出口断路器和自动灭磁装置的控制回路一般合用一组熔断器。Ⅵ.两个及以上安装单位的公用保护和自动装置回路(如母线保护等),应装设单独的熔断器。 ⑵信号回路熔断器的配置 Ⅰ.每个安装单位的信号回路(包括隔离开关的位置信号、事故和预告信号、指挥信号等)一般用一组熔断器。 Ⅱ.公用的信号回路(如中央信号等)应装设单独的熔断器。 Ⅲ.厂用电源和母线设备信号回路一般分别装设公用的熔断器。 Ⅳ.闪光小母线的分支线上,一般不装设熔断器。 Ⅴ.信号回路用的熔断器均应加以监视,一般用隔离开关的位置指示器进行监视,也可以用继电器或信号灯来监视。 1.1.2熔断器的选择 ⑴控制、信号和保护回路熔断器的选择

于博士Cadence视频教程原理图设计pdf

Cadence SPB 15.7 快速入门视频教程 的SPB 16.2版本 第01讲 - 第15讲:OrCAD Capture CIS原理图创建 第16讲 - 第26讲:Cadence Allegro PCB创建封装 第27讲 - 第36讲:Cadence Allegro PCB创建电路板和元器件布局 第37讲 - 第46讲:Cadence Allegro PCB设置布线规则 第47讲 - 第56讲:Cadence Allegro PCB布线 第57讲 - 第60讲:Cadence Allegro PCB后处理、制作光绘文件 第1讲 课程介绍,学习方法,了解CADENCE软件 1.要开发的工程 本教程以下面的例子来开始原理图设计和PCB布线 2.教程内容

3.软件介绍 Design Entry CIS:板级原理图工具 Design Entry HDL:设计芯片的原理图工具,板级设计不用 Layout Plus:OrCAD自带的PCB布线工具,功能不如PCB Editor强大 Layout Plus SmartRoute Calibrate:OrCAD自带的PCB布线工具,功能不如PCB Editor强大PCB Editor:Cadence 的PCB布线工具 PCB Librarian:Cadence 的PCB封装制作工具 PCB Router:Cadence 的自动布线器 PCB SI:Cadence 的PCB信号完整性信号仿真的工具 SigXplorer:Cadence 的PCB信号完整性信号仿真的工具 4.软件列表

5.开始学习Design Entry CIS 启动:Start/Cadence SPB 16.2/Design Entry CIS 启动后,显示下图: 里面有很多选项,应该是对应不同的License 本教程使用:OrCAD Capture CIS 我个人认为:Allegro PCB Design CIS XL是所有可选程序中,功能最强大的,但不知道,强在哪里;而且本教程的原理图文件可以使用上表中不同的程序打开 6.选择OrCAD Capture CIS,启动后显示下图

如何将altium designer的原理图和PCB转入cadence里

说明: 1)本教程适用于将altium designer的原理图和PCB转入cadence(分别对应capture CIS和allegro)里。对于protel 99se,可以将其先导入较新版本的AD里,再转入cadence中。 2)整个过程中使用的软件包括altium designer Summer 08,cadence16.6,orCAD10.3-capture(免安装精简版),PADS9.3三合一完美精简版。其中,后面两个软件较小,便于下载。 3)原理图的转化路线是,从altium designer导出的.dsn文件,用orcad10.3-capture打开后,保存为cadence16.6可以打开的文件。因为较新版本的cadence不能直接打开AD转换出来的.dsn文件。如果你不是这些版本的软件,也可以参考本人的方法进行尝试。 4)pcb转化的顺序是,altium designer导出的文件,导入PADS9.3打开,然后导出.asc文件。随后利用allegro对pads的接口,将pads文件导入。 1. 原理图的导入 1.1选中原理图的项目文件,即.PRJPCB文件,右键-》save projec as,选择.dsn文件,输入要保存的文件名,保存。注意输入新的文件名的时候要把文件名的后缀手动改掉。 1.2打开orCAD10.3-capture文件夹下面的capture.exe(如果同一台电脑装了新版本的cadence,例如cadence16.6的话,环境变量中的用户变量会有冲突。具体地来说对于orCAD10.3来说,CDS_LIC_FILE的值必须是安装目录\orCAD10.3-capture\crack\license.dat。而对于cadence16.6来说,环境变量必须是5280@localhost。因此要使用orCAD10.3的话,必须将CDS_LIC_FILE 的值改掉,否则无法打开。等下使用cadence16.6,就必须将值改回来)。 1.3使用orCAD10.3将刚才保存的.dsn文件打开,并保存成project。 1.4 随后就可以使用新版本的cadence的capture CIS打开保存的文件(注意改环境变量中的用户变量CDS_LIC_FILE)。 2. PCB的导入 由于allegro可以根据已有的brd文件生成元器件的封装,因此将PCB导入allegro后使用者免于重新使用allegro绘制一遍封装。 1.1打开pads9.3,file-》new,按照默认配置建立一个文件,保存。 1.2file-》import,选中要转换的.pcb文件,打开,保存在C盘的PADS Projects文件夹下面。 (安装PADS9.3三合一完美精简版时会自动在C盘产生这个文件夹。) 1.3file-》export,将文件保存为.asc文件。接下来回弹出下图所示的对话框。注意要将.pcb

CADENCE从原理图到PCB步骤(精)

CADENCE从原理图到PCB步骤 一.原理图 1.建立工程 与其他绘图软件一样,OrCAD以Project来管理各种设计文件。点击开始菜单,然后依次是所有程序-- Allegro SPB 15.5--Design Entry CIS,在弹出的Studio Suite Selection对话框中选择第一项OrCAD_Capture_CIS_option with capture,点击Ok进入Capture CIS。接下来是File--New--Project,在弹出的对话框中填入工程名、路径等等,点击Ok进入设计界面。2.绘制原理图 新建工程后打开的是默认的原理图文件SCHEMATIC1 PAGE1,右侧有工具栏,用于放置元件、画线和添加网络等等,用法和Protel类似。点击上侧工具栏的Project manager(文件夹树图标)进入工程管理界面,在这里可以修改原理图文件名、设置原理图纸张大小和添加原理图库等等。 1)修改原理图纸张大小: 双击SCHEMATIC1文件夹,右键点击PAGE1,选择Schematic1 Page Properties,在Page Size 中可以选择单位、大小等; 2)添加原理图库: File--New--Library,可以看到在Library文件夹中多了一个library1.olb的原理图库文件,右键单击该文件,选择Save,改名存盘; 3)添加新元件: 常用的元件用自带的(比如说电阻、电容的),很多时候都要自己做元件,或者用别人做好的元件。右键单击刚才新建的olb库文件,选New Part,或是New Part From Spreadsheet,后者以表格的方式建立新元件,对于画管脚特多的芯片元件非常合适,可以直接从芯片Datasheet中的引脚描述表格中直接拷贝、粘贴即可(pdf格式的Datasheet按住Alt键可以按列选择),可以批量添加管脚,方便快捷。 4)生成网络表(Net List): 在画板的时候需要导入网络表,在这之前原理图应该差不多完工了,剩下的工作就是查缺补漏。可以为元件自动编号,在工程管理界面下选中.dsn文件,然后选Tools—Annotate (注解),在弹出的对话框中选定一些编号规则,根据需求进行修改或用默认设置即可。进行DRC检测也是在生成网络表之前的一项重要工作,可以避免出现一些不必要的设计错误。DRC之后可以尝试去生成网络表了,还是在工程管理界面下,选Tools--Create Netlist,可以在弹出的对话框中选择网络表的存放路径,其他默认设置即可,生成网络表的过程中如果出错,可以通Windows--Session Log查看出错的原因,比如说有元器件忘了添加封装等。 5)更新元件到原理图: 当元件库中的某个元件修改后需要原理图也同步更新时,可以不必重新放置元件(万一有100个或更多该元件岂不是要疯了),在工程管理界面下,双击Design Cache文件夹,选中刚才修改的元件,右键单击选择Update Cache,一路yes下去即可将原理图中该元件全部更新。 6)一些细节: 画原理图时的放大和缩小分别是按键“i”(Zoom In)和“o”(Zoom Out)和Protel有所区别;在创建元件封装的时候,除了GND可以同名以外,不能有其他同名的管脚,否者报错,不过貌似报错也没有影响,因为打开OrCAD自带的元件库时(比如Xilinx的FPGA),也有除GND外的同名管脚;添加网络标号的快捷键是“n”,不过在OrCAD中网络标号无法复制,记得Protel中是可以通过复制已有的网络标号来添加新的网络标号的。

CANDENCE原理图库设计指南

原理图库设计 一,工具及库文件目录结构 目前公司EDA库是基于Cadence设计平台,Cadence提供Part Developer库开发工具供大家建原理图库使用。 Cadence 的元件库必具备如下文件目录结构为: Library----------cell----------view(包括Sym_1,Entity,Chips,Part-table) Sym_1:存放元件符号 Entity:存放元件端口的高层语言描述 Chips:存放元件的物理封装说明和属性 Part-table:存放元件的附加属性,用于构造企业特定部件 我们可以通过定义或修改上述几个文件的内容来创建和修改一个元件库,但通过以下几个步骤来创建元件库则更直观可靠一些。 二,原理图库建库参考标准 1,Q/ZX 04.104.1电路原理图设计规范-Cadence元器件原理图库建库要求 该标准规定了元件库的分类基本要求和划分规则,元器件原理图符号单元命名基本要求和规则,元器件原理图符号单元图形绘制基本要求和规则。 2, Q/ZX 04.125 EDA模块设计规范 此标准规定了全公司基于Cadence设计平台的EDA模块库的设计标准。 3, Q/ZX 73.1151 EDA 库管理办法 此标准规定了公司统一的基于Cadence设计平台的元器件原理图库,封装库,仿真库和相应PCBA DFM评审辅助软件VALOR的VPL库及相应的元器件资料的管理办法。从此标准中我们可以知道VPL建库流程,建库过程的各项职责以及VPL库的验证,维护等管理办法。 4, Q/ZX 73.1161 EDA模块库管理办法 此标准规定了全公司基于Cadence设计平台的EDA模块库的管理办法。三,原理图库建库step by step 第一步,建库准备 在打开或新建的Project Manager中,如图示,打开Part Developer。

原理图和PCB的设计规范

一.PCB设计规范 1、元器件封装设计 元件封装的选用应与元件实物外形轮廓,引脚间距,通孔直径等相符合。元件外框丝印统一标准。 插装元件管脚与通孔公差相配合(通孔直径大于元件管脚直径8-20mil),考虑公差可适当增加。建立元件封装时应将孔径单位换算为英制(mil),并使孔径满足序列化要求。插装元件的孔径形成序列化,40mil以上按5mil递加,即40mil,45mil,50mil……,40mil以下按4mil递减,即36mil,32mil,28mil……。 2、PCB外形要求 1)PCB板边角需设计成(R=1.0-2.0MM)的圆角。 2)金手指的设计要求,除了插入边按要求设计成倒角以外,插板两侧边也应设计成(1-1.5)X45度的倒角或(R1-1.5)的圆角,以利于插入。 1.布局 布局是PCB设计中很关键的环节,布局的好坏会直接影响到产品的布通率,性能的好坏,设计的时间以及产品的外观。在布局阶段,要求项目组相关人员要紧密配合,仔细斟酌,积极沟通协调,找到最佳方案。 器件转入PCB后一般都集中在原点处,为布局方便,按合适的间距先把 所有的元器件散开。 2)综合考虑PCB的性能和加工效率选择合适的贴装工艺。贴装工艺的优先顺序为: 元件面单面贴装→元件面贴→插混装(元件面插装,焊接面贴装一次波峰成形); 元件面双面贴装→元件面插贴混装→焊接面贴装。 1.布局应遵循的基本原则 1.遵照“先固后移,先大后小,先难后易”的布局原则,即有固定位 置,重要的单元电路,核心元器件应当优先布局。

2.布局中应该参考原理图,根据重要(关键)信号流向安排主要元器 件的布局。 3.布局应尽量满足以下要求:总的连线尽可能短,关键信号线最短, 过孔尽可能少;高电压,大电流信号与低电压,小电流弱信号完全分开; 模拟与数字信号分开。 4.在满足电器性能的前提下按照均匀分布,重心平衡,美观整齐的标 准优化布局。 5.如有特殊布局要求,应和相关部门沟通后确定。 2.布局应满足的生产工艺和装配要求 为满足生产工艺要求,提高生产效率和产品的可测试性,保持良好的可维护性,在布局时应尽量满足以下要求: 元器件安全间距(如果器件的焊盘超出器件外框,则间距指的是焊盘之 间的间距)。 1.小的分立器件之间的间距一般为0.5mm,最小为0.3mm,相邻器件 的高度相差较大时,应尽可能加大间距到0.5mm以上。如和IC (BGA),连接器,接插件,钽电容之间等。 2.IC、连接器、接插件和周围器件的间距最好保持在1.0mm以上, 最少为0.5mm,并注意限高区和禁止摆放区的器件布局。 3.安装孔的禁布区内无元器件。如下表所示 4.高压部分,金属壳体器件和金属件的布局应在空间上保证与其它 器件的距离满足安规要求。

Cadence原理图设计简介

原理图设计简介 本文简要介绍了原理图的设计过程,希望能对初学者有所帮助。 一.建立一个新的工程 在进行一个新的设计时,首先必须利用Project Manager 对该设计目录进行配置,使该目录具有如下的文件结构。 所用的文件库 信息。 Design directory 启动Project Manager Open: 打开一个已有Project . New :建立一个新的Project . 点击New 如下图: cadence 将会以你所填入的project name 如:myproject 给project file 和design library 分别命

名为myproject.cpm和myproject.lib 点击下一步 Available Library:列出所有可选择的库。包括cadence自带库等。Project Library:个人工程中将用到的所有库。如myproject_lib 点击下一步 点击下一步

点击Finish完成对设计目录的配置。 为统一原理图库,所有共享的原理图库统一放在CDMA硬件讨论园地----PCB设计专栏内。 其中:libcdma 目录为IS95项目所用的器件库。 libcdma1目录为IS95项目之后所用的器件库。 每台机器上只能存放一套共享的原理图库,一般指定放在D:盘的根目录下, 即:D:\libcdma , D:\libcdma1 ... * 注意:设计开始时,应该首先将机器上的库与共享的原理图库同步。 下面介绍如何将共享库加入到自己的工程库中。 点击Setup 点击Edit 编辑cds.lib文件。添入以下语句: define libcdma d:\libcdma define libcdma1 d:\libcdma1 则库libcdma , libcdma1被加入Availiable Library 项内。如下图:

cadence原理图设计规范

原理图设计规范 理念: 设计好一份规范的原理图对设计好PCB/跟机/做客户资料具有指导性意义,是做好一款产品的基础。 一、标准图框图幅 根据实际需要,我公司常用图幅为A2、A3、A4,并有标准格式的图框。其中每一图幅可根据方向分为Landscape(纵向)及Portrait(横向)。在选用图纸时,应能准确清晰的表达区域电路的完整功能。 二、电路布局 原理图的作用是表示电路连接关系,因此需要注意电路结构的易读性。一般可将电路按照功能划分成几个部分,并按照信号流程将各部分合理布局。连线时,需注意避免线条的不必要交叉,以免难于辨识。具体要求如下: 1. 各功能块布局要合理, 整份原理图需布局均衡. 避免有些地方很挤,而有些 地方又很松, PCB 设计同等道理. 2. 尽量将各功能部分模块化(如功放,RADIO, E.VOL, SUB-WOOFER 等),以便于同 类机型资源共享, 各功能模块界线需清晰. 3. 接插口(如电源/喇叭插座, AUX IN, RCA OUTPUT, KB/CD SERVO 接口等)尽 量分布在图纸的四周围, 示意出实际接口外形及每一接脚的功能. 4. 可调元件(如电位器), 切换开关等对应的功能需标识清楚. 5. 滤波器件(如高/低频滤波电容,电感)需置于作用部位的就近处. 6. 重要的控制或信号线需标明流向及用文字标明功能. 7. CPU 为整机的控制中心, 接口线最多. 故CPU周边需留多一些空间进行布线 及相关标注,而不致于显得过分拥挤. 8. CPU 的设置管脚(如AREA1/AREA2, CLOCK1/CLOCK2等)需于旁边做一表格进 行对应设置的说明. 9. 重要器件(如接插座,IC, TUNER 等)外框用粗体线(统一 0.5mm). 10. 元件标号照公司要求按功能块进行标识. 11. 元件参数/数值务求准确标识. 特别留意功率电阻一定需标明功率值, 高耐 压的滤波电容需标明耐压值. 12. 每张原理图都需有公司的标准图框,并标明对应图纸的功能,文件名,制图人 名/审核人名, 日期, 版本号.

Cadence-原理图批量修改元器件属性

一、导出BOM 前提条件:对所有器件的位号进行过检测。不允许出来两个器件使用相同的位号。最简单的方式是通过Tool→Annotate重新进行编排,保证不会出错。 步骤1,选中所在的工程设计,如下图 步骤2,点击Tools→Bill of Meterials

步骤3:选中“Place each part entry on a separate line”,并且在header和Combined propert string 中输入你所想要导出的参数,其中必须选择”Reference”,这个是器件的位号,属于唯一值,后面有大用。 至此,BOM已经按照我们想要的格式导出来的。接下来就是修改BOM 二、修改BOM的内容 步骤1:打开BOM,刚打开的BOM应该是长得跟下面差不多

步骤2:将期修改一下,去掉一些不必要的几行,和不必要的列“item”和”quantity”修改后应该是这样。 步骤3:根据自己的想法,修改BOM的具体内容,注意,Reference这一列一定不能修改。

这个演示只是装简单地添加了一个叫做Mount的属性,用于表明这个器件要不要焊接 修改完成后,如下图所示: 三、生成upd文件。 Cadence Capture CIS能够从UPD文件中自动更新器件的属性。所以一个很重要的步骤就是生成UPD文件。 UPD文件格式的基本样子是这样子的: "{Part Reference}" "TOL" "R1" "10%" "U1" "/IGNORE/" 步骤1:添加分号。方便起见将工作簿修改一下名字,同时增加两个新的工作页。如下图

步骤2:在sheet2的A1格中输入="$"&sheet1!A1&"$" 。如下图所示。这样做的目录是将sheet1的A1格的内容前后各加一个$号。其实添加$号也不是最终目的,只是这样操作比较简单

如何将altiumdesigner的原理图和PCB转入cadence里

说明: 1)本教程适用于将altiumdesigner的原理图和PCB转入cadence(分别对应captureCIS和allegro)里。对于protel99se,可以将其先导入较新版本的AD里,再转入cadence中。 2)整个过程中使用的软件包括altiumdesignerSummer08,cadence16.6,orCAD10.3-capture(免安装精简版),PADS9.3三合一完美精简版。其中,后面两个软件较小,便于下载。 3)原理图的转化路线是,从altiumdesigner导出的.dsn文件,用orcad10.3-capture打开后,保存为cadence16.6可以打开的文件。因为较新版本的cadence不能直接打开AD转换出来的.dsn文件。如果你不是这些版本的软件,也可以参考本人的方法进行尝试。 4)pcb转化的顺序是,altiumdesigner导出的文件,导入PADS9.3打开,然后导出.asc文件。随后利用allegro对pads的接口,将pads文件导入。 1.原理图的导入 1.1选中原理图的项目文件,即.PRJPCB文件,右键-》saveprojecas,选择.dsn文件,输入要保存的文件名,保存。注意输入新的文件名的时候要把文件名的后缀手动改掉。 1.2打开orCAD10.3-capture文件夹下面的capture.exe(如果同一台电脑装了新版本的cadence,例如cadence16.6的话,环境变量中的用户变量会有冲突。具体地来说对于orCAD10.3来说,CDS_LIC_FILE的值必须是安装目录\orCAD10.3-capture\crack\license.dat。而对于cadence16.6来说,环境变量必须是5280@localhost。因此要使用orCAD10.3的话,必须将CDS_LIC_FILE的值改掉,否则无法打开。等下使用cadence16.6,就必须将值改回来)。 1.3使用orCAD10.3将刚才保存的.dsn文件打开,并保存成project。 1.4随后就可以使用新版本的cadence的captureCIS打开保存的文件(注意改环境变量中的用户变量CDS_LIC_FILE)。 2.PCB的导入 由于allegro可以根据已有的brd文件生成元器件的封装,因此将PCB导入allegro后使用者免于重新使用allegro绘制一遍封装。 1.1打开pads9.3,file-》new,按照默认配置建立一个文件,保存。 1.2file-》import,选中要转换的.pcb文件,打开,保存在C盘的PADSProjects文件夹下面。 (安装PADS9.3三合一完美精简版时会自动在C盘产生这个文件夹。) 1.3file-》export,将文件保存为.asc文件。接下来回弹出下图所示的对话框。注意要将.pcb 文件和.asc文件保存在同一个目录下,即C盘的PADSProjects文件夹下面,否则allegro 转换时会出现pads_in.log找不到的现象。(关于AD的pcb文件导入pads,网上还有一种方法是AD保存为PCB二进制文件,即.PcbDoc文件,再由pads导入.PcbDoc文件。用户可以自行尝试。总之,ad转换成pads似乎较为顺畅) 1.4格式选择PowerPCBV5.0,勾选认为比较的项目。点击“OK”。 1.5随后使用allegro的import-》translator,选择pads,弹出如下的对话框。 其中第一行是指定.asc文件,第三行是指定要转换成的.brd文件。一般而言都是C盘的PADSProjects文件夹内部。第二行只要指定目录,然后在对话框里点保存即可。点击translate,即可完成转换。随后file-》open,打开刚才建立的.brd文件。

实验指导书1——原理图库文件的创建

实验一、原理图库文件的创建 一、实验目的: 1、掌握原理图库文件的建立方法。 2、掌握原理图元件的绘制方法。 二、实验步骤: Ⅰ、新建一个元件库: 1、原理图元件库的建立 新建一个新的原理图库文件并保存该文件:执行菜单file->new->schematic library,系统默认新建一个名为schlib1.schlib的库文件,鼠标右键单击该库文件,在弹出的菜单中选择save 或save as,选择合适的路径,改名(只需输入文件名即可,如abc)并保存该文件。 2、新建一个原理图元件(以一个PDIUSBD12为例) 1)、如果是新建的一个库文件,则系统自动新建一个新元件component_1。否则执行菜单tools->new component,新建一个新元件component_1。在sch library(右下角SCH标签中)中可以看到元件。 2)、改名:在sch library(右下角SCH标签中)中,选中器件,执行菜单tools->rename component, 输入元件名(如本例中为PDIUSBD12)即可。 3)、绘制元件的外形,执行菜单place->rectangle,单击鼠标左键确定外形的左上角,拖动鼠标,在外形的右下角单击鼠标左键。然后单击鼠标右键取消放置外形。 4)、添加引脚,执行菜单place->pin,按TAB键,编辑引脚属性。要编辑引脚名(display name)、引脚号(Designator)、及引脚的电气属性(Electrical Type)。如第1脚,引脚名(display name)为DA TA<0>,引脚号(Designator)为1,引脚的电气属性(Electrical Type)为IO。同样,放置其它引脚。PDIUSBD12 的引脚图见附录。 说明:放置引脚时引脚号在原件外形框外;反斜杠“\”可以给引脚添加取反号。 5)、设置元件属性,在sch library中,选中器件,点edit。“Designator”输入默认的标识,”IC?”;“Comment”输入默认的元件标注,” PDIUSBD12”;在model区域添加PCB封装:单击add,在mode type栏内选footprint,单击ok。点按钮browse,再点右边的…, 选择合适的封装即可。注:元件封装可暂时不加。这里,“Designator”项必不可少。 3、建立一个多功能原理图元件(以反向器74HC14为例)

cadence原理图设计

本文简要介绍了cadence原理图的设计过程,希望能对初学者有所帮助。 一.建立一个新的工程 在进行一个新的设计时,首先必须利用Project Manager 对该设计目录进行配置,使该目录具有如下的文件结构。 下面举例说明: 启动Project Manager Open: 打开一个已有Project . New :建立一个新的Project . 点击New 如下图: cadence 将会以你所填入的project name 如:myproject 给project file和design library分别命名为myproject.cpm 和myproject.lib

点击下一步 Available Library:列出所有可选择的库。包括cadence 自带库等。Project Library:个人工程中将用到的所有库。如myproject_lib 点击下一步 点击下一步

点击Finish完成对设计目录的配置。 为统一原理图库,所有共享的原理图库统一放在CDMA 硬件讨论园地----PCB 设计专栏内。其中: libcdma 目录为IS95 项目所用的器件库。libcdma1 目录为IS95 项目之后所用的器件库。 每台机器上只能存放一套共享的原理图库,一般指定放在D:盘的根目录下,即:D:libcdma , D:libcdma1 ... * 注意:设计开始时,应该首先将机器上的库与共享的原理图库同步。 下面介绍如何将共享库加入到自己的工程库中。 点击 Edit 编辑cds.lib 文件。添入以下语句: define libcdma d:libcdma define libcdma1 d:libcdma1 则库libcdma , libcdma1 被加入Availiable Library 项内。如下图:

CADENCE 培训(原理图设计一)

CONCEPT-HDL原理图设计 一.创建新项目 1.用Project Manager建立Project *注意:在这里最好新建一个自己的设计目录并将所用库拷到本目录下,如果用默认的目录和库,很容易将目录结构搞乱。记住一定要编辑cds.lib文件 在Project Manager工具栏中选择File->New,将出现一个建立Project的对话框,按着提示新建了一个cpm文件并建立起了一个Lib:Cell:View:File结构的目录层次。其中Lib、Cell和View分别表示一组目录。在实际使用中发现,认识并理解这个结构,对学习这套工具的使用很有帮助。下图显示了一个典型的Lib:Cell:View目录结构: 由上图可以看出Lib目录是一个库目录,该目录下包含了所有的Cells。每个Cell目录下存放了一个设计(这里的设计是指PCB或芯片的设计,因此PCB中使用的芯片也被认为是一个设计而存在Cell目录下)的所有数据。这些数据又被分类归入各个VIEW。比如,UAS项目中交换板的Cell目录是SPB,在SPB下有schematic,symbol,package和physical等view目录。每个View目录下包含了一个设计的某一方面的数据。比如,原理图数据都被存放在sch_n VIEW(n表示原理图的版本号)。而Layout数据则被放physical下。