数字集成电路物理设计阶段的低功耗技术

28卷 第4期2011年4月

微电子学与计算机

MICROELECTRONICS &COM PU TER

V ol.28 N o.4A pr il 2011

收稿日期:2010-06-10;修回日期:2010-08-28基金项目:国家自然科学基金项目(60736010)

数字集成电路物理设计阶段的低功耗技术

桑红石,张 志,袁雅婧,陈 鹏

(华中科技大学图像识别与人工智能研究所多谱信息处理技术国家级重点实验室,湖北武汉430074)摘 要:通过一个图像处理So C 的设计实例,着重讨论在物理设计阶段降低CM O S 功耗的方法.该方法首先调整PA D 摆放位置、调整宏单元摆放位置、优化电源规划,得到一个低电压压降版图,间接降低CM OS 功耗;接着,通过规划开关活动率文件与设置功耗优化指令,直接降低CM OS 功耗.最终实验结果表明此方法使CM O S 功耗降低了10.92%.基于该设计流程的图像处理SoC 已经通过A T E 设备的测试,并且其功耗满足预期目标.关键词:集成电路;物理设计;电压降;低功耗

中图分类号:T N492 文献标识码:A 文章编号:1000-7180(2011)04-0073-03

A Method of Reducing the CMOS Power During

the Physical Design Stage of Digital Integrated Circuit

SANG Hong -shi,ZH ANG Zhi,YU AN Ya -jing,CHEN Peng

(Institute for Patter n R eco gnition &A rt ificial Intelligence,H U ST N atio nal K ey L abo rato ry o f Science&

T echnolog y on mult-i spectra l infor matio n pro cessing ,Wuhan 430074,China)

Abstract:T he method t o reduce the CM OS pow er during the physical desig n stag e is disucssed in this pa per ,util-i zing t he SoC instance o f an image pr ocessing desig n.F irstly,the placement locations of the P A D and macro cells wer e adjusted and the po wer planning w as o pt imized.As a result,an intermediate la yout w ith low er vo ltag e dr op is gained,which reduces the CM OS po wer indir ect ly.Seco ndly ,the file of swit ching activity ratio planned and the po wer optimization inst ruct ions set ar e applied o n the inter mediat e layout,and the CM O S pow er is directly reduced.Finally,simulation results sho w that the method has sav ed t he po wer 10.92%.T he So C instance chip entity has passed the test on the AT E and the po wer meets the desig n expection.

Key words:int eg rat ed cir cuit;phy sical design;I R dr op;low power consumptio n

1 引言

随着集成电路规模的扩大以及便携式和嵌入式应用需求的增长,低功耗数字集成电路设计技术日益受到重视,已成为集成电路设计的研究热点.通常低功耗设计技术包括三个方面:设计中的低功耗技术、封装的低功耗技术和运行管理的低功耗技术.其中设计中的低功耗技术包括前端设计阶段的体系结构级低功耗技术、RT L 级低功耗技术、门级低功耗技术和物理设计阶段的低功耗技术.

本文提出了物理设计阶段两种降低CM OS 功

耗的方法.首先,调整PAD 摆放位置、调整宏单元摆放位置、优化电源规划,得到一个低电压压降版图,器件在低电压压降区域消耗功耗较少,间接降低CM OS 功耗;其次,规划开关活动率文件与设置功耗优化指令实现器件的替换、缓冲器的插入、管脚交换、逻辑重组直接降低CM OS 功耗.其中,开关活动率文件定义了高翻转率信号,可以使工具通过减少线电容和门尺寸进行动态功耗优化.对比实验中各种情况的电压压降结果和功耗分析结果,发现在物理设计阶段调整PAD 摆放位置[1]、调整宏单元摆放位置、优化电源规划可以在一定程度上减少电压压

微电子学与计算机2011年

降,规划开关活动率文件和设置功耗优化指令可以降低一定程度的动态功耗.2 物理设计流程

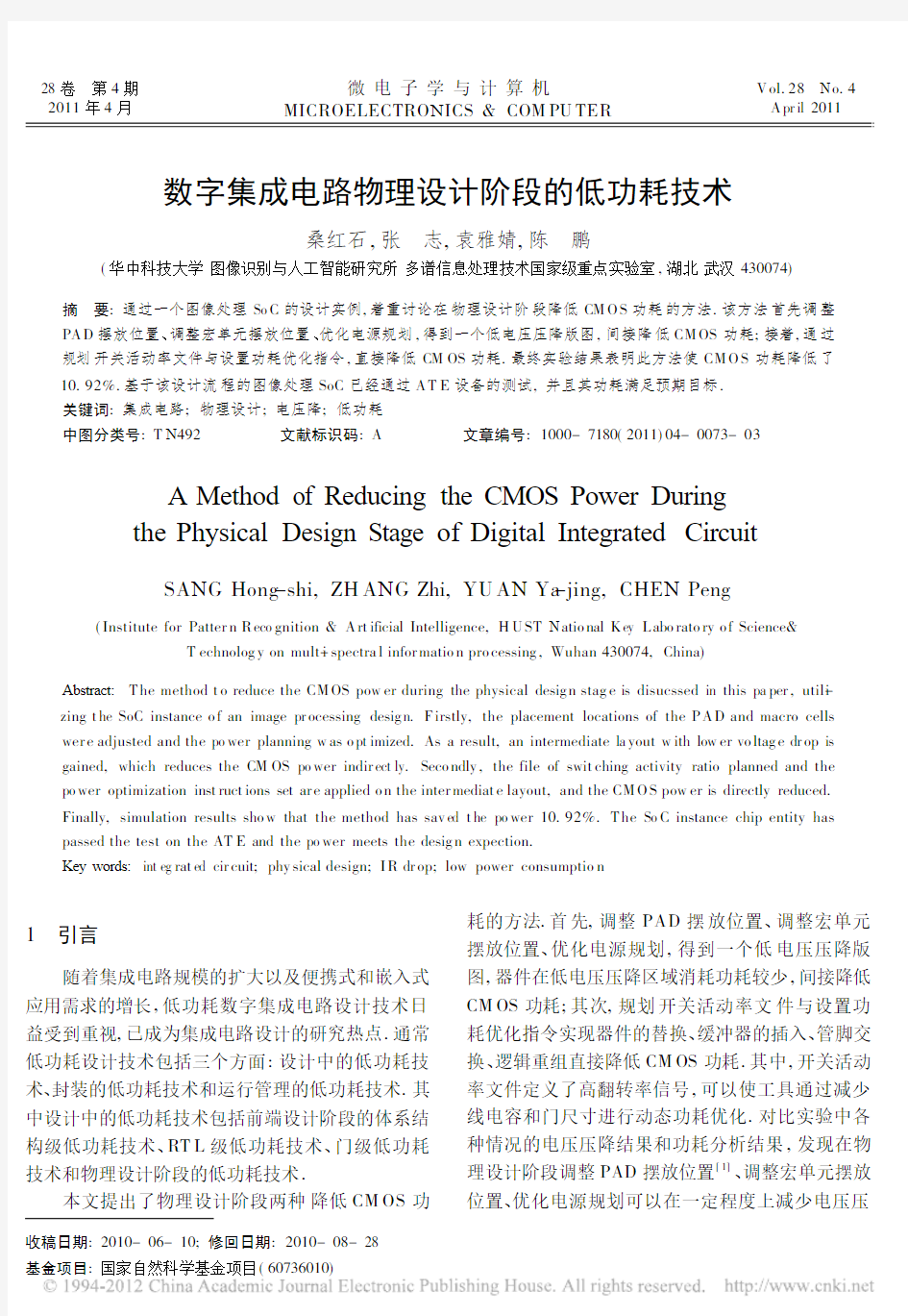

物理设计阶段包括数据准备、布局规划、时钟树综合、布线、寄生参数抽取、可制造性分析等环节.采

用Synopsy s 的IC Compiler 集成设计环境,着重利用其M CM M (M ult-i Corner M ult-i Mo de)功能.因为MCM M 能同时处理多个scenar io ,对时序与功耗进行同步优化.该图像处理SoC 物理设计的scenar -io 定义如图1所示.每个scenario 由角、模式和T lup 寄生参数文件组成

.

图1 scenar io 的定义

设计以M CMM (多角多模式)的func _w orst _cor ner 为curr ent_scenar io ,在布局规划、时钟树综

合、布线阶段同时对4个scenario 下的所有时序路径进行优化,并在这期间进行时序分析、拥塞分析以减少逻辑DRC(Desig n Rule Check)、物理DRC 以及LVS (Layo ut Versus Scheme )违例.其中逻辑DRC 指过渡时间、扇出和电容,物理DRC 指设计规则检查,LVS 指版图与原理图比对.流片前检查时序、DRC 与LVS 是否满足设计要求,如果有违例就要返回到版图修改,如果没有违例就可以流片.

3 物理设计中的低功耗考虑

物理设计阶段的低功耗技术包括间接降低CM OS 功耗技术与直接降低CM OS 功耗技术.下面

以某图像处理SoC 为例,对两种方法的具体实现和性能进行讨论.

3.1 间接降低CM OS 功耗技术

电压压降(IR -Dro p)由电线电阻和电源与地之间的电流产生的,与峰值电流有关.电压压降违例会使芯片动态功耗增大,因为电压压降违例区域对电源电压的需求增大,由公式P 动态=U 2

I 可知,电源电压与动态功耗成正比,所以电压压降违例会间接增大芯片动态功耗.一个好布局会减少一定程度的电压压降[2-3],间接降低CM OS 功耗,这就是物理设计阶段通过规划布局间接降低CM OS 功耗的基本依据.

布局规划首先考虑布图规划,即根据前端提供的门级网表和时序约束文件,把具有逻辑关系的PAD 、宏单元和标准单元就近放置.时钟PA D 要尽可能靠近电源PAD,电源PAD 要考虑电压压降的

大小,一般需要在布局阶段完成后做电压压降分析,从而选择一个最好的PAD 摆放位置.宏单元放在

四周,流出版图中间位置布标准单元.宏单元之间流出布线通道,用于布线.最后用飞线分析各模块信号流整体流向的一致性.

其次,电源规划[4-5]对降低IR -Dr op 也有重要作用.为了保证芯片充分供电,放置了4对给内核供电的电源/地和4对给PAD 供电的电源/地.根据参考文献[6]中提供的Ring 宽度计算方法得到Core Ring 和Stripe 的宽度分别为14L m 、5L m.加宽Pow er Ring 可以增大与电流垂直的电阻截面面积使电阻减小,减少压降.在面积允许的条件下,通过适量增大Pow er Ring 宽度减小压降.由于顶层金属具有方块电阻小的优点,能有效降低电源环上的IR -Dro p,通常全局的电源环使用顶层金属来走线.电源网络规划时要保证每个宏单元至少有一个电源条Str ipe 穿过,且使之分布均匀.为了降低修复可制造分析阶段的天线效应难度,宏单元外层电源环采用3、4层金属.

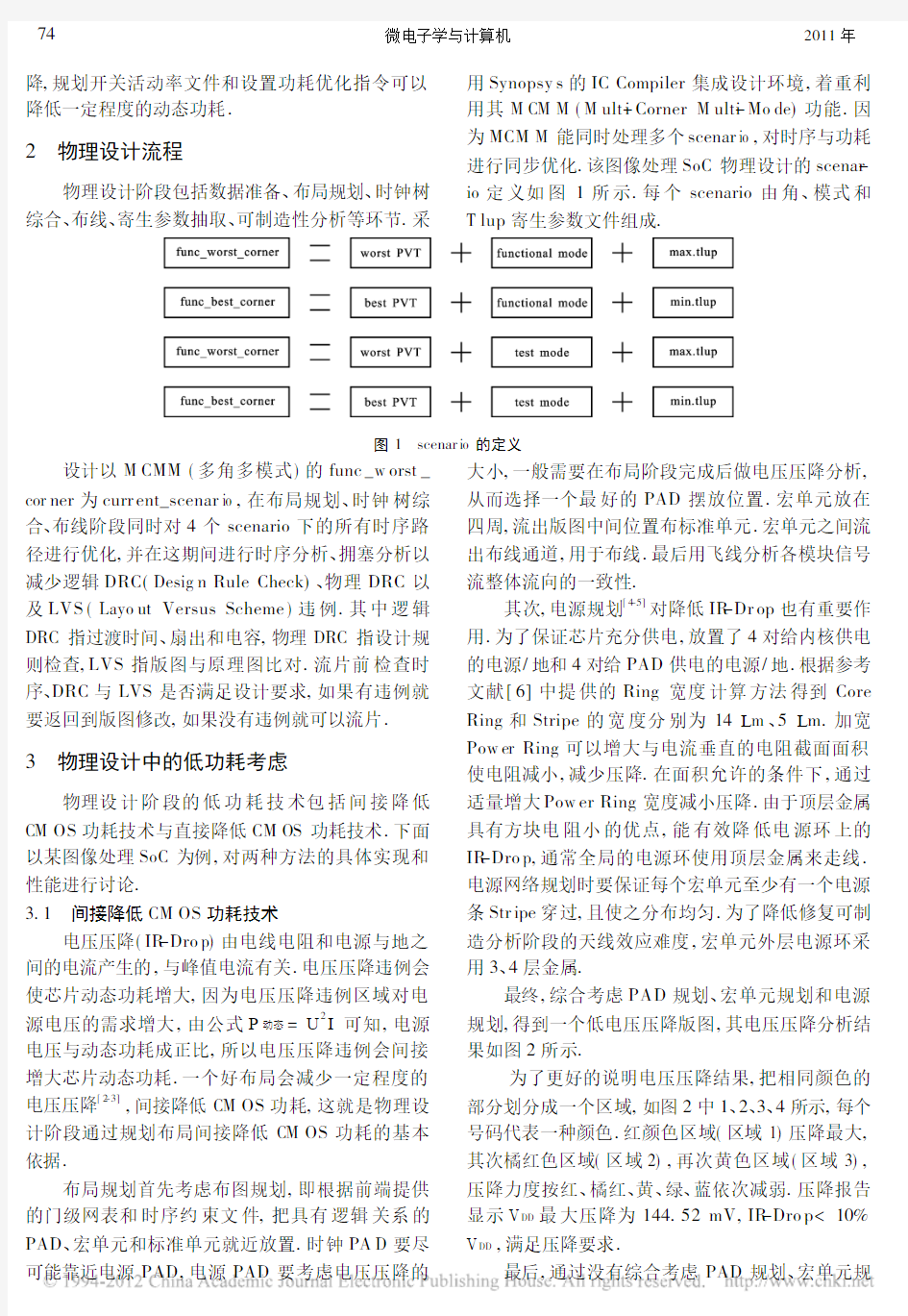

最终,综合考虑PAD 规划、宏单元规划和电源规划,得到一个低电压压降版图,其电压压降分析结果如图2所示.

为了更好的说明电压压降结果,把相同颜色的部分划分成一个区域,如图2中1、2、3、4所示,每个号码代表一种颜色.红颜色区域(区域1)压降最大,其次橘红色区域(区域2),再次黄色区域(区域3),压降力度按红、橘红、黄、绿、蓝依次减弱.压降报告显示V DD 最大压降为144.52mV,IR -Dro p<10%V DD ,满足压降要求.

最后,通过没有综合考虑PAD 规划、宏单元规

74

第4期桑红石,等:

数字集成电路物理设计阶段的低功耗技术

图2电压压降结果示意图

划和电源规划的一般布局与最终布局的对比实验,获得如表1所示数据.

表1各种规划压降与功耗结果

一般布局最终布局电压压降/mV177.8144.5

动态功耗/mW459.9330417.9126

如表1所示,与最终布局相比,一般布局时电压压降增大18.73%,功耗上升8.9%.这些实验数据说明减少电压压降可以间接降低CMOS功耗.

3.2直接降低CM OS功耗技术

CM OS功耗由动态功耗(Dynamic Pow er)和静态功耗(Static Pow er)组成.动态功耗包括电平转换功耗(Net Sw itching Pow er)和内部功耗(Internal Pow er).内部功耗是由于短路电流引起的短路功耗和器件内部电容充电导致的功耗.电平转换功耗是当器件输出端口电平变换时,开关寄生电容充电到V dd或放电到Gro und引起的功耗.物理设计阶段可以通过减少电平转换功耗直接降低CM OS功耗.电平转换功耗用以下公式计算[7]:

P sw=0.5V2DD f clock C load E sw(1)式中,f clock为时钟频率,C load为负载电容,E sw为电平转换参数.从式(1)可以看出,电平转换功耗与供电电压的平方、时钟频率、电容负载、电平转换参数成正比.物理设计阶段使用降低负载电容的方法来降低功耗,降低负载电容可以考虑功耗的布局、基于寄存器的分组的布局优化、变换驱动能力、基于器件连线权重的布局优化、布线后基于抽取的寄生参数的优化.IC Compiler本身具有降低负载电容的功能,通过功耗优化指令的设置实现.具体指令如下所示: set_pow er_o ptions–low_pow er_ placem ent true

placem ent_opt–ar ea_reco very–optimize_ dft–pow er

set_pow er_o ptions–dy namic true

psynopt–area_recov ery-pow er

功耗优化指令的设置必须在规划开关活动率文件基础上进行,因为开关活动率文件定义了高翻转率信号,可以使工具通过减少线电容和门尺寸进行动态功耗优化.ICC读入开关活动率文件后,通过LPP(Low Pow er Placem ent)和GLPO(Gate-level Pow er Optimizatio n),降低一定程度的动态功耗. LPP通过优化与高翻转率线连在一起的单元布局,缩短这些高翻转率连线,从而减小寄生电容.GLPO 通过插入缓冲器、改变门的尺寸、互换引脚等技术减小负载电容.有无设置功耗优化指令的各阶段功耗结果分别如表2、表3所示.表格中功耗单位为m W.

表2未优化的功耗分析结果

内部功耗电平转换功耗总动态功耗布局后255.17317.52572.69

时钟树后163.3320.07183.40

布线后163.4019.18182.58

表3优化后的功耗分析结果

内部功耗电平转换功耗总动态功耗布局后142.30275.61417.91

时钟树后154.3518.06172.41

布线后145.8116.85162.66

表2、表3中分别列举了布局后、时钟树综合后、布线后动态功耗.为了更好地说明设置功耗优化指令后动态功耗有一定程度的下降,表4列举了设置功耗优化指令后各阶段动态功耗下降百分比.这些实验数据证实设置功耗优化指令能够降低CM OS功耗.

表4功耗下降力度表%

内部功耗电平转换功耗总动态功耗布局后44.2313.2027.03

时钟树后 5.509.98 6.01

布线后10.7712.1610.92

4结束语

本文以某图像处理SoC为例阐述了基于标准单元的设计流程中,物理设计阶段的低功耗技术.通过对比采用与未采用该技术的电压压降分析结果与

(下转第80页)

75

微电子学与计算机2011年

缺点:(1)证书文件的管理和分发.使用OPENSSL的API很容易生成自认证证书和密钥,但是有一定的使用期限,这就要求管理员定期对证书文件进行更新再分发.另外没有解决证书的分发问题,目前需要管理手动分发到各通讯进程的主机上.(2)信息编码的支持有一定的局限性.目前只支持ANSI中的ASCII编码.(3)对于分布式部署,应该对负载均衡算法进行进一步研究,保证分布子在不同主机上的相同功能模块的负载平衡.

5结束语

目前该通讯方法已经应用在BIND10服务器软件开发中,能够有效协调进程间通信.同时,该方法的应用不局限于DNS服务器,对于基于多进程的任何项目都可以直接使用.对于支持多种信息编码、以及多种数据类型方面应有所扩展;应考虑使用更智能的方式分发证书文件以及分布式部署的负载平衡问题.

参考文献:

[1]Paul A lbitz,Cr icket Liu.DNS and BIN D[M].5th

Edition.Amer ica:O'Reilly,2006.[2]T atuya Jinmei,Paul V ix ie,Implementat ion and evalua-

tion of moderate parallelism in the BIND9DN S server

[C]//Pr oceeding s o f the annual confer ence o n U SENIX

'06A nnual T echnical Conference.Bo sto n,M A:ACM,

2006:12-20.

[3]Int ernet Systems Co nso rtium(I SC)BIN D[CP/OL].

[2010-05-27].htt p://ww w.isc.o rg/.

[4]BIN D10pro ject[EB/O L].[2010-05-27].ht tp://

bind10.isc.o rg/.

[5]OpenSSL pro ject[EB/OL].(2004)[2010-05-27].

2004.http://ww w.o penssl.o rg/.

[6]Stev ens W R,F enner B,Rndoff A M.U nix网络编程

第1卷:套接口A PI[M].杨继张,译.3版.北京:清华大学出版社,2006.

作者简介:

沈婷婷女,(1985-),硕士研究生.研究方向为计算机网络、DN S服务器的安全与设计开发.

金键男,(1976-),硕士.研究方向为计算机网络系统、互联网寻址技术.

毛伟男,(1968-),研究员,博士生导师.研究方向为下一代互联网技术、资源定位与寻址技术、网络安全技术.

(上接第75页)

功耗报告分析结果,证明了本文所采用方法的有效性,最终实现45.7万门、内核功耗199mW、时钟频率105M H z的So C.

参考文献:

[1]P ayman ZarkeshH a,M eindi James D.Optimum on chip

pow er distr ibution netw or ks for g ig asca le integr ation

[C]//Pr oceeding s o f the IEEE2001International Inter

connect T echno lo gy Conference.Bur ling ame,CA, U SA:IEEE,2001(6):125-127.

[2]田志新,刘勇攀,杨华中,等.基于马尔可夫-蒙特卡洛

采样的电源网络分析[J].微电子学与计算机,2008

(12):1-4.

[3]严晓浪,杨垠丹.超深亚微米集成电路I R-DR OP快速

论证分析的研究[D].杭州:浙江大学,2004.[4]高海霞,张弘.低功耗测试向量产生技术的研究[D].微

电子学与计算机,2009,26(1):213-216.

[5]Chen H ong yu,Wang Q,M o ri M,et.al.Optimal Plan-

ning fo r M esh-Based Po wer Distr ibut ion[C]//Pr o-ceeding s o f the ASP-DA https://www.360docs.net/doc/6a3418224.html, and South Pacific Design A uto mtio n Conference.N J,U SA:IEEE,2004

(1):444-449.

[6]陈春章,艾霞,王国雄.数字集成电路物理设计[M].北

京:科学出版社,2008.

[7]曾晓洋,郭小川.低功耗物理设计[D].北京:中国学位论

文全文数据库,2007.

作者简介:

桑红石女,(1970-),博士,副教授,硕士生导师.研究方向为集成电路.

80

数字集成电路物理设计阶段的低功耗技术

数字集成电路物理设计阶段的低功耗技术 张小花(200XXXXXXXX) 2011年六月 摘要:通过一个图像处理SoC的设计实例,着重讨论在物理设计阶段降低CMOS功耗的方法。该方法首先调整 PAD摆放位置、调整宏单元摆放位置、优化电源规划,得到一个低电压压降版图,间接降低CMOS功耗;接着,通过规划开关活动率文件与设置功耗优化指令,直接降低CMOS功耗。最终实验结果表明此方法使CMOS功耗降低了 10.92%。基于该设计流程的图像处理SoC已经通过ATE设备的测试,并且其功耗满足预期目标。 关键词: 集成电路; 物理设计; 电压降; 低功耗 Digital integrated circuit physical design phase of the low power technology luo jiang nan(2008102041) June, 2011 Abstract: through a image processing of SoC design examples, the paper discuss the physical design stage reduce power consumption method. CMOS This method firstly PAD put the position, adjusting adjustment macro unit put the position, optimizing power planning, get a low voltage pressure drop, reduce the power consumption of the CMOS indirect territory; Then, through the planning activities rate documents and set switch power optimization, reduce the power consumption of the CMOS setup instructions directly. Finally the experimental results show that the method that CMOS power consumption was reduced by 10.92%. Based on the design process of the image processing has been through the ATE the SoC test equipment, and its power consumption to meet expectations. Keywords: IC; physical design; voltage drop; low power consumption 1 引言 随着集成电路规模的扩大以及便携式和嵌入式应用需求的增长,低功耗数字集成电路设计技术日益受到重视,已成为集成电路设计的研究热点.通常低功耗设计技术包括三个方面:设计中的低功耗技术、封装的低功耗技术和运行管理的低功耗技术.其中设计中的低功耗技术包括前端设计阶段的 体系结构级低功耗技术、RTL级低功耗技术、门级低功耗技术和物理设计阶段的低功耗 技术.

集成电路的功耗优化和低功耗设计技术

集成电路的功耗优化和低功耗设计技术 摘要:现阶段各行业的发展离不开对能源的消耗,随着目前节能技术要求的不 断提升,降低功耗成为行业发展的重要工作之一。本文围绕集成电路的功耗优化 以及低功耗设计技术展开分析,针对现阶段常见的低功耗设计方式以及技术进行 探究,为集成电路功耗优化提供理论指导。 关键词:集成电路;功耗优化;低功耗 目前现代节能技术要求不断提升,针对设备的功耗控制成为当前发展的主要问题之一。 针对数字系统的功耗而言,决定了系统的使用性能能否得到提升。一般情况下,数字电路设 计方面,功耗的降低一直都是优先考虑的问题,并且通过对整个结构进行分段处理,同时进 行优化,最后总结出较为科学的设计方案,采用多种方式降低功耗,能够很大程度上提升设 备的使用性能。下面围绕数字电路的功耗优化以及低功耗设计展开分析。 一、设计与优化技术 集成电路的功耗优化和低功耗设计是相对系统的内容,一定要在设计的每个环节当中使 用科学且合理的技术手段,权衡并且综合考虑多方面的设计策略,才能够有效降低功耗并且 确保集成电路系统性能。因为集成电路系统的规模相对较大且具有一定的特殊性,想要完全 依靠人工或者手动的方式来达到这些目的并不现实且缺少可行性,一定要开发与之对应的电 路综合技术。 1 工艺级功耗优化 将工艺级功耗应用到设计当中,通常情况下采取以下两种方式进行功耗的降低: 首先,根据比例调整技术。进行低功耗设计过程中,为了能够实现功耗的有效降低会利 用工艺技术进行改善。在设计过程中,使用较为先进的工艺技术,能够让设备的电压消耗有 效缩减。现阶段电子技术水平不断提升,系统的集成度也随之提高,目前采用的零件的规格 也逐渐缩小,零件的电容也实现了良好的控制,进而能够很大程度上降低功耗。借助比例技术,除了能够将可见晶体管的比例进行调整,而且也能够缩小互连线的比例[1]。目前在晶体 管的比例缩小方面,能够依靠缩小零件的部分重要参数,进而在保持性能不被影响的情况下,通过较小的沟道长度,确保其他的参数不受影响的栅压缩方式,进而将零件的体积进行缩减,同时也缩短了延长的用时,使功耗能够有效降低。针对互连线缩小的方式主要将互连线的整 个结构进行调整,工作人员在进行尺寸缩减的过程中,会面临多方面的难题,比如系统噪音 无法控制,或者降低了电路使用的可靠性等等。 其次,采用封装技术进行降低。采用封装技术,能够让芯片与外部环境进行有效的隔离,进而避免了外部环境给电气设备造成一定的破坏与影响,在封装阶段,芯片的功耗会受到较 大的影响,因此需要使用更加有效的封装手段,才能够提升芯片的散热性,进而有效降低功 耗[2]。在多芯片的情况下,因为芯片与其他芯片之间的接口位置会产生大量的功耗,因此针 对多芯片采取封装技术,首先降低I/0接口的所有功能,接着解决电路延迟的问题,才能够 实现对集成电路的优化。 2 电路功耗优化 一般情况下,对电路级的功耗会选择动态的逻辑设计。在集成电路当中,往往会包含多 种电路逻辑结构,比如动态、静态等等,逻辑结构从本质上而言具有一定的差异性,这种差 异性也使得逻辑结构有着不同作用的功能。动态逻辑结构有着较为典型的特性[3]。静态的逻 辑结构当中所有的输入都会对接单独的MOS,因此逻辑结构功耗更大,动态的逻辑结构当中 电路通常具备N、M两个沟道,动态电路会利用时钟信号采取有效的控制,进而能够实现预

浅谈模拟集成电路自动化设计方案

浅谈模拟集成电路自动化设计方案 发表时间:2015-12-01T10:22:35.073Z 来源:《基层建设》2015年17期供稿作者:马俊 [导读] 广东广晟通信技术有限公司虽然集成电路取得了很好的发展,但是模拟集成电路自动化设计目前仍然处于滞后的阶段,需要我们不断地进行研发和探究。 马俊 广东广晟通信技术有限公司 510515 摘要:随着集成电路技术的不断发展,集成电路设计也取得了很好研究成果。模拟集成电路自动化设计目前主要应用在高精尖的领域内,当前的模拟集成电路自动化技术的研发还不够成熟,远远滞后于集成电路设计,因此需要大力进行模拟集成电路自动化的研发工作,本文将简要的分析一下模拟集成电路自动化的设计方案。 关键词:集成电路;模拟集成电路自动化;设计方案 目前,我国的集成电路产业经过多年的发展,已经形成了较好的产业链,电子市场广阔的需求,使得集成电路设计也和芯片制造业在发展变化中,获取了巨大的经济效益。虽然集成电路取得了很好的发展,但是模拟集成电路自动化设计目前仍然处于滞后的阶段,需要我们不断地进行研发和探究。 一、模拟集成电路自动化设计的特征 集成电路目前主要应用在电子产品领域,电子产品与我们每一个人的生活都息息相关,这些产品正是集成电路的产物,它满足了我们的日常生活、办公、学习的需要,依托集成电路,我们的生活有了质的飞跃。虽然集成电路取得了很好的发展,但是模拟集成电路自动化设计目前仍然处于滞后的阶段,需要我们不断地进行研发和探究。 模拟集成电路的基本电路主要是由电流源、单级放大器、滤波器、反馈电路、电流镜电路等部分组成,根据这些组成部分,我们可以把模拟集成电路再细分为线性集成电路和非线性集成电路两种,线性集成电路的输出、输入信号,有一定的相似性,呈现出了线性关系;非线性集成电路的输出、输入信号不具有相似性,一般是平方关系,所以它呈现出了非线性关系。这两种集成线路共同组成了模拟集成电路。模拟集成电路的自动化设计是将集成电路系统用计算模拟出来,然后通过转换,使之变成符合各项研发指标的电路图的过程,在这个过程中仍有许多流程支持着计算机的模拟转换,例如选择电路拓扑结构、优化器件尺寸、物理版图等等。 模拟集成电路的自动化设计目前发展较为滞后,现阶段对于它的研发探讨主要集中在器件参数优化,以及物理综合方面,通过研究,我们知道是由于哪些原因阻碍了模拟集成电路自动化的研发。首先,模拟集成电路自动化自身存在着一定的缺陷,所以这些缺陷就阻碍了模拟集成电路自动化设计的发展;其次,在设计的过程中,各个流程之间没有一个有效的管理措施,因此对流程点进入和离开的条件缺乏一定的控制;最后,模拟集成电路自动化在设计的过程中需要进行物理检测,每一次都会使原始数据发生变化更新,这种更新就会带来设计问题。所以,这些原因都导致了模拟集成电路自动化设计的滞后。 由于模拟集成电路设计较为复杂,发展较为滞后,所以我们需要对这门技术进行不断地研发,模拟集成电路自动化的设计特征主要有:第一个特征,即性能和结构的抽象表述存在着一定的难度。数字集成电路的设计只要包括系统级、芯片级、门级和版图级等方面,这些方面可以使抽象的电路系统简单的表述出来,但是模拟集成电路自动化就无法完成这一点,它的性能和结构的抽象表述,目前仍然存在着一定的困难,无法很直观的表现出电路系统,因此,这个特征会阻碍模拟集成电路自动化的进一步发展。第二个特征,即抗干扰能力较差。模拟信号在处理的过程中,需要达到一定的速度和精度,因此模拟集成电路自动化在设计的过程对信号的干扰、噪声等因素表现的尤为敏感,一旦发生干扰,模拟集成电路自动化设计就无法顺利进行,所以在设计的过程中,需要充分考虑这些干扰因素对模拟电路设计的影响。模拟集成电路自动化在设计的过程中要考虑芯片面积最小化,也要考虑这些干扰因素对于集成电路的影响作用。第三个特征,即繁杂的性能指标。模拟集成电路自动化在进行行为模拟时会遇到很多繁杂的性能指标,例如功耗指标、低频指标、摆率指标、单位增益频率指标、余度指标、输入输出阻抗指标等等,这些指标内容庞杂,也没有进行统一,它们在一定范围内的性能指标是正确的,但是对于整个模拟集成电路自动化设计而言,这个性能指标是有待商榷的。 二、模拟集成电路自动化设计的具体方案 进行模拟集成电路自动化设计,需要设计它的具体流程,这些流程可以指导我们完成电路自动化设计的方案。 (一)检查流程数据 目前的模拟集成电路自动化设计流程包含很多方面的设计,主要有电路网表综合设计、电路图综合设计、电路综合和优化设计、布局和布线设计等等。为了能够得到准确的模拟电路自动化设计的数据,我们需要检查这些设计的数据,看它的数据能否执行模拟集成电路自动化设计方案的运行。 (二)条件约束 模拟集成电路自动化设计方案的流程检查结束后,接下来就是条件约束,这里的条件约束主要约束的是电路图综合、电路综合、布局和布线、自动布图规划等等,条件约束是模拟集成电路自动化设计方案中的重要一步。以往的数字电路没有采用分析算法分析电路的特点,因此它生成的电路图不能准确地反应电路的结构特征,而模拟集成电路自动化却有效的弥补了这一点,分析了电路的特点,又用必要的约束条件缩小了电路综合和优化时的解空间,这样可以更好的设计出合理的电路。这些约束条件的设计,需要专业的设计人员,这些人员拥有着丰富的设计经验,他们在丰富的知识以及经验的指导下,可以设计出很好的约束条件。 (三)调试修正 条件约束完成后,接下来我们需要进行调试修正。模拟集成电路自动化的调试与修正在电路自动化的设计方案中占据着十分重要的地位,是必不可少的一部分,也是研发的重点之处。调试也就是一个检查的过程,检查之后,根据得到的相关数据来确定是否要进行修改,以及如何进行修改。 调试首先是要检查电路网表和电路图食肉存在错误链接的问题,以及温度的稳定性问题,耗能问题,检查结束之后,我们再根据相应的研究数据进行修正,使电路网表和电路图能够正确的链接,在温度不稳定的情况下,要增加温度进而补偿电路,以及插入低功耗来控制电路;其次我们要检查性能测试电路是否正确、完整,检查出问题之后,我们要进行电路测试;我们还要进行器件组版图的检查,检查他

集成电路设计基础复习

1、解释基本概念:集成电路,集成度,特征尺寸 参考答案: A、集成电路(IC:integrated circuit)是指通过一系列特定的加工工艺,将晶体管、二极管等有源器件和电阻、电容等无源器件,按照一定的电路互连,“集成”在一块半导体晶片(如硅或砷化镓)上,封装在一个外壳内,执行特定电路或系统功能的集成块。 B、集成度是指在每个芯片中包含的元器件的数目。 C、特征尺寸是代表工艺光刻条件所能达到的最小栅长(L)尺寸。 2、写出下列英文缩写的全称:IC,MOS,VLSI,SOC,DRC,ERC,LVS,LPE 参考答案: IC:integrated circuit;MOS:metal oxide semiconductor;VLSI:very large scale integration;SOC:system on chip;DRC:design rule check;ERC:electrical rule check;LVS:layout versus schematic;LPE:layout parameter extraction 3、试述集成电路的几种主要分类方法 参考答案: 集成电路的分类方法大致有五种:器件结构类型、集成规模、使用的基片材料、电路功能以及应用领域。根据器件的结构类型,通常将其分为双极集成电路、MOS集成电路和Bi-MOS 集成电路。按集成规模可分为:小规模集成电路、中规模集成电路、大规模集成电路、超大规模集成电路、特大规模集成电路和巨大规模集成电路。按基片结构形式,可分为单片集成电路和混合集成电路两大类。按电路的功能将其分为数字集成电路、模拟集成电路和数模混合集成电路。按应用领域划分,集成电路又可分为标准通用集成电路和专用集成电路。 4、试述“自顶向下”集成电路设计步骤。 参考答案: “自顶向下”的设计步骤中,设计者首先需要进行行为设计以确定芯片的功能;其次进行结构设计;接着是把各子单元转换成逻辑图或电路图;最后将电路图转换成版图,并经各种验证后以标准版图数据格式输出。 5、比较标准单元法和门阵列法的差异。 参考答案:

专用集成电路

实验一 EDA软件实验 一、实验目的: 1、掌握Xilinx ISE 9.2的VHDL输入方法、原理图文件输入和元件库的调用方法。 2、掌握Xilinx ISE 9.2软件元件的生成方法和调用方法、编译、功能仿真和时序仿真。 3、掌握Xilinx ISE 9.2原理图设计、管脚分配、综合与实现、数据流下载方法。 二、实验器材: 计算机、Quartus II软件或xilinx ISE 三、实验内容: 1、本实验以三线八线译码器(LS74138)为例,在Xilinx ISE 9.2软件平台上完成设计电 路的VHDL文本输入、语法检查、编译、仿真、管脚分配和编程下载等操作。下载芯片选择Xilinx公司的CoolRunner II系列XC2C256-7PQ208作为目标仿真芯片。 2、用1中所设计的的三线八线译码器(LS74138)生成一个LS74138元件,在Xilinx ISE 9.2软件原理图设计平台上完成LS74138元件的调用,用原理图的方法设计三线八线译 码器(LS74138),实现编译,仿真,管脚分配和编程下载等操作。 四、实验步骤: 1、三线八线译码器(LS 74138)VHDL电路设计 (1)三线八线译码器(LS74138)的VHDL源程序的输入 打开Xilinx ISE 6.2编程环境软件Project Navigator,执行“file”菜单中的【New Project】命令,为三线八线译码器(LS74138)建立设计项目。项目名称【Project Name】为“Shiyan”,工程建立路径为“C:\Xilinx\bin\Shiyan1”,其中“顶层模块类型(Top-Level Module Type)”为硬件描述语言(HDL),如图1所示。 图1 点击【下一步】,弹出【Select the Device and Design Flow for the Project】对话框,在该对话框内进行硬件芯片选择与工程设计工具配置过程。

对半导体技术、微电子技术、集成电路技术三者的浅略认识

对半导体技术、微电子技术、集成电路技术三者的浅略认识 一、半导体技术、微电子技术、集成电路技术三者的联系与区别 我们首先从三者的概念或定义上来分别了解一下这三种技术。 半导体技术就是以半导体为材料,制作成组件及集成电路的技术。在电子信息方面,绝大多数的电子组件都是以硅为基材做成的,因此电子产业又称为半导体产业。半导体技术最大的应用便是集成电路,它们被用来发挥各式各样的控制功能,犹如人体中的大脑与神经。 微电子技术是随着集成电路,尤其是超大型规模集成电路而发展起来的一门新的技术,是建立在以集成电路为核心的各种半导体器件基础上的高新电子技术,为微电子学中的各项工艺技术的总和。 集成电路技术,在电子学中是一种把电路小型化的技术。采用一定的工艺,把一个电路中所需的各种电子元件及布线互连一起,制作在一小块或几小块半导体晶片或介质基片上,然后封装在一个管壳内,成为具有所需电路功能的微型结构。(以上三者概念均来源于网络)这般看来,三者概念上互相交叉,却也略有区别。依我这个初次接触这三个名词、对电子信息几乎一窍不通的大一新生来看,半导体技术是其他二者技术的基础,因为半导体是承载整个电子信息的基石,不管是微电子还是集成电路,便是以半导体为材料才可以建造、发展。而微电子技术,个人感觉比较广泛,甚至集成电路技术可以包含在微电子技术里。除此之外,诸如小型元件,如纳米级电子元件制造技术,都可以归为微电子技术。而集成电路技术概念上比较狭窄,单单只把电路小型化、集成化技术,上面列举的小型元件制造,便不能归为集成电路技术,但可以归为微电子技术。以上便是鄙人对三者概念上、应用上联系与区别的区区之见,如有错误之处还望谅解。 二、对集成电路技术的详细介绍 首先我们了解一下什么是集成电路。 集成电路是一种微型电子器件或部件。人们采用一定的工艺,把一个电路中所需的各种元件及布线互连一起,制作在一小块或几小块半导体晶片或介质基片上,然后封装在一个管壳内,成为具有所需电路功能的微型结构。其中所有元件在结构上已组成一个整体,使电子元件向着微小型化、低功耗、智能化和高可靠性方面迈进了一大步。它在电路中用字母“IC”表示。当今半导体工业大多数应用的是基于硅的集成电路。集成电路具有体积小,重量轻,引出线和焊接点少,寿命长,可靠性高,性能好等优点,同时成本低,便于大规模生产。 而简单来说,集成电路技术便是制造集成电路的技术方法。它涉及半导体器件物理、微电子学、电子学、无线电、光学以及信息学等学科领域的知识。 从产业分工角度,集成电路技术可以分为集成电路加工技术、集成电路测试封装技术以及集成电路设计技术等几方面。 1. 集成电路加工技术 集成电路加工技术主要是通过物理或化学手段在硅材料上生成半导体器件(比如场效应管)以及器件之间的物理互连。这些器件以及器件之间的互连构成的电路功能要符合系统设计要求。集成电路加工技术涉及的知识包括半导体器件物理、精密仪器、光学等领域,具体应用在工艺流程中,包括注入、掺杂、器件模型、工艺偏差模型、成品率分析以及工艺过程设计等。在近十几年的时间里,集成电路加工工艺水平一直按照摩尔(Moore)定律在快速发展。 2.集成电路测试、封装技术 集成电路测试包括完成在硅基上产生符合功能要求的电路后对裸片硅的功能和性能的

常用低功耗设计

随着半导体工艺的飞速发展和芯片工作频率的提高,芯片的功耗迅速增加,而功耗增加又将导致芯片发热量的增大和可靠性的下降。因此,功耗已经成为深亚微米集成电路设计中的一个非常重要的考虑因素。为了使产品更具有竞争力,工业界对芯片设计的要求已从单纯的追求高性能、小面积,转换为对性能、面积、功耗的综合要求。微处理器作为数字系统的核心部件,其低功耗设计对降低整个系统的功耗具有非常重要的意义。 本文首先介绍了微处理器的功耗来源,重点介绍了常用的低功耗设计技术,并对今后低功耗微处理器设计的研究方向进行了展望。 1 微处理器的功耗来源 研究微处理器的低功耗设计技术,首先必须了解其功耗来源。高层次仿真得出的结论如图1所示。 从图1中可以看出,时钟单元(Clock)功耗最高,因为时钟单元有时钟发生器、时钟驱动、时钟树和钟控单元的时钟负载;数据通路(Datapath)是仅次于时钟单元的部分,其功耗主要来自运算单元、总线和寄存器堆。除了上述两部分,还有存储单元(Mem ory),控制部分和输入/输出 (Control,I/O)。存储单元的功耗与容量相关。 如图2所示,C MOS电路功耗主要由3部分组成:电路电容充放电引起的动态功耗,结反偏时漏电流引起的功耗和短路电流引起的功耗。其中,动态功耗是最主要的,占了总功耗的90%以上,表达式如下: 式中:f为时钟频率,C1为节点电容,α为节点的翻转概率,Vdd为工作电压。

2 常用的低功耗设计技术 低功耗设计足一个复杂的综合性课题。就流程而言,包括功耗建模、评估以及优化等;就设计抽象层次而言,包括自系统级至版图级的所有抽象层次。同时,功耗优化与系统速度和面积等指标的优化密切相关,需要折中考虑。下面讨论常用的低功耗设计技术。 2.1 动态电压调节 由式(1)可知,动态功耗与工作电压的平方成正比,功耗将随着工作电压的降低以二次方的速度降低,因此降低工作电压是降低功耗的有力措施。但是,仅仅降低工作电压会导致传播延迟加大,执行时间变长。然而,系统负载是随时间变化的,因此并不需要微处理器所有时刻都保持高性能。动态电压调节DVS (Dynarnic Voltage Scaling)技术降低功耗的主要思路是根据芯片工作状态改变功耗管理模式,从而在保证性能的基础上降低功耗。在不同模式下,工作电压可以进行调整。为了精确地控制DVS,需要采用电压调度模块来实时改变工作电压,电压调度模块通过分析当前和过去状态下系统工作情况的不同来预测电路的工作负荷。 2.2 门控时钟和可变频率时钟 如图1所示,在微处理器中,很大一部分功耗来自时钟。时钟是惟一在所有时间都充放电的信号,而且很多情况下引起不必要的门的翻转,因此降低时钟的开关活动性将对降低整个系统的功耗产牛很大的影响。门控时钟包括门控逻辑模块时钟和门控寄存器时钟。门控逻辑模块时钟对时钟网络进行划分,如果在当前的时钟周期内,系统没有用到某些逻辑模块,则暂时切断这些模块的时钟信号,从而明显地降低开关功耗。图3为采用“与”门实现的时钟控制电路。门控寄存器时钟的原理是当寄存器保持数据时,关闭寄存器时钟,以降低功耗。然而,门控时钟易引起毛刺,必须对信号的时序加以严格限制,并对其进行仔细的时序验证。 另一种常用的时钟技术就是可变频率时钟。根据系统性能要求,配置适当的时钟频率,避免不必要的功耗。门控时钟实际上是可变频率时钟的一种极限情况(即只有零和最高频率两种值),因此,可变频率时钟比门控时钟技术更加有效,但需要系统内嵌时钟产生模块PLL,增加了设计复杂度。去年Intel公司推出的采用先进动态功耗控制技术的Montecito处理器,就利用了变频时钟系统。该芯片内嵌一个高精度数字电流表,利用封装上的微小电压降计算总电流;通过内嵌的一个32位微处理器来调整主频,达到64级动态功耗调整的目的,大大降低了功耗。

集成电路物理设计库

1.集成电路物理设计库 集成电路物理设计库(PDK 和标准单元库)作为芯片制造商、EDA 供应商、芯片设计者之间的桥梁。开发工作必备的资源较多:工艺信息、集成电路设计方法和 EDA 技术。从 2006 年开始,电子设计平台与共性技术研究室基于中芯国际、上海宏力、上海华虹的 65nm、90nm、 0.13um 和 0.35um 等工艺节点,开发出一系列功能完善、器件类型丰富、设计合理及参数正确的 PDK 和标准单元库,并建立了相应的设计参考流程。 在实现 PDK 完整功能的基础上,相关研发团队从设计者角度优化参数化单元的 CDF 参数,并采用结构化的方式开发 Pcell 和批处理方式验证 Pcell,保证了开发流程的高效性和可靠性。同时,对标准单元进行了 OPC 校正,移向掩膜分析(PSM),分辨率增强(RET)等 DFM 优化分析;光学模拟仿真结果证实了优化后的标准单元边缘放置误差(EPE)平均减小了 5%,即优化后的标准单元库具有更高的可靠性、准确性和可制造性。经过验证,每套 PDK 和标准单元库都能灵活准确的支持电路设计。能够根据芯片设计者的需求提供专业PDK 设计服务和芯片设计技术支持。在此基础上,建立了一套完善的设计开发流程。 电子设计平台与共性技术研究室开发的集成电路物理设计库的工艺设计包(PDK:Process Design Kit)应用于数模混合 IC 设计,其包含的内容是和全定制流程紧密结合在一起的。PDK 库主要包括以下内容:

(1)器件模型(Device Model):由 Foundry 提供的仿真模型文件; (2)Symbols & View:用于原理图设计的符号,参数化的设计单元都通过了 SPICE 仿真的验证; (3)组件描述格式(CDF:Component Description Format) & Callback:器件的属性描述文件,定义了器件类型、器件名称、器件参数及参数调用关系函数集 Callback、器件模型、器件的各种视图格式等; (4)参数化单元(Pcell:Parameterized Cell):它由 Cadence 的 SKILL 语言编写,其对应的版图通过了 DRC 和 LVS 验证,方便设计人员进行原理图驱动的版图(SDL:Schematic Driven Layout)设计流程; (5)技术文件(Technology File):用于版图设计和验证的工艺文件,包含 GDSII 的设计数据层和工艺层的映射关系定义、设计数据层的属性定义、在线设计规则、电气规则、显示色彩定义和图形格式定义等; (6)物理验证规则文件(PV Rule File):包含版图验证文件集(DRC/LVS/RC)。 而集成电路物理设计库的标准单元库应用于大规模数字 IC 设计,从前端功能仿真到后端版图实现支撑着整个数字 IC 设计流程。标准单元库研究的主要内容包括: (1)网表信息文件:包含标准单元的器件尺寸和节点连接关系。

专用集成电路AD的设计

A/D转换器的设计 一.实验目的: (1)设计一个简单的LDO稳压电路 (2)掌握Cadence ic平台下进行ASIC设计的步骤; (3)了解专用集成电路及其发展,掌握其设计流程; 二.A/D转换器的原理: A/D转换器是用来通过一定的电路将模拟量转变为数字量。 模拟量可以是电压、电流等电信号,也可以是压力、温度、湿度、位移、声音等非电信号。但在A/D转换前,输入到A/D转换器的输入信号必须经各种传感器把各种物理量转换成电压信号。符号框图如下: 数字输出量 常用的几种A/D器为; (1):逐次比较型 逐次比较型AD由一个比较器和DA转换器通过逐次比较逻辑构成,从MSB 开始,顺序地对每一位将输入电压与内置DA转换器输出进行比较,经n次比较而输出数字值。其电路规模属于中等。其优点是速度较高、功耗低,在低分辩率(<12位)时价格便宜,但高精度(>12位)时价格很高。 (2): 积分型 积分型AD工作原理是将输入电压转换成时间(脉冲宽度信号)或频率(脉冲频率),然后由定时器/计数器获得数字值。其优点是用简单电路就能获得高分辨率,但缺点是由于转换精度依赖于积分时间,因此转换速率极低。初期的单片AD转换器大多采用积分型,现在逐次比较型已逐步成为主流。 (3):并行比较型/串并行比较型

并行比较型AD采用多个比较器,仅作一次比较而实行转换,又称FLash(快速)型。由于转换速率极高,n位的转换需要2n-1个比较器,因此电路规模也极大,价格也高,只适用于视频AD转换器等速度特别高的领域。 串并行比较型AD结构上介于并行型和逐次比较型之间,最典型的是由2个n/2位的并行型AD转换器配合DA转换器组成,用两次比较实行转换,所以称为Half flash(半快速)型。还有分成三步或多步实现AD转换的叫做分级型AD,而从转换时序角度又可称为流水线型AD,现代的分级型AD中还加入了对多次转换结果作数字运算而修正特性等功能。这类AD速度比逐次比较型高,电路规模比并行型小。 一.A/D转换器的技术指标: (1)分辨率,指数字量的变化,一个最小量时模拟信号的变化量,定义为满刻度与2^n的比值。分辨率又称精度,通常以数字信号的位数来表示。 (2)转换速率,是指完成一次从模拟转换到数字的AD转换所需的时间的倒数。积分型AD的转换时间是毫秒级属低速AD,逐次比较型AD是微秒级,属中速AD,全并行/串并行型AD可达到纳秒级。采样时间则是另外一个概念,是指两次转换的间隔。为了保证转换的正确完成,采样速率必须小于或等于转换速率。因此有人习惯上将转换速率在数值上等同于采样速率也是可以接受的。常用单位ksps 和Msps,表示每秒采样千/百万次。 (3)量化误差,由于AD的有限分辩率而引起的误差,即有限分辩率AD的阶梯状转移特性曲线与无限分辩率AD(理想AD)的转移特性曲线(直线)之间的最大偏差。通常是1 个或半个最小数字量的模拟变化量,表示为1LSB、1/2LSB。(4)偏移误差,输入信号为零时输出信号不为零的值,可外接电位器调至最小。(5)满刻度误差,满度输出时对应的输入信号与理想输入信号值之差。 (6)线性度,实际转换器的转移函数与理想直线的最大偏移,不包括以上三种误差。 三、实验步骤 此次实验的A/D转换器用的为逐次比较型,原理图如下:

低功耗电路设计

便携式产品低功耗电路设计的综合考虑 集成电路和计算机系统的发展对低功耗的要求越来越高 分析了功耗产生的主要原因以及与成本的关系 如今为了适应这一变化 低功率逻辑电路的标准被定义为每一级门电路功耗小于1.3uW/MHz最终用户认为 对于总体系统设计来说这是电子工业发展的必然趋势更轻和功能更强大的最终产品 从功率观点看设计任务将变得更加艰巨 就是单个或一组充电电池能维持设备连续几天的工作 另外绿色所有政府部门采购的台式电脑必须符合功耗要求 VLSI技术公司移动产品部销售经理Barta指出深绿色 这些机器将挂起所有操作直到被相关激励信号唤醒后才进入正常运行模式 ARPA?y?ú??μí1|?êμ?×óáìóò×÷é?è??D?? ê1D?ò?′úμ?×ó?μí3μ?1|o?????μíóú??óD?μí3μ?1|o? ?÷?tμ??′1üàíμè?÷??áìóò?Dμ??è????ê? òò?a?aá???áìóòé??°′óá?μ??ìo?D?o?′|àí 随着每隔几年电路密度的成倍增大难度越来越大 LSI逻辑公司ASIC市场部副总裁Koc说200k门数的芯片 这么大的功率已经远远超过了封装的散热能力 因为高温工作会给集成电路带来可靠性和功能性问题 与温度有关的这些故障模型包括工作器件故障以及电流密度 低功率应用 在电池供电模式下由于受便携式电脑的实际尺寸和重量限制也限制了电池的大小和重量

低功率系统的另一个例子是蜂窝电话模拟电路 电池在充电一次后接收模式下工作一整天 一般来说而现在系统设计都将功耗作为其中的一项重要性能指标 同时也带来功耗问题但利用适当的功率控制方法或创新性设计可以获得多种解决方案 首先则速度越慢 会减小电容充放电的电流或负载驱动电流较低的电压将导致较低的输出功率或较低的信号幅度 产生功耗的原因 整体的功耗取决于诸多因素封装密度产品性能和供电电压往往速度越高功耗越大 它通常由负载器件和寄生元件产生 在电阻性负载电路如模拟电路中更是如此 电路中的导线(金属导线)和层间寄生电阻会产生静态阻抗功耗 有源器件的正常工作模式可用一条转移曲线和某些I-V特性来描述 适用于全部有源器件对无源和有源器件来说 在CMOS电路中I-V转移曲线是一个瞬态函数 从一个状态转移到另一个状态不消耗功率转移曲线并不是理想的方形理论上看 具有零内阻的开关器件会在电源与地之间形成直接短路的现象 最大的功耗来自于内部和外部电容的充放电 据此 峰值电流I=C(V/T)T是上升或下降沿时间因此峰值电流通常都比较大此时C 是指输出端的负载电容F则是开关频率 所需要的电源电压也越高由此产生的影响涉及到电源总线母板布线另外 因此可能会影响到系统的总体封装

数字集成电路低功耗物理实现技术与UPF

数字集成电路低功耗物理实现技术与UPF 孙轶群sun.yiqun@https://www.360docs.net/doc/6a3418224.html, 国民技术股份有限公司 Nationz Technologies Inc 摘要 本文从CMOS电路功耗原理入手,针对不同工艺尺寸下数字集成电路的低功耗物理实现方法进行描述,并着重描述了Synopsys UPF(Unified Power Format)对低功耗设计的描述方法。UPF是Synopsys公司提出的一种对芯片中电源域设计进行约束的文件格式。通过与UPF 格式匹配的Liberty文件,UPF约束文件可以被整套Galaxy物理实现平台的任何一个环节直接使用,并将设计者的电源设计约束传递给设计工具,由工具完成设计的实现工作,从而实现整套数字集成电路低功耗物理实现的流程。 1.0 概述 本文从数字集成电路低功耗设计原理下手,对设计中低功耗的实现技术进行描述,包括完成低功耗设计需要的库资料以及常用EDA工具对低功耗技术实现的方法。 2.0 CMOS电路的低功耗设计原理 CMOS电路功耗主要分3种,静态功耗主要与工艺以及电路结构相关,短路电流功耗主要与驱动电压、p-MOS和n-MOS同时打开时产生的最大电流、翻转频率以及上升、下降时间有关,开关电流功耗主要与负载电容、驱动电压、翻转频率有关。做低功耗设计,就必须从这些影响功耗的因素下手。 3.0 低功耗设计手段及Library需求 低功耗的设计手段较为复杂,但对于不同的设计,或者不同的工艺,实现的方法却各不相同。 3.1 0.18um及以上工艺 0.18um及以上工艺,在低功耗设计手段上较为有限,主要原因在于,静态功耗很小,基本不用关心。 动态功耗方面,主要的功耗来自于Switching Power,即与负载电容、电压以及工作中的信号翻转频率相关。 减小负载电容,就必须在设计上下功夫,减少电路规模。减少信号翻转频率,除了降低时钟频率外,只有在设计上考虑,能不翻转的信号就不翻转。至于电压,由于0.18um及以上工艺的阈值电压有一定的限制,因此,供电电压降低,势必影响工作频率。 一般说来,在0.18um工艺下设计电路,主要有以下几种对低功耗设计的考虑。 3.1.1 静态功耗可以忽略 根据现有项目经验可知,利用0.18um工艺Standard Cell设计出来的某芯片,数字逻辑加上Ram和Rom约40万门的电路,在完全静止的状态下,功耗约200uA左右(实测数据为400uA 左右,包括了50uA Flash,30uA的PHY,113uA的VR,其他模拟部分漏电不大,因此这里估算为200uA)。这样的功耗,我们是可以接受的。如果非要减少静态功耗,则可以参照90nm工艺的设计思路,专门设计高阈值电压的MOSFET,或者专门设计切断电源所需的元件,但由此带来设计的复杂性,对0.18um工艺的影响还是很大的。如果设计规模没有那么大,且可以满足应用,往往还是可以忽略这个结果的。 3.1.2 时钟门控减小不必要的动态功耗 在寄存器的电路设计中,时钟输入端都会有一个反向器负载,就算输入端不发生变化,时钟的变化也会造成该反向器的变化,由此产生动态功耗。因此在如果该寄存器输入在某种条件下等于输出(即输出保持)时,可以将时钟门控住,以减少无效的时钟翻转。 时钟门控的实现原理如下图所示:

集成电路设计实习Integrated

集成电路设计实习Integrated Circuits Design Labs I t t d Ci it D i L b 单元实验一(第一次课) 基本门电路设计--电路仿真 2006-2007 Institute of Microelectronics Peking University

实验内容 z实验内容: z完成CMOS反相器的电路设计 z实验目的 z掌握基本门电路的设计方法 z熟悉Cadence的设计数据管理结构,以及定制设计的原理图输入、电路仿真、版图设计、版图验证工具的使用 z提示: z电路结构和优化设计可以参考《CMOS VLSI分析与设计》 Institute of Microelectronics, Peking University集成电路设计实习-单元实验一Page2

反相器的设计 z设计目的:基于csmc05工艺,完成一个具有逻辑反相功能的电路z设计要求: z1、反相器的逻辑阈值在Vdd/2附近,即噪声容限最大 z2、反相器的版图高度限制为24微米,电源和地线宽度各为2微米 z3、反相器宽度限制为mos器件不折栅 z4、为了给顶层设计留出更多的布线资源,版图中只能使用金属1 和多晶硅作为互连线,输入,输出和电源、地线等pin脚必须使用 金属1 z5、版图满足设计规则要求,并通过LVS检查 z6、为了满足以后复杂门电路设计的需要,要求反相器版图满足上、下、左、右并置排列的时候不违反设计规则 Institute of Microelectronics, Peking University集成电路设计实习-单元实验一Page3

集成电路低功耗设计方法研究【文献综述】

毕业设计文献综述 电子信息科学与技术 集成电路低功耗设计方法研究 摘要:随着IC制造工艺达到纳米级,功耗问题已经与面积、速度一样受到人们关注,并成为制约集成电路发展的关键因素之一。同时,由于电路特征尺寸的缩小,之前相比于电路动态功耗可以忽略的静态漏功耗正不断接近前者,给电路低功耗设计提出了新课题,即低漏功耗设计。本文将分析纳米工艺下芯片功耗的组成和对低漏功耗进行研究的重要性,然后介绍目前主要的低功耗设计方法。此外,由于ASIC技术是目前集成电路发展的趋势和技术主流,而标准单元是ASIC设计快速发展的重要支撑,本文在最后提出了标准单元包低漏功耗设计方法,结合电路级的功耗优化技术,从而拓宽ASIC功耗优化空间。 关键字:低功耗,标准单元,ASIC设计 前言: 自1958年德克萨斯仪器公司制造出第一块集成电路以来,集成电路产业一直以惊人的速度发展着,到目前为止,集成电路基本遵循着摩尔定律发展,即集成度几乎每18个月翻一番。 随着制造工艺的发展,IC设计已经进入了纳米级时代:目前国际上能够投入大规模量产的最先进工艺为40nm,国内的工艺水平正将进入65nm;2009年,Intel酷睿i系列创纪录采用了领先的32nm 工艺,并且下一代22nm工艺正在研发中。但伴随电路特征尺寸的减小,电路功耗数值正呈指数上升,集成电路的发展遭遇了功耗瓶颈。功耗问题已经同面积和速度一样受到人们重视,成为衡量IC设计成功与否的重要指标之一。若在设计时不考虑功耗而功利地追求集成度的提高,则可能会使电路某些部分因功耗过大引起温度过高而导致系统工作不稳定或失效。如Intel的1.5GHz Pentium Ⅳ处理器,拥有的晶体管数量高达4200万只,功率接近95瓦,整机生产商不得不为其配上了特大号风扇来维持其正常工作。功耗的增大不仅将导致器件的可靠性降低、芯片的稳定性下降,同时也给芯片的散热和封装带来问题。因此,功耗已经成为阻碍集成电路进一步发展的难题之一,低功耗设计也已成为集成电路的关键设计技术之一。 一、电路功耗的组成 CMOS电路中有两种主要的功耗来源,动态功耗和静态功耗。其中,动态功耗包括负载电容的充放电功耗(交流开关功耗)和短路电流引起的功耗;静态功耗主要是由漏电流引起的功耗,如图1所示。

集成电路设计基础 课后答案

班级:通信二班姓名:赵庆超学号:20071201297 7,版图设计中整体布局有哪些注意事项? 答:1版图设计最基本满足版图设计准则,以提高电路的匹配性能,抗干扰性能和高频工作性能。 2 整体力求层次化设计,即按功能将版图划分为若干子单元,每个子单元又可能包含若干子单元,从最小的子单元进行设计,这些子单元又被调用完成较大单元的设计,这种方法大大减少了设计和修改的工作量,且结构严谨,层次清晰。 3 图形应尽量简洁,避免不必要的多边形,对连接在一起的同一层应尽量合并,这不仅可减小版图的数据存储量,而且版图一模了然。 4 在构思版图结构时,除要考虑版图所占的面积,输入和输出的合理分布,较小不必要的寄生效应外,还应力求版图与电路原理框图保持一致(必要时修改框图画法),并力求版图美观大方。 8,版图设计中元件布局布线方面有哪些注意事项? 答:1 各不同布线层的性能各不相同,晶体管等效电阻应大大高于布线电阻。高速电路,电荷的分配效应会引起很多问题。 2 随器件尺寸的减小,线宽和线间距也在减小,多层布线层之间的介质层也在变薄,这将大大增加布线电阻和分布电阻。 3 电源线和地线应尽可能的避免用扩散区和多晶硅布线,特别是通过

较大电流的那部分电源线和地线。因此集成电路的版图设计电源线和地线多采用梳状布线,避免交叉,或者用多层金属工艺,提高设计布线的灵活性。 4 禁止在一条铝布线的长信号霞平行走过另一条用多晶硅或者扩散区布线的长信号线。因为长距离平行布线的两条信号线之间存在着较大的分布电容,一条信号线会在另一条信号线上产生较大的噪声,使电路不能正常工作。、 5 压点离开芯片内部图形的距离不应少于20um,以避免芯片键和时,因应力而造成电路损坏。

专用集成电路设计

专用集成电路课程设计 简易电子琴 通信工程学院 011051班 侯珂

01105023 目录 1 引言 (1) 1.1设计的目的 (1) 1.2设计的基本内容 (2) 2 EDA、VHDL简介 (2) 2.1EDA技术 (2) 2.2硬件描述语言——VHDL (3) 2.2.1 VHDL的简介 (3) 2.2.2 VHDL语言的特点 (3) 2.2.3 VHDL的设计流程 (4) 3 简易电子琴设计过程 (5) 3.1简易电子琴的工作原理 (5) 3.2简易电子琴的工作流程图 (5) 3.3简易电子琴中各模块的设计 (6) 3.3.1 乐曲自动演奏模块 (7) 3.3.2 音调发生模块 (8) 3.3.3 数控分频模块 (9)

3.3.4 顶层设计 (10) 4 系统仿真 (12) 5 结束语 (14) 收获和体会.................................................................................................. 错误!未定义书签。参考文献 .. (15) 附录 (16)

1 引言 我们生活在一个信息时代,各种电子产品层出不穷,作为一个计算机专业的学生,了解这些电子产品的基本组成和设计原理是十分必要的,我们学习的是计算机组成的理论知识,而课程设计正是对我们学习的理论的实践与巩固。本设计主要介绍的是一个用超高速硬件描述语言VHDL设计的一个具有若干功能的简易电子琴,其理论基础来源于计算机组成原理的时钟分频器。 摘要本系统是采用EDA技术设计的一个简易的八音符电子琴,该系统基于计算机中时钟分频器的原理,采用自顶向下的设计方法来实现,它可以通过按键输入来控制音响。系统由乐曲自动演奏模块、音调发生模块和数控分频模块三个部分组成。系统实现是用硬件描述语言VHDL按模块化方式进行设计,然后进行编程、时序仿真、整合。本系统功能比较齐全,有一定的使用价值。 关键字电子琴、EDA、VHDL、音调发生 1.1 设计的目的 本次设计的目的就是在掌握计算机组成原理理论的基础上,了解EDA技术,掌握VHDL硬件描述语言的设计方法和思想,通过学习的VHDL语言结合电子电路的设计知识理论联系实际,掌握所学的课程知识,例如本课程设计就是基于所学的计算机原理中的时钟分频器和定时器的基础之上的,通过本课程设计,达到巩固和综合运用计算机原理中的知识,理论联系实际,巩固所学理论知识,并且提高自己通过所学理论分析、解决计算机实际问题的能力。