Proteusg画PCB教程

一个小小的电路板,画得真累,也是第一次使用它画PCB,不怎么熟悉操作。

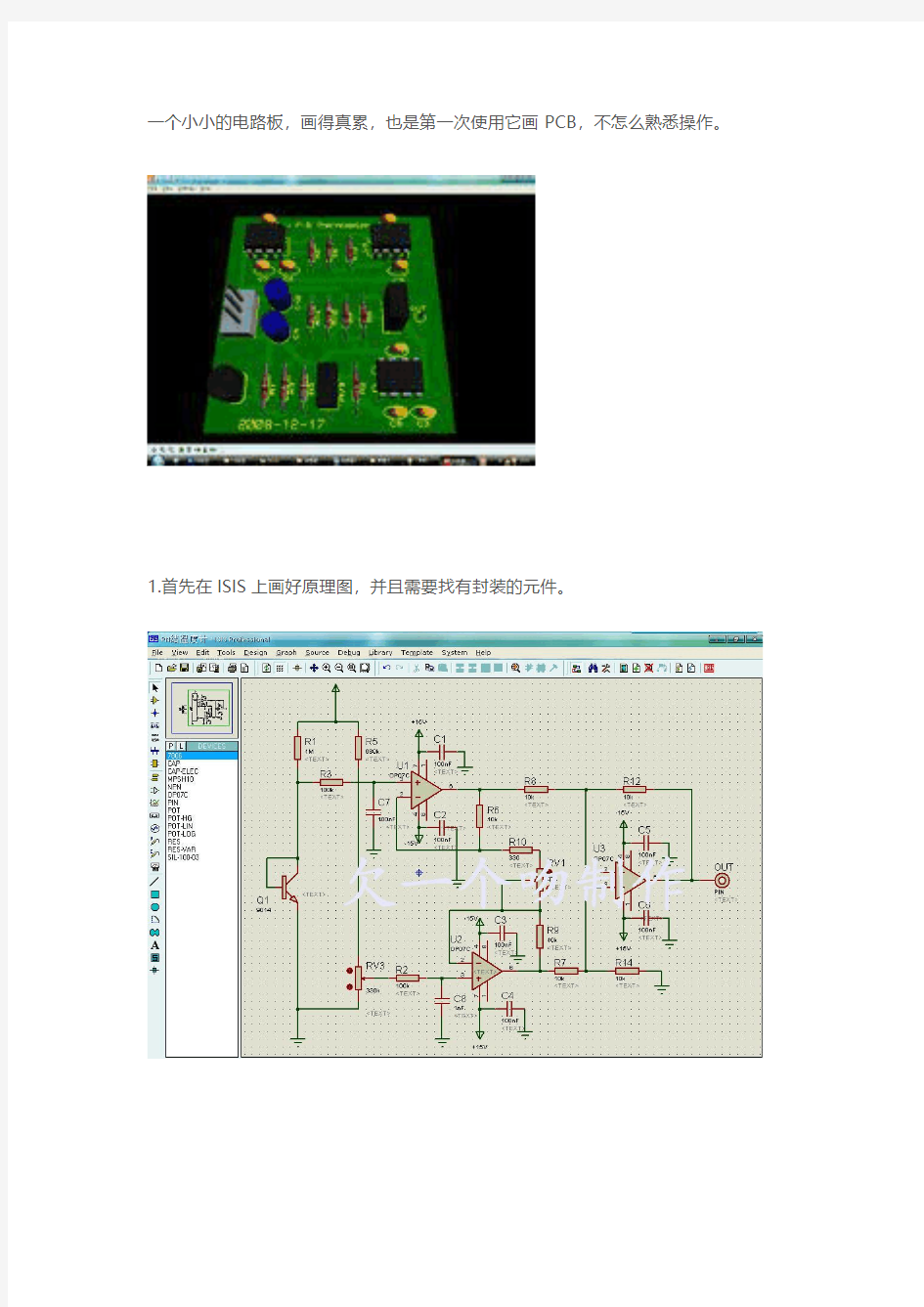

1.首先在ISIS上画好原理图,并且需要找有封装的元件。

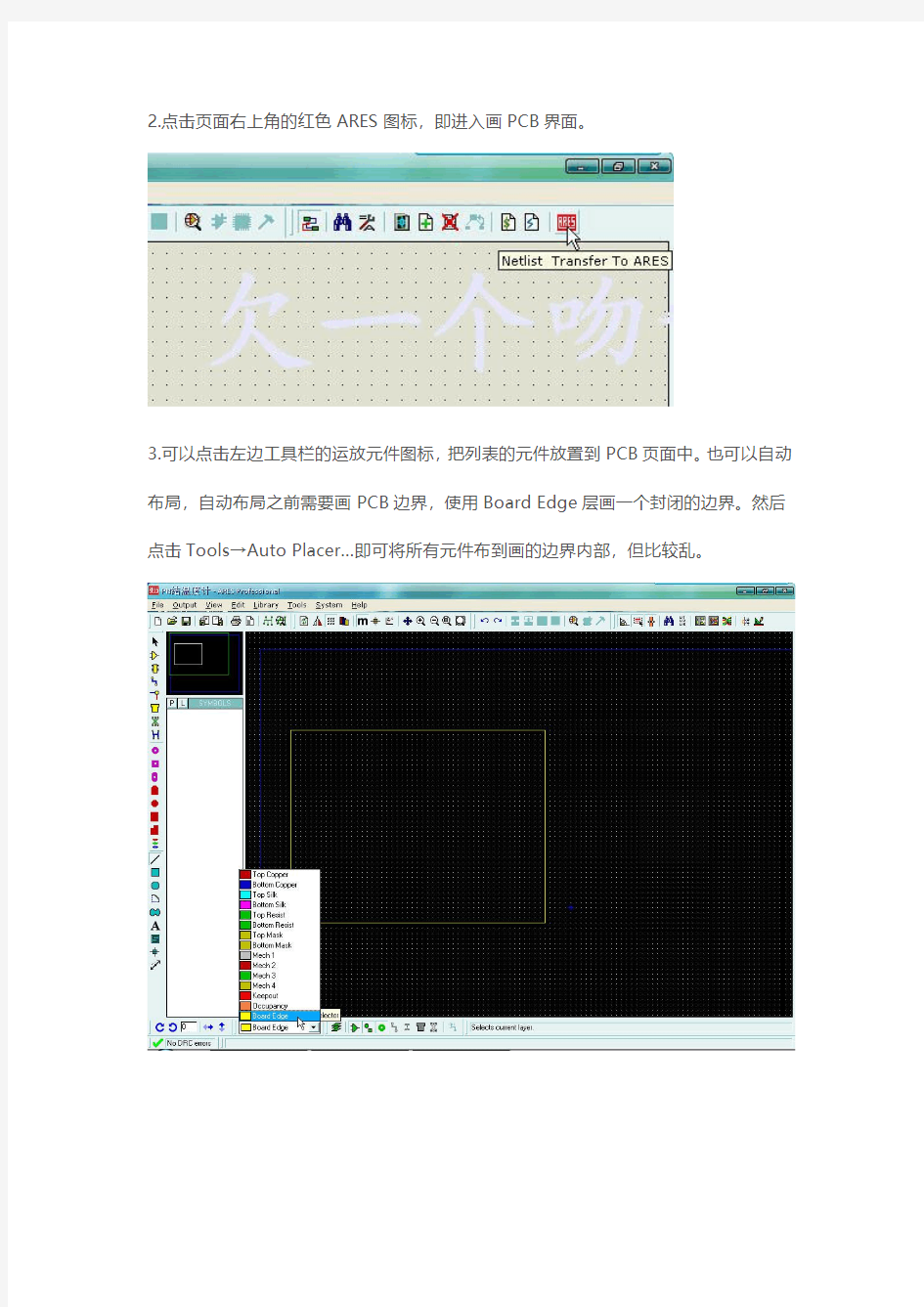

2.点击页面右上角的红色ARES图标,即进入画PCB界面。

3.可以点击左边工具栏的运放元件图标,把列表的元件放置到PCB页面中。也可以自动布局,自动布局之前需要画PCB边界,使用Board Edge层画一个封闭的边界。然后点击Tools→Auto Placer…即可将所有元件布到画的边界内部,但比较乱。

4.自动布局后:

5.手动布局完毕后点击Tools→Auto Router…弹出设置布线规则,详细设置点击Edit Strategies

6.自动布线后如下图。

7.如果要撤销所有布线,我还没有找到那个工具,但可以点击页面下方的一栏工具,选择元件、导线、焊盘等点击无效操作,将除导线和过孔外的其它屏蔽后就可以选中这个

PCB,这时只能选择导线,就可以全部删除了。

8.画好的PCB

9.3D仿真效果,它的3D还挺逼真。

Cadence画PCB简单快速教程

Cadence的简单快捷PCB画法 一.原理图 1.建立工程 与其他绘图软件一样,OrCAD以Project来管理各种设计文件。点击开始菜单,然后依次是所有程序—打开cadence软件—》一般选用Design Entry CIS,点击Ok进入Capture CIS。接下来是File--New--Project,在弹出的对话框中填入工程名、路径等等,点击Ok进入设计界面。 2.绘制原理图 新建工程后打开的是默认的原理图文件SCHEMATIC1 PAGE1,右侧有工具栏,用于放置元件、画线和添加网络等等,用法和Protel类似。点击上侧工具栏的Project manager(文件夹树图标)或者是在操作界面的右边都能看到进入工程管理界面,在这里可以修改原理图文件名、设置原理图纸张大小和添加原理图库等等。 1)修改原理图纸张大小: 双击SCHEMATIC1文件夹,右键点击PAGE1,选择Schematic1 Page Properties,在Page Size中可以选择单位、大小等; 2)添加原理图库: File--New--Library,可以看到在Library文件夹中多了一个library1.olb的原理图库文件,右键单击该文件,选择Save,改名存盘;(注意:在自己话原理图库或者封装库的时候,在添加引脚的时候,最好是画之前设定好栅格等参数,要不然很可能出现你画的封装,很可能在原理图里面布线的时候通不过,没法对齐,连不上线!) 3)添加新元件: 常用的元件用自带的(比如说电阻、电容的),很多时候都要自己做元件,或者用别人做好的元件。右键单击刚才新建的olb库文件,选New Part,或是New Part From Spreadsheet,后者以表格的方式建立新元件,对于画管脚特多的芯片元件非常合适,可以直接从芯片Datasheet中的引脚描述表格中直接拷贝、粘贴即可(pdf格式的Datasheet按住Alt键可以按列选择),可以批量添加管脚,方便快捷。 4)生成网络表(Net List): 在画板PCB的时候需要导入网络表,在这之前原理图应该差不多完工了,剩下的工作就是查缺补漏。可以为元件自动编号,在工程管理界面下选中.dsn文件,然后选Tools--Annotate,在弹出的对话框中选定一些编号规则,根据需求进行修改或用默认设置即可。进行DRC检测也是在生成网络表之前的一项重要工作,可以避免出现一些不必要的设计错误。DRC之后可以尝试去生成网络表了,还是在工程管理界面下,选Tools--Create Netlist,可以在弹出的对话框中选择网络表的存放路径,其他默认设置即可,生成网络表的过程中如果出错,可以通Windows--Session Log查看出错的原因,(第一次用cadence 画板子,免不了会出很多错误,通过查阅报表的错误原因,做好记录,是学好该软件的捷径)比如说有元器件忘了添加封装等。 5)更新元件到原理图: 当元件库中的某个元件修改后需要原理图也同步更新时,可以不必重新放置元件(万一有100个或更多该元件岂不是要疯了),在工程管理界面下,双击Design Cache文件夹,选中刚才修改的元件,右键单击选择Update Cache,一路yes下去即可将原理图中该元件全部更新。

ad画pcb板教程

ad画pcb板教程 篇一:AD10画PCB基本步骤 AD10画PCB注意要点: 一、线路 1)、最小线宽6mil,一般在10mil左右,越宽越好。 2)、最小线距6mil,即线与线,线与焊盘之间的距离,一 般为10mil,如果条件允许,则越大越好。 3)、线路与外形线间距为20mil。 二、VIA过孔(导电孔) 1)、最小孔径12mil,最小过孔孔径=12mil,焊盘单边最 好大于8mil。 2)、过孔孔到孔间距(孔边到孔边)最好大于8mil。 3)、焊盘到外形间距20mil。 三、PAD焊盘(插件孔PTH) 1)、插件孔焊盘外环单边不能小于8mil。 2)、插件孔孔到孔间距不能小于12mil。 3)、焊盘外形间距20mil。 四、字符 1)、字符字宽大于等于6mil,字高大于等于32mil,宽高之 比最好为5 五、元器件布局 1)、有连线关系的器件放在一起。 2)、数字器件和模拟器件要分开,尽量远离。 3)、去耦电容尽量靠近器件的VCC。 4)、放置器件时要考虑以后的焊接,不要太密集 篇二:AD10简明教程--印制板制作1 目录 第六部分Altium Designer 10电路设

计................................................................- 2 - 第1章印制电路板与Protel概述 .................................................................. .- 2 - 1.1印制电路板设计流程 .................................................................. .........- 2 - 第2章原理图设计 .................................................................. ........................- 4 - 2.1 原理图设计步骤: ................................................................ ............- 4 - 2.2 原理图设计具体操作流程................................................................- 4 - 第3章原理图库的建立 .................................................................. ............. - 11 - 3.1 原理图库概述 .................................................................. ............... - 11 - 3.2 编辑和建立元件库 .................................................................. ...... - 11 - 第4章创建PCB元器件封装 .................................................................. ....- 17 -

(完整版)cadence PCB 画图(傻瓜教程快速入门)

cadence 画 PCB 板傻瓜教程(转帖) 复制于某网站,谢谢。拿出来分享吧,希望对初学者能有帮助,可以很快了解 Cadence 的使用,谢谢共享者。 一.原理图 1.建立工程 与其他绘图软件一样,OrCAD 以Project 来管理各种设计文件。点击开始菜单,然后依次是所有程序—打开 cadence 软件—》一般选用 Design Entry CIS,点 击Ok 进入Capture CIS。接下来是 File--New--Project,在弹出的对话框中填入工程名、路径等等,点击 Ok 进入设计界面。 2.绘制原理图 新建工程后打开的是默认的原理图文件 SCHEMATIC1 PAGE1,右侧有工具栏,用 于放置元件、画线和添加网络等等,用法和 Protel 类似。点击上侧工具栏的Project manager(文件夹树图标)或者是在操作界面的右边都能看到进入工程管 理界面,在这里可以修改原理图文件名、设置原理图纸张大小和添加原理图库 等等。 1)修改原理图纸张大小: 双击 SCHEMATIC1 文件夹,右键点击 PAGE1,选择 Schematic1 Page Properties,在 Page Size 中可以选择单位、大小等; 2) 添加原理图库: File--New--Library,可以看到在 Library 文件夹中多了一个 library1.olb 的原理图库文件,右键单击该文件,选择 Save,改名存盘;(注意:在自己话原 理图库或者封装库的时候,在添加引脚的时候,最好是画之前设定好栅格等参数,要不然很可能出现你画的封装,很可能在原理图里面布线的时候通不过, 没法对齐,连不上线!) 3)添加新元件: 常用的元件用自带的(比如说电阻、电容的),很多时候都要自己做元件,或 者用别人做好的元件。右键单击刚才新建的 olb 库文件,选 New Part,或是New Part From Spreadsheet,后者以表格的方式建立新元件,对于画管脚特多的芯片元件非常合适,可以直接从芯片 Datasheet 中的引脚描述表格中直接拷贝、粘贴即可(pdf 格式的 Datasheet 按住Alt 键可以按列选择),可以批量添加管脚,方便快捷。 4)生成网络表(Net List): 在画板 PCB 的时候需要导入网络表,在这之前原理图应该差不多完工了,剩下 的工作就是查缺补漏。可以为元件自动编号,在工程管理界面下选中.dsn 文件,然后选 To ol s--A n n o t a te,在弹出的对话框中选定一些编号规则,根据需求进行修改 或用默认设置即可。进行 DRC 检测也是在生成网络表之前的一项重

Cadence画PCB傻瓜式教程

一.原理图 1.建立工程 与其他绘图软件一样,OrCAD以Project来管理各种设计文件。点击开始菜单,然后依次是所有程序—打开cadence软件—》一般选用Design Entry CIS,点击Ok进入Capture CIS。接下来是File--New--Project,在弹出的对话框中填入工程名、路径等等,点击Ok进入设计界面。 2.绘制原理图 新建工程后打开的是默认的原理图文件SCHEMATIC1 PAGE1,右侧有工具栏,用于放置元件、画线和添加网络等等,用法和Protel类似。点击上侧工具栏的Project manager(文件夹树图标)或者是在操作界面的右边都能看到进入工程管理界面,在这里可以修改原理图文件名、设置原理图纸张大小和添加原理图库等等。 1)修改原理图纸张大小: 双击SCHEMATIC1文件夹,右键点击PAGE1,选择Schematic1 Page Properties,在Page Size中可以选择单位、大小等; 2)添加原理图库: File--New--Library,可以看到在Library文件夹中多了一个library1.olb的原理图库文件,右键单击该文件,选择Save,改名存盘;(注意:在自己话原理图库或者封装库的时候,在添加引脚的时候,最好是画之前设定好栅格等参数,要不然很可能出现你画的封装,很可能在原理图里面布线的时候通不过,没法对齐,连不上线!) 3)添加新元件: 常用的元件用自带的(比如说电阻、电容的),很多时候都要自己做元件,或者用别人做好的元件。右键单击刚才新建的olb库文件,选New Part,或是New Part From Spreadsheet,后者以表格的方式建立新元件,对于画管脚特多的芯片元件非常合适,可以直接从芯片Datasheet中的引脚描述表格中直接拷贝、粘贴即可(pdf格式的Datasheet按住Alt键可以按列选择),可以批量添加管脚,方便快捷。 4)生成网络表(Net List): 在画板PCB的时候需要导入网络表,在这之前原理图应该差不多完工了,剩下的工作就是查缺补漏。可以为元件自动编号,在工程管理界面下选中.dsn文件,然后选Tools--Annotate,在弹出的对话框中选定一些编号规则,根据需求进行修改或用默认设置即可。进行DRC检测也是在生成网络表之前的一项重要工作,可以避免出现一些不必要的设计错误。DRC之后可以尝试去生成网络表了,还是在工程管理界面下,选Tools--Create Netlist,可以在弹出的对话框中选择网络表的存放路径,其他默认设置即可,生成网络表的过程中如果出错,可以通Windows--Session Log查看出错的原因,(第一次用cadence 画板子,免不了会出很多错误,通过查阅报表的错误原因,做好记录,是学好该软件的捷径)比如说有元器件忘了添加封装等。 5)更新元件到原理图: 当元件库中的某个元件修改后需要原理图也同步更新时,可以不必重新放置元件(万一有100个或更多该元件岂不是要疯了),在工程管理界面下,双击Design Cache文件夹,选中刚才修改的元件,右键单击选择Update Cache,一路yes下去即可将原理图中该元件全部更新。 注意:在生成网表的时候,经常报错一定要注意,在自己画的原理图库或者是封装库的时候,一定要有系统的存放,按照一定的规则命名,在添加的时候,原件要把自己所画的封装库的路径添加上,要不然,是不能正确生成网表的。同时,这样方便以后工程的调用

cadence PCB 画图(傻瓜教程快速入门)

cadence画PCB板傻瓜教程(转帖) 一.原理图 1.建立工程 与其他绘图软件一样,OrCAD以Project来管理各种设计文件。点击开始菜单,然后依次是所有程序—打开cadence软件—》一般选用DesignEntryCIS,点击Ok进入CaptureCIS。接下来是File--New--Project,在弹出的对话框中填入工程名、路径等等,点击Ok进入设计界面。 2.绘制原理图 新建工程后打开的是默认的原理图文件SCHEMATIC1PAGE1,右侧有工具栏,用于放置元件、画线和添加网络等等,用法和Protel类似。点击上侧工具栏的Projectmanager(文件夹树图标)或者是在操作界面的右边都能看到进入工程管理界面,在这里可以修改原理图文件名、设置原理图纸张大小和添加原理图库等等。 1)修改原理图纸张大小: 双击SCHEMATIC1文件夹,右键点击PAGE1,选择 Schematic1PageProperties,在PageSize中可以选择单位、大小等; 2)添加原理图库: File--New--Library,可以看到在Library文件夹中多了一个library 1."olb的原理图库文件,右键单击该文件,选择Save,改名存盘;(注意: 在自己话原理图库或者封装库的时候,在添加引脚的时候,最好是画之前设定好栅格等参数,要不然很可能出现你画的封装,很可能在原理图里面布线的时候通不过,没法对齐,连不上线!) 3)添加新元件:

常用的元件用自带的(比如说电阻、电容的),很多时候都要自己做元件,或者用别人做好的元件。右键单击刚才新建的olb库文件,选NewPart,或是NewPartFromSpreadsheet,后者以表格的方式建立新元件,对于画管脚特多的芯片元件非常合适,可以直接从芯片Datasheet中的引脚描述表格中直接拷贝、粘贴即可(pdf格式的Datasheet按住Alt键可以按列选择),可以批量添加管脚,方便快捷。 4)生成网络表(NetList): 在画板PCB的时候需要导入网络表,在这之前原理图应该差不多完工了,剩下的工作就是查缺补漏。可以为元件自动编号,在工程管理界面下选中.dsn 文件,然后选Tools--Annotate,在弹出的对话框中选定一些编号规则,根据需求进行修改或用默认设置即可。进行DRC检测也是在生成网络表之前的一项重要工作,可以避免出现一些不必要的设计错误。DRC之后可以尝试去生成网络表了,还是在工程管理界面下,选Tools--CreateNetlist,可以在弹出的对话框中选择网络表的存放路径,其他默认设置即可,生成网络表的过程中如果出错,可以通Windows--SessionLog查看出错的原因,(第一次用cadence画板子,免不了会出很多错误,通过查阅报表的错误原因,做好记录,是学好该软件的捷径)比如说有元器件忘了添加封装等。 5)更新元件到原理图: 当元件库中的某个元件修改后需要原理图也同步更新时,可以不必重新放置元件(万一有100个或更多该元件岂不是要疯了),在工程管理界面下,双击DesignCache文件夹,选中刚才修改的元件,右键单击选择UpdateCache,一路yes下去即可将原理图中该元件全部更新。 注意: 在生成网表的时候,经常报错一定要注意,在自己画的原理图库或者是封装库的时候,一定要有系统的存放,按照一定的规则命名,在添加的时候,原件要把自己所画的封装库的路径添加上,要不然,是不能正确生成网表的。同时,这样方便以后工程的调用 6)一些细节:

AD软件画PCB板心得

AD软件画PCB板心得 Altium designer 10 画图心得 1. 使用AD10设计PCB电路板走线时无法捕捉特征点 Design/board options/snap options目录下snap to object hotspots(自动捕捉热点) 2. 设置PCB板原点及板子外形 设置原点:edit/origin/set/快捷键J L(jump to location)/输入X、Y坐标,enter 设置板子外形:design/board shape/redefine board shape/快捷键J L(jump to location)通过设置坐标来设置板子的尺寸。(此时起始坐标为(0,0)已设原点处) 3. 复制板子外形 在需要复制的图中,点击keep-out layer成为当前层, edit/select/all on layer,去除定位孔的选择:shift+单击。 edit/copy在原点处单击。在新图中点击keep-out layer成为当前

层,edit/paste,找到原点的位置(快捷键J L(jump to location) 起始坐标为(0,0)),enter。Design/board shape/define from selected objects 注:create primitives from board shape 根据板子外形生成禁止布线层 4. 在原理图中改同一类型的参数 封装:在某一相同封装类型元器件右键find similar objects/current footprint 0805 any-same/勾选select matching,ok/在弹出的对话框中0805-0603单击任意位置。 5. 在PCB中修改序号尺寸 在某一序号右键 find similar objects/text height text width any-same/在弹出的小对话框中修改两项参数,单击任意位置。 6. 同时锁定多根线

cadencePCB画图(傻瓜教程快速入门).doc

cadence 画 PCB板傻瓜教程(转帖) 一.原理图 1.建立工程 与其他绘图软件一样, OrCAD以 Project 来管理各种设计文件。点击开始菜单,然后依次是所有程序—打开 cadence 软件—》一般选用 DesignEntryCIS,点击Ok 进入 CaptureCIS。接下来是 File--New--Project,在弹出的对话框中填入 工程名、路径等等,点击 Ok 进入设计界面。 2.绘制原理图 新建工程后打开的是默认的原理图文件 SCHEMATIC1PAGE1,右侧有工具栏,用于放置元件、画线和添加网络等等,用法和 Protel 类似。点击上侧工具栏的 Projectmanager(文件夹树图标)或者是在操作界面的右边都能看到进入工程管理界面,在这里可以修改原理图文件名、设置原理图纸张大小和添加原理图库 等等。 1)修改原理图纸张大小: 双击 SCHEMATIC1文件夹,右键点击 PAGE1,选择 Schematic1PageProperties,在 PageSize中可以选择单位、大小等; 2)添加原理图库: File--New--Library,可以看到在 Library 文件夹中多了一个library 1."olb 的原理图库文件,右键单击该文件,选择Save,改名存盘;(注意: 在自己话原理图库或者封装库的时候,在添加引脚的时候,最好是画之前 设定好栅格等参数,要不然很可能出现你画的封装,很可能在原理图里面布线 的时候通不过,没法对齐,连不上线!) 3)添加新元件:

常用的元件用自带的(比如说电阻、电容的),很多时候都要自己做元 件,或者用别人做好的元件。右键单击刚才新建的olb 库文件,选 NewPart,或是NewPartFromSpreadsheet,后者以表格的方式建立新元件,对于画管脚特多 的芯片元件非常合适,可以直接从芯片Datasheet 中的引脚描述表格中直接拷贝、粘贴即可( pdf 格式的 Datasheet 按住 Alt 键可以按列选择),可以批量添 加管脚,方便快捷。 4)生成网络表( NetList): 在画板 PCB的时候需要导入网络表,在这之前原理图应该差不多完工了, 剩下的工作就是查缺补漏。可以为元件自动编号,在工程管理界面下选中 .dsn 文件,然后选 Tools--Annotate,在弹出的对话框中选定一些编号规则,根据需求进 行修改或用默认设置即可。进行 DRC检测也是在生成网络表之前的一项重要工作,可以避免出现一些不必要的设计错误。 DRC之后可以尝试去生成网络表了,还是在工程管理界面下,选 Tools--CreateNetlist,可以在弹出的对话框中选择网络表的存放路径,其他默认设置即可,生成网络表的过程中如果出错, 可以通 Windows--SessionLog查看出错的原因,(第一次用 cadence画板子,免不了会出很多错误,通过查阅报表的错误原因,做好记录,是学好该软件的捷径)比如说有元器件忘了添加封装等。 5)更新元件到原理图: 当元件库中的某个元件修改后需要原理图也同步更新时,可以不必重新放 置元件(万一有100 个或更多该元件岂不是要疯了),在工程管理界面下,双 击 DesignCache文件夹,选中刚才修改的元件,右键单击选择UpdateCache,一路yes 下去即可将原理图中该元件全部更 新。注意: 在生成网表的时候,经常报错一定要注意,在自己画的原理图库或者是封 装库的时候,一定要有系统的存放,按照一定的规则命名,在添加的时候,原 件要把自己所画的封装库的路径添加上,要不然,是不能正确生成网表的。同 时,这样方便以后工程的调用 6)一些细节:

PCB四层板教程

https://www.360docs.net/doc/b66977704.html,/forum.php?mod=viewthread&tid=3982551 第一次把四层板画完,发去做了,现在有点无聊。 以前参加电子竞赛的时候,都是画单层板,这次毕业课题忽然要画四层,开始的时候以为没什么,但是发现这个过程中还是遇到很多问题,现在整理一下,仅供没有画过四层板的参考,高手们请多拍砖,下面就开始了。 一.原理图 一般用四层板的原理图还是分模块画好,其实和画在一幅里面是一样的,同样名字的网络也还是互相连接的,都的时候需要放置输入输出的接口,我个人认为放不放都行的。 我采用的是自底向上的方法画的,就是说先把各个模块画好,然后再综合进行ERC 首先画好各个模块,然后再新建一个TOP.Sch,在TOP.Sch里面放置SHEET SYMBOL(在place wire正下方),如下图设置,FileName即你要代表的原理图单元的文件, (原文件名:sheetsymbol.jpg) IO.Sch即输入输出的模块,name可以随便取。

下面的过程要特别注意,在综合时要编辑各个原理图模块的属性,以第一个AD.Sch为例, (原文件名:org.jpg) 在空白处右击,选择DocumenOption,设置sheet为0,total为总的原理图的单元,按照同样的方法,依次设置所有的模块,设置好后,自动出现下图,所有的模块都在TOP.Sch下面了。

(原文件名:TOP.jpg) (原文件名:总的sch.jpg) 当完成原理图以后,要进行ERC检查,这时候要设Sheets to Netlist要置成Active Project.