哈工大数电试卷1

数字电子技术 (A 卷)

一、 填空题:(每空2分,共30分)

(1)(11100.011)2 =( 28.6 )10 =( )8421BCD

(2) (204.125) 10 =( ) 2 =( )8 =( )16

(3)字母TTL 代表( )。

(4) 三态门的输出状态共有( )三个状态。

(5)将模拟信号转换为数字信号需经过( )四个步骤。 (6)触发器的触发方式可分为电平触发和( )触发。 (7) 逻辑门电路输出端可驱动同类门电路的个数称为( )。

(8) 将))((C B A C B A Y ++++= 化为最小项形式为( )。 (9) ( )(译码器,编码器)的特点是在任一时刻只有一个输入有效。 (10)一位半加器具有( )个输入和两个输出。

(11)已知A/D 转换器的分辨率为8位,其输入模拟电压范围为

0~5V ,则当输入电压为1.96V 时,输出数字量为( )。

(12)利用双稳态触发器存储信息的RAM 称为( )RAM 。 二、(共10分) (1)(4分) 用代数法化简:C B BC C B A BCD A A F ++++=

(2)(6分) 用卡诺图化简:

∑∑+=m d 8) 4, 2, 1, (0, 6,7,10) 5, 3, (D) C, B,,Y(A

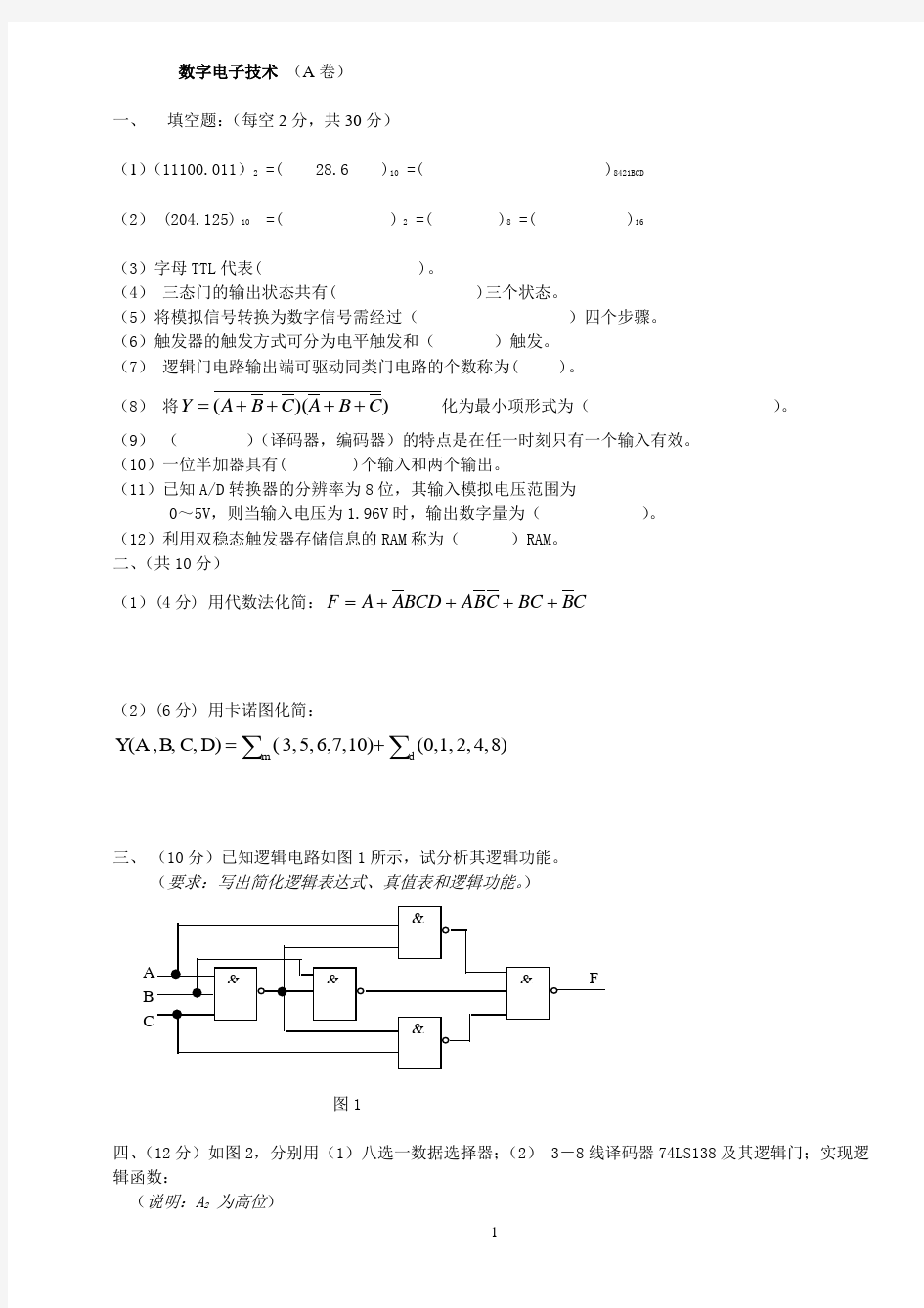

三、 (10分)已知逻辑电路如图1所示,试分析其逻辑功能。

(要求:写出简化逻辑表达式、真值表和逻辑功能。)

图1

四、(12分)如图2,分别用(1)八选一数据选择器;(2) 3-8线译码器74LS138及其逻辑门;实现逻辑函数:

(说明:A 2 为高位)

& & & & & F A B C

C B A C B A AC F ++=

五、(15分)电路和波形如图3 (a ),(b)所示,设Q 0 ,Q 1 的初态均为0。

(1)写出驱动方程,状态方程和输出方程;

(2)画出Q 0 ,Q 1和Y 的波形(直接画在本试卷上)。

图3 (a )

图3 (b )

D 4 D 5 D 6 D 7

A 0 A 1 A 2 D 0 D 1 D 2 D 3 Y

A 2 A 1 A 0 G 1 G 2A G 2B

74LS138

Y 7

Y …

图2

1J

Q

1K Q 1

C > 1J

Q

1K Q

1

C >CP

&

Y

Q 0

Q 1

A

B

Y Q 0 Q 1 A B CP

六、(12分)试利用集成计数器74LS161(图4)和必要的逻辑门,

(1)用反馈清零法构成12进制计数器;

(2)用反馈置数法构成8进制计数器,要求计数器的初始状态为“0”;(上述均要求画出状态转换图。)

(说明:74LS161 为同步四位二进制递增计数器,计数脉冲CP为上升沿触发,且为异步清0,同步置数,低电平有效。)

图4

七、(5分)分析图5 中所示电路为几进制计数器?

(对于74LS161 ,Q3Q2Q1Q0 =1111时,进位输出CO=1)

图5

八、(6分)用两个555定时器可以组成如图6所示的模拟声响电路。(1)适当选择定时元件,当接通电源时,可使扬声器以 1kHz频率间歇鸣响。

(2)说明两个555定时器分别构成什么电路。

(3)改变电路中什么参数可改变扬声器间歇鸣响时间?

(4)改变电路中什么参数可改变扬声器鸣响的音调高低?

图6

数字电子技术 (B 卷)

一.填空题:(每空2分,共30分)

(1) (110011.11)2 = ( )10 =( )8421BCD

(2) (631.25) 10 =( ) 2 =( )8 =( )16

(3) 字母CMOS 代表( )。 (4) 集电极开路输出的TTL 门电路需要( )电阻,接在输出端和+5V 电源之间。 (5) 将模拟信号转换为数字信号需经过( )四个步骤。 (6) 触发器的触发方式可分为电平触发和( )触发。 (7) 未联接的TTL 输入端等效为( )(高,低)电平。 (8)将)C B A )(C B A (Y ++++=化为最小项形式为( )。 (9) 一位全加器具有( )个输入和两个输出。 (10) ( )(译码器,编码器)的特点是在任一时刻只有一个输出有效。 (11) 利用电容的存储功能来存储信息的RAM 称为( )RAM 。 (12) 已知D/A 转换器的输入数字量为10000000时, 输出电压

为5V ,则输入数字量为01010000时,输出电压为( )。

二、(共10分) (1)(4分)用代数法化简:ABC C AB C B A C B A F +++=

(2)(6分) 用卡诺图化简:

∑∑+=m d 11) 4,5, 3, (2, 8,10) 1, 0, (D) C, B ,,Y(A

三、(10分)已知逻辑电路如图1所示,试分析其逻辑功能。

(要求:写出简化逻辑表达式、真值表和逻辑功能。)

图1

四、(12分)如图2,分别用(1)八选一数据选择器;(2) 3-8线译码器74LS138及其逻辑门;实现逻辑函数:

(说明:A 2 为高位)

C B A C A BC F ++=

五、(15分) 电路和波形如图3 (a ),(b)所示,设Q 0 ,Q 1 的初态均为0。 (1)写出驱动方程,状态方程和输出方程;

(2)画出Q 0 ,Q 1和Y 的波形(直接画在本试卷上)。

图3 (a )

&

&

&

&

&

F

A B C D 4 D 5 D 6 D 7

A 0 A 1 A 2 D 0 D 1 D 2 D 3 Y

A 2 A 1 A 0 G 1 G 2A G 2

B 74LS138 0Y 7Y … 1J Q 1K Q 1

C > 1J Q 1K Q 1

C >CP

& Y Q 0 Q 1

A B

图3 (b )

六、 (12分)试利用集成计数器74LS161(图4)和必要的逻辑门, (1) 用反馈清零法构成13进制计数器;

(2) 用反馈置数法构成 9进制计数器,要求计数器的初始状态

为“0” ;(上述均要求画出状态转换图。)

(说明:74LS161 为同步四位二进制递增计数器,计数脉冲CP 为上升沿触发,且为异步清0,同步置数,

低电平有效。)

图4 七、(5分) 分析图5 中所示电路为几进制计数器?

(对于74LS161 ,Q 3Q 2Q 1Q 0 =1111时,进位输出CO=1)

图5

Y Q 0 Q 1 A B CP

八、(6分)用两个555定时器可以组成如图6所示的电子门铃电路。适当选择定时元件,当按下按钮S 时,可使扬声器以 1kHz 频率鸣响10秒钟。

(5) 说明两个555定时器分别构成什么电路。

(6) 改变电路中什么参数可改变扬声器鸣响持续时间? (7) 改变电路中什么参数可改变扬声器鸣响的音调高低?

(8)

图6

2005-2006学年第1学期期终考试试题(B )

一、 填空题(22分每空2分)

1.(41)10 = ( )8 = ( )2

2.在数字电路中,三极管通常是工作在

状态。 3.单稳态触发器中,两个状态一个为 态,另一个为 态.多谐振荡器两个状态都为 态,施密特触发器两个状态都为 态.

4.TTL 与非门输入高电平的噪声容限为 V NH = ,输入低电平的噪声容限为V NL = 。

5.一个触发器只能存贮 位二进制代码,要存贮三位二进制代码,要用到 个触发器。 二、 化简题(15分 每小题5分)

1.用卡诺图化简逻辑函数,必须在卡诺图上画出卡诺圈

1) Y=D C B A ABC ++++

2)),,,,,()+,,,()=,,,(1413121110,94Σ6521Σd m D C B A L 2.利用代数法化简逻辑函数,必须写出化简过程

三、 画图题(10分 每题5分)

据输入波形画输出波形或状态端波形(触发器的初始状态为0).

)

)((D B A D B A B A B A AB Y +++++=

1. 2.

四、 分析题(17分)

1.写出下图的逻辑函数表达式,并画出真值表(6分)

2.电路如图所示,分析该电路,画出完全的状态转换图(11分)

五、 设计题(28分)

1.某公司招聘职员,由经理和两位副经理决定,只有当两位或两位以上(必须含经理)同意之后,应聘者才被录用。(20分)

(1) 要求用或非门实现此裁决电路

(2) 要求用74LS138和适当与非门实现此裁决电路

2.用74LS 161实现一个五进制加法计数器(8分)

J Q cp K Q

cp

cp Q 1 ≥1 =1 A B

C L A B

C

L Q1 J1 Q1 K1 Q2 J2 Q2 K2 cp 1

Z &

—

六、分析画图题(8分)

画出下图所示电路在i V 作用下,输出电压的波形

2006-2007学年第1学期期终考试试题 一. 填空题(22分每空2分)

1.=⊕0A

, =⊕1A 。 2.JK 触发器的特性方程为: 。

3.单稳态触发器中,两个状态一个为 态,另一个为 态.多谐振荡器两个状态都为 态, 施密特触发器两个状态都为 态.

4.组合逻辑电路的输出仅仅只与该时刻的 有关, 而与 无关。

5.某数/模转换器的输入为8位二进制数字信号(D 7~D 0)

,输出为0~25.5V 的模拟电压。若数字信号的最低位是“1”其余各位是“0”,则输出的模拟电压为 。

6.一个四选一数据选择器,其地址输入端有 个。

二. 化简题(15分 每小题5分)

用卡诺图化简逻辑函数,必须在卡诺图上画出卡诺圈

1) Y (A,B,C,D )=∑m (0,1,2,3,4,5,6,7,13,15)

2)∑∑+=

)11,10,9,3,2,1()15,14,13,0(),,,(d m D C B A L

利用代数法化简逻辑函数,必须写出化简过程

3)________________________________________

__________)(),,(B A B A ABC B A C B A F +++=

三. 画图题(10分 每题5分)

据输入波形画输出波形或状态端波形(触发器的初始状态为0). 1.

2.

四.分析题(17分)

1.分析下图,并写出输出逻辑关系表达式,要有分析过程(6分)

2.电路如图所示,分析该电路,画出完全的时序图,并说明电路的逻辑功能,要有分析过程(11分)

五.设计题(28分)

1.用红、黄、绿三个指示灯表示三台设备的工作情况:绿灯亮表示全部正常;红灯亮表示有一台不正常;黄灯亮表示两台不正常;红、黄灯全亮表示三台都不正常。列出控制电路真值表,要求用74LS138和适当的与非门实现此电路(20分)

2.中规模同步四位二进制计数器74LS161的功能表见附表所示;请用反馈预置回零法设计一个六进制加法计数器。(8分)

六、分析画图题(8分)

画出下图所示电路在

i

V 作用下,输出电压的波形和电压传输特性

2004─2005学年 第一学期

一、(25分)选择与填空(1-4题每空2分,5-9题每空1分) 1.(4F)16=( )10=( )2=( )8

=( )8421BCD=( )5421BCD

2.已知D/A电路中,当输入数字量为00000001时,输出电压为0.02V ,则当输入为01010001时,其输出电压为( )。

3.三态门的输出状态共有( )三个状态。 4.A/D转换的四个过程为( )。 5.( )(译码器、编码器)的特点是在任一时刻只有一个输入有效。 6.将))((C B A C B A Y ++++=化为最小项形式为( )。

7.字母”TTL ”代表( )。 8.4256?的存储器有( )根数据线,( )根地址线,若该存储器的起始地址为00H,则最高地址为( ),欲将该存储器扩展为81?K 的存储系统,需要4256?的存

储器( )个。

9.电路如图1所示,该电路为( )(单稳态触发器,多谐振荡器)。若为单稳态触发器,则输出脉冲宽度的表达式T W 为 ,若为多谐振荡器,则其振荡周期的表达式T 为

图1 二、(16分)逻辑函数化简(每小题4分)

1.用代数法将下列逻辑函数化为最简“与或”式。 (1) ()AB B A AB B A F ++⊕=1

(2)C A ABC B A F ??+=2 2.用卡诺图将下列函数化为最简“与或”式。 (1)D C B A ABD D C B B A F +++=1 (2)()()∑∑+=

d

m

D C B A F 15,14,13,12,11,109,8,7,6,5,,3,2,0),,,(2

U 0 8 4

7 6 3

2 1

V CC 555 R1 R2 C

三、(15分)组合逻辑电路如图2所示

(1)写出逻辑函数表达式;

(2)画出真值表;

(3)确定电路的逻辑功能;

(4)用译码器74LS138和必要的逻辑门实现该逻辑函数。(见图2(b),其中A2为最高位)

图2(a)第三题

图2(b)第三题

四、(10分)电路和波形如图3(a)、(b)所示,设Q0,Q1的初态为0,试画出Q0,Q1及Y的波形。

图3(a)

A2 A1A0G1 G2A G2B

74LS138

Y

7

Y

…

Q0 Q1

Y

1J Q

1K Q

1

C

>

1D Q

Q

1

C

>

&

A

CP

图(4) 五、(20分)时序逻辑电路如图4所示, (1)写出驱动方程,时钟方程和状态方程。

(2)画出完整的状态转换图(顺序按Q2Q1Q0排列)。 (3)确定电路的逻辑功能。 (4)检查能否自启动。

图4 第五题

六、(10分)74LS161计数器如图5(a )所示, (1)试采用反馈清零法设计一个13进制计数器。 (2)电路如图5(b )所示,试确定该电路的功能。

说明:(a) 图中Q 3和Q D 为最高位;(b) 均要求画出状态转换图。

Y Q 0 Q 1 A CP 1J Q 1K Q 1C > 1J Q 1K Q 1C > 1J Q

1K Q

1C >& Q 0 Q 1 Q 2 CP

CT T Q 0 Q 1 Q 2 Q 3 CT P 74LS161 CLR

CP D 0 D 1 D 2 D 3

CP A Q A Q B Q C Q D CP B 74LS90 R 0(1) R 0(2) S 9(1) S 9(2) CP A Q A Q B Q C Q D CP B 74LS90 R 0(1) R 0(2) S 9(1) S 9(2) & CP

一、(25分)选择与填空(1-4题每空2分,5-9题每空1分) 1.(D2)16=( )10=( )2=( )8

=( )8421BCD=( )5421BCD

2.已知D/A电路中,当输入数字量为00000001时,输出电压为0.02V ,则当输入为01001101时,其

输出电压为( )。

3.集电极开路输出的TTL 门需要( )电阻,接在输出端和+5V 电源之间。 4.A/D转换的四个过程为( )。 5.( )(译码器、编码器)的特点是在任一时刻只有一个输出有效。 6.TTL 数字集成电路的电源电压为( )(+5V ,+10V )。 7.将)C B A )(C B A (Y ++++=化为最小项形式为( )。

8.41?K 的存储器有( )根数据线,( )根地址线,若该存储器的起始地址为00H,则最高

地址为( ),欲将该存储器扩展为82?K 的存储系统,需要41?K 的存储器( )个。 9.电路如图1所示,该电路为( )(单稳态触发器,多谐振荡器)。若为单稳态触发器,则输

出脉冲宽度的表达式T W 为 ,若为多谐振荡器,则其振荡周期的表达式T 为

图1

二、(16分)逻辑函数化简(每小题4分)

1.用代数法将下列逻辑函数化为最简“与或”式。 (1) ()CD D C CD D C F ++⊕=1 (2)E C CDE D C F ??+=2

2.卡诺图将下列函数化为最简“与或”式。

(1) ()D C B A D C B A BCD C B A D B A D C B A Y ++++=,,,1 (2) ()()()∑∑+=

d

m

D C B A Y 15,14,11,10,9,813,12,7,5,4,2,0,,,2

三.(15分)组合逻辑电路如图2所示,

(5) 写出逻辑函数表达式; (6) 画出真值表;

(7) 确定电路的逻辑功能;

(8) 用译码器74LS138和必要的逻辑门实现该逻辑函数。(见图2(b ),其中A 2为最高位)

U 0 9 4 7 6 3 2 1

V CC 555 V i

R

C

图2(a ) 第三题

图2(b ) 第三题

四.(10分)电路和波形如图3(a )、(b )所示,设Q 0,Q 1的初态为0,试画出Q 0,Q 1及Y的波形。

图3(a )

图3(b )

五、(16分)时序逻辑电路如图4所示, (1)写出驱动方程,时钟方程和状态方程。

Y

Q 0

Q 1

A CP

A 2 A 1 A 0 G 1 G 2A G 2B

74LS138

Y 7

Y …

Q 0

Q 1

Y 1J Q 1K Q 1C > 1D

Q

Q 1

C > &

A CP

(2)画出完整的状态转换图(顺序按Q2Q1Q0排列)。 (3)确定电路的逻辑功能。 (4)检查能否自启动。

图4 第五题

六、(10分)74LS161计数器如图5(a )所示, (1)试采用反馈清零法设计一个12进制计数器。 (2)电路如图5(b )所示,试确定该电路的功能。

说明:(a) 图中Q 3和Q D 为最高位;(b) 均要求画出状态转换图。

图5(a

图5(b )

数字电子技术 (A 卷)

一、 数制与码制转换(10分) 1.(123.625)10 =( )2 =( )8 =( )16

CT T Q 0 Q 1 Q 2 Q 3 CT P 74LS161 CLR

CP D 0 D 1 D 2 D 3 Q 0 Q 1 CP 1J Q 1K Q 1C > 1J Q

1K Q 1C > 1J Q 1K Q 1C >Q 2 & & 1

CP A Q A Q B Q C Q D CP B 74LS90 R 0(1) R 0(2) S 9(1) S 9(2) CP A Q A Q B Q C Q D CP B 74LS90 R 0(1) R 0(2) S 9(1) S 9(2) & CP

2. (101001.10101)2 =( )10 =( )5421BCD

二、 化简下列各式为最简“与或”表达式(方法不限)(20分) 1.C AB C B BC A AC Y +++= 2.

AC C B B A B A Y +++=

3. ∑

∑+=m

d 15) 14, 13, 12, 11, (10, 9) 6, 4, 2, (0,D) C, B,,Y(A

4. 已知 :

D)C A D)(C B )(D C B (A Y CD,ABC X +++++++=+=,

求XY Z = 的最简“与或”式.

三、 电话机需对四种电话进行编码控制,按紧急次序排列的优先权由高到低是:火警电话A 、急救电话B 、

工作电话C 和生活电话D ,它们分别被编码为:11、10、01、00。试设计该编码器。(设输入为高电平有效,用任意逻辑门实现)(9分)

四、 电路如图1(a),(b),(c)所示,求输入变量取何值时各电路等效?(8分) (a) (b)

(c)

图1 题四

五、分析图2 中(a ),(b),(c)所示电路分别为几进制计数器?对于图(a )和图(b)电路,要求按 Q 3Q 2Q 1Q 0 的排列顺序画出状态转换图。(15分)

(说明:74LS161 为同步四位二进制递增计数器,计数脉冲CP 为上升沿触发,且为异步清0,同步置数,低电平有效。)

1 ≥1 A B

F1 1

1

& 1

A

B F2 1

1

& & ≥1 A B

F3

(a) (b)

六、电路和波形如图3 中(a ),(b)所示,设Q 0 ,Q 1 的初态均为0,画出Q 0 ,Q 1和Y 的波形(直接画在本试

卷上)。(15分)

(a)

(b) 图3 题六

1

1 CT T Q 0 Q 1 Q

2 Q

3 CT P 74LS161 CLR

CP D 0 D 1 D 2 D 3

1J Q 1K Q 1C > 1J

Q 1K Q 1

C >CP

& Y Q 0 Q 1 1

M

CP M Y Q 0 Q 1 CT T Q 0 Q 1 Q 2 Q 3 CT P 74LS161 CLR

CP D 0 D 1 D 2 D 3

1 1 &

CT T Q 0 Q 1 Q 2 Q 3

CT P 74LS161 LD

CP D 0 D 1 D 2 D 3

1 1

&

1 1 0 0 &

CT T Q 0 Q 1 Q 2 Q 3 CO CT P 74LS161 CLR

CP D 0 D 1 D 2 D 3

CP

七、分别用一块双四选一数据选择器74LS153和一块3-8线译码器74LS138(如图4所示)实现下列两输出逻辑函数:(15分)

Y 1 = A+BC Y 2 =B+AC

图4 题七

八、如图5所示,74LS90为BCD 码计数器,CP A 接计数脉冲,CP B 接Q A ,此时Q D Q C Q B Q A 为8421BCD 码的十进制计数器,它为异步清0,异步置9,且高电平有效,时钟为下降沿触发。DAC0832 为8位倒T 电阻型D/A 转换器。74LS151为八选一数据选择器,EN 为低电平有效。试定性画出U 01 , Q C , Q B , Q A ,U 02 ,U 03 的波形。 (8分)

图5 题八

数字电子技术 (B 卷)

五、 数制与码制转换(10分) 1.(127.8125)10 =( )2 =( )8 =( )16

2. (111001.101)2 =( )10 =( )5421BCD 六、 化简下列各式为最简“与或”表达式(方法不限)(20分) 1.C B A C B BC A AB Y +++=

A 2 A 1 A 0 G 1 G 2A G 2B

74LS138 0Y 7

Y … 10 4 7 6 3 2 1 U 01 555定时器 V CC

+5V U 03 -5V V CC R f

V R DAC0832 I O1 I O2

D 7 . … D 2D 1 D 0

CP A Q A Q B Q C Q D CP B 74LS90 R 0(1) R 0(2) S 9(1) S 9(2) & 1 1 0 0 1 0 1 0 U 02

A 0 A 1 A 2 D0 D1 D2 74151 D3 D4 D5 D6 D7 EN 74LS153

D 0 D 1 D 2 D 3 A 0

A 1 D 0 D 1 D 2 D 3 S 1 S 2

Y 1 Y 2

2.

C A C B AB B A Y +++=

3. ∑

∑+=m

d 11) 9, 6, 4, 2, (0, ) ,15 ,14 ,13 (10,12D) C, B,,Y(A

4. 已知 :

D)C D)(A C D)(B C B (A Y D,A ABC X +++++++=+=,

求XY Z = 的最简“与或”式.

七、 电话机需对四种电话进行编码控制,按紧急次序排列的优先权由高到低是:火警电话A 、急救电话B 、

工作电话C 和生活电话D ,它们分别被编码为:00、01、10、11。试设计该编码器。(设输入为高电平有效,用任意逻辑门实现)(9分) 八、 电路如图1(a),(b),(c)所示,求输入变量取何值时各电路等效?(8分) (a) (b)

(c)

图1 题四

五、分析图2 中(a ),(b),(c)所示电路分别为几进制计数器?对于图(a )和图(b)电路,要求按 Q 3Q 2Q 1Q 0 的排列顺序画出状态转换图。(15分)

(说明:74LS161 为同步四位二进制递增计数器,计数脉冲CP 为上升沿触发,且为异步清0,同步置数,低电平有效。)

1 ≥1 A B

F1 1

1

& 1

A

B F2 1

1

& & ≥1 A B

F3

CT T Q 0 Q 1 Q 2 Q 3 CT P 74LS161 LD CP D 0 D 1 D 2 D 3

1 1

&

0 1 1 0 CT T Q 0 Q 1 Q 2 Q 3 CT P 74LS161 CLR CP D 0 D 1 D 2 D 3

1 1 &

哈工大数字电路设计加减乘三则计算器

哈工大数字电路设计加减乘三则计算器

————————————————————————————————作者:————————————————————————————————日期:

H a r b i n I n s t i t u t e o f T e c h n o l o g y 数字电子技术基础大作业 课程名称:数字电子技术基础Ⅱ 设计题目:四位二进制计算器 院系: 班级: 设计者:宇之翔LEO 学号: 指导教师: 设计时间:2015年12月-2016年1月 作者声明:本大作业是本人在考试之前花费大量时间完成的,之前在网上也可以相关的文章和做法,但是水平不是很高,而且存在很多错误,我在参考的时候也受到许多误导,最终在本人汇总和潜心钻研后总结出一篇较完整、较准确的文章。考虑到我完成作业时受到的各种辛苦,特将这份资料分享给大家。仅供参考,有问题可以给我提!由于含有本人大量的心血,所以需要的劵也偏高,希望各位理解!完成作业对你们的帮助更是巨大的,希望对你们有所帮助,解决令人头疼的作业! 另外,目前除法计算器的电路设计过于复杂且难度较高,尚无法完成,资料也查阅不到,有完成者可以与本人交流! 哈尔滨工业大学

一、设计目的和要求 本次大作业是在学完本门课程后,对所学知识的综合性考察和对思维的锻炼。通过本次作业,灵活运用学过的数字电子元器件和数字电子技术等方面的知识,完成从设计、选片、连线、调试、排除故障到实现一个数字系统的全过程。 本次作业我选择设计四位二进制的计算器,使用Multisim 软件进行设计和仿真,最终实现四位二进制数的加、减、乘的目的,并能够通过数码显示管将输入的数字和输出的运算结果显示出来。 二、设计方案 1.设计综述 此计算器分加减区和乘法区,通过开关选择运算方式,选择加减法区,则乘法区的数码管为清零状态,通过控制开关置数,在加减法区数码管显示输入和运算结果:选择乘法区,则加减法区的数码管为清零状态,通过控制开关置数,在乘法区数码管显示输入和运算结果。在加减法区中,通过开关选择加、减运算方式,分别在数码管中显示输入和运算结果。 2. 系统方框图 置数 置数 三、各部分计算器电路的设计和仿真 1.加法计算器器电路 如图1所示,这是加法器最简单的电路,也是本次设计的核心电路部分。 图1 加减 乘法 加减法运算 加法 减法 乘法区 显示输加减法区显示

《数字电路》期末模拟试题及答案

- 1 - 一、填空题 1. PN 结具有单向导电性。正向偏置时,多子以扩散运动为主,形成正向电流;反向 偏置时,少子漂移运动,形成反向饱电流。 2. 双极型晶体三极管输出特性曲线的三个工作区是放大区、截止区、饱和区。 3. 已知三态与非门输出表达式C AB F ?=,则该三态门当控制信号C 为高电平时, 输出为高阻态。 4. 十进制数211转换成二进制数是(11010011)2;十六进制数是(D3)16。 5. 将若干片中规模集成电路计数器串联后,总的计数容量为每片计数容量的乘积。 6. 若用触发器组成某十一进制加法计数器,需要四个触发器,有五个无效状态。 7. 同步RS 触发器的特性方程为n 1n Q R S Q +=+;约束方程为RS=0 。 8. 下图所示电路中,Y 1 =B A Y 1=;Y 2 = ;Y 3 =AB Y 3= 二、选择题 1. 下列函数中,是最小项表达式形式的是____ c _____。 A. Y=A+BC B. Y=ABC+ACD C. C B A C B A Y +?= D. BC A C B A Y +?= 2. 要实现n 1n Q Q =+,JK 触发器的J 、K 取值应为__d ___。 A . J=0,K=0 B. J=0,K=1 C. J=1,K=0 D. J=1,K=1 3.数值[375]10与下列哪个数相等_b __。 A . [111011101]2 B. [567]8 C. [11101110]BCD D. [1F5]16 4.属于组合逻辑电路的是_____b ______ A . 触发器 B. 全加器 C. 移位寄存器 D. 计数器 5.M 进制计数器状态转换的特点是:设定初态后,每来_c __个计数脉冲CP ,计数器重 新 B 2 B V CC Y 1

数电复习题集(含答案解析)-数电复习题集

数 电 复 习 题 选择题: 1.下列四个数中,与十进制数(163)10不相等的是( D ) A 、(A3)16 B 、(10100011)2 C 、(000101100011)8421BC D D 、(203)8 2.N 个变量可以构成多少个最小项( C ) A 、N B 、2N C 、2N D 、2N -1 3.下列功能不是二极管的常用功能的是( C ) A 、检波 B 、开关 C 、放大 D 、整流 4..将十进制数10)18(转换成八进制数是 ( B ) A 、20 B 、22 C 、21 D 、23 5.译码器的输入地址线为4根,那么输出线为多少根( C ) A 、8 B 、12 C 、16 D 、20 6.能把正弦信号转换成矩形脉冲信号的电路是(D ) A 、多谐振荡器 B 、D/A 转换器 C 、JK 触发器 D 、施密特触发器 7.三变量函数()BC A C B A F +=,,的最小项表示中不含下列哪项 ( A ) A 、m2 B 、 m5 C 、m3 D 、 m7 8.用PROM 来实现组合逻辑电路,他的可编程阵列是( B ) A 、与阵列 B 、或阵列 C 、与阵列和或阵列都可以 D 、以上说法都不对 9.A/D 转换器中,转换速度最高的为( A )转换 A 、并联比较型 B 、逐次逼近型 C 、双积分型 D 、计数型 10.关于PAL 器件与或阵列说确的是 ( A ) A 、 只有与阵列可编程 B 、 都是可编程的 C 、 只有或阵列可编程 D 、 都是不可编程的 11. 当三态门输出高阻状态时,输出电阻为 ( A ) A 、无穷大 B 、约100欧姆 C 、无穷小 D 、约10欧姆 12为使采样输出信号不失真地代表输入模拟信号,采样频率 f s 和输入模

数电期末模拟题及答案

《数字电子技术》模拟题一 一、单项选择题(2×10分) 1.下列等式成立的是( ) A 、 A ⊕1=A B 、 A ⊙0=A C 、A+AB=A D 、A+AB=B 2.函数F=(A+B+C+D)(A+B+C+D)(A+C+D)的标准与或表达式是( ) A 、F=∑m(1,3,4,7,12) B 、F=∑m(0,4,7,12) C 、F=∑m(0,4,7,5,6,8,9,10,12,13,14,15) D 、F=∑m(1,2,3,5,6,8,9,10,11,13,14,15) 3.属于时序逻辑电路的是( )。 A 、寄存器 B 、ROM C 、加法器 D 、编码器 4.同步时序电路和异步时序电路比较,其差异在于后者( ) A 、没有触发器 B 、没有统一的时钟脉冲控制 C 、没有稳定状态 D 、输出只与内部状态有关,与输入无关 5.将容量为256×4的RAM 扩展成1K ×8的RAM ,需( )片256×4的RAM 。 A 、 16 B 、2 C 、4 D 、8 6.在下图所示电路中,能完成01=+n Q 逻辑功能的电路有( ) 。 A 、 B 、 C 、 D 、 7.函数F=A C+AB+B C ,无冒险的组合为( )。 A 、 B=C=1 B 、 A=0,B=0 C 、 A=1,C=0 D 、 B=C=O 8.存储器RAM 在运行时具有( )。 A 、读功能 B 、写功能 C 、读/写功能 D 、 无读/写功能 9.触发器的状态转换图如下,则它是: ( ) A 、T 触发器 B 、RS 触发器 C 、JK 触发器 D 、D 触发器 10.将三角波变换为矩形波,需选用 ( ) A 、多谐振荡器 B 、施密特触发器 C 、双稳态触发器 D 、单稳态触发器 二、判断题(1×10分) ( )1、在二进制与十六进制的转换中,有下列关系: (1001110111110001)B =(9DF1)H ( )2、8421码和8421BCD 码都是四位二进制代码。 ( )3、二进制数1001和二进制代码1001都表示十进制数9。 ( )4、TTL 与非门输入采用多发射极三极管,其目的是提高电路的开关速度。 ( )5、OC 与非门的输出端可以并联运行,实现“线与”关系,即L=L 1+L 2 ( )6、CMOS 门电路中输入端悬空作逻辑0使用。 ( )7、数字电路中最基本的运算电路是加法器。 ( )8、要改变触发器的状态,必须有CP 脉冲的配合。

数字电子技术试题及答案(题库)

《数字电子技术》试卷 姓名:__ _______ 班级:__________ 考号:___________ 成绩:____________ 1. 有一数码10010011,作为自然二进制数时,它相当于十进制数( ),作为8421BCD 码时,它相当于 十进制数( )。 2.三态门电路的输出有高电平、低电平和( )3种状态。 3.TTL 与非门多余的输入端应接( )。 4.TTL 集成JK 触发器正常工作时,其d R 和d S 端应接( )电平。 5. 已知某函数??? ??+??? ??++=D C AB D C A B F ,该函数的反函数F =( ) 。 6. 如果对键盘上108个符号进行二进制编码,则至少要( )位二进制数码。 7. 典型的TTL 与非门电路使用的电路为电源电压为( )V ,其输出高电平为( )V ,输出低电平为( )V , CMOS 电路的电源电压为( ) V 。 8.74LS138是3线—8线译码器,译码为输出低电平有效,若输入为A 2A 1A 0=110时,输出 01234567Y Y Y Y Y Y Y Y 应为( )。 9.将一个包含有32768个基本存储单元的存储电路设计16位为一个字节的ROM 。该ROM 有( )根地址线,有( )根数据读出线。 10. 两片中规模集成电路10进制计数器串联后,最大计数容量为( )位。 11. );Y 3 =( )。

12. 某计数器的输出波形如图1所示,该计数器是( )进制计数器。 13.驱动共阳极七段数码管的译码器的输出电平为( )有效。 二、单项选择题(本大题共15小题,每小题2分,共30分) (在每小题列出的四个备选项中只有一个是最符合题目要求的,请将其代码填写在题后的括号内。错选、多选或未选均无分。) 1. 函数F(A,B,C)=AB+BC+AC 的最小项表达式为( ) 。 A .F(A,B,C)=∑m (0,2,4) B. (A,B,C)=∑m (3,5,6,7) C .F(A,B,C)=∑m (0,2,3,4) D. F(A,B,C)=∑m (2,4,6,7) 2.8线—3线优先编码器的输入为I 0—I 7 ,当优先级别最高的I 7有效时,其输出012Y Y Y ??的值是( )。 A .111 B. 010 C. 000 D. 101 3.十六路数据选择器的地址输入(选择控制)端有( )个。 A .16 B.2 C.4 D.8 4. 有一个左移移位寄存器,当预先置入1011后,其串行输入固定接0,在4个移位脉冲CP 作用下,四位数据的移位过程是( )。 A. 1011--0110--1100--1000--0000 B. 1011--0101--0010--0001--0000 C. 1011--1100--1101--1110--1111 D. 1011--1010--1001--1000--0111 5.已知74LS138译码器的输入三个使能端(E 1=1, E 2A = E 2B =0)时,地址码A 2A 1A 0=011,则输出 Y 7 ~Y 0是( ) 。 A. 11111101 B. 10111111 C. 11110111 D. 11111111 6. 一只四输入端或非门,使其输出为1的输入变量取值组合有( )种。 A .15 B .8 C .7 D .1 7. 随机存取存储器具有( )功能。 A.读/写 B.无读/写 C.只读 D.只写 8.N 个触发器可以构成最大计数长度(进制数)为( )的计数器。

哈工大数字电路实验报告实验一

数字逻辑电路与系统上机实验报告 实验一组合逻辑电路的设计与仿真 学校:哈尔滨工业大学 院系:电信学院通信工程系 班级:1205102 学号:11205102 姓名: 哈尔滨工业大学

实验一组合逻辑电路的设计与仿真 2.1 实验要求 本实验练习在Maxplus II环境下组合逻辑电路的设计与仿真,共包括5个子实验,要求如下:

2.2三人表决电路实验 2.2.1 实验目的 1. 熟悉MAXPLUS II原理图设计、波形仿真流程 2. 练习用门电路实现给定的组合逻辑函数 2.2.2 实验预习要求 1. 预习教材《第四章组合逻辑电路》 2. 了解本次实验的目的、电路设计要求 2.2.3 实验原理 设计三人表决电路,其原理为:三个人对某个提案进行表决,当多数人同意时,则提案通过,否则提案不通过。 输入:A、B、C,为’1’时表示同意,为’0’时表示不同意; 输出:F,为’0’时表示提案通过,为’1’时表示提案不通过; 波形仿真。 2.2.4 实验步骤 1. 打开MAXPLUS II, 新建一个原理图文件,命名为EXP2_ 2.gdf。 2. 按照实验要求设计电路,将电路原理图填入下表。

制输入信号A、B、C的波形(真值表中的每种输入情况均需出现)。 4. 运行仿真器得到输出信号F的波形,将完整的仿真波形图(包括全部输入输

2.3 译码器实验 2.3.1实验目的 熟悉用译码器设计组合逻辑电路,并练习将多个低位数译码器扩展为一个高位数译码器。 2.3.2实验预习要求 1. 预习教材《4-2-2 译码器》一节 2. 了解本次实验的目的、电路设计要求 2.3.3实验原理 译码器是数字电路中的一种多输入多输出的组合逻辑电路,负责将二进制码或BCD码变换成按十进制数排序的输出信息,以驱动对应装置产生合理的逻辑动作。商品的译码器品种较多,有2-4线、3-8线、4-10线及4-16线等。本实验练习对双2-4线译码器74LS139的扩展,并用其实现特定的组合逻辑。74LS139包含两个2-4线译码器,其输入输出如下: 74LS139中译码器1真值表如下: 74LS139中译码器2真值表如下:

数字电路期末复习题

. 第一套 一、选择题(本大题共10道小题,每小题2分,共20分。) 1. 用编码器对16个信号进行编码,其输出二进制代码的位数是( ) A.2位 B.3位 C.4位 D.16位 2. 逻辑函数F=(A+B)(B+C )的对偶式F ′=( ) A.B A +B C B.AB+B C C. B A +C D.AB+B C 3.一个8选一数据选择器的地址输入端有_______个。( ) A.1 B.2 C.3 D.4 4.同步时序电路和异步时序电路比较,其差异在于后者( ) A.没有触发器 B.没有统一的时钟脉冲控制 C.没有稳定状态 D.输出只与内部状态有关 5. 如下图所示电路中,只有______不能实现Q n+1 =n Q 。( ) 6.下列各函数等式中无冒险现象的函数式有( ) A.F= F=C B +AC+A B+BC+A B +C A B.F=C A +BC+A B C.F=A C +BC+A B +A B D.C B +AC+A B 7.JK 触发器在CP 作用下,若状态必须发生翻转,则应使( ) A.J=K=0 B.J=K=1 C.J=O ,K=1 D.J=1,K=0 8. 下列电路中,不属于组合逻辑电路的是( ) A.编码器 B.全加器 C.寄存器 D.译码器 9. 可以用来实现并/串转换和串/并转换的器件是( ) A.计数器 B.全加器 C.移位寄存器 D.存储器 10. 自动产生矩形波脉冲信号为( ) A.施密特触发器 B.单稳态触发器 C.T 触发器 D.多谐振荡器

1. 八进制数(34.2 ) 8的等值二进制数为;十进制数98 的8421BCD 码 为。 2. 二极管内含PN结,PN结在导电性能上的最大特点是_______________。 3.函数 ) (D C A AB A Y+ + + = ,其反函数为,对偶式为。 4.常见的脉冲产生电路有,常见的脉冲整形电路有。 5. A/D转换器的主要参数有,。 6. 四位环型计数器和扭环形计数器,初始状态是1000,经过5个时钟脉冲后,状态分别为和。 7. 对于JK触发器的两个输入端,当输入信号相反时构成触发器,当输入信号相同时构成触发器。 8. 时序逻辑电路的输出不仅和____ ___有关,而且还与___ ________有关。 9. TTL或非门多余输入端应.三态门的输出除了有高、低电平外,还有一种输出状态叫态 10. D触发器的特征方程为,JK触发器的特征方程为。 三、作图题(本大题共2道小题,每小题6分,共12分。) 1、如下图所示,根据CP波形画出Q波形。(设各触发器的初态均为1) 2、试说明如下图所示的用555 定时器构成的电路功能,求出U T+、U T-和ΔU T, 得分 阅卷人

哈工大电工技术 试题

哈尔滨工业大(威海) 2003 /2004 学年 秋 季学期 电工技术 试题(A) 题号 一 二 三 四 五 六 七 八 九 十 总分 附加题 分数 一、选择与填空( 20分 ,1-7每题 2分,8题每空2分) 1.图(1)所示电路中,a 、b 间的等效电阻为(4?)。 (1) (2) 2.试计算图(2)所示电路中的 A点的电位为(5V)。 3.将下图所示电路的ab 二端网络化成戴维南等效电路。 4.三相异步电动机的额定转速为 1460r/min 。当负载转矩为额定转矩的一 半时,电动机的转速为(1480r/min )。 姓名 班级: 注 意 行 为 规 范 遵 守 考 试 纪 律 10V I +-a b 0.5 I 1k Ω 1k Ω

5.电路如图所示,已知X L =R=X C ,并已知安培计A 的读数为5A ,则A 1的读数为(52A ),A 2的读数为(5A )。 6.有一交流铁心线圈,线圈匝数加倍,线圈的电阻及电源电压保持不变。铁心的磁感应强度将(增大、减小、不变),线圈中的电流将(增大、减 小 、不变) 7.将R L =8Ω的扬声器接在输出变压器的副绕组上,已知N1=300匝,N2=100匝,信号源电动势E=6V,内阻R0=100Ω,扬声器得到的功率为 (0.0876W)。 8.三相异步电动机的额定转速为1470转/分,电源电压为380V,三角形联接,功率为30kW ,效率为93%,功率因数为0.85。试计算额定转矩为(194.90N m ?);额定转差率为( 2% );额定电流为( 57.66A )。 二、图中N为无源电阻网络,已知当US=10V,IS=0时,UX=10V;当US=0,IS=1A时,UX=20V。求当US=20V,IS=3A时,UX为多少。(7分) 解: 由线性电路的叠加定理得: a s U + b s I = c x V 当V V s 10=时 V U I s s 10,0== 即 10a=10c + - U s + - U x

数电选择题答案及详解

1 : 对于JK触发器,输入J=0,K=1,CLK脉冲作用后,触发器的次态应为()。(2分) A:0 B:1 C:Q' D:不确定 您选择的答案: 正确答案: A 知识点:JK触发器的特性为:J=1,K=1时,Q状态为翻转,即Q= Q’ 2 : 已知Y=A+AB′+A′B,下列结果中正确的是()(2分) A:Y=A B:Y=B C:Y=A+B D:Y=A′+B′ 您选择的答案: 正确答案: C 知识点:利用公式A+AB′=A和A+A′B=A+B进行化简 3 : (1001111)2的等值十进制数是()(2分) A:97 B:15.14 C:83 D:79 您选择的答案: 正确答案:D 知识点:把二进制数转换为等值的十进制数,只需将二进制数按多项式展开,然后把所有各项的数值按十进制数相加。 4 : 图中为CMOS门电路,其输出为()状态(2分)(对于CMOS门电路,输入端接负载时,输入电平不变) A:高电平 B:低电平 C:高阻态 D:不确定 您选择的答案: 正确答案: A 知识点:对于CMOS门电路,输入端接负载时,输入电平不变

5 : 四选一数据选择器的数据输出Y与数据输入Di和地址码Ai之间的逻辑表达式为Y=()(2分) A:A1′A0′D0+ A1′A0D1+ A1A0′D2+ A1A0D3 B:A1′A0′D0 C: A1′A0D1 D:A1A0′D2 您选择的答案: 正确答案: A 知识点:四选一数据选择器的Y= A1′A0′D0+ A1′A0D1+ A1A0′D2+ A1A0D 6 : 一个同步时序逻辑电路可用()三组函数表达式描述(2分) A:最小项之和、最大项之积和最简与或式 B:逻辑图、真值表和逻辑式 C:输出方程、驱动方程和状态方程 D:输出方程、特性方程和状态方程 您选择的答案: 正确答案: C 知识点:时序逻辑电路的逻辑关系需用三个方程即输出方程、驱动方程及状态方程来描述。 7 : (1010.111)2的等值八进制数是()(2分) A:10. 7 B:12. 7 C:12. 5 D:10. 5 您选择的答案: 正确答案: B 知识点:把每三位二进制数分为一组,用等值的八进制数表示。 8 : 一位十六进制数可以用()位二进制数来表示。(2分) A:1 B:2 C:4 D:16 您选择的答案: 正确答案: C 知识点: 9 : TTL同或门和CMOS同或门比较,它们的逻辑功能一样吗?(2分)

哈工大数电实验

姓名班级学号 实验日期节次教师签字成绩 可调频双花型彩灯控制器 1.实验目的 在许多场合可以看到LED彩灯。LED彩灯由于其丰富的灯光色彩,低廉的造价以及控制简单等特点而得到了广泛的应用。为了将数字电路的知识灵活的运用到实际应用中,现设计一个能够控制闪烁频率并且能变换花型的LED彩灯的控制电路。 2.总体设计方案或技术路线 由该控制电路的功能可知,该控制器的电路由三部分构成,第一部分是时钟脉冲发生电路,第二部分是花型选择电路,第三部分是花型产生电路。首先,要做变频,可以通过给定不同频率的时钟脉冲来控制,而555定时器构成的多谐振荡电路恰好有输出不同频率波形的功能,通过改变外接电阻阻值即可轻松改变输出波形的频率,所以这一部分用555定时器来产生不同频率的脉冲,再用2/8分频器分频;受到实验室的实验箱的限制,本次实验仅产生两种花型做演示,选择电路由74LS138译码器完成;花型彩灯的花型需要序列脉冲发生器产生,移位寄存器74LS194组成的脉冲发生器可以实现此功能。 3.实验电路图

4.仪器设备名称、型号和技术指标 实验箱、555定时器*1、74LS138*1、74LS93*1、74LS194*2、74LS20*1、74LS32、5kΩ电阻*1、10kΩ滑动变阻器*1、1μF电容*2 5.理论分析或仿真分析结果 电路接通后,555定时器输出端开始产生脉冲信号,由于此时频率较高,不便于观察,所以需降频,经过2/8分频器之后,频率有明显下降,将此信号接到译码器的G1端,译码器B、C端接低电平,A端手动控制,Y0、Y1端分别接到两个74LS194芯片的CP端,当A接低电平时,Y0有效,此时第一个194芯片被选中,A接高电平,第二个194芯片被选中。下表为要实现的花型,按此表画卡诺图并化简,得到花型1的 D SR=~(Q A Q B Q C Q D),花型1的D SR=~Q D,并由此连接电路。两片194芯片的输出通过或门 9 10000001

数电选择题2及答案详解

1 : (110.1)2的等值十六进制数是()(2分) A:110.1 B:15. 5 C:6. 8 D:2. 1 您选择的答案: 正确答案: C 知识点:把每四位二进制数分为一组,用等值的十六进制数表示。 2 : 两输入的与门在下列()时可能产生竞争—冒险现象(2分)门电路两个输入信号同时向相反的逻辑电平跳变的现象称为竞争 A:一个输入端为0,另一个端为1 B:一个输入端发生变化,另一个端不变 C:两个不相等的输入端同时向相反的逻辑电平跳变 D:两个相等的输入端同时向相反的逻辑电平跳变 您选择的答案: 正确答案: C 知识点:门电路两个输入信号同时向相反的逻辑电平跳变的现象称为竞争 3 : 电路如下图所示,设起始状态Q2Q1=00,第3个上升沿,Q2Q1变为( ) (5分) A:00 B:01 C:10 D:11 您选择的答案: 正确答案:D 知识点:参考T触发器的特性表 您选择的答案: 正确答案: A 4 : 逻辑函数Y(A, B, C, D)=∑m(0,2,4,6,9,13) + d(1,3,5,7,11,15)的最简与或式为()(5分) A:AD+A’D’ B:A’+D C: A+D D:A’C+AD 您选择的答案: 正确答案: B 知识点:化简具有无关项的逻辑函数最好用卡诺图的方法。 5 : 图中为TTL门电路,其输出为()状态(2分)

A:高电平 B:低电平 C:高阻态 D:不确定 您选择的答案: 正确答案: C 知识点:图示中,控制端低电平电平有效。控制端无效时输出为高阻态 6 : 逻辑函数Y=(A’+D)(A C+B C’) ’+A B D’ 的Y’ 是()(2分) A:(AD’+(A’+C’)(B’+C))(A’+B’+D) B:(AD’+((A’+C’)(B’+C))’)(A’+B’+D) C:AD’+(A’+C’)(B’+C)(A’+B’+D) D:AD’+((A’+C’)(B’+C))’(A’+B’+D) 您选择的答案: 正确答案: B 知识点:利用反演定理求Y’时,要注意:利用加括号的方式保证原来的运算顺序不变;非单个变量上的非号不变。 7 : ()的特性方程为Q*=A (2分) A: D触发器 B:T触发器 C:JK触发器 D: SR触发器 您选择的答案: 正确答案: A 知识点:D触发器的特性方程为Q*=D 8 : 组合逻辑电路消除竞争冒险的方法有((2分) A:修改逻辑设计 B:在输出端接入滤波电容 C:后级加缓冲电路 D:屏蔽输入信号的尖峰干扰 您选择的答案: 正确答案: B 知识点:输出端接入滤波电容可以滤除竞争冒险产生的尖峰 9 : (1001111)2的等值十进制数是()(2分) A:97 B:15.14 C:83 D:79 您选择的答案: 正确答案:D

哈工大数电自主实验 数字流水灯

Harbin Institute of Technology 数字电路自主设计实验 院系:航天学院 班级: 姓名: 学号: 指导教师: 哈尔滨工业大学

一、实验目的 1.进一步掌握数字电路课程所学的理论知识。 2.熟悉几种常用集成数字芯片的功能和应用,并掌握其工作原理,进一步学会使用其进行电路设计。 3.了解数字系统设计的基本思想和方法,学会科学分析和解决问题。 4.培养认真严谨的工作作风和实事求是的工作态度。 5.数电课程实验为我们提供了动手实践的机会,增强动手实践的能力。 二、实验要求 设计流水灯,即一排灯按一定的顺序逐次点亮,且可调频、暂停、步进。 三、实验步骤 1.设计电路实现题目要求,电路在功能相当的情况下设计越简单越好; 2. 画出电路原理图(或仿真电路图); 3.元器件及参数选择; 4.电路仿真与调试; 5.到实验时进行电路的连接与功能验证,注意布线,要直角连接,选最短路径,不要相互交叉,注意用电安全,所加电压不能太高,以免烧坏芯片; 6.找指导教师进行实验的检查与验收; 7.编写设计报告:写出设计与制作的全过程,附上有关资料和图纸,心得体会。 四、实验原理 设计流水灯的方法有很多种,我的设计思路是: 利用555定时器产生秒脉冲信号,74LS161组成8进制计数器,74LS138进行译码,点亮电平指示灯。并通过调节555的电阻,实现频率可调。通过两与非门,实现暂停、步进功能。

1.秒信号发生器 (1)555定时器结构(2)555定时器引脚图 (3)555定时器功能表 (4)555定时器仿真图

2. 74LS161实现8进制加计数 74LS161是常用的四位二进制可预置的同步加法计数器,它可以灵活地运用在各种数字电路,以及单片机系统中实现分频器等很多重要的功能。 (1)74LS161同步加法器引脚图 管脚图介绍: 始终CP和四个数据输入端 P0-P3 清零CLR 使能EP,ET 置数PE 数据输出端Q0-Q3 进位输出TC (2)74LS161功能表 (5)74LS161仿真图 对74LS161进行八进制计数改组,需要一个与非门,即芯片74LS00,也就是将74LS161的输出端通过与非门,当输出为8时将输出为高电平的端口与非后接到74LS161的清零段。即计数到8是异步清零,所以74LS161变为八进制计数。

《数字电路》期末模拟试题及答案

数字电子电路 模拟试题-3 题 号 一 二 三 四 总 分 得 分 一、填空题(共30分) 1. 逻辑变量的异或表达式为: _____________________ =⊕B A B A B A + 2. 二进制数A=1011010;B=10111,则A -B=__(1000011)2_____。 3. 组合电路没有______功能,因此,它是由______组成。 4. 同步RS 触发器的特性方程为:Q n+1 =______,其约束方程为:______。 5. 将BCD 码翻译成十个对应输出信号的电路称为________,它有___个输入 端,____输出端。 6. 下图所示电路中,Y 1 =______;Y 2 =______;Y 3 =______。 二、选择题(共 20分) 1. 四个触发器组成的环行计数器最多有____个有效状态。 A.4 B. 6 C. 8 D. 16 2. 逻辑函数D C B A F +=,其对偶函数F * 为________。 A .( )()D C B A ++ B. ()()D C B A ++ C. ()()D C B A ++ 得 分 评 卷 人 得 分 评 卷 人 A 1 B Y 2 A B C Y 1 A B Y 3

3. 用8421码表示的十进制数65,可以写成______。 A .65 B. [1000001]BCD C. [01100101]BCD D. [1000001]2 4. 用卡诺图化简逻辑函数时,若每个方格群尽可能选大,则在化简后的最简表达式 中 。 A .与项的个数少 B . 每个与项中含有的变量个数少 C . 化简结果具有唯一性 5. 已知某电路的真值表如下,该电路的逻辑表达式为 。 A .C Y = B . AB C Y = C .C AB Y += D .C C B Y += A B C Y A B C Y 0 0 0 0 1 0 0 0 0 0 1 1 1 0 1 1 0 1 0 0 1 1 0 1 0 1 1 1 1 1 1 1 三、化简下列逻辑函数,写出最简与或表达式:(共20分) 1. 证明等式:AB B A B A B A +?=+ 2. Y 2=Σm (0,1,2,3,4,5,8,10,11,12) 3. Y 3=ABC C AB C B A C B A +++? 四、分析设计题 (共 30分) 1.双四选一数据选择器如图所示,其功能表达式如下。现要实现八选一数据选择器的功能(地址信号为 A 2A 1A 0,数据输入端信号为 D 7 ~ D 0 ) ,请画出电路连接图。 101130112011101101S A A D A A D A A D A A D Y ?++?+?=)( 201230122012101202S A A D A A D A A D A A D Y ?++?+?=)( 得 分 评 卷 人 得 分 评 卷 人 Y 1 Y 2 A S

电工学课件(哈工大)第三章_正弦交流电路资料

哈尔滨工业大学 电工学教研室 第3章正弦交流电路 返回

3.1 正弦电压与电流3.3 电阻元件、电感元件与电容元件3.4 电阻元件的交流电路3.5 电感元件的交流电路3.6 电容元件的交流电路 3.7 电阻、电感与电容元件的交流电路3.8 阻抗的串联与并联3.9 交流电路的频率特性3.10 功率因数的提高 目录 3.2 正弦量的相量表示法

3.1 正弦电压与电流 直流电和正弦交流电 前面两章分析的是直流电路,其中的电压和电流的大小 和方向是不随时间变化的。 I,U O t 直流电压和电流 返回

t i u O 正弦电压和电流 实际方向和参考方向一致 实际方向和参考方向相反 + - 正半周 实际方向和参考方向一致 + _ u R ⊕ i 负半周 实际方向和参考方向相反 + _ u R ⊕ i 正弦交流电的电压和电流是按照正弦规律周期性变化的。

3.1.1 频率和周期 正弦量变化一次所需要的时间(秒)称为周期(T )。每秒内变化的次数称为频率(),单位是赫兹(Hz )。 我国和大多数国家采用50Hz 的电力标准,有些国家(美国、日本等)采用60Hz 。 小常识 正弦量变化的快慢还可用角频率来表示:f T ππω22==t T 2 T 2 3T t ωπ π 2π3π 4T 2u i O f 频率是周期的倒数: f =1/T 已知=50Hz,求T 和ω。 [解]T =1/=1/50=0.02s, ω=2π=2×3.14×50=314rad/s f f f 例题3.1

3.1.2 幅值和有效值 瞬时值和幅值 正弦量在任一瞬间的值称为瞬时值,用小写字母表示,如、u、e等。 i 瞬时值中的最大的值称为幅值或最大值,用带下标m的大写字母表示,如I U m、E m等。 m、 有效值 在工程应用中常用有效值表示交流电的幅度。一般所讲的正 弦交流电的大小,如交流电压380V或220V,指的都是有效值。 有效值是用电流的热效应来规定的。设一交流电流和一直流 电流I 流过相同的电阻R,如果在交流电的一个周期内交流电和直 流电产生的热量相等,则交流电流的有效值就等于这个直流电的 电流I。

(完整版)数电试题及答案

通信 071~5 班 20 08 ~20 09 学年 第 二 学期 《数字电子技术基 础》 课试卷 试卷类型: A 卷 一、 单项选择题(每小题2分,共24分) 1、8421BCD 码01101001.01110001转换为十进制数是:( ) A :78.16 B :24.25 C :69.71 D :54.56 2、最简与或式的标准是:( ) A :表达式中乘积项最多,且每个乘积项的变量个数最多 B :表达式中乘积项最少,且每个乘积项的变量个数最多 C :表达式中乘积项最少,且每个乘积项的变量个数最少 D :表达式中乘积项最多,且每个乘积项的变量个数最多 3、用逻辑函数卡诺图化简中,四个相邻项可合并为一项,它能:( ) A :消去1个表现形式不同的变量,保留相同变量 B :消去2个表现形式不同的变量,保留相同变量 C :消去3个表现形式不同的变量,保留相同变量 表1 D :消去4个表现形式不同的变量,保留相同变量 4、已知真值表如表1所示,则其逻辑表达式为:( ) A :A ⊕B ⊕C B :AB + BC C :AB + BC D :ABC (A+B+C ) 5、函数F(A ,B ,C)=AB+BC+AC 的最小项表达式为:( ) A :F(A,B,C)=∑m (0,2,4) B :F(A,B,C)=∑m (3,5,6,7) C :F(A,B,C)=∑m (0,2,3,4) D :F(A,B,C)=∑m (2,4,6,7) 6、欲将一个移位寄存器中的二进制数乘以(32)10需要( )个移位脉冲。 A :32 B : 10 C :5 D : 6 7、已知74LS138译码器的输入三个使能端(E 1=1,E 2A =E 2B =0)时,地址码A 2A 1A 0=011,则输出Y 7 ~Y 0是:( ) A :11111101 B :10111111 C :11110111 D :11111111 8、要实现n 1n Q Q =+,JK 触发器的J 、K 取值应是:( ) A :J=0,K=0 B :J=0,K=1 C :J=1,K=0 D :J=1,K=1

数电期末复习题

练习 一、填空 (101)10=( )2 (5A、E)16=( )10 (3128)10=( )8421BCD 二、用卡诺图化简 F1(A,B,C,D)=Σm(5,6,8,10)+Σd(0,1,2,13,14,15) 三、选择 1、A、B、C是三个开关,每个开关有两个状态0和1,F为电灯,亮时为逻辑1,灭时为逻辑0;开关中出现1的个数为奇数时灯亮。若在三个不同的地方控制同一个电灯的灭亮,逻辑函数F的表达式应为 。 A. ABC B. A+B+C C. A⊕B⊕C D.A⊙B⊙C 2、逻辑函数F= = 。 A.B B.A C. D. 3、求一个逻辑函数F的反函数,可将F中的 。 A.变量不变 B.原变量换成反变量 反变量换成原变量 C.常数0换成1 1换成0 D.·换成+ +换成· 4、在 种输入情况下,“与非”运算的结果是逻辑0。 A.全部输入是1 B. 仅一输入是0 C. 全部输入是0 D. 任一输入是0 5、用四选一数据选择器实现函数Y=,应使 。 A.D0=D2=0,D1=D3=1 B.D0=D2=1,D1=D3=0 C.D0=D1=0,D2=D3=1 D.D0=D1=1,D2=D3=0 四、分析 下图为8选1数据选择器,写出输出F的表达式,化简F,说出电路功能,并用与非门画出电路。 D0 D1 D2 D3 D4 D5 D6 D7 A0 A1 A2 ST

Y MUX F 1 1 1 1 C B A 五、设计 1、有三位裁判员(A,B,C,其中C为主裁判),进行举重成绩判别,当主裁判和至少有一位副裁判认定成绩有效,该运动员的举重成绩才有效。要求设计逻辑电路,用4选1数据选择器实现。 2、某工厂有三条生产线,耗电分别为1号线10kW,2号线20kW,3号线30kW,生产线的电力由两台发电机提供,其中1号机20kW,2号机40kW。试设计一个供电控制电路,根据生产线的开工情况启动发电机,使电力负荷达到最佳配置。要求用译码器实现。

《数字电路》期末模拟考试试题及答案

数字电子电路模拟试题-2 一、填空题(共30分) 1. 三极管有NPN和PNP两种类型,当它工作在放大状态时,发射结____,集电结_ _____;NPN型三极管的基区是______型半导体,集电区和发射区是______型半导体。 2. 把高电压作为逻辑1,低电平作为逻辑0的赋值方法称作_______逻辑赋值。 一种电路若在正逻辑赋值时为与非门,则在负逻辑赋值时为________。 3. 四位二进制编码器有____个输入端;____个输出端。 4. 将十进制数287转换成二进制数是________;十六进制数是______ _。 5. 根据触发器功能的不同,可将触发器分成四种,分别是____触发器、____触 6. 下图所示电路中, 7. Y 2 二、选择题(共 20分) 1. 当晶体三极管____时处于饱和状态。 A. 发射结和集电结均处于反向偏置 B. 发射结正向偏置,集电结反向偏置 C. 发射结和集电结均处于正向偏置 2. 在下列三个逻辑函数表达式中,____是最小项表达式。 A.B A B A ) B ,A ( Y+ = B. C B C B A BC A ) C ,B , A ( Y+ + =

C. C AB ABC B C A C B A )D ,C ,B ,A (Y +++??= 3.用8421码表示的十进制数45,可以写成__________ A .45 B. [101101]BCD C. [01000101]BCD D. [101101]2 4.采用OC 门主要解决了_____ A .TTL 与非门不能相与的问题 B. TTL 与非门不能线与的问题 C. TTL 与非门不能相或的问题 5.已知某触发的特性表如下(A 、B 为触发器的输入)其输出信号的逻辑表达式为___ A . Q n+1 =A B. n n 1n Q A Q A Q +=+ C. n n 1n Q B Q A Q +=+ 三、化简下列逻辑函数,写出最简与或表达式:(共20分) 1. BC A C B A C B B A Y 1+?++= 2. Y 2=Σm (0,1,8,9,10,11) 3. Y 3见如下卡诺图 四、分析设计题 (共 30分)

数字电子技术基础试题及答案 (1)

数字电子技术基础期末考试试卷 一、填空题 1. 时序逻辑电路一般由 和 两分组成。 2. 十进制数(56)10转换为二进制数为 和十六进制数为 。 3. 串行进位加法器的缺点是 ,想速度高时应采用 加法器。 4. 多谐振荡器是一种波形 电路,它没有稳态,只有两个 。 5. 用6个D 触发器设计一个计数器,则该计数器的最大模值M= 。 二、化简、证明、分析综合题: 1.写出函数F (A,B,C,D) =A B C D E ++++的反函数。 2.证明逻辑函数式相等:()()BC D D B C AD B B D ++++=+ 3.已知逻辑函数F= ∑(3,5,8,9,10,12)+∑d(0,1,2) (1)化简该函数为最简与或式: (2)画出用两级与非门实现的最简与或式电路图: 4.555定时器构成的多谐振动器图1所示,已知R 1=1K Ω,R 2=Ω,C=μF 。试求脉冲宽度 T ,振荡频率f 和占空 比q 。 图1 5.某地址译码电路如图2所示,当输入地址变量A7-A0的状态分别为什么状态 ………………………密……………………封…………………………装…………………订………………………线……………………… 系别 专业(班级) 姓名 学号 ………

时,1Y 、6Y 分别才为低电平(被译中)。 图2 6.触发器电路就输入信号的波形如图3所示,试分别写出D 触发器的Q 和Q1的表达式,并画出其波形。 图3 D= Q n+1= Q 1= 7. 已知电路如图4所示,试写出: ①驱动方程; ②状态方程; ③输出方程; ④状态表; ⑤电路功能。 图4

哈工大数字电路实验报告实验二

数字逻辑电路与系统上机实验讲义 实验二时序逻辑电路的设计与仿真 课程名称:数字逻辑电路与系统 院系:电子与信息工程学院 班级:1205102 姓名: 学号:1120510 教师:吴芝路 哈尔滨工业大学 2014年12月

实验二时序逻辑电路的设计与仿真3.1实验要求 本实验练习在Maxplus II环境下时序逻辑电路的设计与仿真,共包括6个子实验,要求如下: 节序实验内容要求 3.2同步计数器实验必做 3.3时序电路分析实验必做 3.4移位寄存器实验必做 3.5三人抢答器实验必做 3.6串并转换电路实验选做 3.7奇数分频电路实验选做

3.2同步计数器实验 3.2.1实验目的 1.练习使用计数器设计简单的时序电路 2.熟悉用MAXPLUS II仿真时序电路的方法 3.2.2实验预习要求 1.预习教材《6-3计数器》 2.了解本次实验的目的、电路设计要求 3.2.3实验原理 计数器是最基本、最常用的时序逻辑电路之一,有很多品种。按计数后的输出数码来分,有二进制及BCD码等区别;按计数操作是否有公共外时钟控制来分,可分为异步及同步两类;此外,还有计数器的初始状态可否预置,计数长度(模)可否改变,以及可否双向等区别。 本实验用集成同步4位二进制加法计数器74LS161设计N分频电路,使输出信号CPO的频率为输入时钟信号CP频率的1/N,其中N=(学号后两位mod 8)+8。下表为74LS161的功能表。 CLR N LDN ENP ENT CLK D C B A QD QC QB QA CO 0----------------00000 10----↑D C B A D C B A0 1111↑--------加法计数0 1111↑--------11111 110------------QD n QC n QB n QA n 11--0---------- 3.2.4实验步骤 1.打开MAXPLUS II,新建一个原理图文件,命名为EXP3_ 2.gdf。 2.按照实验要求设计电路,将电路原理图填入下表。