流水灯基于Verilog语言实现及测试代码

流水灯实验的Testbench报告

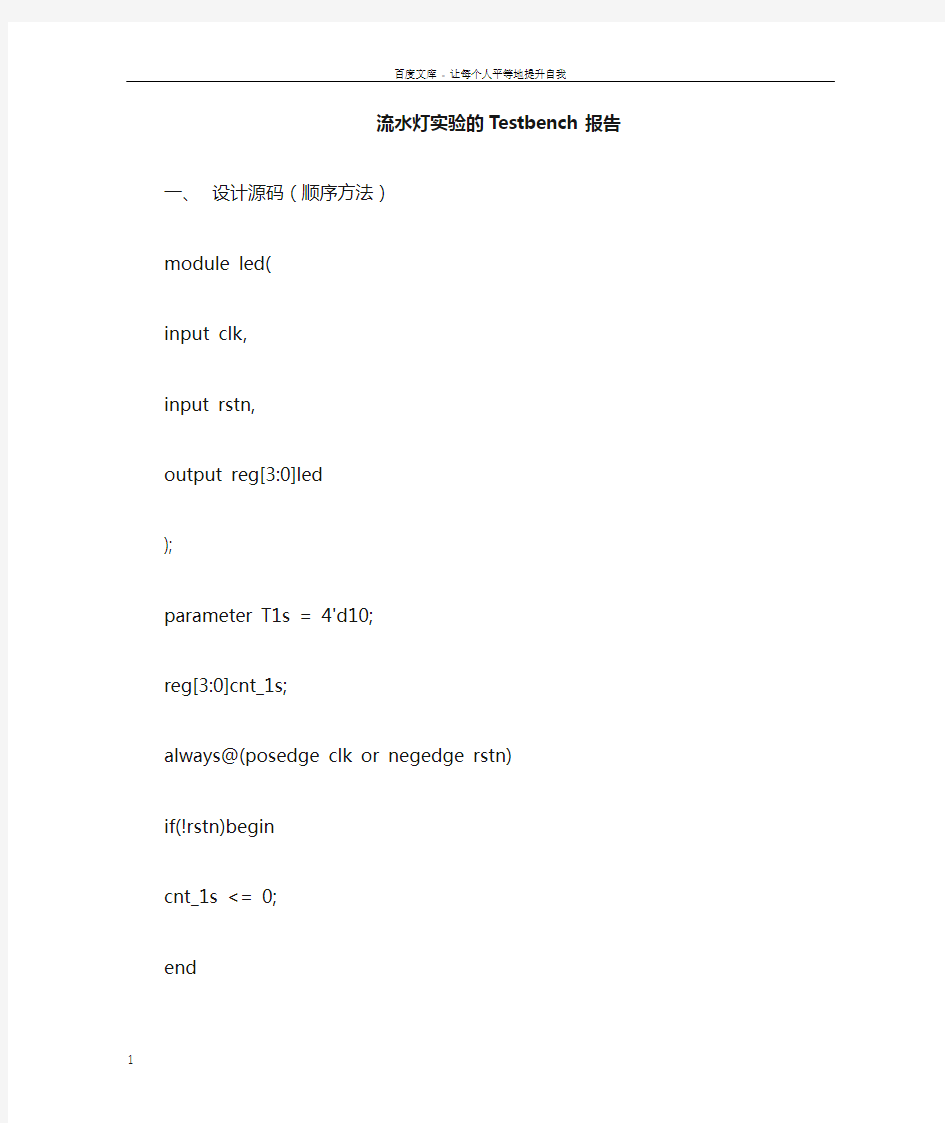

一、设计源码(顺序方法)

module led(

input clk,

input rstn,

output reg[3:0]led

);

parameter T1s = 4'd10;

reg[3:0]cnt_1s;

always@(posedge clk or negedge rstn)

if(!rstn)begin

cnt_1s <= 0;

end

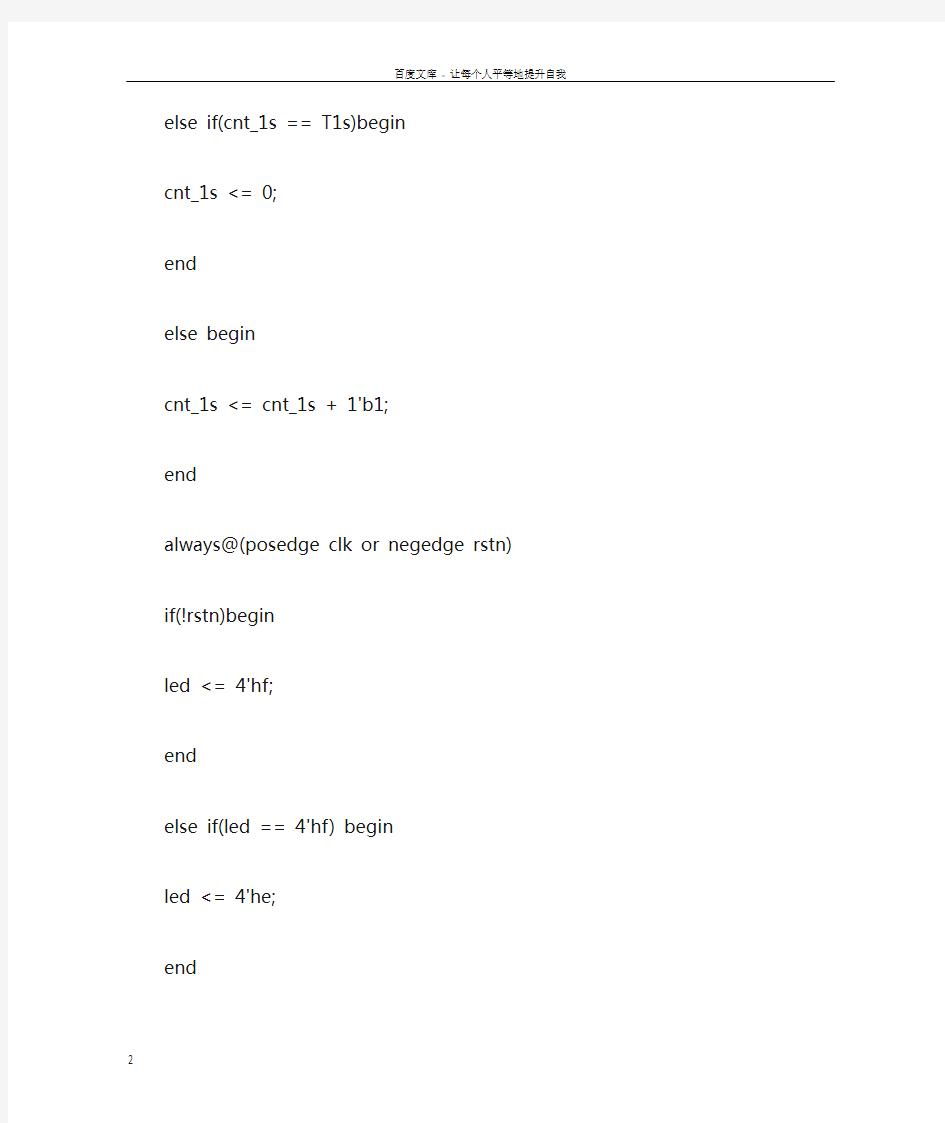

else if(cnt_1s == T1s)begin

cnt_1s <= 0;

end

else begin

cnt_1s <= cnt_1s + 1'b1;

end

always@(posedge clk or negedge rstn)

if(!rstn)begin

led <= 4'hf;

end

else if(led == 4'hf) begin

led <= 4'he;

end

else if(cnt_1s == T1s)begin

led <= {led[2:0],1'b1};

end

endmodule

二、测试代码

`timescale 1 ns/1 ns

module led_tb();

reg clk ;

reg rstn;

wire[3:0] led;

parameter CYCLE = 20;

parameter RST_TIME = 3 ;

led u( .clk (clk ),

.rstn (rstn ),

.led (led )

);

initial begin

clk = 0;

forever

#(CYCLE/2)

clk=~clk;

end

initial begin

rstn = 1;

#CYCLE;

rstn = 0;

#(CYCLE*RST_TIME);

rstn = 1;

end

endmodule

Testbench设计的几个步骤:

1、设定时间标尺、timescale;

2、定义信号类型,与输入对接的reg,与输出对接的wire;

3、对待测设计的顶层模块进行例化,即将testbench与待测设计接口对接;

4、给输入接口产生激励。

三、结果分析

老师的源代码中设置的流水灯跳转周期是1S钟,但是在仿真的过程中,1S 实在是太漫长了,所以我将跳转周期改为10个时钟周期了。

根据testbench可知,第一个时间周期结束,拉低复位信号。复位信号产生低电平,always块得到反应,led=4’hf(即1111);每次clk上升沿的时候always都会响应,但是rstn为低电平时,计数的变量cnt_1s会一直清零,led 一直处于全灭状态。我在TESTBENCH中设置的rstn拉低持续3时钟周期,3时钟周期后,rstn会变成高电平,在下一个clk上升沿,always又开始响应,根据设计当led原状态为1111,触发后会跳转为1110,即第一个led亮。

之后,按设计初衷应该是每过10个时钟周期,led产生一次流水式变化,但实际情况并非如此。

我们可以看到上图中黄线位置,led由0111经过10个时钟周期后变成1111,但是1111只持续了一个周期就变成了1110.原来,在第二个always

中有这么一句

else if(led == 4'hf) begin

led <= 4'he;

end

虽然计时变量cnt_1s未满足条件,但是led==1111,仍然会使led发生改变。

而且led==1111时,led是处于全灭状态,作为流水灯应该是不希望全灭状态的出现,第四个灯亮完,应该马上跳转到第一个灯。即便如此在实

物电路中,这并不会影响功能的实现,因为多出的这一个时钟周期仅为20ns,人的肉眼根本无法识别。

四、程序优化

试想如果这不是一个流水灯实验,而是一个对精度有很高要求的电路,不允许出现这么一段全1的状态,那么程序该如何修改?

其实led全为1的状态,主要是由于第二个always模块产生,所以只用修改第二个always的内容,下面是我修改后的代码,和运行结果。

这段代码主要的关键就在于阻塞赋值。

修改后:

运行结果:

对比运行结果,我们很容易发现,led没有再出现全1的状态,而是标准的按照10个时钟周期跳转一次,达到预期效果。

Verilog流水灯实验报告

流水灯实验报告 实验二流水灯 一、实验目的 学会编写一个简单的流水灯程序并掌握分频的方法。熟悉Modelsim仿真软件的使用。 二、实验要求 用Quartus编写流水灯程序,在Modelsim软件中进行仿真。 三、实验仪器和设备 1、硬件:计算机 2、软件:Quartus、Modelsim、(UE) 四、实验内容 1、将时钟周期进行分频。 2、编写Verilog程序实现LED等依次亮灭,用Modelsim进行仿真,绘制波形图。 五、实验设计 (一)分频原理 已知时钟周期f为50MHz,周期T为1/f,即20ns。若想得到四分频计数器,即周期为80ns的时钟,需要把时钟进行分频。即每四个时钟周期合并为一个周期。原理图如图1所示。 图1 四分频原理图 (二)流水灯设计思路 1、实现4盏LED灯依次隔1s亮灭,即周期为1s; 2、计算出频率f为1/T=1Hz; 3、设置计数器cnt,当检测到clk上升沿时开始计数,当cnt计数到24_999_999时,clk_4跳变为1,LED灯亮起,当cnt计数49_999_999时,clk_4置0,LED灯熄灭。 4、给LED赋初值4’b0001,第一盏灯亮。 5、利用位拼接,实现循环。 (三)设计框图 图2 设计基本框图 (四)位拼接的用法 若输入a=4'b1010,b=3'b101,c=4'b0101,想要使输出d=5'b10001 用位拼接,符号“{ }”:d<={b[2:1],c[1],a[2:1]} 即把b的低1~2位10,c的低1位0,a的低1~2位01拼接起来,得到10 0 01。 流水灯 4'b0001 4'b0010 4'b0100 4'b1000

VerilogHDL流水灯设计讲课稿

V e r i l o g H D L流水灯 设计

大规模数字逻辑题目:流水灯控制 专业电子信息科学与技术 班级 学号 学生姓名 设计时间 教师评分 2013年 12 月 10 日

目录 一、概述 0 二、设计目的 0 三、设计内容 0 四、设计原理图 (1) 五、引脚分配情况 (1) 六、源程序代码 (1) VerilogHDL 程序: (1) 分频器部分: (4) 七、心得体会 (5) 八、参考文献 (6)

一、概述 流水灯是一串按一定的规律像流水一样连续闪亮,流水灯控制是可编程控制器的一个应用,其控制思想在工业控制技术领域也同样适用。流水灯控制可用多种方法实现,但对现代可编程控制器而言,基于EDA技术的流水灯设计也是很普遍的。 二、设计目的 1、熟悉利用Quartus II 开发数字电路的基本流程和Quartus II 软件的相关操作。 2、掌握基本的设计思路,软件环境参数配置,仿真,管脚分配,利用JTAG/AS进行下载等基本操作。 3、了解VerilogHDL 语言设计或原理图设计方法。 4、通过本此设计,了解流水灯的工作原理,掌握其逻辑功能及设计方法。 三、设计内容 1、用VerilogHDL语言设计一个流水灯,输入0的时候led~led7,1Hz正向流水3次,然后全亮;然后2Hz逆向流水5次全亮;循环。输入1的时候led0~led7,0.5Hz奇数流水2次,全亮,1Hz偶数流水4次,全亮,然后循环。 2、用QuartusII 软件进行编译,仿真,下载到实验平台进行验证。

四、设计原理图 en为可调输入,输出为8位数据,为流水灯实验,试用8个LED指示灯来表示,具体引脚分配见下。 五、引脚分配情况 六、源程序代码 VerilogHDL 程序: module LED( clk,led,en ); input clk; input en; output [7:0]led;// 输出端口定义为寄存器型

VerilogHDL流水灯设计

大规模数字逻辑题目:流水灯控制 专业电子信息科学与技术 班级 学号 学生 设计时间 教师评分 2013年12 月10 日

目录 一、概述 (1) 二、设计目的 (1) 三、设计容 (1) 四、设计原理图 (2) 五、引脚分配情况 (2) 六、源程序代码 (2) VerilogHDL 程序: (2) 分频器部分: (5) 七、心得体会 (6) 八、参考文献 (7)

一、概述 流水灯是一串按一定的规律像流水一样连续闪亮,流水灯控制是可编程控制器的一个应用,其控制思想在工业控制技术领域也同样适用。流水灯控制可用多种方法实现,但对现代可编程控制器而言,基于EDA技术的流水灯设计也是很普遍的。 二、设计目的 1、熟悉利用Quartus II 开发数字电路的基本流程和Quartus II 软件的相关操作。 2、掌握基本的设计思路,软件环境参数配置,仿真,管脚分配,利用JTAG/AS 进行下载等基本操作。 3、了解VerilogHDL 语言设计或原理图设计方法。 4、通过本此设计,了解流水灯的工作原理,掌握其逻辑功能及设计方法。 三、设计容 1、用VerilogHDL语言设计一个流水灯,输入0的时候led~led7,1Hz正向流水3次,然后全亮;然后2Hz逆向流水5次全亮;循环。输入1的时候led0~led7,0.5Hz奇数流水2次,全亮,1Hz偶数流水4次,全亮,然后循环。 2、用QuartusII 软件进行编译,仿真,下载到实验平台进行验证。

四、设计原理图 en为可调输入,输出为8位数据,为流水灯实验,试用8个LED指示灯来表示,具体引脚分配见下。 五、引脚分配情况 六、源程序代码 VerilogHDL 程序: module LED( clk,led,en ); input clk; input en; output [7:0]led;// 输出端口定义为寄存器型

FPGA 用verilog语言写的花样流水灯包含四种变换

FPGA 用verilog语言写的花样流水灯包含四种变换 module ledwater(clk,rst,sla,slb,out); input clk,sla,slb,rst; output[7:0] out; reg[7:0] out,date,count; reg[3:0] h,l; reg flg; always@(posedge clk) if(rst) begin if(count==8'd128) begin count=8'd0; case({sla,slb}) 2'b00: begin date=~date;out=date;end 2'b01: begin date=date<<1;out=~date;if(date==8'b00000000)date=8'b11111111;end 2'b10: begin h=h>>1;l=l<<1;date={h,l};out=~date;if(date==8'b00000000)begin h=4'b1111;l=4'b1111;end end 2'b11: begin if(flg==1'b0)begin date=date<<1;out=~date;if(date==8'b00000000)begin date=8'b11111111; flg=1'b1;end end else begin date=date>>1;out=date;if(date==8'b00000000)begin date=8'b11111111; flg=1'b0;end end end endcase end else count=count+8'd1; end else begin date=8'b11111111;h=4'b1111;l=4'b1111;flg=1'b0;count=8'd0;end endmodule

Verilog流水灯实验报告

流水灯实验报告 实验二 流水灯 一、 实验目的 学会编写一个简单的流水灯程序并掌握分频的方法。熟悉Modelsim 仿真软件的使用。 二、 实验要求 用Quartus 编写流水灯程序,在Modelsim 软件中进行仿真。 三、 实验仪器和设备 1、 硬件:计算机 2、 软件:Quartus 、Modelsim 、(UE ) 四、 实验内容 1、 将时钟周期进行分频。 2、 编写Verilog 程序实现LED 等依次亮灭,用Modelsim 进行仿真,绘制波形图。 五、 实验设计 (一)分频原理 已知时钟周期f 为50MHz ,周期T 为1/f ,即20ns 。若想得到四分频计数器,即周期为80ns 的时钟,需要把时钟进行分频。即每四个时钟周期合并为一个周期。原理图如图1所示。 rst_n clk clk_4 图1 四分频原理图 (二)流水灯设计思路 1、实现4盏LED 灯依次隔1s 亮灭,即周期为1s ; 2、计算出频率f 为1/T=1Hz ; 3、设置计数器cnt ,当检测到clk 上升沿时开始计数,当cnt 计数到24_999_999时,clk_4跳变为1,LED 灯亮起,当cnt 计数49_999_999时,clk_4置0,LED 灯熄灭。 4、给LED 赋初值4’b0001,第一盏灯亮。 5、利用位拼接,实现循环。 (三)设计框图

FPGA clk cnt LED LED 图2 设计基本框图 (四)位拼接的用法 若输入a=4'b1010,b=3'b101,c=4'b0101,想要使输出d=5'b10001 用位拼接,符号“{ }”:d<={b[2:1],c[1],a[2:1]} 即把b 的低1~2位10,c 的低1位0,a 的低1~2位01拼接起来,得到10 0 01。 流水灯 4'b0001 4'b0010 4'b0100 4'b1000 相当于把低三位左移,并最高位放在最低位。 用位拼接可写为: led<={led[2:0], led[3]}; 低三位 最高位 六、 实验方法和步骤 (一)时钟分频 1、 编写分频程序。 2、 编写测试程序。 3、 进行仿真,波形如图3所示。 图3 分频仿真结果 (二)流水灯 1、编写分频程序。

LED灯移位显示,ise开发环境Verilog编程流水灯

DDPP课程设计 八位LED可控移位显示设计与实现 本设计基于Xilinx ISE Design Suite 13.2软件开发平台和其综合工具进行八位LED可控移位显示数字电路的功能设计,在FPGA BSSYS2开发板上来完成设计的测试和实现。 I、总体RTL SCHEMATIC 端口说明: CLK_IN:50MHZ时钟输入 C:控制左右移,0为 LED[0]-LED[7],1反之。 S:选择移动频率,共四档。 RST:重置 LED:点亮LED灯 II、源程序 module led_shiftingdisplay(LED,CLK_IN,RST,S,C); input CLK_IN,RST,C; input [1:0] S; output [7:0] LED; reg [25:0] cn; reg CLK; reg [7:0] LED; wire CLK_OUT;

wire CLK2_OUT; wire CLK3_OUT; wire CLK4_OUT; initial begin cn=0; end always @(posedge CLK_IN) begin if(cn==49999999) begin cn<=0; end else cn<=cn+26'd1; end assign CLK_OUT=cn[25]; //1HZ assign CLK2_OUT=cn[24]; //2HZ assign CLK3_OUT=cn[21]; //16HZ assign CLK4_OUT=cn[20]; //32HZ always @(S,CLK_OUT,CLK2_OUT,CLK3_OUT,CLK4_OUT) begin case(S) 2'd0:CLK<=CLK_OUT; 2'd1:CLK<=CLK2_OUT; 2'd2:CLK<=CLK3_OUT; 2'd3:CLK<=CLK4_OUT; endcase end initial begin LED=8'b00000000;end always @(posedge CLK) begin if(C) //C==1,left shifting if(RST) LED<=8'b00000001; else if(LED==8'b00000000) LED<=8'b00000001; else LED<=LED<<1; else //C==1,right shifting if(RST) LED<=8'b10000000; else if(LED==8'b00000000) LED<=8'b10000000; else LED<=LED>>1; end endmodule

VerilogHDL流水灯设计

VerilogHDL流水灯设计

大规模数字逻辑题目:流水灯控制 专业电子信息科学与技术 班级 学号 学生姓名 设计时间 教师评分 2013年12 月10 日

目录 一、概述 0 二、设计目的 0 三、设计内容 0 四、设计原理图 0 五、引脚分配情况 (1) 六、源程序代码 (1) VerilogHDL 程序: (1) 分频器部分: (11) 七、心得体会 (12) 八、参考文献 (13)

一、概述 流水灯是一串按一定的规律像流水一样连续闪亮,流水灯控制是可编程控制器的一个应用,其控制思想在工业控制技术领域也同样适用。流水灯控制可用多种方法实现,但对现代可编程控制器而言,基于EDA技术的流水灯设计也是很普遍的。 二、设计目的 1、熟悉利用Quartus II 开发数字电路的基本流程和Quartus II 软件的相关操作。 2、掌握基本的设计思路,软件环境参数配置,仿真,管脚分配,利用JTAG/AS 进行下载等基本操作。 3、了解VerilogHDL 语言设计或原理图设计方法。 4、通过本此设计,了解流水灯的工作原理,掌握其逻辑功能及设计方法。 三、设计内容 1、用VerilogHDL语言设计一个流水灯,输入0的时候led~led7,1Hz正向流水3次,然后全亮;然后2Hz逆向流水5次全亮;循环。输入1的时候led0~led7,0.5Hz奇数流水2次,全亮,1Hz偶数流水4次,全亮,然后循环。 2、用QuartusII 软件进行编译,仿真,下载到实验平台进行验证。 四、设计原理图

en为可调输入,输出为8位数据,为流水灯实验,试用8个LED指示灯来表示,具体引脚分配见下。 五、引脚分配情况 六、源程序代码 VerilogHDL 程序: module LED( clk,led,en ); input clk; input en; output [7:0]led;// 输出端口定义为寄存器型 reg [7:0] led; reg [8:0] state1;

流水灯基于Verilog语言实现及测试代码

流水灯实验的Testbench报告 一、设计源码(顺序方法) module led( inputclk, inputrstn, outputreg[3:0]led ); parameter T1s = 4'd10; reg[3:0]cnt_1s; always@(posedgeclk or negedgerstn) if(!rstn)begin cnt_1s <= 0; end else if(cnt_1s == T1s)begin cnt_1s <= 0; end else begin cnt_1s <= cnt_1s + 1'b1; end always@(posedgeclk or negedgerstn) if(!rstn)begin led<= 4'hf; end else if(led == 4'hf) begin led<= 4'he; end else if(cnt_1s == T1s)begin led<= {led[2:0],1'b1}; end endmodule 二、测试代码 `timescale 1 ns/1 ns moduleled_tb(); regclk ; regrstn; wire[3:0] led; parameter CYCLE = 20; parameter RST_TIME = 3 ;

led u( .clk (clk ), .rstn (rstn ), .led (led ) ); initial begin clk = 0; forever #(CYCLE/2) clk=~clk; end initial begin rstn = 1; #CYCLE; rstn = 0; #(CYCLE*RST_TIME); rstn = 1; end endmodule Testbench设计的几个步骤: 1、设定时间标尺、timescale; 2、定义信号类型,与输入对接的reg,与输出对接的wire; 3、对待测设计的顶层模块进行例化,即将testbench与待测设计接口对接; 4、给输入接口产生激励。 三、结果分析 老师的源代码中设置的流水灯跳转周期是1S钟,但是在仿真的过程中,1S 实在是太漫长了,所以我将跳转周期改为10个时钟周期了。

verilog- HDL实现流水灯

用verilog实现流水灯 module flow_deng( input wire pin_clk_in, input wire pin_rest_n , input wire [1:0] pin_ctrl, output reg [7:0] pin_led_out ); wire clk ; reg [31: 0] counter32; //fen ping always @ (posedge pin_clk_in or negedge pin_rest_n) begin if(pin_rest_n==1'b0) begin counter32 <= 32'b0; end else begin counter32 <= counter32+1'b1; end end assign clk = counter32[3] ; //16 fen pin reg [4:0] state; parameter [4:0] IDLE =5'b0_0001; parameter [4:0] RIGHT =5'b0_0010; parameter [4:0] LEFT =5'b0_0100; parameter [4:0] DOUB_LEFT =5'b0_1000; parameter [4:0] ERROR =5'b1_0000; reg [4:0] cur_sta; always @ (posedge clk or negedge pin_rest_n) begin if(pin_rest_n==1'b0) begin state <= IDLE ; end else begin case (state) IDLE : begin if (pin_ctrl==2'b00) begin state <= LEFT ; end else if (pin_ctrl==2'b01) begin

verilog流水灯

实验报告 (六) 流水灯设计 第四批1202121262 孙疆涛

流水灯设计 一实验任务与要求 任务:(1)设计实验使发光二极管循环点亮。 (2)要求:使实验板上7个发光二极管LD~LD7每隔3秒点亮一个 二实验程序 module liushuiled(clk,reset,z); input clk,reset; output [6:0]z; reg[2:0] state; reg[6:0]z; parameter S0=3'b000,S1=3'b001,S2=3'b011,S3=3'b010,S4=3'b110,S5=3'b111 ,S6=3'b101; always@(posedge clk) begin if(reset) state<=S0; else case(state) S0:state<=S1; S1:state<=S2; S2:state<=S3; S3:state<=S4;

S4:state<=S5; S5:state<=S6; S6: state<=S0; default state<=S0; endcase end always@(state) begin case (state) S0:z=7'b0111111; S1:z=7'b1011111; S2:z=7'b1101111; S3:z=7'b1110111; S4:z=7'b1111011; S5:z=7'b1111101; S6:z=7'b1111110; default:z=7'b0000000; endcase end endmodule 三实验结果与仿真 引脚分配

verilog语言的FPGA变速花样流水灯设计

基于XILINX--XSE500E型FPGA 的变速流水灯以及花样流水灯的verilog语言设计 摘要 临近大四毕业,诸多工科院校电子电科通信等专业会选择用FPGA项目作为课程设计的课题,笔者同样经历了这个过程,收获颇多,在此将设计成果在此分享,以帮助大家更好掌握FPGA设计。 FPGA种类繁多,时效性非常好,设计过程中十分注重实时性,在时间点控制上非常优秀。此次设计采用XILINX的XSE500E型芯片的开发板,芯片采用FG320型接口,速度级别-4。板载时钟50MHz,如需其他时钟周期,可采用IP核中的clocking,其中的 DCM可以实现变频,引入DCM,输入频率50MHz,输出频率填入需要的频率即可,之后进行实例化。此外,可以借助计数器进行延时减速,此次设计采用了计数器延时方法。 本次列举了四种流水灯相关设计:普通流水灯(向左和向右滚动),自动反复式流水灯(到最右端自动向左滚动,到左端自动向右滚动),花样流水灯,变速流水灯。 谢谢大家的支持! 正文 一,普通流水灯 1,建模思想 普通流水灯,可以向右滚动,到最右端返回最左端,也可以向左滚动,到最左端返回最右端。 普通流水灯模块涉及的端口有:clk,它是时钟输入,一般就是板载时钟,这里是50MHz,具体参照开发板说明。还有复位输入rst,高电平有效。此外就是led端口,这个端口有8根管脚,共8位,连接8个led灯。 采用verilog语言,端口定义格式如下: module led( input clk, input rst, output reg[7:0] led //此行定义说明led端口既是驱动管脚的,又是寄存器 ); 采用过程建模,这里不采用行为建模和功能建模,因为这个过程就是一个大循环,规律性极强。由于板载时钟50MHz,如果每个时钟周期都要滚动流水灯,那么速度是惊人的,人眼根本无法分辨。所以采用计数器延时,当计数达到约4千万时候,驱动系统进行动作,可以判断,也可以进行流水灯动作。 普通流水灯,需要判断流水灯是否到了尽头,如果到了尽头,需要回归起点。 每次上电之后,需要按一下复位,才能进行流水灯循环。 Rst的作用就是初始化,首先为led赋予一个初始状态,可以让一个灯循环,也可以让几个灯一起亮,一起循环。几个灯亮,关键在于rst初始化。 2,全部代码如下:这里列举右滚动流水灯 module led( //这行定义了模块名字为led input clk, input rst,

Verilog关于LED控制程序几例

1.下面的这段程序是通过Verilog语言编写程序实现让LED点亮的功能。有两种方法可以参考。 (A)利用连续赋值语句assign实现,文件名ledlight1.v 程序代码: module ledlight1 (LED); output [7:0] LED; assign LED=8’b10101010; endmodule (B)利用过程赋值语句来实现,文件名ledlight2.v 程序代码: module ledlight2 (LED); output [7:0] LED; reg [7:0] LED; always begin LED=8'b10101010; end endmodule ============================================================= 2.下面的这个程序是用Verilog语言控制8个数码管(共阳)接法,然后让它们隔一段时间(大约是1S)亮,然后隔一段时间又灭的一个程序。很简单的几句。 module shumaguanliangmie (LED,CLK); output[7:0] LED; input CLK; reg [7:0] LED; reg [24:0] counter; always@(posedge CLK) //在时钟负延跳变,也就是计数什么的 begin counter<=counter+1; //计数器加1 if(counter==25'b1_0111_1101_0111_1000_0100_0000) //这个数就是25000000 begin LED<=~LED; //求反,闪烁 counter<=0; //重新计数 end end endmodule =================================================================

VerilogHDL流水灯设计

V e r i l o g H D L流水灯设 计 Company Document number:WTUT-WT88Y-W8BBGB-BWYTT-19998

大规模数字逻辑题目:流水灯控制 专业电子信息科学与技术 班级 学号 学生姓名 设计时间 教师评分 2013年 12 月 10 日

目录

一、概述 流水灯是一串按一定的规律像流水一样连续闪亮,流水灯控制是可编程控制器的一个应用,其控制思想在工业控制技术领域也同样适用。流水灯控制可用多种方法实现,但对现代可编程控制器而言,基于EDA技术的流水灯设计也是很普遍的。 二、设计目的 1、熟悉利用Quartus II 开发数字电路的基本流程和Quartus II 软件的相关操作。 2、掌握基本的设计思路,软件环境参数配置,仿真,管脚分配,利用JTAG/AS进行下载等基本操作。 3、了解VerilogHDL 语言设计或原理图设计方法。 4、通过本此设计,了解流水灯的工作原理,掌握其逻辑功能及设计方法。 三、设计内容 1、用VerilogHDL语言设计一个流水灯,输入0的时候led~led7,1Hz正向流水3次,然后全亮;然后2Hz逆向流水5次全亮;循环。输入1的时候led0~led7,奇数流水2次,全亮,1Hz偶数流水4次,全亮,然后循环。 2、用QuartusII 软件进行编译,仿真,下载到实验平台进行验证。

四、设计原理图 en为可调输入,输出为8位数据,为流水灯实验,试用8个LED指示灯来表示,具体引脚分配见下。 五、引脚分配情况 六、源程序代码 VerilogHDL 程序: module LED( clk,led,en ); input clk; input en; output [7:0]led;国大学生电子设计获奖作品汇编[J].北京理工大学出版社,2005。 [2] 康华光 .电子技术基础-数字部分[M].高等教育出版社,1998。 [3] 谭会生等 . EDA技术及应用[M].西安电子科技大学出版社,2001 [4] 潘松,等.EDA技术实用教程[M].科学出版社,2006 [5] 雷伏容 HDL电路设计[M].清华大学出版社,2006 [6] Charles ,等.数字系统设计与HDL[M].电子工业出版社,2008

开发板上基于VERILOG编程语言实现流水灯控制(仿交通灯)

大规模数字电路课程设计设计题目:交通信号灯 专业电子信息科学与技术 班级电信091 学号200916022108 学生姓名陈恩雄 设计时间2011-2012学年上学期 教师评分 2011年12月5日

目录 一、实验目的: (2) 二、实验器材: (2) 三、实验步骤 (2) 四、设计思路及实现方法 (3) (1)设计思路 (3) (2)实现方法 (3) ①分频器 (3) ②状态控制 (4) (3)开发板管脚分配 (4) 五、程序代码 (5) 六、实验过程及结果 (8) 1、在线调试: (8) 2、管脚分配: (8) 3、开发板截图: (9) 七、设计总结与体会 (11) 设计中遇到的问题及解决方法 (11) 个人体会 (11)

一、实验目的: 1、系统功能: 实现十字路口的交通灯显示。 2、系统要求: (1)要求控制南北、东西方向各3个灯(红、黄、绿)的亮灭; (2)要求绿灯转红灯前,黄灯亮两秒; (3)要求南北向红灯亮16秒,同时东西向绿灯亮14秒,东西向绿灯转红灯前,黄灯亮亮秒;南北向红灯直接转成绿灯亮14秒,此时,东西向红灯亮16秒。, 3.、熟悉程序设计的基本流程 4.、熟悉开发板的应用 5、进一步巩固所学语言的熟练度 二、实验器材: 1.计算机、quartusⅡ软件 2.实验开发板 三、实验步骤 1,构思模块以及程序结构 2.分析程序结构 3.编写程序

4.程序的调试 5.在开发板上试验程序 四、设计思路及实现方法 (1)设计思路 使用V erilog语言,控制实验开发板LED灯LED0~LED7。其中led0~led2分别表示东西向红、黄、绿灯;led3~led5分别表示南北向红、黄、绿灯;led6不使用、led7每秒闪烁一次便于观察时间。 (2)实现方法 ①分频器 分频器实现的是将高频时钟信号转换成低频时钟信号,用于触发控制器、计数器和扫描显示电路。

verilog程序-流水灯

/**************************************************** 程序功能:流水灯 版本:1.1 版权:分享快乐 *****************************************************/ module liu_shui_deng( input wire pin_clk_in, input wire pin_rest_n , input wire [1:0] pin_ctrl, output reg [7:0] pin_led_out ); wire clk ; reg [31: 0] counter32; always @ (posedge pin_clk_in or negedge pin_rest_n) begin if(pin_rest_n==1'b0) begin counter32 <= 32'b0; end else begin counter32 <= counter32+1'b1; end end assign clk = counter32[3] ; reg [2:0] cur_sta,state parameter [2:0] IDLE =3'b000; parameter [2:0] RIGHT =5'b001; parameter [2:0] LEFT =5'b010; parameter [2:0] DOUB_LEFT =5'b011; parameter [2:0] ERROR =5'b100; always @ (posedge clk or negedge pin_rest_n) begin if(pin_rest_n==1'b0) begin state <= IDLE ; end else begin case (state) IDLE : begin if (pin_ctrl==2'b00) begin state <= LEFT ; end else if (pin_ctrl==2'b01) begin state <= RIGHT ; end else if (pin_ctrl==2'b10) begin

基于FPGA的verilog的流水灯程序

基于FPGA的流水灯verilog程序 `define cnt 17d7840 //cnt是计数量此处计时0.5s。我调试的板子晶振频 率是50MHZ。32’h17d7840就是0.5s 。这个十六 进制的数值你可以用电脑自带的计数器转换的。`define cnt_n 17d7841 //cnt值加一,用于下边的计数寄存器led_cnt的复位module led_new (clk,rest,led); input clk; input rest; output [7:0]led; reg [7:0]led; reg [7:0]led_n; reg [31:0] led_cnt; always@(posedge clk or negedge rest) begin if(!rest) led<=8'h80; else led<=led_n; end always@(*) begin if(!rest) led_n=8'h00; else if(led_cnt==32'h`cnt) led_n={led[6:0],led[7]}; else led_n=led; end always@(posedge clk or negedge rest) begin if(!rest) led_cnt<=32'h0; else if(led_cnt==32'h`cnt_n) led_cnt<=32'h0; else led_cnt<=led_cnt+1'b1; end endmodule

十进制数转换成十六进制的操作: 先在电脑的开始》附件》计数器;打开计数器,点击“科学型”,窗口右边的键盘输入你想要的计数值,然后再点十六进制就行了 QUARTUS II里面的引脚绑定 其中clk是芯片内部时钟,仔细观察板子,观察晶振连进板子的那个引脚就是时钟引脚了。我板子上边标示的是clk0/17。 注意:把程序复制进去的时候请把那些注释删掉,因为我写那些注释只是在WORD文档写而已的。格式不对

VerilogHDL流水灯设计

V e r i l o g H D L流水灯设计 Prepared on 24 November 2020

大规模数字逻辑题目:流水灯控制 专业电子信息科学与技术 班级 学号 学生姓名 设计时间 教师评分 2013年 12 月 10 日

目录

一、概述 流水灯是一串按一定的规律像流水一样连续闪亮,流水灯控制是可编程控制器的一个应用,其控制思想在工业控制技术领域也同样适用。流水灯控制可用多种方法实现,但对现代可编程控制器而言,基于EDA技术的流水灯设计也是很普遍的。 二、设计目的 1、熟悉利用Quartus II 开发数字电路的基本流程和Quartus II 软件的相关操作。 2、掌握基本的设计思路,软件环境参数配置,仿真,管脚分配,利用JTAG/AS进行下载等基本操作。 3、了解VerilogHDL 语言设计或原理图设计方法。 4、通过本此设计,了解流水灯的工作原理,掌握其逻辑功能及设计方法。 三、设计内容 1、用VerilogHDL语言设计一个流水灯,输入0的时候led~led7,1Hz正向流水3次,然后全亮;然后2Hz逆向流水5次全亮;循环。输入1的时候led0~led7,奇数流水2次,全亮,1Hz偶数流水4次,全亮,然后循环。 2、用QuartusII 软件进行编译,仿真,下载到实验平台进行验证。

四、设计原理图 en为可调输入,输出为8位数据,为流水灯实验,试用8个LED指示灯来表示,具体引脚分配见下。 五、引脚分配情况 六、源程序代码 VerilogHDL 程序: module LED( clk,led,en ); input clk; input en; output [7:0]led;国大学生电子设计获奖作品汇编[J].北京理工大学出版社,2005。 [2] 康华光 .电子技术基础-数字部分[M].高等教育出版社,1998。 [3] 谭会生等 . EDA技术及应用[M].西安电子科技大学出版社,2001 [4] 潘松,等.EDA技术实用教程[M].科学出版社,2006 [5] 雷伏容 HDL电路设计[M].清华大学出版社,2006 [6] Charles ,等.数字系统设计与HDL[M].电子工业出版社,2008