RC-4;中文规格书,Datasheet资料

TPA2038D1YFFR,TPA2038D1YFFR,TPA2038D1YFFR,TPA2038D1YFFT,TPA2038D1YFFEVM, 规格书,Datasheet 资料

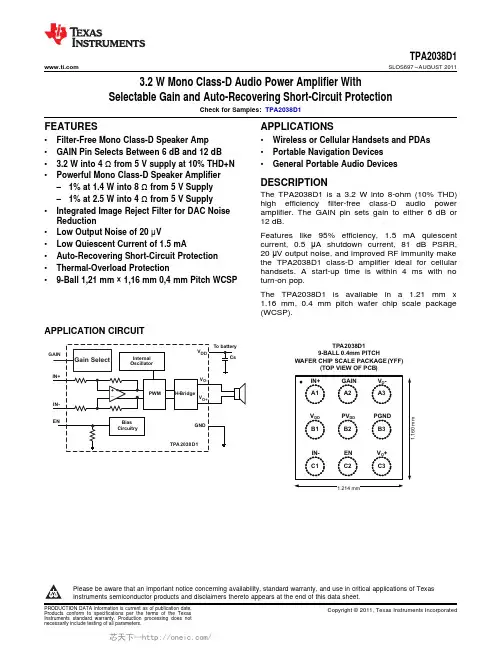

TPA2038D19-BALL0.4mm PITCHWAFER CHIP SCALE PACKAGE(YFF)(TOP VIEW OF PCB)TPA2038D1 SLOS697–AUGUST20113.2W Mono Class-D Audio Power Amplifier WithSelectable Gain and Auto-Recovering Short-Circuit ProtectionCheck for Samples:TPA2038D1FEATURES APPLICATIONS•Filter-Free Mono Class-D Speaker Amp•Wireless or Cellular Handsets and PDAs•GAIN Pin Selects Between6dB and12dB•Portable Navigation Devices• 3.2W into4Ωfrom5V supply at10%THD+N•General Portable Audio Devices•Powerful Mono Class-D Speaker AmplifierDESCRIPTION–1%at1.4W into8Ωfrom5V SupplyThe TPA2038D1is a3.2W into8-ohm(10%THD)–1%at2.5W into4Ωfrom5V Supply high efficiency filter-free class-D audio power•Integrated Image Reject Filter for DAC Noise amplifier.The GAIN pin sets gain to either6dB or Reduction12dB.•Low Output Noise of20μV Features like95%efficiency, 1.5mA quiescent•Low Quiescent Current of1.5mA current,0.5μA shutdown current,81dB PSRR,20μV output noise,and improved RF immunity make •Auto-Recovering Short-Circuit Protectionthe TPA2038D1class-D amplifier ideal for cellular •Thermal-Overload Protection handsets.A start-up time is within4ms with no•9-Ball1,21mm×1,16mm0,4mm Pitch WCSP turn-on pop.The TPA2038D1is available in a 1.21mm x1.16mm,0.4mm pitch wafer chip scale package(WCSP).APPLICATION CIRCUITPlease be aware that an important notice concerning availability,standard warranty,and use in critical applications of TexasInstruments semiconductor products and disclaimers thereto appears at the end of this data sheet.TPA2038D1SLOS697–These devices have limited built-in ESD protection.The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.ORDERING INFORMATIONT A PACKAGED DEVICES(1)PART NUMBER(2)SYMBOLTPA2038D1YFFR QWK -40°C to85°C9-ball WCSPTPA2038D1YFFT QWK(1)For the most current package and ordering information,see the Package Option Addendum at the end of this document,or see the TIWeb site at (2)The YFF package is only available taped and reeled.The suffix"R"indicates a reel of3000,the suffix"T"indicates a reel of250. ABSOLUTE MAXIMUM RATINGSover operating free-air temperature range,T A=25°C(unless otherwise noted)(1)VALUE UNITIn active mode–0.3to6.0VV DD,PV DD Supply voltageIn shutdown mode–0.3to6.0VV I Input voltage EN,IN+,IN––0.3to V DD+0.3VR L Minimum load resistance 3.2ΩOutput continuous total power dissipation See Dissipation Rating TableT A Operating free-air temperature range–40to85°CT J Operating junction temperature range–40to150°CT stg Storage temperature range–65to85°C (1)Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device.These are stress ratingsonly,and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied.Exposure to Absolute Maximum Ratings conditions for extended periods may affect device reliability.DISSIPATION RATINGSPACKAGE DERATING FACTOR(1)T A<25°C T A=70°C T A=85°CYFF(WCSP) 4.2mW/°C525mW336mW273mW(1)Derating factor measure with high K board.RECOMMENDED OPERATING CONDITIONSMIN MAX UNIT V DD,Class-D supply voltage 2.5 5.5VPV DDV IH High-level input voltage EN,GAIN 1.3VV IL Low-level input voltage EN,GAIN0.35VV IC Common mode input voltage range V DD=2.5V,5.5V,CMRR≥49dB0.75V DD-1.1VT A Operating free-air temperature–4085°C GAIN SETTINGGAIN PIN GAIN SETTINGGND12dBVDD6dBTPA2038D1 SLOS697–AUGUST2011ELECTRICAL CHARACTERISTICSPVDD=VDD=3.6V,T A=25°C(unless otherwise noted)PARAMETER TEST CONDITIONS MIN TYP MAX UNIT Output offset voltage|V OS|VDD=2.5V to5.5V,GAIN=VDD15mV (measured differentially)|I IH|High-level EN input current VDD=5.5V,EN=GAIN=5.5V50μA|I IL|Low-level EN input current VDD=5.5V,EN=GAIN=0V1μAVDD=5.5V,no load 1.8 2.5I(Q)Quiescent current VDD=3.6V,no load 1.5 2.3mAVDD=2.5V,no load 1.3 2.1I(SD)Shutdown current EN=0.35V,VDD=3.6V0.12μAR O,SD Output impedance in EN=0.35V2kΩshutdown modef(SW)Switching frequency VDD=2.5V to5.5V250300350kHzA V Gain GAIN=0V11.51212.5dBGAIN=VDD 5.56 6.5R EN Resistance from EN to GND300kΩA V=6dB;EN=VDD150R IN Single-ended input resistance A V=12dB;EN=VDD75kΩEN=0.35V75 OPERATING CHARACTERISTICSPVDD=VDD=3.6V,A V=6dB,T A=25°C,R L=8Ω(unless otherwise noted)PARAMETER TEST CONDITIONS MIN TYP MAX UNITV DD=5V 3.24THD+N=10%,f=1kHz,V DD=3.6V 1.62WR L=4ΩV DD=2.5V0.70V DD=5V 2.57THD+N=1%,f=1kHz,V DD=3.6V 1.32WR L=4ΩV DD=2.5V0.57P O Output powerV DD=5V 1.80THD+N=10%,f=1kHz,V DD=3.6V0.91WR L=8ΩV DD=2.5V0.42V DD=5V 1.46THD+N=1%,f=1kHz,V DD=3.6V0.74WR L=8ΩV DD=2.5V0.33V DD=3.6V,Inputs AC A-weighting20Output voltage noise,A V=6dB grounded with CI =2μF,No weighting26f=20Hz to20kHzE NμV RMSA-weighting27 Output voltage noise,A V=12dBNo weighting36VDD=5.0V,P O=1.0W,f=1kHz,R L=8Ω0.12%VDD=3.6V,P O=0.5W,f=1kHz,R L=8Ω0.05%VDD=2.5V,P O=0.2W,f=1kHz,R L=8Ω0.05%THD+N Total harmonic distortion plus noiseVDD=5.0V,P O=2.0W,f=1kHz,R L=4Ω0.32%VDD=3.6V,P O=1.0W,f=1kHz,R L=4Ω0.11%VDD=2.5V,P O=0.4W,f=1kHz,R L=4Ω0.12%A V=6dB,Inputs AC grounded with C I=2μF,81200mV pp ripple,f=217HzPSRR AC power supply rejection ratio dBA V=12dB,Inputs AC grounded with82C I=2μF,200mV pp ripple,f=217HzTPA2038D1SLOS697–OPERATING CHARACTERISTICS(continued)PVDD=VDD=3.6V,A V=6dB,T A=25°C,R L=8Ω(unless otherwise noted)PARAMETER TEST CONDITIONS MIN TYP MAX UNIT CMRR Common mode rejection ratio A V=6dB,V IC=200mV PP,f=217Hz79dBA V=12dB,V IC=200mV PP,f=217Hz77T SU Startup time from shutdown4msV O+shorted to VDDV O–shorted to VDDI SC Short circuit protection threshold V O+shorted to GND2AV O–shorted to GNDV O+shorted to V O–T AR Overcurrent recovery time VDD=2.5V to5.5V100msTerminal FunctionsTERMINALI/O DESCRIPTIONNAME WCSP BALLIN+A1I Positive audio input.GAIN A2I Gain select.Set to GND for12dB;set to VDD for6dB.V O-A3O Negative audio output.VDD B1I Power supply terminal.Connect to PVDD using a direct connection.PVDD B2I Class-D output power supply.Connect to VDD using a direct connection.GND B3I Ground.IN–C1I Negative audio input.EN C2I Enable.Set to logic high to enable device.V O+C3O Positive audio output.FUNCTIONAL BLOCK DIAGRAMTPA2038D1 SLOS697–AUGUST2011TEST SETUP FOR GRAPHS1.C I was shorted for any common-mode input voltage measurement.All other measurements were taken with C I=0.1μF(unless otherwise noted).2.C S1=0.1μF is placed very close to the device.The optional C S2=10μF is used for datasheet graphs.3.The30kHz low-pass filter is required even if the analyzer has an internal low-pass filter.An RC low-pass filter(1kΩ,4700pF)is used on each output for the data sheet graphs.P O − Output Power − W η − E f f i c i e n c y − %0.00.20.40.60.81.01.21.41.61.82.00102030405060708090100P O − Output Power − Wη − E f f i c i e n c y − %0.00.20.40.60.81.01.21.41.61.82.00102030405060708090100P O − Output Power − W P D − P o w e r D i s s i p a t i o n − W0.00.40.8 1.2 1.6 2.00.00.10.20.30.40.5P O − Output Power − WP D − P o w e r D i s s i p a t i o n − W0.00.40.8 1.2 1.6 2.0 2.4 2.8 3.2 3.6 4.00.00.10.20.30.40.50.6P O − Output Power − WI D D − S u p p l y C u r r e n t − A0.00.20.40.60.81.01.21.41.61.82.02.22.42.62.83.03.23.43.6100m200m 300m 400m 500m 600m 700m 800m 900m1P O − Output Power − WI D D − S u p p l y C u r r e n t − A0.00.20.40.60.81.01.21.41.61.82.00100m200m300m400m500m600mTPA2038D1SLOS697–AUGUST 2011TYPICAL CHARACTERISTICSPVDD =VDD =3.6V,C I =0.1μF,C S1=0.1μF,C S2=10μF,T A =25°C,R L =8Ω(unless otherwise noted)EFFICIENCY EFFICIENCY vs OUTPUT POWERvs OUTPUT POWERFigure 1.Figure 2.POWER DISSIPATION POWER DISSIPATION vs OUTPUT POWERvs OUTPUT POWERFigure 3.Figure 4.SUPPLY CURRENT SUPPLY CURRENT vs OUTPUT POWERvs OUTPUT POWERFigure 5.Figure 6.V DD − Supply Voltage − V I D D − S u p p l y C u r r e n t − m A2.53.03.54.04.55.05.51.001.251.501.752.00V EN − EN Voltage − VI D D − S u p p l y C u r r e n t − n A0.00.10.20.30.40.5050100150200R L − Load Resistance − ΩP O − O u t p u t P o w e r − W48121620242832R L − Load Resistance − ΩP O − O u t p u t P o w e r − W4812162024283201234V DD − Supply Voltage − V2.53.03.54.04.55.0TPA2038D1SLOS697–AUGUST 2011TYPICAL CHARACTERISTICS (continued)PVDD =VDD =3.6V,C I =0.1μF,C S1=0.1μF,C S2=10μF,T A =25°C,R L =8Ω(unless otherwise noted)SUPPLY CURRENT SUPPLY CURRENT vs SUPPLY VOLTAGEvs EN VOLTAGEFigure 7.Figure 8.OUTPUT POWER OUTPUT POWER vs LOAD RESISTANCEvs LOAD RESISTANCEFigure 9.Figure 10.OUTPUT POWER vs SUPPLY VOLTAGEFigure 11.P O − Output Power − WT H D +N − T o t a l H a r m o n i c D i s t o r t i o n + N o i s e − %10m100m15P O − Output Power − W10m100m15f − Frequency − HzT H D +N −T o t a l H a r m o n i c D i s t o r t i o n + N o i s e − %201001k10k20k0.0010.010.1110f − Frequency − HzT H D +N− T o t a l H a r m o n i c D i s t o r t i o n + N o i s e − %201001k10k20k0.0010.010.1110f − Frequency − HzT H D +N− T o t a l H a r m o n i c D i s t o r t i o n + N o i s e − %201001k10k20k0.0010.010.1110f − Frequency − HzT H D +N− T o t a l H a r m o n i c D i s t o r t i o n + N o i s e − %201001k10k20k0.0010.010.1110TPA2038D1SLOS697–AUGUST 2011TYPICAL CHARACTERISTICS (continued)PVDD =VDD =3.6V,C I =0.1μF,C S1=0.1μF,C S2=10μF,T A =25°C,R L =8Ω(unless otherwise noted)THD +NOISETHD +NOISEvs OUTPUT POWER (6dB GAIN)vs OUTPUT POWER (6dB GAIN)Figure 12.Figure 13.THD +NOISETHD +NOISEvs FREQUENCY (6dB GAIN)vs FREQUENCY (6dB GAIN)Figure 14.Figure 15.THD +NOISETHD +NOISEvs FREQUENCY (6dB GAIN)vs FREQUENCY (6dB GAIN)Figure 16.Figure 17.f − Frequency − HzT H D +N − T o t a l H a r m o n i c D i s t o r t i o n + N o i s e − %201001k10k20k0.0010.010.1110f − Frequency − HzT H D +N − T o t a l H a r m o n i c D i s t o r t i o n + N o i s e − %201001k10k20k0.0010.010.1110P O − Output Power − WT H D +N − T o t a l H a r m o n i c D i s t o r t i o n + N o i s e − %10m100m15P O − Output Power − W10m100m15f − Frequency − HzT H D +N− T o t a l H a r m o n i c D i s t o r t i o n + N o i s e − %201001k10k20k0.0010.010.1110f − Frequency − HzT H D +N− T o t a l H a r m o n i c D i s t o r t i o n + N o i s e − %201001k10k20k0.0010.010.1110TPA2038D1SLOS697–AUGUST 2011TYPICAL CHARACTERISTICS (continued)PVDD =VDD =3.6V,C I =0.1μF,C S1=0.1μF,C S2=10μF,T A =25°C,R L =8Ω(unless otherwise noted)THD +NOISETHD +NOISEvs FREQUENCY (6dB GAIN)vs FREQUENCY (6dB GAIN)Figure 18.Figure 19.THD +NOISETHD +NOISEvs OUTPUT POWER (12dB GAIN)vs OUTPUT POWER (12dB GAIN)Figure 20.Figure 21.THD +NOISETHD +NOISEvs FREQUENCY (12dB GAIN)vs FREQUENCY (12dB GAIN)Figure 22.Figure 23.f − Frequency − HzT H D +N − T o t a l H a r m o n i c D i s t o r t i o n + N o i s e − %201001k10k20k0.0010.010.1110f − Frequency − HzT H D +N − T o t a l H a r m o n i c D i s t o r t i o n + N o i s e − %201001k10k20k0.0010.010.1110f − Frequency − HzT H D +N − T o t a l H a r m o n i c D i s t o r t i o n + N o i s e − %201001k10k20k0.0010.010.1110f − Frequency − HzT H D +N − T o t a l H a r m o n i c D i s t o r t i o n + N o i s e − %201001k10k20k0.0010.010.1110V IC − Common Mode Input Voltage − VP S R R − P o w e r S u p p l y R e j e c t i o n R a t i o − d B0.00.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0 4.5 5.0−100−90−80−70−60−50−40−30−20−10f − Frequency − HzP S R R − P o w e r S u p p l y R e j e c t i o n R a t i o − d B201001k10k20k−100−90−80−70−60−50−40−30−20−10TPA2038D1SLOS697–AUGUST 2011TYPICAL CHARACTERISTICS (continued)PVDD =VDD =3.6V,C I =0.1μF,C S1=0.1μF,C S2=10μF,T A =25°C,R L =8Ω(unless otherwise noted)THD +NOISETHD +NOISEvs FREQUENCY (12dB GAIN)vs FREQUENCY (12dB GAIN)Figure 24.Figure 25.THD +NOISETHD +NOISEvs FREQUENCY (12dB GAIN)vs FREQUENCY (12dB GAIN)Figure 26.Figure 27.POWER SUPPLY REJECTION RATIOPOWER SUPPLY REJECTION RATIOvs COMMON MODE INPUT VOLTAGE (12dB GAIN)vs FREQUENCY (6dB GAIN)Figure 28.Figure 29.f − Frequency − HzP S R R − P o w e r S u p p l y R e j e c t i o n R a t i o − d B201001k10k20k−100−90−80−70−60−50−40−30−20−100V IC − Common Mode Input Voltage − VP S R R − P o w e r S u p p l y R e j e c t i o n R a t i o − d B0.00.51.01.52.02.53.03.54.04.55.0−100−90−80−70−60−50−40−30−20−10f − Frequency − HzP S R R − P o w e r S u p p l y R e j e c t i o n R a t i o − d B201001k10k20k−100−90−80−70−60−50−40−30−20−10f − Frequency − HzP S R R − P o w e r S u p p l y R e j e c t i o n R a t i o − d B201001k10k 20k−100−90−80−70−60−50−40−30−20−100V IC − Common Mode Input Voltage − VC M R R − C o m m o n M o d e R e j e c t i o n R a t i o − d B0.00.51.01.52.02.53.03.54.04.55.0−100−90−80−70−60−50−40−30−20−100f − Frequency − HzC M R R − C o m m o n M o d e R e j e c t i o n R a t i o − d B201001k10k20k−100−90−80−70−60−50−40−30−20−100TPA2038D1SLOS697–AUGUST 2011TYPICAL CHARACTERISTICS (continued)PVDD =VDD =3.6V,C I =0.1μF,C S1=0.1μF,C S2=10μF,T A =25°C,R L =8Ω(unless otherwise noted)POWER SUPPLY REJECTION RATIOPOWER SUPPLY REJECTION RATIO vs FREQUENCY (6dB GAIN)vs COMMON MODE INPUT VOLTAGEFigure 30.Figure 31.POWER SUPPLY REJECTION RATIOPOWER SUPPLY REJECTION RATIOvs FREQUENCY (12dB GAIN)vs FREQUENCY (12dB GAIN)Figure 32.Figure 33.COMMON MODE REJECTION RATIOCOMMON MODE REJECTION RATIOvs COMMON MODE INPUT VOLTAGE (6dB GAIN)vs FREQUENCY (6dB GAIN)Figure 34.Figure 35.V IC − Common Mode Input Voltage − VC M R R − C o m m o n M o d e R e j e c t i o n R a t i o − d B−100−90−80−70−60−50−40−30−20−100f − Frequency − HzC M R R − C o m m o n M o d e R e j e c t i o n R a t i o − dB201001k10k20k−100−90−80−70−60−50−40−30−20−100V 500 mV/divDDV 500V/div OUTm C1 - High 3.6 VC1 -Amplitude 500 mV C1 - Duty Cycle 20%G026t −Time −ms 0 2.557.51012.51517.52022.525V 500 mV/divDDV 500V/divOUTm C1 - High 3.6 VC1 -Amplitude 500 mV C1 - Duty Cycle 20%G026t −Time −ms0 2.557.51012.51517.52022.525f −Frequency −kHz V −O u t p u t V o l t ag e −d B VO V −S u p p l y V o l t a g e −d B VD D −200−175−175−150−150−125−125−100−100−75−75−50−500−25−2502.4G0274.87.29.61214.416.819.221.624f −Frequency −kHzV −O u t p u t V o l t a g e −d B VO V −S u p p l y V o l t a g e −d B VD D −200−175−175−150−150−125−125−100−100−75−75−50−500−25−2502.4G0274.87.29.61214.416.819.221.624TPA2038D1SLOS697–AUGUST 2011TYPICAL CHARACTERISTICS (continued)PVDD =VDD =3.6V,C I =0.1μF,C S1=0.1μF,C S2=10μF,T A =25°C,R L =8Ω(unless otherwise noted)COMMON MODE REJECTION RATIOCOMMON MODE REJECTION RATIOvs COMMON MODE INPUT VOLTAGE (12dB GAIN)vs FREQUENCY (12dB GAIN)Figure 36.Figure 37.GSM POWER SUPPLY REJECTIONGSM POWER SUPPLY REJECTIONvs TIME (6dB GAIN)vs TIME (12dB GAIN)Figure 38.Figure 39.GSM POWER SUPPLY REJECTIONGSM POWER SUPPLY REJECTION vs FREQUENCY (6dB GAIN)vs FREQUENCY (12dB GAIN)Figure 40.Figure 41.()C I I 1f 2πR C =()I I C 1C 2πR f =TPA2038D1SLOS697–AUGUST 2011APPLICATION INFORMATIONSHORT CIRCUIT AUTO-RECOVERYWhen a short-circuit event occurs,the TPA2038D1goes to shutdown mode and activates the integrated auto-recovery process whose aim is to return the device to normal operation once the short-circuit is removed.This process repeatedly examines (once every 100ms)whether the short-circuit condition persists,and returns the device to normal operation immediately after the short-circuit condition is removed.This feature helps protect the device from large currents and maintain a good long-term reliability.INTEGRATED IMAGE REJECT FILTER FOR DAC NOISE REJECTIONIn applications which use a DAC to drive Class-D amplifiers,out-of-band noise energy present at the DAC's image frequencies fold back into the audio-band at the output of the Class-D amplifier.An external low-pass filter is often placed between the DAC and the Class-D amplifier in order to attenuate this noise.The TPA2038D1has an integrated Image Reject Filter with a low-pass cutoff frequency of 130kHz,which significantly attenuates this noise.Depending on the system noise specification,the integrated Image Reject Filter may help eliminate external filtering,thereby saving board space and component cost.COMPONENT SELECTIONFigure 42shows the TPA2038D1typical schematic with differential inputs,while Figure 43shows the TPA2038D1with differential inputs and input capacitors.Figure 44shows the TPA2038D1with a single-ended input.Decoupling Capacitors (C S1,C S2)The TPA2038D1is a high-performance class-D audio amplifier that requires adequate power supply decoupling to ensure the efficiency is high and total harmonic distortion (THD)is low.For higher frequency transients,spikes,or digital hash on the line,a good low equivalent-series-resistance (ESR)ceramic capacitor C S1=0.1μF,placed as close as possible to the device V DD lead works best.Placing C S1close to the TPA2038D1is important for the efficiency of the class-D amplifier,because any resistance or inductance in the trace between the device and the capacitor can cause a loss in efficiency.For filtering lower-frequency noise signals,a 10μF or greater capacitor (C S2)placed near the audio power amplifier would also help,but it is not required in most applications because of the high PSRR of this device.Typically,the smaller the capacitor's case size,the lower the inductance and the closer it can be placed to the TPA2038D1.X5R and X7R dielectric capacitors are recommended for both C S1and C S2.Input Capacitors (C I )The TPA2038D1does not require input coupling capacitors if the design uses a differential source that is biased within the common-mode input voltage range.That voltage range is listed in the Recommended Operating Conditions table.If the input signal is not biased within the recommended common-mode input range,such as in needing to use the input as a high pass filter,shown in Figure 43,or if using a single-ended source,shown in Figure 44,input coupling capacitors are required.The same value capacitors should be used on both IN+and IN –for best pop performance.The 3dB high-pass cutoff frequency f C of the filter formed by the input coupling capacitor C I and the input resistance R I (typically 150k Ω)of the TPA2038D1is given by Equation 1:(1)The value of the input capacitor is important to consider as it directly affects the bass (low frequency)performance of the circuit.Speaker response may also be taken into consideration when setting the corner frequency using input capacitors.Solving for the input coupling capacitance,we get:(2)If the corner frequency is within the audio band,the capacitors should have a tolerance of ±10%or better,because any mismatch in capacitance causes an impedance mismatch at the corner frequency and below.DifferentialInputTPA2038D1SLOS697–AUGUST 2011For a flat low-frequency response,use large input coupling capacitors (0.1μF or larger).X5R and X7R dielectric capacitors are recommended.Figure 42.Typical TPA2038D1Application Schematic With DC-coupled Differential InputFigure 43.Figureq JA +1Derating Factor T A Max +T J Max *q JA P DmaxFerrite TPA2038D1SLOS697–AUGUST 2011EFFICIENCY AND THERMAL INFORMATIONThe maximum ambient operating temperature of the TPA2038D1depends on the load resistance,power supply voltage and heat-sinking ability of the PCB system.The derating factor for the YFF package is shown in the dissipation rating table.Converting this to θJA :(3)Given θJA (from the Package Dissipation ratings table),the maximum allowable junction temperature (from theAbsolute Maximum ratings table),and the maximum internal dissipation (from Power Dissipation vs Output Power figures)the maximum ambient temperature can be calculated with the following equation.Note that the units on these figures are Watts RMS.Because audio contains crest factors (ratio of peak power to RMS power)from 9–15dB,thermal limitations are not usually encountered.(4)The TPA2038D1is designed with thermal protection that turns the device off when the junction temperaturesurpasses 150°C to prevent damage to the IC.Note that the use of speakers less resistive than 4Ω(typ)is not advisable.Below 4Ω(typ)the thermal performance of the device dramatically reduces because of increased output current and reduced amplifier efficiency.The Absolute Maximum rating of 3.2Ωcovers the manufacturing tolerance of a 4Ωspeaker and speaker impedance decrease due to frequency.θJA is a gross approximation of the complex thermal transfer mechanisms between the device and its ambient environment.If the θJA calculation reveals a potential problem,a more accurate estimate should be made.WHEN TO USE AN OUTPUT FILTERDesign the TPA2038D1without an Inductor /Capacitor (LC)output filter if the traces from the amplifier to the speaker are short.Wireless handsets and PDAs are great applications for this class-D amplifier to be used without an output filter.The TPA2038D1does not require an LC output filter for short speaker connections (approximately 100mm long or less).A ferrite bead can often be used in the design if failing radiated emissions testing without an LC filter;and,the frequency-sensitive circuit is greater than 1MHz.If choosing a ferrite bead,choose one with high impedance at high frequencies,but very low impedance at low frequencies.The selection must also take into account the currents flowing through the ferrite bead.Ferrites can begin to loose effectiveness at much lower than rated current values.See the EVM User's Guide (SLOU298)for components used successfully by TI.Figure 45shows a typical ferrite-bead output filter.Figure 45.Typical Ferrite Chip Bead FilterTPA2038D1SLOS697– PRINTED CIRCUIT BOARD LAYOUTIn making the pad size for the WCSP balls,it is recommended that the layout use non-solder-mask-defined (NSMD)land.With this method,the solder mask opening is made larger than the desired land area,and the opening size is defined by the copper pad width.Figure46shows the appropriate diameters for a WCSP layout.nd Pattern Image and DimensionsSOLDER PAD SOLDER MASK COPPER STENCIL COPPER PAD STENCIL OPENING(6)(7) DEFINITIONS OPENING(5)THICKNESS THICKNESSNon-solder-mask-1oz max0.275mm x0.275mm Sq.0.23mm0.310mm0.1mm thickdefined(NSMD)(0.032mm)(rounded corners)1.Circuit traces from NSMD defined PWB lands should be75μm to100μm wide in the exposed area insidethe solder mask opening.Wider trace widths reduce device stand off and impact reliability.2.Best reliability results are achieved when the PWB laminate glass transition temperature is above theoperating the range of the intended application.3.Recommend solder paste is Type3or Type4.4.For a PWB using a Ni/Au surface finish,the gold thickness should be less0.5mm to avoid a reduction inthermal fatigue performance.5.Solder mask thickness should be less than20μm on top of the copper circuit pattern6.Best solder stencil performance is achieved using laser cut stencils with electro e of chemicallyetched stencils give inferior solder paste volume control.7.Trace routing away from WCSP device should be balanced in X and Y directions to avoid unintentionalcomponent movement due to solder wetting forces.yout SnapshotAn on-pad via is not required to route the middle ball B2(PV DD)of the TPA2038D1.Short ball B2(PV DD)to ball B1(V DD)and connect both to the supply trace as shown in Figure47.This simplifies board routing and saves manufacturing cost.TPA2038D1 SLOS697–AUGUST2011PACKAGE DIMENSIONSD EMax=1244µm Max=1190µmMin=1184µm Min=1130µmPACKAGE OPTION ADDENDUM6-Oct-2011Addendum-Page 1PACKAGING INFORMATIONOrderable Device Status(1)Package Type PackageDrawingPins Package QtyEco Plan(2)Lead/Ball Finish MSL Peak Temp (3)Samples (Requires Login)TPA2038D1YFFR ACTIVE DSBGA YFF 93000Green (RoHS & no Sb/Br)SNAGCU Level-1-260C-UNLIM TPA2038D1YFFTACTIVEDSBGAYFF9250Green (RoHS & no Sb/Br)SNAGCULevel-1-260C-UNLIM(1)The marketing status values are defined as follows:ACTIVE: Product device recommended for new designs.LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.PREVIEW: Device has been announced but is not in production. Samples may or may not be available.OBSOLETE: TI has discontinued the production of the device.(2)Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check /productcontent for the latest availability information and additional product content details.TBD: The Pb-Free/Green conversion plan has not been defined.Pb-Free (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.Pb-Free (RoHS Exempt): This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)(3)MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.芯天下--/。

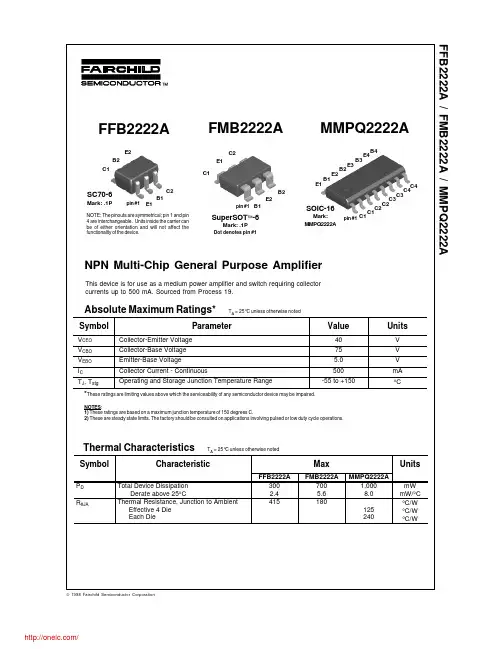

FMB2222A;中文规格书,Datasheet资料

Thermal Characteristics

Symbol

PD RθJA

TA = 25°C unless otherwise noted

Characteristic

Total Device Dissipation Derate above 25°C Thermal Resistance, Junction to Ambient Effective 4 Die Each Die FFB2222A 300 2.4 415

*Pulse Test: Pulse Width ≤ 300 µs, Duty Cycle ≤ 2.0%

Spice Model

NPN (Is=14.34f Xti=3 Eg=1.11 Vaf=74.03 Bf=255.9 Ne=1.307 Ise=14.34f Ikf=.2847 Xtb=1.5 Br=6.092 Nc=2 Isc=0 Ikr=0 Rc=1 Cjc=7.306p Mjc=.3416 Vjc=.75 Fc=.5 Cje=22.01p Mje=.377 Vje=.75 Tr=46.91n Tf=411.1p Itf=.6 Vtf=1.7 Xtf=3 Rb=10)

300

VCE(sat) VBE(sat)

Collector-Emitter Saturation Voltage* Base-Emitter Saturation Voltage*

0.3 1.0 1.2 2.0

V V V V

SMALL SIGNAL CHARACTERISTICS

fT Cobo Cibo NF Current Gain - Bandwidth Product Output Capacitance Input Capacitance Noise Figure IC = 20 mA, VCE = 20 V, f = 100 MHz VCB = 10 V, IE = 0, f = 100 kHz VEB = 0.5 V, IC = 0, f = 100 kHz IC = 100 µA, VCE = 10 V, RS = 1.0 kΩ, f = 1.0 kHz 300 4.0 20 2.0 MHz pF pF dB

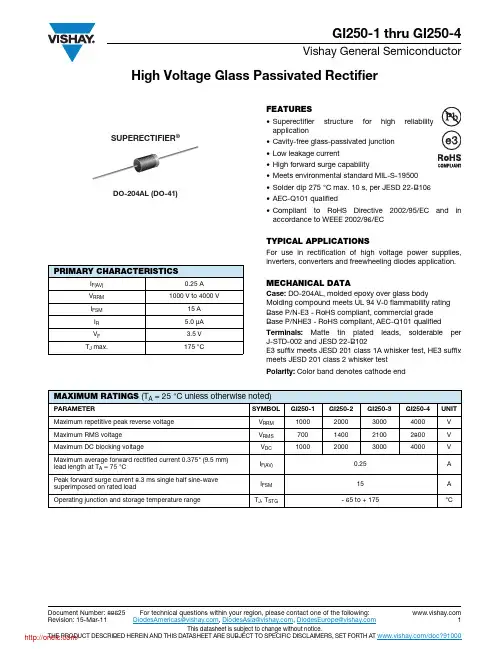

GI250-1-E373;GI250-2-E373;GI250-4-E373;GI250-1-E354;GI250-2-E354;中文规格书,Datasheet资料

Document Number: 88625For technical questions within your region, please contact one of the following: High Voltage Glass Passivated RectifierGI250-1 thru GI250-4Vishay General SemiconductorFEATURES•Superectifier structure for high reliability application•Cavity-free glass-passivated junction •Low leakage current•High forward surge capability•Meets environmental standard MIL-S-19500•Solder dip 275 °C max. 10 s, per JESD 22-B106•AEC-Q101 qualified•Compliant to RoH S Directive 2002/95/EC and in accordance to WEEE 2002/96/ECTYPICAL APPLICATIONSFor use in rectification of high voltage power supplies,inverters, converters and freewheeling diodes application.MECHANICAL DATACase: DO-204AL, molded epoxy over glass bodyMolding compound meets UL 94 V-0 flammability rating Base P/N-E3 - RoHS compliant, commercial grade Base P/NHE3 - RoHS compliant, AEC-Q101 qualified Terminals: Matte tin plated leads, solderable per J-STD-002 and JESD 22-B102E3 suffix meets JESD 201 class 1A whisker test, HE3 suffix meets JESD 201 class 2 whisker test Polarity: Color band denotes cathode endPRIMARY CHARACTERISTICSI F(AV)0.25 A V RRM 1000 V to 4000 VI FSM 15 A I R 5.0 μA V F 3.5 V T J max.175 °CDO-204AL (DO-41)SUPERECTIFIER ®MAXIMUM RATINGS (T A = 25°C unless otherwise noted)PARAMETERSYMBOL GI250-1GI250-2GI250-3GI250-4UNIT Maximum repetitive peak reverse voltage V RRM 1000200030004000V Maximum RMS voltage V RMS 700140021002800V Maximum DC blocking voltageV DC 1000200030004000V Maximum average forward rectified current 0.375" (9.5 mm)lead length at T A = 75 °CI F(AV)0.25A Peak forward surge current 8.3 ms single half sine-wave superimposed on rated loadI FSM 15A Operating junction and storage temperature rangeT J , T STG- 65 to + 175°C For technical questions within your region, please contact one of the following:Document Number: 88625GI250-1 thru GI250-4Vishay General SemiconductorNote(1)Thermal resistance from junction to ambient at 0.375" (9.5 mm) lead length, P.C.B. mountedNote(1)AEC-Q101 qualifiedRATINGS AND CHARACTERISTICS CURVES(T A = 25 °C unless otherwise noted)Fig. 1 - Forward Current Derating Curve Fig. 2 - Maximum Non-repetitive Peak Forward Surge CurrentELECTRICAL CHARACTERISTICS (T A = 25°C unless otherwise noted)PARAMETERTEST CONDITIONS SYMBOLGI250-1GI250-2GI250-3GI250-4UNIT Maximum instantaneous forward voltage 0.25 AV F 3.5V Maximum DC reverse current at rated DC blocking voltage T A = 25 °C I R 5.0μA T A = 100 °C50Typical reverse recovery time I F = 0.5 A, I R = 1.0 A,I rr = 0.25 A t rr 2.0μs Typical junction capacitance4.0 V, 1 MHzC J3.0pFTHERMAL CHARACTERISTICS (T A = 25°C unless otherwise noted)PARAMETERSYMBOL GI250-1GI250-2GI250-3GI250-4UNIT Typical thermal resistanceR JA (1)130°C/WORDERING INFORMATION (Example)PREFERRED P/N UNIT WEIGHT (g)PREFERRED PACKAGE CODEBASE QUANTITYDELIVERY MODEGI250-4E3/540.33954550013" diameter paper tape and reelGI250-4E3/730.339733000Ammo pack packaging GI250-4HE3/54 (1)0.33954550013" diameter paper tape and reelGI250-4HE3/73 (1)0.339733000Ammo pack packagingDocument Number: 88625For technical questions within your region, please contact one of the following: GI250-1 thru GI250-4Vishay General SemiconductorFig. 3 - Typical Instantaneous Forward Characteristics Fig. 4 - Typical Reverse CharacteristicsFig. 5 - Typical Junction CapacitancePACKAGE OUTLINE DIMENSIONS in inches (millimeters)Legal Disclaimer Notice VishayDisclaimerALL PRODU CT, PRODU CT SPECIFICATIONS AND DATA ARE SU BJECT TO CHANGE WITHOU T NOTICE TO IMPROVE RELIABILITY, FUNCTION OR DESIGN OR OTHERWISE.Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively,“Vishay”), disclaim any and all liability for any errors, inaccuracies or incompleteness contained in any datasheet or in any other disclosure relating to any product.Vishay makes no warranty, representation or guarantee regarding the suitability of the products for any particular purpose or the continuing production of any product. To the maximum extent permitted by applicable law, Vishay disclaims (i) any and all liability arising out of the application or use of any product, (ii) any and all liability, including without limitation special, consequential or incidental damages, and (iii) any and all implied warranties, including warranties of fitness for particular purpose, non-infringement and merchantability.Statements regarding the suitability of products for certain types of applications are based on Vishay’s knowledge of typical requirements that are often placed on Vishay products in generic applications. Such statements are not binding statements about the suitability of products for a particular application. It is the customer’s responsibility to validate that a particular product with the properties described in the product specification is suitable for use in a particular application. Parameters provided in datasheets and/or specifications may vary in different applications and performance may vary over time. All operating parameters, including typical parameters, must be validated for each customer application by the customer’s technical experts. Product specifications do not expand or otherwise modify Vishay’s terms and conditions of purchase, including but not limited to the warranty expressed therein.Except as expressly indicated in writing, Vishay products are not designed for use in medical, life-saving, or life-sustaining applications or for any other application in which the failure of the Vishay product could result in personal injury or death. Customers using or selling Vishay products not expressly indicated for use in such applications do so at their own risk and agree to fully indemnify and hold Vishay and its distributors harmless from and against any and all claims, liabilities, expenses and damages arising or resulting in connection with such use or sale, including attorneys fees, even if such claim alleges that Vishay or its distributor was negligent regarding the design or manufacture of the part. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay. Product names and markings noted herein may be trademarks of their respective owners.Material Category PolicyVishay Intertechnology, Inc. hereb y certifies that all its products that are identified as RoHS-Compliant fulfill the definitions and restrictions defined under Directive 2011/65/EU of The European Parliament and of the Council of June 8, 2011 on the restriction of the use of certain hazardous substances in electrical and electronic equipment (EEE) - recast, unless otherwise specified as non-compliant.Please note that some Vishay documentation may still make reference to RoHS Directive 2002/95/EC. We confirm that all the products identified as being compliant to Directive 2002/95/EC conform to Directive 2011/65/EU.Revision: 12-Mar-121Document Number: 91000分销商库存信息:VISHAY-GENERAL-SEMICONDUCTORGI250-1-E3/73GI250-2-E3/73GI250-4-E3/73 GI250-1-E3/54GI250-2-E3/54GI250-3-E3/54 GI250-4-E3/54GI250-2HE3/73GI250-4HE3/73 GI250-2HE3/54GI250-4HE3/54。

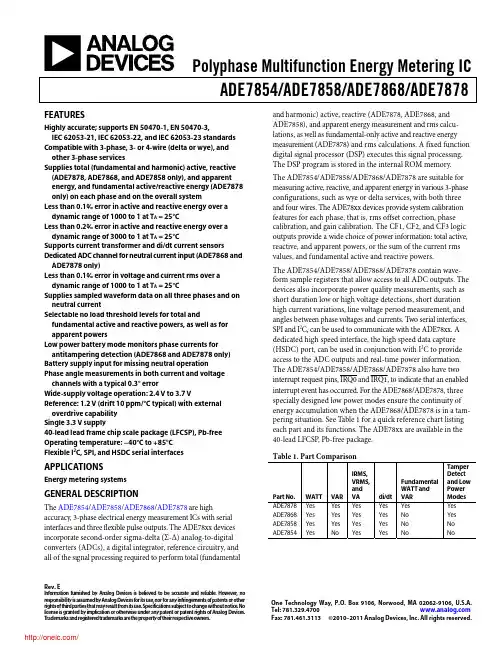

ADE7878ACPZ;ADE7854ACPZ;ADE7854ACPZ-RL;ADE7858ACPZ-RL;ADE7868ACPZ-RL;中文规格书,Datasheet资料

Polyphase Multifunction Energy Metering ICADE7854/ADE7858/ADE7868/ADE7878 Rev. EInformation furnished by Analog Devices is believed to be accurate and reliable. However, noresponsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. T rademarks and registered trademarks are the property of their respective owners. One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 Fax: 781.461.3113 ©2010–2011 Analog Devices, Inc. All rights reserved.FEATURESHighly accurate; supports EN 50470-1, EN 50470-3,IEC 62053-21, IEC 62053-22, and IEC 62053-23 standards Compatible with 3-phase, 3- or 4-wire (delta or wye), and other 3-phase servicesSupplies total (fundamental and harmonic) active, reactive (ADE7878, ADE7868, and ADE7858 only), and apparent energy, and fundamental active/reactive energy (ADE7878 only) on each phase and on the overall systemLess than 0.1% error in active and reactive energy over a dynamic range of 1000 to 1 at T A = 25°CLess than 0.2% error in active and reactive energy over a dynamic range of 3000 to 1 at T A = 25°CSupports current transformer and di/dt current sensors Dedicated ADC channel for neutral current input (ADE7868 and ADE7878 only)Less than 0.1% error in voltage and current rms over a dynamic range of 1000 to 1 at T A = 25°CSupplies sampled waveform data on all three phases and on neutral currentSelectable no load threshold levels for total and fundamental active and reactive powers, as well as for apparent powersLow power battery mode monitors phase currents for antitampering detection (ADE7868 and ADE7878 only) Battery supply input for missing neutral operationPhase angle measurements in both current and voltage channels with a typical 0.3° errorWide-supply voltage operation: 2.4 V to 3.7 VReference: 1.2 V (drift 10 ppm/°C typical) with external overdrive capabilitySingle 3.3 V supply40-lead lead frame chip scale package (LFCSP), Pb-free Operating temperature: −40°C to +85°CFlexible I2C, SPI, and HSDC serial interfaces APPLICATIONSEnergy metering systemsGENERAL DESCRIPTIONThe ADE7854/ADE7858/ADE7868/ADE7878 are high accuracy, 3-phase electrical energy measurement ICs with serial interfaces and three flexible pulse outputs. The ADE78xx devices incorporate second-order sigma-delta (Σ-Δ) analog-to-digital converters (ADCs), a digital integrator, reference circuitry, and all of the signal processing required to perform total (fundamental and harmonic) active, reactive (ADE7878, ADE7868, and ADE7858), and apparent energy measurement and rms calcu-lations, as well as fundamental-only active and reactive energy measurement (ADE7878) and rms calculations. A fixed function digital signal processor (DSP) executes this signal processing. The DSP program is stored in the internal ROM memory. The ADE7854/ADE7858/ADE7868/ADE7878 are suitable for measuring active, reactive, and apparent energy in various 3-phase configurations, such as wye or delta services, with both three and four wires. The ADE78xx devices provide system calibration features for each phase, that is, rms offset correction, phase calibration, and gain calibration. The CF1, CF2, and CF3 logic outputs provide a wide choice of power information: total active, reactive, and apparent powers, or the sum of the current rms values, and fundamental active and reactive powers.The ADE7854/ADE7858/ADE7868/ADE7878 contain wave-form sample registers that allow access to all ADC outputs. The devices also incorporate power quality measurements, such as short duration low or high voltage detections, short duration high current variations, line voltage period measurement, and angles between phase voltages and currents. Two serial interfaces, SPI and I2C, can be used to communicate with the ADE78xx. A dedicated high speed interface, the high speed data capture (HSDC) port, can be used in conjunction with I2C to provide access to the ADC outputs and real-time power information. The ADE7854/ADE7858/ADE7868/ADE7878 also have two interrupt request pins, IRQ0 and IRQ1, to indicate that an enabled interrupt event has occurred. For the ADE7868/ADE7878, three specially designed low power modes ensure the continuity of energy accumulation when the ADE7868/ADE7878 is in a tam-pering situation. See for a quick reference chart listing each part and its functions. The ADE78xx are available in the 40-lead LFCSP, Pb-free package.Table 1Table 1. Part ComparisonPart No. WATT VARIRMS,VRMS,andVA di/dtFundamentalWATT andVARTamperDetectand LowPowerModes ADE7878 Yes Yes Yes Yes Yes Yes ADE7868 Yes Yes Yes Yes No Yes ADE7858 Yes Yes Yes Yes No No ADE7854 Yes No Yes Yes No NoADE7854/ADE7858/ADE7868/ADE7878Rev. E | Page 2 of 96TABLE OF CONTENTSFeatures..............................................................................................1 Applications.......................................................................................1 General Description.........................................................................1 Revision History...............................................................................3 Functional Block Diagrams.............................................................4 Specifications.....................................................................................8 Timing Characteristics..............................................................11 Absolute Maximum Ratings..........................................................14 Thermal Resistance....................................................................14 ESD Caution................................................................................14 Pin Configuration and Function Descriptions...........................15 Typical Performance Characteristics...........................................17 Test Circuit......................................................................................19 Terminology....................................................................................20 Power Management........................................................................21 PSM0—Normal Power Mode (All Parts)................................21 PSM1—Reduced Power Mode (ADE7868, ADE7878 Only)21 PSM2—Low Power Mode (ADE7868, ADE7878 Only).......21 PSM3—Sleep Mode (All Parts)................................................22 Power-Up Procedure..................................................................24 Hardware Reset...........................................................................25 Software Reset Functionality....................................................25 Theory of Operation......................................................................26 Analog Inputs..............................................................................26 Analog-to-Digital Conversion..................................................26 Current Channel ADC...............................................................27 di/dt Current Sensor and Digital Integrator..............................29 Voltage Channel ADC...............................................................30 Changing Phase Voltage Datapath...........................................31 Power Quality Measurements...................................................32 Phase Compensation.................................................................37 Reference Circuit........................................................................39 Digital Signal Processor.............................................................39 Root Mean Square Measurement.............................................40 Active Power Calculation..........................................................44 Reactive Power Calculation—ADE7858, ADE7868, ADE7878 Only..............................................................................................49 Apparent Power Calculation.....................................................54 Waveform Sampling Mode.......................................................57 Energy-to-Frequency Conversion............................................57 No Load Condition....................................................................61 Checksum Register.....................................................................63 Interrupts.....................................................................................64 Serial Interfaces..........................................................................65 ADE7878 Evaluation Board......................................................72 Die Version..................................................................................72 Silicon Anomaly.............................................................................73 ADE7854/ADE7858/ADE7868/ADE7878 FunctionalityIssues............................................................................................73 Functionality Issues....................................................................73 Section 1. ADE7854/ADE7858/ADE7868/ADE7878Functionality Issues....................................................................74 Registers List...................................................................................75 Outline Dimensions.......................................................................93 Ordering Guide.. (93)ADE7854/ADE7858/ADE7868/ADE7878Rev. E | Page 3 of 96REVISION HISTORY4/11—Rev. D to Rev. EChanges to Input Clock FrequencyParameter, Table 2..............10 Changes to Current RMS Offset Compensation Section..........42 Changes to Voltage RMS Offset Compensation Section...........44 Changes to Note 2, Table 30...........................................................77 Changes to Address 0xE707, Table 33..........................................80 Changes to Table 45........................................................................87 Changes to Table 46........................................................................88 Changes to Bit Location 7:3, Default Value, Table 54.. (92)2/11—Rev. C to Rev. DChanges to Figure 1...........................................................................4 Changes to Figure 2...........................................................................5 Changes to Figure 3...........................................................................6 Changes to Figure 4...........................................................................7 Changes to Table 2............................................................................8 Changed SCLK Edge to HSCLK Edge, Table 5...........................13 Change to Current Channel HPF Section...................................28 Change to di/dt Current Sensor and Digital IntegratorSection..............................................................................................30 Changes to Digital Signal Processor Section...............................39 Changes to Figure 59......................................................................44 Changes to Figure 62......................................................................47 Changes to Figure 65......................................................................49 Changes to Figure 66......................................................................52 Changes to Line Cycle Reactive Energy Accumulation Mode Section and to Figure 67.................................................................53 No Load Detection Based On Total Active, Reactive Powers Section..............................................................................................61 Change to Equation 50...................................................................63 Changes to the HSDC Interface Section......................................70 Changes to Figure 87 and Figure 88.............................................71 Changes to Figure 89......................................................................72 Changes to Table 30 (77)11/10—Rev. B to Rev. CChange to Signal-to-Noise-and-Distortion Ratio, SINADParameter, Table 1.............................................................................9 Changes to Figure 18......................................................................18 Changes to Figure 22......................................................................19 Changes to Silicon Anomaly Section............................................72 Added Table 28 to Silicon Anomaly Section, RenumberedTables Sequentially..........................................................................73 8/10—Rev. A to Rev. BChanges to Figure 1..........................................................................4 Changes to Figure 2..........................................................................5 Changes to Figure 3..........................................................................6 Changes to Figure 4..........................................................................7 Change to Table 8............................................................................16 Changes to Power-Up Procedure Section....................................23 Changes to Equation 6 and Equation 7........................................33 Changes to Equation 17.................................................................43 Changes to Active Power Offset Calibration Section.................45 Changes to Figure 63......................................................................46 Changes to Reactive Power Offset Calibration Section.............49 Changes to Figure 82......................................................................65 Added Silicon Anomaly Section, Renumbered TablesSequentially (71)3/10—Rev. 0 to Rev. AAdded ADE7854, ADE7858, and ADE7878..................Universal Reorganized Layout...........................................................Universal Added Table 1, Renumbered Sequentially.....................................1 Added Figure 1, Renumbered Sequentially...................................3 Added Figure 2..................................................................................4 Added Figure 3..................................................................................5 Changes to Specifications Section..................................................7 Changes to Figure 9........................................................................14 Changes to Table 8..........................................................................14 Changes to Typical Performance Characteristics Section.........16 Changes to Figure 22......................................................................18 Changes to the Power Management Section...............................20 Changes to the Theory of Operation Section..............................25 Changes to Figure 31 and Figure 32.............................................27 Change to Equation 28...................................................................47 Changes to Figure 83......................................................................66 Changes to Figure 86......................................................................68 Changes to the Registers List Section...........................................72 Changes to Ordering Guide.. (91)2/10—Revision 0: Initial VersionADE7854/ADE7858/ADE7868/ADE7878Rev. E | Page 4 of 96FUNCTIONAL BLOCK DIAGRAMSR E S E TR E F C L K I C L K O U I A I A V A I B I B V B I C I C V C V S C L K/S C LS D AH S DA08510-204Figure 1. ADE7854 Functional Block DiagramADE7854/ADE7858/ADE7868/ADE7878Rev. E | Page 5 of 96R E S E TR E F C L K I C L K O U I A I A V A I B I B V B I C I C V C V S C L K/S C LS D AH S DA08510-203Figure 2. ADE7858 Functional Block DiagramADE7854/ADE7858/ADE7868/ADE7878Rev. E | Page 6 of 96R E S E TR E F C L K I C L K O U I A I A V A I B I B V B I C I C V C V S C L K/S C LS D AH S DAI N I N 08510-202Figure 3. ADE7868 Functional Block DiagramADE7854/ADE7858/ADE7868/ADE7878Rev. E | Page 7 of 96R E S E TR E F C L K I C L K O U I A I A V A I B I B V B I C I C V C V S C L K/S C LS D AH S DAI N I N 08510-201Figure 4. ADE7878 Functional Block DiagramADE7854/ADE7858/ADE7868/ADE7878Rev. E | Page 8 of 96SPECIFICATIONSVDD = 3.3 V ± 10%, AGND = DGND = 0 V , on-chip reference, CLKIN = 16.384 MHz, T MIN to T MAX = −40°C to +85°C. Table 2.Parameter 1, 2 Min Typ Max Unit Test Conditions/Comments ACCURACYActive Energy MeasurementActive Energy Measurement Error (per Phase)Total Active Power0.1%Over a dynamic range of 1000 to 1, PGA = 1, 2, 4; integrator off0.2 % Over a dynamic range of 3000 to 1, PGA = 1, 2, 4;integrator off0.1 % Over a dynamic range of 500 to 1, PGA = 8, 16;integrator onFundamental Active Power (ADE7878 Only) 0.1% Over a dynamic range of 1000 to 1, PGA = 1, 2, 4; integrator off 0.2 % Over a dynamic range of 3000 to 1, PGA = 1, 2, 4;integrator off0.1 % Over a dynamic range of 500 to 1, PGA = 8, 16;integrator onPhase Error Between Channels Line frequency = 45 Hz to 65 Hz, HPF on Power Factor (PF) = 0.8 Capacitive ±0.05 Degrees Phase lead 37° PF = 0.5 Inductive ±0.05 Degrees Phase lag 60° AC Power Supply Rejection VDD = 3.3 V + 120 mV rms/120 Hz, IPx = VPx =±100 mV rmsOutput Frequency Variation 0.01 % DC Power Supply Rejection VDD = 3.3 V ± 330 mV dc Output Frequency Variation 0.01 %Total Active Energy MeasurementBandwidth2 kHz REACTIVE ENERGY MEASUREMENT(ADE7858, ADE7868, AND ADE7878)Reactive Energy Measurement Error(per Phase)Total Active Power 0.1 % Over a dynamic range of 1000 to 1, PGA = 1, 2, 4;integrator off0.2 % Over a dynamic range of 3000 to 1, PGA = 1, 2, 4;integrator off0.1 % Over a dynamic range of 500 to 1, PGA = 8, 16;integrator onFundamental Active Power (ADE7878 Only) 0.1% Over a dynamic range of 1000 to 1, PGA = 1, 2, 4; integrator off 0.2 % Over a dynamic range of 3000 to 1, PGA = 1, 2, 4;integrator off0.1 % Over a dynamic range of 500 to 1, PGA = 8, 16;integrator onPhase Error Between Channels Line frequency = 45 Hz to 65 Hz, HPF on PF = 0.8 Capacitive ±0.05 Degrees Phase lead 37° PF = 0.5 Inductive ±0.05 Degrees Phase lag 60° AC Power Supply Rejection VDD = 3.3 V + 120 mV rms/120 Hz, IPx = VPx =±100 mV rmsOutput Frequency Variation 0.01 %ADE7854/ADE7858/ADE7868/ADE7878Rev. E | Page 9 of 96Parameter 1, 2Min Typ Max Unit Test Conditions/Comments DC Power Supply Rejection VDD = 3.3 V ± 330 mV dc Output Frequency Variation0.01% Total Reactive Energy Measurement Bandwidth2kHzRMS MEASUREMENTSI rms and V rms Measurement Bandwidth2 kHz I rms and V rms Measurement Error (PSM0 Mode)0.1 % Over a dynamic range of 1000 to 1, PGA = 1 MEAN ABSOLUTE VALUE (MAV)MEASUREMENT (ADE7868 AND ADE7878)I mav Measurement Bandwidth (PSM1 Mode)260 Hz I mav Measurement Error (PSM1 Mode) 0.5 % Over a dynamic range of 100 to 1, PGA = 1, 2, 4, 8 ANALOG INPUTSMaximum Signal Levels±500mV peakDifferential inputs between the following pins: IAP and IAN, IBP and IBN, ICP and ICN; single-ended inputs between the following pins: VAP and VN, VBP and VN, VCP and VN Input Impedance (DC)IAP , IAN, IBP , IBN, ICP , ICN, VAP , VBP , and VCP Pins 400 kΩVN Pin130 kΩADC Offset Error±2 mV PGA = 1, uncalibrated error, see the Terminology sectionGain Error±4 % External 1.2 V referenceWAVEFORM SAMPLINGSampling CLKIN/2048, 16.384 MHz/2048 = 8 kSPS Current and Voltage Channels See the Waveform Sampling Mode section Signal-to-Noise Ratio, SNR70 dB PGA = 1 Signal-to-Noise-and-Distortion Ratio, SINAD60 dB PGA = 1Bandwidth (−3 dB)2 kHz TIME INTERVAL BETWEEN PHASESMeasurement Error0.3 Degrees Line frequency = 45 Hz to 65 Hz, HPF on CF1, CF2, CF3 PULSE OUTPUTSMaximum Output Frequency 8 kHz WTHR = VARTHR = VATHR = PMAX = 33,516,139 Duty Cycle50%If CF1, CF2, or CF3 frequency > 6.25 Hz and CFDEN is even and > 1(1 + 1/CFDEN) × 50% If CF1, CF2, or CF3 frequency > 6.25 Hz andCFDEN is odd and > 1Active Low Pulse Width 80 ms If CF1, CF2, or CF3 frequency < 6.25 Hz Jitter 0.04 % For CF1, CF2, or CF3 frequency = 1 Hz andnominal phase currents are larger than 10% of full scaleREFERENCE INPUT REF IN/OUT Input Voltage Range 1.1 1.3 V Minimum = 1.2 V − 8%; maximum = 1.2 V + 8% Input Capacitance 10 pF ON-CHIP REFERENCE Nominal 1.207 V at the REF IN/OUT pin at T A = 25°C PSM0 and PSM1 Modes Reference Error ±2 mV Output Impedance 1.2 kΩ Temperature Coefficient 10 50 ppm/°C Maximum value across full temperature rangeof −40°C to +85°CADE7854/ADE7858/ADE7868/ADE78781 See the Typical Performance Characteristics section.2 See the Terminology section for a definition of the parameters.Rev. E | Page 10 of 96分销商库存信息:ANALOG-DEVICESADE7878ACPZ ADE7854ACPZ ADE7854ACPZ-RL ADE7858ACPZ-RL ADE7868ACPZ-RL ADE7878ACPZ-RL ADE7858ACPZ ADE7868ACPZ EVAL-ADE7878EBZ。

414;中文规格书,Datasheet资料

/

414

DC axial compact fan

Product drawing

Web data sheet XI · Page 3 of 4 ebm-papst St. Georgen GmbH & Co. KG · Hermann-Papst-Straße 1 · D-78112 St. Georgen · Phone +49 7724 81-0 · Fax +49 7724 81-1309 · info2@ ·

Mass Dimensions Material of impeller Housing material Direction of air flow Direction of rotation Bearing Lifetime L10 at 20 °C Lifetime L10 at 60 °C Connection line Motor protection Approval

/

分销商库存信息:

EBM-PAPST 414

/

414

DC axial compact fan

Technical features

General description Particular design features: Compact fan with low power consumption. Some models suitable for use at high ambient temperatures. General features: Material: fibreglass-reinforced plastic. Impeller PA, housing PBT. Electronic commutation completely integrated. Protected against reverse polarity and locking. Connection via single strands AWG 28, TR 64, bared and tin-plated. Air exhaust over bars. Direction of rotation counter-clockwise seen on rotor. Masse: 17 g. 0.027 kg 40 x 40 x 20 mm Fiberglass-reinforced PA plastic Fiberglass-reinforced PBT plastic Air exhaust over bars Left, looking at rotor Sintec sleeve bearing 50000 h 20000 h Single strands AWG 28, TR 64, bared and tin-plated. Protected against reverse polarity and locking. VDE, CSA, UL

VLF4012AT-4R7M1R1;VLF4012AT-100MR79;VLF4012AT-3R3M1R3;VLF4012AT-2R2M1R5;中文规格书,Datasheet资料

Inductance tolerance(%) ±30 ±20 ±20 ±20 ±20 ±20 ±20

Test frequency (kHz) 100 100 100 100 100 100 100

DC resistance( ) max. 0.054 0.1 0.15 0.2 0.31 0.46 1.20 typ. 0.047 0.091 0.13 0.1R7

2.8±0.2

1.4max. Dimensions in mm

RECOMMENDED PC BOARD PATTERN

1.2 2.1 3.4 Dimensions in mm

Inductance [at 1/2 Idc1]3 (µH) 1 2.2 3.3 4.7 6.8 10 22

• All specifications are subject to change without notice.

/

001-04 / 20120310 / e531_vlf

(3/17)

Inductors for Power Circuits Wound/STD • Magnetic Shielded

Part No. VLF3014AT-1R0N1R7 VLF3014AT-2R2M1R2 VLF3014AT-3R3M1R0 VLF3014AT-4R7MR90 VLF3014AT-6R8MR72 VLF3014AT-100MR59 VLF3014AT-220MR37

1

SHAPES AND DIMENSIONS

VLF-MT Series VLF302510MT

With the VLF302510MT Series, a DC to DC converter with topclass voltage conversion efficiency for similar size products was achieved by optimizing the magnetic material and configuration. These products are optimal for use as choke coils in switching power supplies such as those in mobile devices requiring spacesaving design. FEATURES • Miniature size Mount area: 3.02.5mm Low profile: 1.0mm max. height • Generic use for portable DC to DC converter line. • High magnetic shield construction should actualize high resolution for EMC protection. • The products contain no lead and also support lead-free soldering. • The products is halogen-free. • It is a product conforming to RoHS directive. APPLICATIONS Smartphones, cellular phones, DSCs, DVCs, HDDs, LCD displays, compact power supply modules, etc. SHAPES AND DIMENSIONS

8.07.00 JTAG ISOLATOR;中文规格书,Datasheet资料

User Manual for J-Link JTAG Isolator 1/4© 2008 SEGGER Microcontroller GmbH & Co. KGUM08010-R3User Manual J-Link JTAG IsolatorIntroductionThe J-Link JTAG Isolator can be connected between J-Link ARM and any ARM-board that uses the standard 20-pin JTAG-ARM connector to provide electrical isolation. This is essential when the development tools are not connected to the same ground as the application. It is also useful to protect the development tools from electrical spikes that often occur in some applications, such as motor control applications.A 20-pin flat cable (supplied with J-Link) is needed to connect the target.Power supplyBoth sides, target and emulator, are totally isolated and separately powered. The target side draws power from pins 1 or 2, the emulator side draws power from pin 19.Figure 1. J-Link JTAG IsolatorPower LEDReset LEDPower LEDTarget sideEmulator Side (J-Link)Features• 1kV DC isolation• 3.3V and 5V target operation supported • Powered from emulator and target•JTAG standard 20-pin connection supporting TRST, TDI, TMS, TCK, RTCK, TDO and RESET signals• Power consumption on target side: < 50mA • JTAG frequency: Up to 4MHz• 3 LEDs to indicate emulator power, target power and target RESETUser Manual for J-Link JTAG Isolator 2/4© 2008 SEGGER Microcontroller GmbH & Co. KGConnectors and indicatorsThe Isolator uses high speed optocouplers that allow a very low propagation time between input and output. It comes with the following connectors and indicators:• 20-pin female EMULATOR connector which can be plugged directly into J-Link• 20-pin male TARGET connector for connection of the target cable • Green LED indicating power on the emulator side • Green LED indicating power on the target side • Red LED indicating RESETBlock diagramThe functional block diagram (Figure 2) illustrates the functional connections between the emulator and target.User Manual for J-Link JTAG Isolator 3/4© 2008 SEGGER Microcontroller GmbH & Co. KGConnecting the Isolator to Target and EmulatorTarget side is connected to the target via a 20-pin flat cable.Using the Isolator with J-LinkIn order to use the Isolator, follow these steps:• Plug the Isolator directly into J-Link. • Power J-Link.• Make sure the green LED on the emulator side is lit. If it is not, follow theinstruction in the next section.• Connect the target via 20-pin flat cable to the target side of the Isolator. • If the target is powered, the green LED on the target side should be lit.The red LED on the target side is lit when a Target RESET is active (low).Preparing J-Link to supply powerJ-Link needs to supply 5V power to the emulator side of the adapter on pin 19. In order to do this, you may have to configure J-Link once as follows: • Make sure that SEGGER J-Link software is installed on your machine.It can be downloaded from /download_jlink.html • Start J-Link Commander, which can be found under “Start -> Programs -> SEGGER -> J-Link ARM ”• Enter the following command: power on perm• Plug in the adapter: The LED on the emulator side should now be lit.Using the Isolator with an other ARM emulatorThe Isolator has been designed for J-Link, but can also be used with other ARM emulators with the same pin-out. In this case, you should make sure that 5V are supplied to pin 19 of the emulator connector and that your emulator is not damaged when applying 5V to this pin. Do this at your own risk!User Manual for J-Link JTAG Isolator 4/4© 2008 SEGGER Microcontroller GmbH & Co. KGDisclaimerSpecifications written in this document are believed to be accurate, but are not guaranteed to be entirely free of error. The information in this manual is subject to change for functional or performance improvements without notice. Please make sure your manual is the latest edition. While the information herein is assumed to be accurate, SEGGER Microcontroller GmbH & Co. KG (the manufacturer) assumes no responsibility for any errors or omissions. The manufacturer makes and you receive no warranties or conditions, express, implied, statutory or in any communication with you. The manufacturer specifically disclaims any implied warranty of merchantability or fitness for a particular purpose.Copyright noticeYou may not extract portions of this manual or modify the PDF file in any way without the prior written permission of the manufacturer.2008 SEGGER Microcontroller GmbH & Co. KG, Hilden / GermanyTrademarksNames mentioned in this manual may be trademarks of their respective companies.Brand and product names are trademarks or registered trademarks of their respective holders.Contact addressSEGGER Microcontroller GmbH & Co. KG In den Weiden 11 D-40721 Hilden GermanyTel.+49 2103-2878-0 Fax.+49 2103-2878-28Email: support@Internet: RevisionsRevision Date ByExplanation0 080104 OO Initial version1 080109 OO Added / updated picture for better understanding.2 080118 OO Updated Figure 2 “Functinal block diagram”3 080827 OO Minor changes分销商库存信息: SEGGER8.07.00 JTAG ISOLATOR。

MLD2N06CLT4;MLD2N06CLT4G;中文规格书,Datasheet资料