基于FPGA的分数间隔预测判决反馈均衡器的设计与实现

基于FPGA自适应均衡器的研究与实现的开题报告

基于FPGA自适应均衡器的研究与实现的开题报告一、研究背景及意义自适应均衡器(Adaptive Equalizer)是数字通信领域中的重要技术之一,能够对接收信号的失真进行补偿,从而提高系统的抗干扰能力和传输性能。

较早期的自适应均衡器是基于DSP处理器或者纯软件实现的,但是这种实现方式存在处理速度慢、功耗较大等问题。

而基于FPGA实现自适应均衡器可以有效解决这些问题,具有处理速度快、硬件可重构、可实现并行处理等优点,因此也成为了近年来广泛应用的实现方式。

本文将会探讨如何基于FPGA实现自适应均衡器,并研究不同均衡算法的优缺点,比较它们在不同信道环境下的性能差异。

研究结果将有助于提高数字通信系统的稳定性和性能表现,对智能终端、移动通信网络等领域具有一定的应用价值和市场前景。

二、研究内容及方法1.研究内容本研究将围绕如下的研究内容展开:(1)自适应均衡器的基本原理及各种均衡算法的模型推导和性能分析。

(2)基于FPGA的自适应均衡器系统的设计和实现,包括硬件电路系统的搭建和算法模块的软件设计。

(3)针对均衡器在不同信道环境下的性能差异进行实验和数据分析,比较不同算法性能的差异。

2.研究方法本研究将采用如下方法进行:(1)文献调研和理论分析:对自适应均衡器和各种均衡算法进行综述和调研,比较它们的优缺点,找出其中适合用于FPGA实现的算法。

(2)硬件电路设计:建立自适应均衡器硬件电路,包括模拟信号采集模块、ADC模块、FPGA模块、DAC模块和模拟输出模块等。

(3)算法模块设计:在FPGA中实现各种自适应均衡算法,比较它们在不同信道环境下的性能表现。

(4)实验和数据分析:利用仿真软件和实际硬件平台,对自适应均衡器在不同信道环境下的性能进行测试和分析,比较各种算法的性能差异。

三、预期成果1.硬件电路设计和实现自适应均衡器,测试其在不同信道环境下的性能表现。

2.实现自适应均衡器中的各个算法模块,比较它们的性能差异,找出适合实际应用的算法。

基于FPGA的判决反馈均衡器设计

前馈 滤 波 器 阶 反 馈 滤 波 器 阶 数 数

3 2 2 6 2 0 3 l 2 5 1 9

和非 线性 均衡 器 都采 用L S M 自适 应算 法 ,信 源采 用O PK 制 ,使 用4 过采 Q S调 倍 样 ,对接 收到 的 基带 信号 进行 平 方根 升余 弦 滚降 成型 滤波 ,滚 降 因子 05 .;

表 2 判 决 反馈 自适 应均 衡器 参数

3MAT 仿 真结 果 U B

均 衡 器

1 2 3

下面 比较 了在 同一 个 系统 中不 使 用均 衡 算法 ,使 用 线性 自适应 均 衡算

法及 使 用判 决 反馈 自适 应均 衡 算 法 的MT A 仿真 结 果 。其 中 ,线 性 均衡 器 ALB

仿真数 据 长度 10 0 ,其 结 果如 下 : 00 0

特 误 码 率 误 码 率

1 1 0。

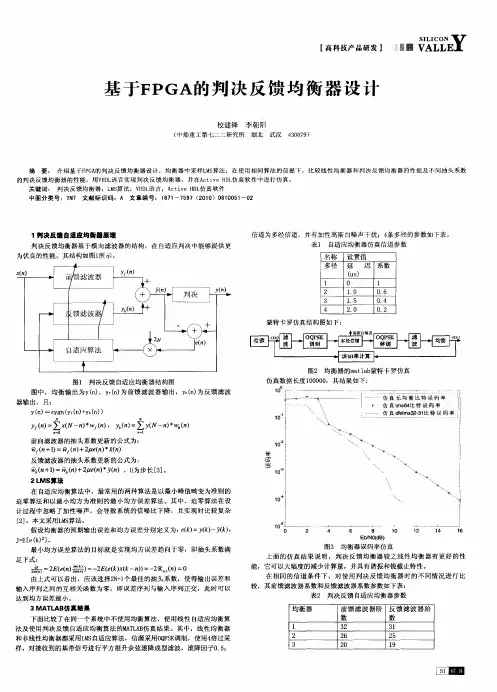

图 中 ,均衡 输 出为 yn ,Y() 前 馈 滤波 器 输 出 ,y() 反馈 滤 波 () r 为 n bn 为 器 输 出 ,且 :

Y n =s g ( f ) y () () y n y ( + bn ) n

1判 决反 馈 自适应 均衡 器 原理 判决 反 馈均 衡器 基 于横 向滤波 器 的结 构 ,在 自适 应 判决 中能够 提供 更 为优 良的性 能; 其结 构如 图 l 示 。 所

信道 为 多经信 道 ,并 有加 性 高斯 白噪声干 扰 ;4 多径 的参 数如 下表 。 条 表 1 自适 应均 衡 器仿 真信 道参 数

的判 决反馈均衡器 的性能 ,用V D 语 言实现判 决反馈均衡 器 ,并在A t v D 仿真 软件 中进 行仿真 。 HL c ieH L

基于FPGA的自适应均衡器设计与实现

Ab ta t s r c :On t e b ss o i l t n o h a i fsmu a i f o LM S a g rt m n M ATLAB p a f r ,t eh r wa e i lm e — lo i h o lto m h a d r mp e n

一

横 向 自适应 滤 波 器 , 过仿 真测 试 , 通 以检 验设 计 的 效果 。

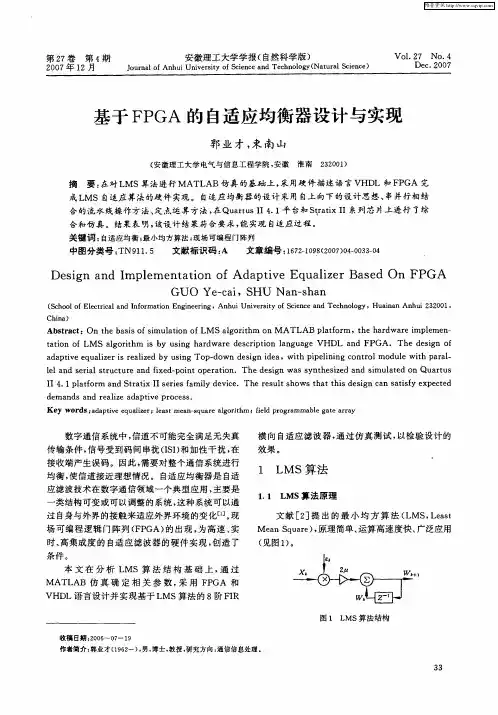

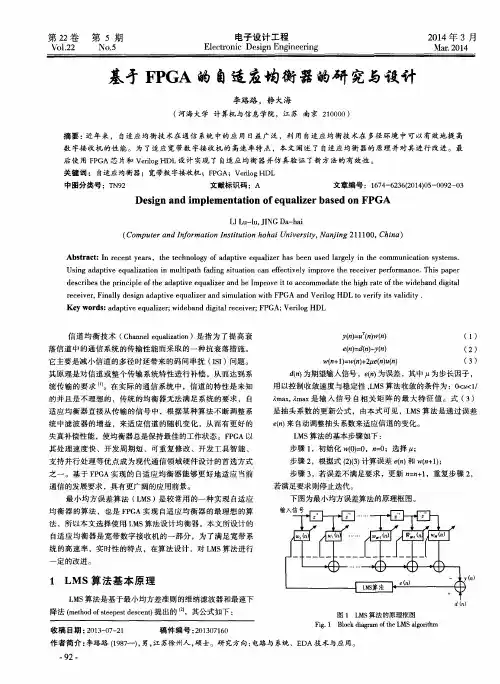

L MS算 法

11 L . MS算 法原 理 文 献 [ ] 出 的 最 小 均 方 算 法 ( MS L at 2提 L , es Me nS u r ) 原理 简单 、 算高 速度快 、 a q ae , 运 广泛应用

误差调整模块先根据期望响应信号dt和滤波器输出值弘求得输出误差值再将输出误差与迭代步长的2倍相乘得到中间变量2卢缸为权向量的迭代提供调整后的误差数据该逻辑单元主要进行减法计算和乘法运算

维普资讯

第2 卷 7

第 4期

安徽理 工 大学 学报 ( 自然 科 学版 )

t t n o a i fLM S ag rt m sb sn a d r e ci t n ln u g oቤተ መጻሕፍቲ ባይዱ l o ih i y u i g h r wa ed srp i a g a e VHDL a d FP o n GA. Th e in o e d sg f

数字通 信系统 中 , 信道不 可能 完全 满足无 失 真

传输 条件 , 信号 受到 码 间 串扰 (S ) 加性 干 扰 , I I和 在 接收端 产生误 码 。因此 , 需要 对 整个通 信系统 进行 均衡 , 使信道接 近 理想情 况 。 自适 应均 衡器是 自适 应滤 波技术 在数字 通 信领域 一个典 型应 用 , 主要 是

分数间隔判决反馈盲均衡器的设计与仿真

DFE-FSE DFE-SSE 25

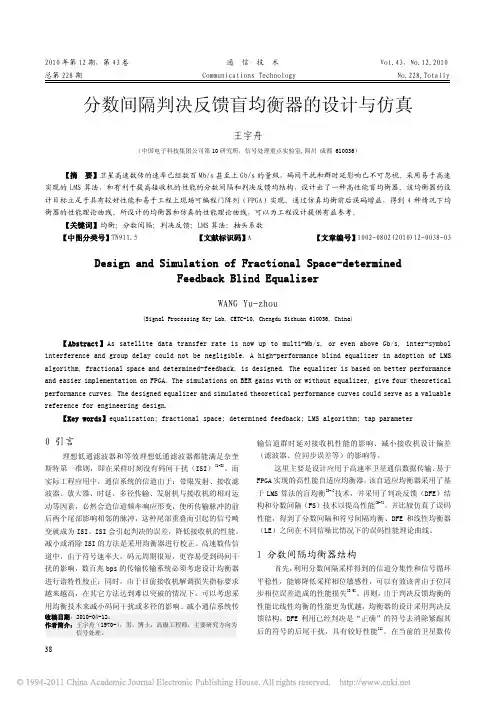

从上面两组仿真的情况可以看出:在其它条件相同的情 况下,FSE 比 SSE 性能要优于 8 dB 左右(误码该善增益); 在其它条件相同的情况下,DFE 比 LE 性能要优于 8 dB 左右 (误码该善增益);若将这个误码该善增益折算到 Eb/N0,将 是 0.8 dB 的性能增益。这个增益是相对性能增益,DFE 和 LE 或 FSE 和 SSE 间相比较的性能增益。可以得到结论是 FSE-DFE 将比 SSE-LE 性能优越 1.6 dB 左右。

如图 2、图 3、图 4 和图 5 是仿真得到误码该善增益的

理论曲线。各仿真图中,横轴为信噪比,从 SNR=0 到 SNR=18,

SNR 变化的分辨率为 0.1 dB;纵坐标表示前面定义的均衡器

前后的误码该善增益,用 dB 进行表示。

18

SSE-LE

16

SSE-DFE

14

均衡前后误码增益/dB

) 12 Bd

其中 z(k) 是判决器的输出, d j (k) 是逆向滤波器的 j 个抽头

系数。

判决器的功能表示为:

z(k)

=

sign(

y(k

))

=

⎧ 1, ⎨⎩−1,

其中, y(k) = P(k) − N (k) 。

y(k) ≥ 0, y(k) < 0,

进行抽头系数更新的自适应算法采用 LMS 算法,其基

本公式如下: 估计误差: e(k) = z(k) − y(k) , 抽头系数更新: ω(k +1) = ω(k) + μu(k)e*(k) ,

4 结语

设计了适合卫星高速数传的分数间隔、DFE 盲均自适应 衡器,并进行了各种性能比较,得到 FSE 与 SSE、DFE 与 LE 的相对性能比较的理论曲线;并同时获得了个种均衡器的绝 对理论性能。设计的均衡器适合 FPGA 或 ASIC 设计,仿真的 理论曲线,对高速数传均衡器设计具有一定的参考价值。

基于FPGA的判决反馈均衡器的设计与实现

基于FPGA的判决反馈均衡器的设计与实现1. 引言在移动通信和高速无线数据通信中,多径效应和信道带宽的有限性以及信道特性的不完善性导致数据传输时不可避免的产生码间干扰,成为影响通信质量的主要因素,而信道的均衡技术可以消除码间干扰和噪声,并减少误码率。

其中判决反馈均衡器(DFE)是一种非常有效且应用广泛得对付多径干扰得措施。

目前DFE 大致有以下几种实现方法:1)采用多片通用数字滤波器集成电路级联方式,但同时由与多片带来的体积和功耗的增加,在实际中运用不多。

2)采用DSP 来实现,如Motorola SC140 就是单片的可编程均衡器,采用软件来实现算法,但由于受器件功能限制,在实时性要求极高的场合中受到限制。

3)采用可编程逻辑器件实现,随着可编程逻辑器件逻辑门数量和速度的不断增加,在单片上实现系统集成已经成为可能,而且FPGA 特别适合实现可配置的判决反馈均衡器。

2.判决反馈均衡器的基本原理判决反馈均衡器(DFE)是一种非线性均衡器。

如图1 所示,由前馈部分(由FIR 滤波器组成)和反馈部分(由IIR 滤波器组成)组成,前馈部分可以抵消在时间上超前的码间干扰和在时间是滞后的码间干扰(由中心抽头的位置决定),反馈部分可以抵消在时间上滞后的码间干扰。

均衡器的输出为:式中M,N 分别为前馈滤波器和反馈滤波器的长度。

抽头系数更新采用DD_LMS(direct decision least mean square)和CMA(constant modulus algorithm)算法,CMA 是一种盲自适应算法,即不需要训练序列,可以让均衡器收敛到较。

基于FPGA的自适应均衡器的研究与设计

Us i n g a d a p t i v e e q u a l i z a t i o n i n mu hi p a t h f a d i n g s i t u a t i o n c a n e f f e c t i v e l y i mp r o v e t h e r e c e i v e r p e r f o r ma n c e . T h i s p a p e r

Ab s t r a c t : I n r e c e n t y e a r s ,t h e t e c h n o l o g y o f a d a p t i v e e q u a l i z e r h a s b e e n u s e d l a r g e l y i n t h e c o mmu n i c a t i o n s y s t e ms .

LI L u — l u . J I NG Da — h a i

( C o m p u t e r a n dI n f o r ma t i o n I n s t i t u t i o n h o h a i U n i v e r s i t y , N a n j i n g 2 1 1 1 0 0 , C h i n a )

d e s c r i b e s t h e p r i n c i p l e o f t h e a d a p t i v e e q u a l i z e r a n d b e I mp r o v e i t t o a c c o mmo d a t e t h e h i g h r a t e o f t h e wi d e b a n d d i g i t a l

判决反馈盲均衡的设计与仿真

判 决 反 馈 盲 均 衡 的 设 计 与 仿 真

江苏金 陵机 械 制造 总厂 徐 立升

【 摘要 】 介绍了判决反馈均衡算法的 实现 ,并将 最陡下降恒模算法应用到D F E ,实现 了自 适应算法 ,通过仿真比较了均衡前后的星座图,并

分析 均衡 前后 的误 码率 曲线 ,验证 了恒模 算 法 的D F E 可减 小 多径 效应的 干扰 、

【 关键词 】 判决反馈 ;恒模算法;误差传播

0 引 言

j 二 用无线通信 领域 ,受传输环境的杉响,传输信 号经过不I 路径到 达接收系统,使得接 收端 的波形 叮避 免的产生码问f扰 。为 J 提高通 信质量,减小码 问干扰 ,接收端通常采 『 l j 均衡器来消除码问干扰 。在各

1 判决反馈均衡器原理

D F E 由前 馈滤 波 器 、反 馈滤 波 器和 判 决器 三个 部 分组 成 … 。 原 理 图如 图1 所 示。

4 6

丈 中采 川ma t l a b 对盲 均 衡DF E 的 性 能进 行 了仿 真 ,采 用 涮制 方 式 为8 P S K,信 噪 比为S NR =3 0 。均新 n d 摩 图如 图3 所示。

表 1农 村 信 道 环 境

多i 1 f = 数

1

卡 ¨对时 I ' i f J【u s)

0. 0 0 I

̄ F: B j 功率 ( d B )

O 0 1 O 8 0 I 2. ( ) l 6. 0 2 O. O

: j

0 2 0 : { 0 I 0 5

~ 1 1 1 . — 一

.

◆

基于FPGA的预测控制器设计_毕业设计 精品

基于FPGA的预测控制器设计摘要预测控制是随着自适应控制的研究而发展起来的一种先进的计算机控制算法,FPGA具有很强的并行运算能力,运行速度快,采用FPGA阵列处理器实现预测控制系统,能大幅提高预测控制的在线优化速度。

本文在Xilinx公司的集成开发环境ISE9.1i中,采用硬件描述语言HDL编程,调用IP核等输入方式,完成了预测控制改进算法的PPGA设计与实现。

论文首先介绍了广义预测控制算法以及改进的算法,由于算法主要涉及矩阵相关的运算需要进行大量的数据计算和处理,为了减少数据计算的复杂性,从实现算法的控制器的硬件结构上改进,因此采用FPGA阵列处理器实现预测控制系统。

针对基于FPGA 硬件实现的特点介绍了求解预测控制中逆矩阵的递推算法,设计出了预测控制的处理器阵列结构.在设计中采用层次化,模块化的思想,将整个算法划分成多个功能模块,画出了各模块的流程图。

包括系统的总体结构设计,基本的处理器单元的设计,递推求逆算法的处理器阵列设计,输出预测的处理器阵列设计,控制增量的计算,参数辨识等。

最后用Modelsim仿真软件对各模块进行了仿真,给出了仿真结果。

设计中的各模块均采用HDL通用硬件描述语言进行描述,对仿真结果进行了分析表明:采用FPGA阵列处理器实现预测控制系统,能大幅提高预测控制的在线优化速度,减小控制器面积,扩大预测控制的应用领域.关键词:预测控制算法;FPGA;处理器阵列;矩阵求逆;并行运算Design of predictive controller based on FPGAAbstractWith the development of adaptive control, predictive control is proposed. Predictive control algorithm is an advanced computer control algorithm, and based on parameter model without strict requirements to process model. FPGA system has strong parallel computing capability and higher speed in calculations. So in-line optimization speed is raised.In the thesis, based on Xilinx integrated developing environment ISE9.1i, using hardware description language as the programming language, IP core as the input, a improved predictive-control algorithm is designed and implemented using FPGA. General predictive-control algorithm and its improved format are introduced. The algorithm involves with many matrix calculation, so a lot of data computing and processing is needed. At the same time improvement from controller and hardware structure is obtained. FPGA array processor is used to implement predictive-control system.Due to the FPGA hardware implement, recurrent method for Matrix inversion in the predictive-control is briefly discussed. Predictive-control processor array structure is designed. In the design, adopting hierarchy and module method, the entire algorithm is divided into function modules, flows of function modules have been drawed. Such as overall system structure design, basic processor design, recurring matrix inversion processor array design, output prediction processor array design, control incrementcalculation, parameter identification, and so on. Every functional module is simulated using software Modelsim. The simulation result is given.HDL description language is applied in the models of design. Analyzes the results of simulation and receives some useful conclusions. So in-line optimization speed is raised and the size and cost is reduced, the application field is greatly expanded.Key words:Predictive-control algorithm; FPGA;Processor arrays; Matrix inversion; Parallel algorithm目录摘要 (I)ABSTRACT (II)第 1 章绪论 (1)1.1 研究现状概述 (1)1.2 预测控制的发展和应用 (3)1.3 预测控制在新应用中面临的问题 (4)1.4 FPGA 实现预测控制器的优势 (5)1.5 主要内容 (7)第 2 章基础知识 (8)2.1 FPGA 技术 (8)2.1.1 FPGA 结构 (8)2.1.2 FPGA 特点 (11)2.2 SOPC 技术 (11)2.3 Nios II 嵌入式软核处理器 (13)2.4 FPGA/SOPC 开发工具 (14)2.5 FPGA/SOPC 开发流程 (16)第3章广义预测控制算法 (19)3.1 预测控制的特点 (19)3.1.1 预测模型 (19)3.2 改进的广义预测控制算法 (21)3.2.1 预测模型 (21)3.2.2 最小方差预报器 (22)3.2.3 预测输出 (22)3.2.4 参考轨迹 (23)3.3 矩阵分解 (23)3.4 递推求逆 (24)第4章预测控制FPGA实现的基本单元介绍 (26)4.1 乘法加法器: (26)4.2 移位寄存器: (27)4.3 A/D转换模块: (28)4.4 D/A转换模块: (30)第5章预测控制器设计方案 (32)5.1 Nios II 处理器内核 (33)5.2 JTAG UART IP 核 (35)5.3 timer IP核 (35)5.4 UART IP核 (36)5.5 SPIIP核 (36)5.6 avalon-M M Tristate总线桥IP核 (37)5.6.1 UART 串口通信 (39)5.7 系统集成及调试 (40)第6 章总结 (42)参考文献 (43)致谢 (45)第 1 章绪论预测控制又称为模型预测控制,它是 70 年代后期在工业过程控制领域中产生的一类新型计算机控制算法。

基于FPGA的奇偶分频器的设计与实现_毕业设计说明书

内蒙古科技大学本科生毕业设计说明书(毕业论文)题目:基于FPGA的奇偶分频器的设计与实现基于FPGA的奇偶分频器的设计与实现摘要分频器作为一种最基本的数字电路,广泛的应用在各种复杂的逻辑电路设计中,对于FPGA芯片来说,虽然能用自带的锁相环来产生一部分我们所需的频率,但是,用VHDL语言实现分频能从同一时钟较为方便、快捷的生成多个所需要的频率,同时能够实现信号的同步,因此,分频器的应用非常广泛。

本设计应用软件为开发平台,运用VHDL语言编程实现整数的奇偶分频的设计,在本设计中实现了0、2、4、6、8、10、12、14偶数的整数分频器设计和1、3、5、7、9、11、13、15奇数的整数分频器设计。

通过仿真结果,验证了设计的正确性。

关键词:FPGA;分频器;VHDL语言;Quartus ⅡDesign and implementation of FPGA-based parity dividerAbstractDivider as a basic digital circuits, widely used in a variety of complex logic circuit design, the FPGA chip, although able to own a part of our phase-locked loop to produce the desired frequency, but using VHDL language divide from the same clock frequency is more convenient and efficient to generate multiple needs, while able to achieve synchronization signal, and therefore, the divider is widely used.The design of application software development platform, the use of VHDL language programming odd integer divider design, the design is implemented in an even integer divider 0,2,4,6,8,10,12,14 design and 1,3,5,7,9,11,13,15 odd integer divider design. The simulation results verify the correctness of the design.Key words: FPGA; divider; VHDL language;Quartus Ⅱ目录摘要 (I)Abstract (II)第一章绪论 (1)1.1 课题来源 (1)1.2 选题的意义和目的 (2)1.3 课题研究现状 (3)1.4 本文组织结构 (4)第二章EDA技术 (6)2.1 FPGA技术 (6)2.2 Quartus Ⅱ软件简介 (7)2.3 VHDL语言 (8)2.3.1 VHDL简介 (8)2.3.2 VHDL特点 (9)2.3.3 VHDL组成 (10)第三章奇偶分频器设计与仿真 (12)3.1 偶数分频 (12)3.1.1 原理分析 (12)3.1.2 设计与仿真 (12)3.2 奇数分频 (17)3.2.1 原理分析 (17)3.2.2 设计与仿真 (18)第四章系统设计 (23)4.1 设计的任务 (23)4.2 系统设计 (23)4.3 其余模块设计 (27)4.3.1 encoder_12模块 (27)4.3.2 mux21模块 (29)4.3.3 数码管显示驱动模块 (30)第五章下载与测试 (35)5.1 BTYG-EDA实验概述 (35)5.2 BTYG-EDA实验开发系统特点 (35)5.3 引脚分配 (35)5.4 验证 (36)第六章结论与展望 (37)6.1 结论 (37)6.2 展望 (37)参考文献 (39)致谢 (40)第一章绪论1.1 课题来源分频器作为数字系统设计中一类重要的电子电路,在数字电路的迅速发展历程中,通常要运用分频器来实现设计中希望获取的时钟频率。

一种基于FPGA的判决反馈均衡器

oo 0 o 01 O1 0 01 1 1o o 1 01 10 i 0 l 3

i 是误差 ,o_ 是 系数调 整量 。反 向滤波 器也是类 n ceo

c e fe c e o r c o

_ _

似定义 :

f ( l c ). s ( st a i x ) r .k l , ee r e ,_n i , e e ( k r te ) . (n

基金项 目: 国家 自然科学基金项 目(00 0 8 ; 6 8 2 1 ) 广西信息与通信技术重点实验 室基金项 目(O 0 )广西教育厅项 目(0O 0 x1 2 19 4 ; 211L 4 )

5 0

21第5第6( 3期 0年 3 1 总 6 ) 1 卷 期 第 6

ln b mai n tr n l d s ly l r t mi a & ip a I o e

等几个部分构成 。

仿真 , 设调制类 型为 B S 采用 L S 假 P K, M 算法 , 理如图 2 原

所示 。

主要仿 真参数设置 为 : 向滤波器 阶数是 9 后 向滤 前 ; 波器 阶数是 9步长值是 0 0 。仿 真结果如 图 3 ; .5 0 所示 , 可

以看 出, 均衡器在几百个数据 以后开始收敛 。

( 桂林 电子科技大学 信息与通信 学院。 广西 桂林 5 10 ) 4 0 4

【 摘 要 】论述 了一种 基 于现 场 可编 程 门阵 列( P A 的判 决 反馈 均衡 器 的设 计 。首 先介 绍 了判决 反馈 均 衡器 的原 理 , FG ) 然后

给 出 了Sm l k仿 真 的 电路 和仿 真结 果 , 绍 了用 分 布 式算 法 ( A) 实现 滤 波器 的原理 和 各模 块原 理 , i ui n 介 D 来 最后 给 出Mo e i d lm s

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

上 实 现 的盲 均 衡 器 能 够 较 好 地 完 成 对 不 同 调 制 阶 数 QAM 信 号 的 均 衡 。

关键 词 盲均衡器 ;分数 间隔;预测判决反馈 ;F GA P 中图分 类 号 ;T 1 . N9 1 5 文献标 识码 t A

1

引 言

在 数 字 通 信 系 统 中 , 为 了消 除 由通 信信 道 有 限 带 宽 限 制 与 多径 传 播 等 因 素 引 起 的 码 间 干扰 ,接 收

图 1 分数 间隔 预测 判决 反馈均 衡器 的多采样 率 系统模 型

Pe it e cs nF eb c q aie,记 为F —DF 。图 1为F DF rdci ii ed akE u l r v De o z SP E) SP E的 多采 样 率 系 统 模 型 。前 向滤 波 器 采 用 分 数 间 隔 , 采 样 频 率 大 于 奈 奎 斯 特 频 率 , 免 了符 号速 率 均 衡 器 因 欠采 样 引起 的频 谱 混 叠 , 其 避

基 于F G P A的分 数 间隔预测 判决 反馈 均衡 器 的设 计 与实现

霍 亚 娟 , 葛 临东 , 王彬

( 息 工 程 大 学 信 息 工 程 学 院 ,河 南 郑 州 4 0 0 ) 信 5 0 2

摘 要 。针对 高 阶 Q AM 信号 ,本 文设 计实 现 了一种 基 于 F GA 的分 数 间隔预 测判 决反 馈均衡 器 。前 向滤波 器采 用 P

端 需 要 引 入 均 衡 技 术 。 由于 盲 均 衡 技术 不 需 要 发 送 端 发 送 训 练 序 列 ,提 高 了频 带 利 用 率 ,因 此 得 到 了

广 泛 应 用 。近 年 来 , 大 量 基 于AS C的 Q I AM解 调 器 设 计 中 引入 了盲 均 衡 器 【 。而 基 于 F GA的盲 均 衡 l J P 器 与 之 相 比 ,具 有 可 重 复编 程 、设 计 灵 活 、 易于 维 护 等 优 势 L 。文 献 [~ ] 于 F GA设 计 实 现 的 盲均 4 J 4 6基 P

在这里 ,用 标识符号速率 ,用 k标识分数 间隔。图 1中,P为过采样 因子 ,发送信号 为离 ()

散信息符号序列, () 为过采样信道的冲激响应函数,v ) ( 为加性高斯 白噪声, ( 为前向滤波器的 J } i 七 )

收稿 日期 ,2 1 ・32 0 00 -2

修 订 日期 :2 1—50 0 00 —4

基 金 项 目 t河 南 省基 础 与前 沿 项 目 ( 83 0 12 5 020430 )

电路与系统学报

第 1 6卷

输入信号,W 为分数间隔前向滤波器的系数。假设分数间隔前向滤波器长度为 ,则分数间隔前向 ()

输入 向量为 =W )l , w ) 0 W … L ) ) 1 ,k 1 。 ) = , ) r 一 +) 经过P r , ( 一 … r 倍抽取得到符号速率输出 信号“ ) 以 ( , 符号速率更新前向 聆

于十字型Q AM信 号 。

2 盲均 衡 器设 计

2 1 算 法 描 述 . 本 文 给 出 了 一 种 基 于 FG P A的 分 数 间 隔 预 测 判 决 反 馈 均 衡 器 ( rc o al p c d F at n l S a e i y

闷

㈤ “ ]j y厂

能 够 补 偿 固有 的信 道 畸 变 。 反馈 滤 波 器 仍 为 符 号 速 率 ,采 用 预 测 判 决 反 馈 结 构 ,可 以从 当前 符 号 中消 除 先 前 符 号 引起 的部 分 码 问干 扰 , 使 输 出信 号 的 均 方 误差 更 小 , 同 时能 够 避 免 传 统 判 决 反 馈 结 构 由于 错 误 传 播 引起 的误 收敛 情 况 …,适 合 深 衰 落 信 道 盲 均 衡 。

第 1 卷 第 4期 6 2 1 年 8月 01

文 章 编 号 : 1 0 .2 9(O 0 — 130 0 70 4 2 l) 40 0 -7 1

电路与系统学报

J 0URNAL OF CI RCUI TS AND YS M S S TE

V O .6 N o. 11 4 Aug t 2011 us,

衡 器 都 采 用 常 模 类 算 法 ( MA) ] 新 均 衡 器 系 数 ,对 高 阶 Q C 更 AM信 号 稳 态 误 差 大 。文 献 [] F G 7在 P A上 设 计 实 现 了基 于 混 合 算 法 的适 用 于 高 阶 Q AM信 号 的盲 均 衡 器 ,但 仅 限 于 方 型QAM信 号 。 本文针对 高阶Q AM信 号 设 计 实现 了一 种 基 于 F GA的分 数 间 隔预 测 判 决 反 馈 均 衡 器 。该 均 衡 器 充 P 分 结 合 了分 数 间 隔 均衡 器 与 预测 判 决 反 馈 均 衡 器 的优 势 , 能够 消 除 由深 衰 落 信 道 引起 的严 重码 间干 扰 。 在 更 新 滤 波 器 抽 头 系 数 时 ,对P n 法 J 行 简 化 ,在 获得 较 低 稳 态 误 差 的 同时 ,简 化 了F G a算 进 P A实现 。 测 试 结 果 表 明 , 本 文 基 于 F GA设 计 实现 的盲 均 衡 器 不 仅 能 够 成 功 均 衡 方 型 高 阶QAM信 号 ,而 且 适 用 P