OPENCV2.4.2移植到TINY6410

Uboot_for_Tiny6410_移植步骤详解

Uboot_for_Tiny6410_移植步骤详解一、设计要求1.目的1)掌握U-boot剪裁编写2)掌握交叉编译环境的配置3)掌握U-boot的移植2.实现的功能1)U-boot编译成功2)移植U-boot,使系统支持从NAND FLASH启动二、设计方案1.硬件资源1)ARM处理器:ARM11芯片(SamsungS3C6410A),基于ARM1176JZF-S核设计,运行频率533Mhz, 最高可达667Mhz2)存储器:128M DDR RAM,可升级至256M;MLC NAND Flash(2GB)3)其他资源:具有三LCD接口、4线电阻触摸屏接口、100M 标准网络接口、标准DB9 五线串口、Mini USB 2.0 接口、USB Host 1.1、3.5mm音频输入输出口、标准TV-OUT 接口、SD卡座、红外接收等常用接口;另外还引出4路TTL串口,另1 路TV-OUT、SDIO2 接口(可接SD WiFi)接口等;在板的还有蜂鸣器、I2C-EEPROM、备份电池、AD可调电阻、8 个中断式按键等。

2.软件资源1)arm-linux-gcc-4.5.1(交叉编译)2)u-boot-2010.09.tar.gzarm-linux-gcc-4.5.1-v6-vfp-20101103.tgz三、移植过程1.环境搭建1)建立交叉编译环境2)去这2 个网站随便下载都可以下载得到最新或者你想要的u-boot。

(/batch.viewlink.php?itemid=1694ftp://ftp.denx.de/pub/u-boot/)下面是具体的对u-boot…的修改一:下载并解压u-boot-gxb.tar.gz。

#tar xzvf u-boot-gxb.tar.gz二:在顶层的目录下找到Makefile文件,并用gedit打开在Makefile中找到下面代码进行修改########################################################################## ARM1176 Systems#########################################################################smdk6400_noUSB_config \smdk6400_config : unconfig@mkdir -p $(obj)include $(obj)board/samsung/smdk6400@mkdir -p $(obj)nand_spl/board/samsung/smdk6400@echo "#define CONFIG_NAND_U_BOOT" > $(obj)include/config.h@echo "CONFIG_NAND_U_BOOT = y" >> $(obj)include/config.mk@if [ -z "$(findstring smdk6400_noUSB_config,$@)" ]; then \echo "RAM_TEXT = 0x57e00000" >> $(obj)board/samsung/smdk6400/config.tmp;\ else \echo "RAM_TEXT = 0xc7e00000" >> $(obj)board/samsung/smdk6400/config.tmp;\ fi@$(MKCONFIG) smdk6400 arm arm1176 smdk6400 samsung s3c64xx@echo "CONFIG_NAND_U_BOOT = y" >> $(obj)include/config.mk下面红色的为新增加的#=====================更改部分=======================================tiny6410_noUSB_config \tiny6410_config : unconfig@mkdir -p $(obj)include $(obj)board/samsung/tiny6410@mkdir -p $(obj)nand_spl/board/samsung/tiny6410@echo "#define CONFIG_NAND_U_BOOT" > $(obj)include/config.h@echo "CONFIG_NAND_U_BOOT = y" >> $(obj)include/config.mk@if [ -z "$(findstring tiny6410_noUSB_config,$@)" ]; then \echo "RAM_TEXT = 0x57e00000" >>$(obj)board/samsung/tiny6410/config.tmp;\else \echo "RAM_TEXT = 0xc7e00000" >> $(obj)board/samsung/tiny6410/config.tmp;\fi@$(MKCONFIG) tiny6410 arm arm1176 tiny6410 samsung s3c64xx@echo "CONFIG_NAND_U_BOOT = y" >> $(obj)include/config.mk#==================================================================三: arch/arm/cpu/arm1176/s3c64xx/cpu_init.S#gedit arch/arm/cpu/arm1176/s3c64xx/cpu_init.S#include <config.h>#include <asm/arch/s3c6400.h>.globl mem_ctrl_asm_initmem_ctrl_asm_init:/* DMC1 base address 0x7e001000 */ldr r0, =ELFIN_DMC1_BASEldr r1, =0x4str r1, [r0, #INDEX_DMC_MEMC_CMD]ldr r1, =DMC_DDR_REFRESH_PRDstr r1, [r0, #INDEX_DMC_REFRESH_PRD]ldr r1, =DMC_DDR_CAS_LATENCYstr r1, [r0, #INDEX_DMC_CAS_LATENCY]ldr r1, =DMC_DDR_t_DQSSstr r1, [r0, #INDEX_DMC_T_DQSS]ldr r1, =DMC_DDR_t_MRDstr r1, [r0, #INDEX_DMC_T_MRD]ldr r1, =DMC_DDR_t_RASstr r1, [r0, #INDEX_DMC_T_RAS]ldr r1, =DMC_DDR_t_RCstr r1, [r0, #INDEX_DMC_T_RC]ldr r1, =DMC_DDR_t_RCDldr r2, =DMC_DDR_schedule_RCDorr r1, r1, r2str r1, [r0, #INDEX_DMC_T_RCD]ldr r1, =DMC_DDR_t_RFCldr r2, =DMC_DDR_schedule_RFCorr r1, r1, r2str r1, [r0, #INDEX_DMC_T_RFC]ldr r1, =DMC_DDR_t_RPldr r2, =DMC_DDR_schedule_RPorr r1, r1, r2str r1, [r0, #INDEX_DMC_T_RP]ldr r1, =DMC_DDR_t_RRDstr r1, [r0, #INDEX_DMC_T_RRD]ldr r1, =DMC_DDR_t_WRstr r1, [r0, #INDEX_DMC_T_WR]ldr r1, =DMC_DDR_t_WTRstr r1, [r0, #INDEX_DMC_T_WTR]ldr r1, =DMC_DDR_t_XPstr r1, [r0, #INDEX_DMC_T_XP]ldr r1, =DMC_DDR_t_XSRstr r1, [r0, #INDEX_DMC_T_XSR]ldr r1, =DMC_DDR_t_ESRstr r1, [r0, #INDEX_DMC_T_ESR]ldr r1, =DMC1_MEM_CFGstr r1, [r0, #INDEX_DMC_MEMORY_CFG]ldr r1, =DMC1_MEM_CFG2str r1, [r0, #INDEX_DMC_MEMORY_CFG2]ldr r1, =DMC1_CHIP0_CFGstr r1, [r0, #INDEX_DMC_CHIP_0_CFG]ldr r1, =DMC_DDR_32_CFGstr r1, [r0, #INDEX_DMC_USER_CONFIG]/* DMC0 DDR Chip 0 configuration direct command reg */ ldr r1, =DMC_NOP0str r1, [r0, #INDEX_DMC_DIRECT_CMD]/* Precharge All */ldr r1, =DMC_PA0str r1, [r0, #INDEX_DMC_DIRECT_CMD]/* Auto Refresh 2 time */ldr r1, =DMC_AR0str r1, [r0, #INDEX_DMC_DIRECT_CMD]str r1, [r0, #INDEX_DMC_DIRECT_CMD]/* MRS */ldr r1, =DMC_mDDR_EMR0str r1, [r0, #INDEX_DMC_DIRECT_CMD]/* Mode Reg */ldr r1, =DMC_mDDR_MR0str r1, [r0, #INDEX_DMC_DIRECT_CMD]/* Enable DMC1 */mov r1, #0x0str r1, [r0, #INDEX_DMC_MEMC_CMD]check_dmc1_ready:ldr r1, [r0, #INDEX_DMC_MEMC_STATUS]mov r2, #0x3and r1, r1, r2cmp r1, #0x1bne check_dmc1_readynop添加下面红色的代码/*===========================更改部分=============================*/#if defined(CONFIG_TINY6410)#define SROM_BC1_REG_Tacs (0x0) // 0clk address set-up#define SROM_BC1_REG_Tcos (0x4) // 4clk chip selection set-up #define SROM_BC1_REG_Tacc (0xE) // 14clk access cycle#define SROM_BC1_REG_Tcoh (0x1) // 1clk chip selection hold#define SROM_BC1_REG_Tah (0x4) // 4clk address holding time#define SROM_BC1_REG_Tacp (0x6) // 6clk page mode access cycle #define SROM_BC1_REG_PMC (0x0) // normal(1data)page mode configuration#define SROM_BW_REG_DATA ((1<<7) | (1<<6) | (1<<4))#define SROM_BW_REG_BC1 (0xf << 4)#define SROM_BC1_REG_DATA ((SROM_BC1_REG_Tacs << 28) | \(SROM_BC1_REG_Tcos << 24) | \(SROM_BC1_REG_Tacc << 16) | (SROM_BC1_REG_Tcoh << 12) | \ (SROM_BC1_REG_Tah << 8) | (SROM_BC1_REG_Tacp << 4) | \(SROM_BC1_REG_PMC))ldr r0, =ELFIN_SROM_BASEldr r1, [r0, #SROM_BW_REG_DATA]mov r2, #(~SROM_BW_REG_BC1)and r1, r1, r2mov r2, #SROM_BW_REG_DATAorr r1, r1, r2str r1, [r0, #INDEX_SROM_BW_REG]ldr r1, =SROM_BC1_REG_DATAstr r1, [r0, #INDEX_SROM_BC1_REG]#endif/*========================================================*/ mov pc, lr.ltorg四:修改arch/arm/cpu/arm1176/s3c64xx/Makefile# gedit arch/arm/cpu/arm1176/s3c64xx/Makefileinclude $(TOPDIR)/config.mkLIB = $(obj)lib$(SOC).aSOBJS = reset.o#COBJS-$(CONFIG_S3C6400) += cpu_init.o speed.o添加下面红色代码#==================================更改部分================================ COBJS-$(CONFIG_S3C6410) += cpu_init.o speed.o#========================================================================= COBJS-y += timer.oOBJS := $(addprefix $(obj),$(SOBJS) $(COBJS-y))all: $(obj).depend $(START) $(LIB)$(LIB): $(OBJS)$(AR) $(ARFLAGS) $@ $(OBJS)五:修改arch\arm\include\asm\arch-s3c64xx\s3c64x0.h#ifndef __S3C64XX_H__#define __S3C64XX_H__添加红色代码/*==================================更改部分===============================*/ #if defined(CONFIG_SYNC_MODE) && defined(CONFIG_S3C6400) || defined(CONFIG_S3C6410) /*========================================================================*//*#error CONFIG_SYNC_MODE unavailable on S3C6400, please, fix your configuration!*/#endif#include <asm/types.h>六:修改arch/arm/include/asm/arch-s3c64xx/s3c6400.h#define ELFIN_SROM_BASE 0x70000000#define SROM_BW_REG __REG(ELFIN_SROM_BASE + 0x0)#define SROM_BC0_REG __REG(ELFIN_SROM_BASE + 0x4)#define SROM_BC1_REG __REG(ELFIN_SROM_BASE + 0x8)#define SROM_BC2_REG __REG(ELFIN_SROM_BASE + 0xC)#define SROM_BC3_REG __REG(ELFIN_SROM_BASE + 0x10)#define SROM_BC4_REG __REG(ELFIN_SROM_BASE + 0x14)#define SROM_BC5_REG __REG(ELFIN_SROM_BASE + 0x18)添加下面红色代码/*====================================更改部分=============================*/ #define INDEX_SROM_BW_REG 0x0#define INDEX_SROM_BC0_REG 0x4#define INDEX_SROM_BC1_REG 0x8#define INDEX_SROM_BC2_REG 0xC#define INDEX_SROM_BC3_REG 0x10#define INDEX_SROM_BC4_REG 0x14#define INDEX_SROM_BC5_REG 0x18/*========================================================================*//*七:在board/samsung建立tiny6410的文件夹,并且把smdk6400文件里面的所有文件复制过去,在修改board/samsung/tiny6410/lowlevel_init.S_TEXT_BASE:.word TEXT_BASE.globl lowlevel_initlowlevel_init:mov r12, lr/* LED on only #8 *//*=========================================更改部分========================*/ #if 0ldr r0, =ELFIN_GPIO_BASEldr r1, =0x55540000str r1, [r0, #GPNCON_OFFSET]ldr r1, =0x55555555str r1, [r0, #GPNPUD_OFFSET]ldr r1, =0xf000str r1, [r0, #GPNDAT_OFFSET]#endif/*=========================================================================*/ 将上面的红色的部分屏蔽掉wakeup_reset:/* Clear wakeup status register */ldr r0, =(ELFIN_CLOCK_POWER_BASE + WAKEUP_STAT_OFFSET)ldr r1, [r0]str r1, [r0]/* LED test *//*========================================更改部分===========================*/ #if 0ldr r0, =ELFIN_GPIO_BASEldr r1, =0x3000str r1, [r0, #GPNDAT_OFFSET]#endif/*===========================================================================*/ /* Load return address and jump to kernel */ldr r0, =(ELFIN_CLOCK_POWER_BASE + INF_REG0_OFFSET)/* r1 = physical address of s3c6400_cpu_resume function */ldr r1, [r0]/* Jump to kernel (sleep-s3c6400.S) */mov pc, r1nopnop将上面红色的部分屏蔽掉/** This was unconditional in original Samsung sources, but it doesn't* seem to make much sense on S3C6400.*//*======================================更改部分===========================*/ /*#ifndef CONFIG_S3C6400*/#if !defined(CONFIG_S3C6400) && !defined(CONFIG_S3C6410)/*=========================================================================*/ ldr r1, [r0, #OTHERS_OFFSET]bic r1, r1, #0xC0orr r1, r1, #0x40str r1, [r0, #OTHERS_OFFSET]八:修改board/Samsung/tiny6410/Makefile中include $(TOPDIR)/config.mkLIB = $(obj)lib$(BOARD).a#=============================更改部分=====================COBJS-y := tiny6410.oSOBJS := lowlevel_init.o#===========================================================SRCS := $(SOBJS:.o=.S) $(COBJS-y:.o=.c)OBJS := $(addprefix $(obj),$(COBJS-y))SOBJS := $(addprefix $(obj),$(SOBJS))九:修改board/samsung/tiny6410/tiny6410.c屏蔽掉下面头文件;/*===========================更改部分====================================*/ #if 0#include <netdev.h>#endif/*============================================================================* /#include <asm/arch/s3c6400.h>/* ===============================更改部分====================================*/ #if 0#define CS8900_Tacs 0x0 /* 0clk address set-up */#define CS8900_Tcos 0x4 /* 4clk chip selection set-up */#define CS8900_Tacc 0xE /* 14clk access cycle */#define CS8900_Tcoh 0x1 /* 1clk chip selection hold */#define CS8900_Tah 0x4 /* 4clk address holding time */#define CS8900_Tacp 0x6 /* 6clk page mode access cycle */#define CS8900_PMC 0x0 /* normal(1data)page mode configuration */#endif/*============================================================================* /static inline void delay(unsigned long loops){__asm__ volatile ("1:\n" "subs %0, %1, #1\n""bne 1b": "=r" (loops) : "0" (loops));}/** Miscellaneous platform dependent initialisations*//*=====================================更改部分==========================*/#if 0static void cs8900_pre_init(void){SROM_BW_REG &= ~(0xf << 4);SROM_BW_REG |= (1 << 7) | (1 << 6) | (1 << 4);SROM_BC1_REG = ((CS8900_Tacs << 28) + (CS8900_Tcos << 24) +(CS8900_Tacc << 16) + (CS8900_Tcoh << 12) +(CS8900_Tah << 8) + (CS8900_Tacp << 4) + CS8900_PMC);}#endif/*=======================================================================*/int board_init(void){DECLARE_GLOBAL_DATA_PTR;/*=========================================更改部分===================*/ #if 0cs8900_pre_init();#endif/* NOR-flash in SROM0 *//* Enable WAIT */SROM_BW_REG |= 4 | 8 | 1;gd->bd->bi_arch_number = MACH_TYPE;gd->bd->bi_boot_params = PHYS_SDRAM_1 + 0x100;return 0;}int dram_init(void){DECLARE_GLOBAL_DATA_PTR;gd->bd->bi_dram[0].start = PHYS_SDRAM_1;gd->bd->bi_dram[0].size = PHYS_SDRAM_1_SIZE;return 0;}#ifdef CONFIG_DISPLAY_BOARDINFOint checkboard(void){printf("Board: TINY6410\n");return 0;}#endif#ifdef CONFIG_ENABLE_MMU/*=====================================更改部分==========================*/ ulong virt_to_phy_tiny6410(ulong addr)/*=======================================================================*/ {if ((0xc0000000 <= addr) && (addr < 0xc8000000))return addr - 0xc0000000 + 0x50000000;elseprintf("do not support this address : %08lx\n", addr);return addr;}#endif/*=======================================更改部分=======================*/ #if 0ulong board_flash_get_legacy (ulong base, int banknum, flash_info_t *info){if (banknum == 0) { /* non-CFI boot flash */info->portwidth = FLASH_CFI_16BIT;info->chipwidth = FLASH_CFI_BY16;info->interface = FLASH_CFI_X16;return 1;} elsereturn 0;}#endif/*=======================================================================*//*=================================更改部分===============================*/#ifdef CONFIG_CMD_NETint board_eth_init(bd_t *bi){int rc = 0;#if defined(CONFIG_DRIVER_DM9000)rc = dm9000_initialize(bi);#endifreturn rc;}#endif十:修改drivers/net/dm9000x.cDM9000_ior(DM9000_MRCMDX); /* Dummy read *//* Get most updated data,only look at bits 0:1, See application notes DM9000 */rxbyte = DM9000_inb(DM9000_DATA) & 0x03;/*========================================更改部分==========================*/ #if 1u8 temp;temp=DM9000_ior(DM9000_MRRH);temp=DM9000_ior(DM9000_MRRL);#endif红色的为增加的/*============================================================================= *//* Status check: this byte must be 0 or 1 */if (rxbyte > DM9000_PKT_RDY) {DM9000_iow(DM9000_RCR, 0x00); /* Stop Device */DM9000_iow(DM9000_ISR, 0x80); /* Stop INT request */printf("DM9000 error: status check fail: 0x%x\n",rxbyte);return 0;}十一:修改drivers/usb/host/ohci-hcd.c#ifdef CONFIG_AT91RM9200#include <asm/arch/hardware.h> /* needed for AT91_USB_HOST_BASE */#endif//=====================更改部分================#if defined(CONFIG_ARM920T) || \defined(CONFIG_S3C24X0) || \defined(CONFIG_S3C6400) || \defined(CONFIG_S3C6410) || \defined(CONFIG_440EP) || \defined(CONFIG_PCI_OHCI)|| \defined(CONFIG_MPC5200) || \defined(CONFIG_SYS_OHCI_USE_NPS)//=============================================# define OHCI_USE_NPS /* force NoPowerSwitching mode */#endif#undef OHCI_VERBOSE_DEBUG /* not always helpful */十二:include/configs/tiny6410.h/** High Level Configuration Options* (easy to change)*///======================更改部分==================================//#define CONFIG_S3C6400 1 /* in a SAMSUNG S3C6400 SoC */#define CONFIG_S3C6410 1 /* in a SAMSUNG S3C6400 SoC */ //===============================================================#define CONFIG_S3C64XX 1 /* in a SAMSUNG S3C64XX Family */#define CONFIG_SMDK6400 1 /* on a SAMSUNG SMDK6400 Board *///=========================更改部分====================================#define CONFIG_TINY6410 1//===================================================================#define CONFIG_SKIP_RELOCATE_UBOOT#define CONFIG_PERIPORT_REMAP#define CONFIG_PERIPORT_BASE 0x70000000#define CONFIG_PERIPORT_SIZE 0x13#define CONFIG_SYS_SDRAM_BASE 0x50000000/* input clock of PLL: SMDK6400 has 12MHz input clock */#define CONFIG_SYS_CLK_FREQ 12000000#if !defined(CONFIG_NAND_SPL) && (TEXT_BASE >= 0xc0000000)#define CONFIG_ENABLE_MMU#endif#define CONFIG_SETUP_MEMORY_TAGS#define CONFIG_CMDLINE_TAG#define CONFIG_INITRD_TAG/** Architecture magic and machine type*///===================更改部分=====================/*#define MACH_TYPE 1270 */#define MACH_TYPE 2520//==============================================#define CONFIG_DISPLAY_CPUINFO#define CONFIG_DISPLAY_BOARDINFO/** Size of malloc() pool*/#define CONFIG_SYS_MALLOC_LEN (CONFIG_ENV_SIZE + 1024 * 1024) #define CONFIG_SYS_GBL_DATA_SIZE 128 /* size in bytes for initial data *//** Hardware drivers*///==========================更改部分============================ 将sc8900的网卡干掉#if 0#define CONFIG_NET_MULTI#define CONFIG_CS8900 /* we have a CS8900 on-board */#define CONFIG_CS8900_BASE 0x18800300#define CONFIG_CS8900_BUS16 /* follow the Linux driver */#endif换成下面的#define CONFIG_NET_MULTI 1#define CONFIG_DRIVER_DM9000 1#define CONFIG_DM9000_NO_SROM 1#define CONFIG_DM9000_USE_16BIT 1#define CONFIG_DM9000_BASE 0x18000300#define DM9000_IO CONFIG_DM9000_BASE#define DM9000_DATA (CONFIG_DM9000_BASE+4)#define CONFIG_ETHADDR 08:08:10:12:10:27#define CONFIG_NETMASK 255.255.255.0#define CONFIG_IPADDR 192.168.1.253#define CONFIG_SERVERIP 192.168.1.159#define CONFIG_GATEWAYIP 192.168.1.1//=============================================================/** select serial console configuration*/#define CONFIG_SERIAL1 1 /* we use SERIAL 1 on SMDK6400 */#define CONFIG_SYS_HUSH_PARSER /* use "hush" command parser */ #ifdef CONFIG_SYS_HUSH_PARSER#define CONFIG_SYS_PROMPT_HUSH_PS2 "> "#endif#define CONFIG_CMDLINE_EDITING/* allow to overwrite serial and ethaddr */#define CONFIG_ENV_OVERWRITE#define CONFIG_BAUDRATE 115200/************************************************************ Command definition***********************************************************/#include <config_cmd_default.h>#define CONFIG_CMD_CACHE#define CONFIG_CMD_REGINFO#define CONFIG_CMD_LOADS#define CONFIG_CMD_LOADB#define CONFIG_CMD_SAVEENV#define CONFIG_CMD_NAND#if defined(CONFIG_BOOT_ONENAND)#define CONFIG_CMD_ONENAND#endif#define CONFIG_CMD_PING#define CONFIG_CMD_ELF#define CONFIG_CMD_FAT#define CONFIG_CMD_EXT2//===========================================更改部分==================添加红色部分#undef CONFIG_CMD_IMLS//======================================================================#define CONFIG_BOOTDELAY 3#define CONFIG_ZERO_BOOTDELAY_CHECK#if (CONFIG_COMMANDS & CONFIG_CMD_KGDB)#define CONFIG_KGDB_BAUDRATE 115200 /* speed to run kgdb serial port */#define CONFIG_KGDB_SER_INDEX 1 /* which serial port to use */#endif/** Miscellaneous configurable options*/#define CONFIG_SYS_LONGHELP /* undef to save memory */下面修改为自己喜欢的提示字符//==============================更改部分====================================== //#define CONFIG_SYS_PROMPT "SMDK6400 # " /* Monitor Command Prompt */ #define CONFIG_SYS_PROMPT "TINY6410 # " /* Monitor Command Prompt *///===========================================================================#define CONFIG_SYS_CBSIZE 256 /* Console I/O Buffer Size */#define CONFIG_SYS_PBSIZE 384 /* Print Buffer Size */#define CONFIG_SYS_MAXARGS 16 /* max number of command args */#define CONFIG_SYS_BARGSIZE CONFIG_SYS_CBSIZE /* Boot Argument Buffer Size */#define CONFIG_SYS_MEMTEST_START C ONFIG_SYS_SDRAM_BASE /* memtest works on*/#define CONFIG_SYS_MEMTEST_END (CONFIG_SYS_SDRAM_BASE + 0x7e00000) /* 126MB in DRAM */#define CONFIG_SYS_LOAD_ADDR CONFIG_SYS_SDRAM_BASE /* default load address */#define CONFIG_SYS_HZ 1000/* valid baudrates */#define CONFIG_SYS_BAUDRATE_TABLE { 9600, 19200, 38400, 57600, 115200 }/*-----------------------------------------------------------------------* Stack sizes** The stack sizes are set up in start.S using the settings below*/#define CONFIG_STACKSIZE 0x40000 /* regular stack 256KB *//**********************************Support Clock Settings**********************************Setting SYNC ASYNC----------------------------------667_133_66 X O533_133_66 O O400_133_66 X O400_100_50 O O**********************************/提高主频//===========================================更改部分===================== #define CONFIG_CLK_667_133_66//#define CONFIG_CLK_533_133_66//========================================================================= /*#define CONFIG_CLK_400_100_50#define CONFIG_CLK_400_133_66#define CONFIG_SYNC_MODE*//* SMDK6400 has 2 banks of DRAM, but we use only one in U-Boot */#define CONFIG_NR_DRAM_BANKS 1#define PHYS_SDRAM_1 CONFIG_SYS_SDRAM_BASE /* SDRAM Bank #1 */#define PHYS_SDRAM_1_SIZE 0x08000000 /* 128 MB in Bank #1 */#define CONFIG_SYS_FLASH_BASE 0x10000000#define CONFIG_SYS_MONITOR_BASE 0x00000000/*-----------------------------------------------------------------------* FLASH and environment organization*/#define CONFIG_SYS_MAX_FLASH_BANKS 1 /* max number of memory banks *//* AM29LV160B has 35 sectors, AM29LV800B - 19 */#define CONFIG_SYS_MAX_FLASH_SECT 40#define CONFIG_AMD_LV800//===================================更改部分=========================//#define CONFIG_SYS_FLASH_CFI 1 /* Use CFI parameters (needed?) */将上面的换成下面红色的部分#define CONFIG_SYS_NO_FLASH 1 /* Use CFI parameters (needed?) *///=================================================================//=========================更改部分===================================删掉下面黄色的#if 0/* Use drivers/cfi_flash.c, even though the flash is not CFI-compliant */#define CONFIG_FLASH_CFI_DRIVER 1#define CONFIG_SYS_FLASH_CFI_WIDTH FLASH_CFI_16BIT#define CONFIG_FLASH_CFI_LEGACY#define CONFIG_SYS_FLASH_LEGACY_512Kx16/* timeout values are in ticks */#define CONFIG_SYS_FLASH_ERASE_TOUT (5 * CONFIG_SYS_HZ) /* Timeout for Flash Erase */ #define CONFIG_SYS_FLASH_WRITE_TOUT (5 * CONFIG_SYS_HZ) /* Timeout for Flash Write */ #endif//============================================================================= ==========#define CONFIG_ENV_SIZE 0x4000 /* Total Size of Environment Sector *//** SMDK6400 board specific data*///=========================================更改部分============================ //#define CONFIG_IDENT_STRING " for SMDK6400"将上面的改为下面的#define CONFIG_IDENT_STRING " for TINY6410"//============================================================================= ====/* base address for uboot */#define CONFIG_SYS_PHY_UBOOT_BASE (CONFIG_SYS_SDRAM_BASE + 0x07e00000)/* total memory available to uboot */#define CONFIG_SYS_UBOOT_SIZE (1024 * 1024)十三:修改include/common.hulong get_OPB_freq (void);ulong get_PCI_freq (void);#endif/*======================================更改部分============================*/ #if defined(CONFIG_S3C24X0) || \defined(CONFIG_LH7A40X) || \defined(CONFIG_S3C6400) || \defined(CONFIG_S3C6410) || \ 添加红色的defined(CONFIG_EP93XX)/*============================================================================= */ulong get_FCLK (void);ulong get_HCLK (void);ulong get_PCLK (void);ulong get_UCLK (void);#endif十四:修改顶层的MAKEALL########################################################################### ARM11 Systems#########################################################################LIST_ARM11=" \cp1136 \omap2420h4 \apollon \imx31_litekit \imx31_phycore \imx31_phycore_eet \mx31ads \mx31pdk \mx31pdk_nand \qong \smdk6400 \tnetv107x_evm \添加下面红色的部分/*=======================================更改部分============================*/ tiny6410 \/*===========================================================================*/ "#########################################################################十五:修改顶层的MAINTAINERS修改下面的为自己的Alex Z黳ke <azu@sysgo.de>lart SA1100dnp1110 SA1110/*==================================更改部分=============================*/ Wnn168<wnn168@>TINT6410 ARM1176JZF-S (S3C6410)/*========================================================================*/-------------------------------------------------------------------------Unknown / orphaned boards:十六:修改nand_spl/board/samsung/ tiny6410/config.mk下面的这个没有改动# FriendlyARM TINY6410 development board,based on# Samsung S3C64xx Reference Platform (smdk6400) board# TEXT_BASE for SPL:## On S3C64xx platforms the SPL is located in SRAM at 0.## TEXT_BASE = 0include $(TOPDIR)/board/$(BOARDDIR)/config.mk# PAD_TO used to generate a 4kByte binary needed for the combined image# -> PAD_TO = TEXT_BASE + 4096PAD_TO := $(shell expr $(TEXT_BASE) + 4096)ifeq ($(debug),1)PLATFORM_CPPFLAGS += -DDEBUGEndif十七:在nand_sql/board/Samsung/tiny6410 这个tiny6410是仿照上述smdk6410做的内容一样复制然后修改下面的就OKNand_sql/board/Samsung/tiny6410/Makefile# from board directory#=========================更改部分=================================== $(obj)lowlevel_init.S:@rm -f $@# @ln -s $(TOPDIR)/board/samsung/smdk6400/lowlevel_init.S $@@ln -s $(TOPDIR)/board/samsung/tiny6410/lowlevel_init.S $@#=================================================================# from nand_spl directory。

tiny6410内核移植

Tiny6410 的内核移植(拿来主义)一、开发环境宿主机: vista+VMware+ fedoral13(win7下虚拟机)编译器: 友善自带arm-linux-gcc-4.5.1-v6-vfp-20101103.tgz开发板: tiny6410,核心板号1106 NAND 2G RAM 256M注意:移植内核时,确保引导文件为u-boot类型,否则到后面下载到开发板使会出现乱码以及不必要的错误二、移植nand_flash1 下载linux-2.6.38的源码ftp:///pub/linux/kernel/v2.6/linux-2.6.38.tar.bz22 解压#tar xvfj /mnt/ubuntu/linux-2.6.38.tar.bz2 -C .3 修改根下的Makefile#vi Makefile191行改为ARCH ?= armCROSS_COMPILE ?= arm-linux- (找到其交叉编译环境)4 生成默认配置文件#cp arch/arm/configs/s3c6400_defconfig .config(如果省略的话,后面会找不到System Type)5 修改配置项(基本配置)#make menuconfigGeneral setup->(/usr/4.5.1/bin/arm-linux-) Cross-compiler tool prefix 我将编译器解压到了/opt/Friendly/toolschain/4.5.1/bin目录(如果第三步中以修改“plier ? = arm-linux- ”此项,这步可以不作)System Type->[*] MINI6410 选上,其他的可以去掉,不确定的可以参考友善之臂的(这样编译出来的内核是可以被uboot引导的,然后是增加nand flash支持)vi arch/arm/mach-s3c64xx/mach-mini6410.c第117行struct mtd_partition mini6410_nand_part[] = {{.name = "Bootloader",.offset = 0,.size = (4 * 128 *SZ_1K),.mask_flags = MTD_CAP_NANDFLASH,},{.name = "Kernel",.offset = (4 * 128 *SZ_1K),.size = (5*SZ_1M) ,.mask_flags = MTD_CAP_NANDFLASH,},{.name = "File System",.offset = MTDPART_OFS_APPEND,.size = MTDPART_SIZ_FULL,}}; //update at 2011-8-26 经过测试发现,这里改完后根本不起作用,甚至将整个注释也无妨,估计分区已经固死在后面的s3c_nand_mlc.fo 中6 拷贝NAND FLASH驱动(将6410内核中的如下文件拷到相应的目录下)需拷贝文件:drivers/mtd/nand/s3c_nand.carch/arm/plat-samsung/include/plat/regs-nand.h 覆盖掉drivers/mtd/nand/s3c_nand_mlc.fo《s3c_nand_mlc.fo友善没有开源的一个驱动之一,所以不用研究了,拷过来就是了。

opencv移植到arm详细过程

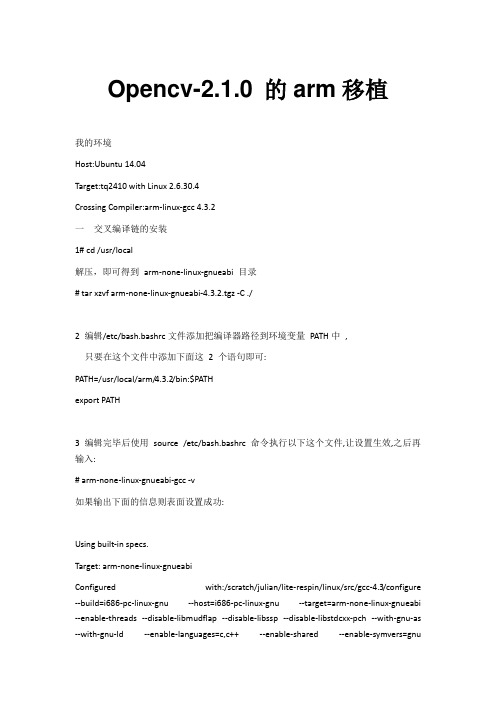

Opencv-2.1.0 的arm移植我的环境Host:Ubuntu 14.04Target:tq2410 with Linux 2.6.30.4Crossing Compiler:arm-linux-gcc 4.3.2一交叉编译链的安装1# cd /usr/local解压,即可得到arm-none-linux-gnueabi 目录# tar xzvf arm-none-linux-gnueabi-4.3.2.tgz -C ./2 编辑/etc/bash.bashrc文件添加把编译器路径到环境变量PA TH中,只要在这个文件中添加下面这2 个语句即可:PATH=/usr/local/arm/4.3.2/bin:$PA THexport PA TH3 编辑完毕后使用source /etc/bash.bashrc 命令执行以下这个文件,让设置生效,之后再输入:# arm-none-linux-gnueabi-gcc -v如果输出下面的信息则表面设置成功:Using built-in specs.Target: arm-none-linux-gnueabiConfigured with:/scratch/julian/lite-respin/linux/src/gcc-4.3/configure --build=i686-pc-linux-gnu --host=i686-pc-linux-gnu --target=arm-none-linux-gnueabi --enable-threads --disable-libmudflap --disable-libssp --disable-libstdcxx-pch --with-gnu-as --with-gnu-ld --enable-languages=c,c++ --enable-shared --enable-symvers=gnu--enable-__cxa_atexit --with-pkgversion='Sourcery G++ Lite 2008q3-72' --with-bugurl=https:///GNUToolchain/--disable-nls--prefix=/opt/codesourcery--with-sysroot=/opt/codesourcery/arm-none-linux-gnu eabi/libc--with-build-sysroot=/scratch/julian/lite-respin/linux/install/arm-none-linux-gnueabi/libc--with-gmp=/scratch/julian/lite-respin/linux/obj/host-libs-2008q3-72-arm-none-linux-gnueabi-i686-p c-linux-gnu/usr--with-mpfr=/scratch/julian/lite-respin/linux/obj/host-libs-2008q3-72-arm-non e-linux-gnueabi-i686-pc-linux-gnu/usr--disable-libgomp--enable-poison-system-directories--with-build-time-tools=/scratch/julian/lit e-respin/linux/install/arm-none-linux-gnueabi/ bin --with-build-time-tools=/scratch/julian/lite-respin/linux/install/arm-none-linux-gnueabi/bin Thread model: posixgcc version 4.3.2 (Sourcery G++ Lite 2008q3-72)但是,此时会报错:bash:/usr/local/arm/4.3.2/bin/arm-none-linux-gnueabi-gcc:没有那个文件或目录这是因为是为62位机与32位不兼容,在64位ubuntu系统上运行32位程序需要安装32位lib网上很多地方说用#sudo apt-get install ia32-libs可解决,但是我执行之后却显示:# sudo apt-get install ia32-libs正在读取软件包列表... 完成正在分析软件包的依赖关系树正在读取状态信息... 完成正在读取软件包列表... 完成正在分析软件包的依赖关系树正在读取状态信息... 完成现在没有可用的软件包ia32-libs,但是它被其它的软件包引用了。

linux下安装opencv

Opencv版本:2.4.4二、安装步骤:1、解压缩OpenCV-2.4.4a.tar.bz2安装包:tar jxvf OpenCV-2.4.4a.tar.bz2cd opencv-2.4.42、用cmake进行编译:mkdir release244 //目录名可以任意命名cd release244cmake -D CMAKE_BUILD_TYPE=RELEASE -DCMAKE_INSTALL_PREFIX=/public/software/opencv244-D BUILD_PYTHON_SUPPORT=ON ..//注意-D CMAKE_INSTALL_PREFIX表示安装目录,我这里选为/public/software/opencv2443、编译和安装上面的步骤执行成功后再执行:makemake install即可完成编译和安装三、安装后的配置1、准备环境变量文件:vi /etc/profile.d/opencv-env.shexport LD_LIBRARY_PATH=/public/software/opencv244/lib:$LD_LIB RARY_PATHexport INCLUDE=/public/software/opencv244/include/opencv:/publi c/software/opencv244/include/opencv2:$INCLUDEexport PKG_CONFIG_PATH=/public/software/opencv244/lib/pkgconf ig//这个文件是根据之前的安装目录写的,PKG_CONFIG_PATH这个必须写,其他两个貌似也可以不写2、载入环境变量:. /etc/profile.d/opencv-env.sh四、算例演示1、准备算例:cat myopencv.cpp#include "highgui.h"int main( int argc, char** argv )IplImage* img = cvLoadImage( argv[1] ); cvNamedWindow( "Example1", CV_WINDOW_AUTOSIZE ); cvShowImage( "Example1", img );cvWaitKey(0);cvReleaseImage( &img );cvDestroyWindow( "Example1" );}2、编译g++ `pkg-config opencv --libs --cflags opencv` myopencv.cpp -o myopencv编译成功后会生成可执行文件myopencv3、运行向此目录下上传一张图片,比如我这里是Lena.jpg执行:./myopencv Lena.jpg便可弹出图片。

opencv2.4.0+win7+64+vs2010配置教程

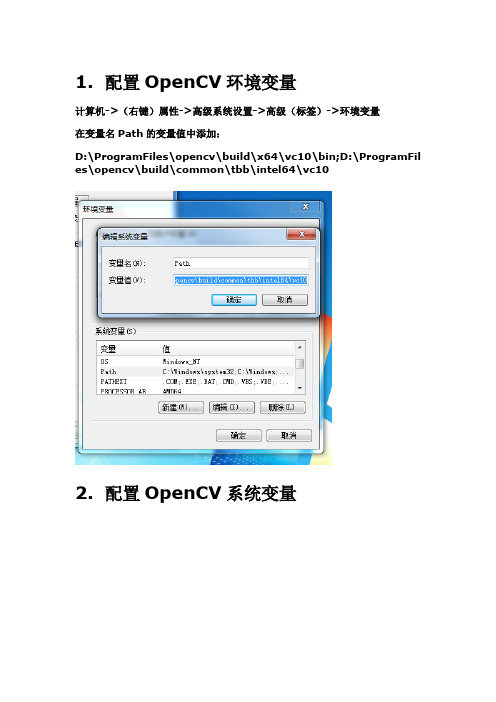

1.配置OpenCV环境变量计算机->(右键)属性->高级系统设置->高级(标签)->环境变量在变量名Path的变量值中添加:D:\ProgramFiles\opencv\build\x64\vc10\bin;D:\ProgramFil es\opencv\build\common\tbb\intel64\vc102.配置OpenCV系统变量在用户变量中新建OPENCV,添加变量值D:\Program Files\opencv\build3.配置工程的opencv依赖1)项目(菜单项)->…属性->VC++目录:需要配置“包含目录”和“库目录”两项。

2)、配置“包含目录”项3)配置“库目录”项:4)、配置连接器:项目(菜单项)->…属性->连接器->输入->附加依赖项针对debug配置添加以下库:opencv_calib3d240d.libopencv_contrib240d.libopencv_core240d.libopencv_features2d240d.libopencv_flann240d.libopencv_gpu240d.libopencv_highgui240d.libopencv_imgproc240d.libopencv_legacy240d.libopencv_ml240d.libopencv_objdetect240d.libopencv_ts240d.libopencv_video240d.lib如果是release配置(以后再说,只需要添加上面的debug配置就行了现在),则添加:opencv_calib3d240.libopencv_contrib240.libopencv_core240.libopencv_features2d240.libopencv_flann240.libopencv_gpu240.libopencv_highgui240.libopencv_imgproc240.libopencv_legacy240.libopencv_ml240.libopencv_objdetect240.libopencv_ts240.libopencv_video240.lib1)、文件->新建->项目->Visual C++->Win32 控制台应用程序(输入名称test)2)、确定->下一步->附加选项选“空项目”->完成3)、解决方案资源管理器->源文件(右键)->添加->新建项4)、Visual C++->C++文件:输入名称test点添加5)、粘贴下面的代码,保存1 #include <opencv2\opencv.hpp>2 #include <iostream>3 #include <string>4using namespace cv;5using namespace std;6int main()7 {8 Mat img = imread("pp.jpg");9if(img.empty())10 {11 cout<<"error";12return -1;13 }14 imshow("xx的靓照",img);15 waitKey();1617return0;18 }6)、把自己的靓照改名为pp.jpg,然后放到工程项目的test文件夹里面(是里面那个test 文件夹)7)、按照第3步骤的方法配置工程的opencv依赖。

linux +qt4.7+opencv2.2移植到tq2440开发板

linux +qt4.7+opencv2.2移植到tq2440开发板以下操作在Fedora下使用超级用户进行我已经安装了交叉编译器arm-linux-gcc 4.3.3和qt4.5的x86和arm版本在目录/opt/EmbedSky下。

修改配置文件/etc/profile 添加pathmunge /opt/EmbedSky/4.3.3/bin安装CMakeOpenCV 2.1的版本,必须使用CMake创建Makefile。

我使用的CMake版本是2.6-Linux-i386的,是fedora 通过软件添加和载卸功能添加的(这个cmake要重新安装,而且要添加bin进去路径)编译OpenCV:1、解压OpenCV 2.1到/opt/EmbedSky/OpenCV-2.1.0目录下2、在超级用户下,运行cmake-gui命令选择源代码目录:/opt/EmbedSky/OpenCV-2.1.0选择Build目录:/home/pww71/opencv-arm/点击Configure,保持generator为Unix Makefiles,选择Specify options for cross-compiling,点击Next Operating System填写arm-inuxC Compilers选择/opt/EmbedSky/4.3.3/bin/arm-linux-gccC++ Compilers选择/opt/EmbedSky/4.3.3/bin/arm-linux-g++程序库的Target Root填写/opt/EmbedSky/4.3.3/,然后点击Finish修改默认配置,X86-opencv的cmake配置添加BUILD_EXAMPLES 和OPENCV_BUILD_3RDPARTY_LIBS 前面的日志已经介绍过了arm-opencv的cmake配置不要加BUILD_EXAMPLES 和OPENCV_BUILD_3RDPARTY_LIBS 和去掉WITH_TIFFCMAKE_EXE_LINKER_FLAGS原来为空,加上-lpthread -lrtx86的opencv默认安装目录为/usr/local,对于arm的交叉编译的库来说并不合适,所以把CMAKE_INSTALL_PREFIX变量改为/usr/local/arm/lib/opencv/没有安装tiff图像的支持,去掉WITH_TIFF点击Generate生成Makefile3、使用超级用户进入目录/home/pww71/opencv-arm,运行make编译opencv4、运行make install,将opencv生成的库和头文件安装到目录/usr/local/arm/lib/opencv/QT的配置已经解压和安装了qt4.5的x86的库和arm交叉交叉编译的库安装qtcreator时记得安装地址并且修改配置文件/etc/profile 添加上qtcreator的安装地址的bin目录我的是pathmunge pathmunge /opt/EmbedSky/qtcreator-1.3.0/bin为了能找到qmake 还要添加路径pathmunge /opt/EmbedSky/qt-4.5/_install/x86/binpathmunge /opt/EmbedSky/qt-4.5/_install/am/bin到配置文件/etc/profile中使用超级用户输入命令source /etc/profile 后再执行qtcreator命令打开Qtcreator界面进入Tools-Options左侧选择QT4-Qt Versions 右侧选项里:如果通过软件添加和载卸工具添加了qt4的话Auto-detected会自动的选择Qt in PATH /usr/local/bin/qmake-qt4 用这个qmake工具生成的可执行文件不用添加-qws命令行参数自己安装的qt4.5 我是如下配置Qt in PATH /opt/EmbedSky/qt-4.5/_install/arm/bin/qmake添加Manual x86-qt-4.5.0 /opt/EmbedSky/qt-4.5/_install/x86/bin/qmake生成的可执行文件需要添加-qws命令行参数分别点击rebuild 最后点击okBuild Settings 中根据需要Add刚才配置的选择BUild configuration for ... 也选择相应的选项在QT工程文件.Pro中添加以下内容INCLUDEPATH += /usr/local/include/opencvLIBS += /usr/local/lib/libcv.so \/usr/local/lib/libcvaux.so \/usr/local/lib/libcxcore.so \/usr/local/lib/libhighgui.so \/usr/local/lib/libml.sopc仿真必须将以上库还要添加到项目文件夹里如果是arm开发板的程序则添加以下内容INCLUDEPATH += /usr/local/arm/lib/opencv/include/opencvLIBS += /usr/local/arm/lib/opencv/lib/libcv.so \/usr/local/arm/lib/opencv/lib/libcvaux.so \/usr/local/arm/lib/opencv/lib/libcxcore.so \/usr/local/arm/lib/opencv/lib/libhighgui.so \/usr/local/arm/lib/opencv/lib/libml.so编译生成可执行文件移植到开发板提示缺少什么库就按提示添加相应的图像库到lib中以及qt4.5的库和字体都添加到相应的目录中中间有一个这个提示QWSDisplay::Data::init: Invalid argumentClient can't attach to main ram memory.Aborted这个是表示缺少命令行参数-qws是Qt4的问题运行命令添加该参数ok一切正常注意的是qtcreator。

6410裸机LCD独立完整程序Tiny6410亲测可用

工具是RVDS2.2 开发板是Tiny6410,本人亲测可用的。

启动文件,和主函数可以自己写,关键是mlcd.c文件!启动文件中的s3c6410.inc image_cfg.inc 和MemParam_mDDR.inc 比较大放在了最后面。

请自建一人main.c 文件,并在Extern LCD_Init();Extern LCD_DrewPixel(int x,int y,int color);void main(){ LCD_Init(); LCD_DrawPixel(100,100, 0x00);}就可以打一个点了。

源程序来自网络!/**************************************************************************************启动文件strartup.s 跳到void mian函数****************************** ***********/INCLUDE s3c6410.incINCLUDE image_cfg.incINCLUDE MemParam_mDDR.incIMPORT main ; C entrypoint for Steppingstone loader.; AREA |.astart|,ALIGN=2,CODE;AreaName SETS "|.astart|";------------------------------------------------------------------------------;; Memory Start Entry;; 内存里直接启动时入口;;------------------------------------------------------------------------------PRESERVE8AREA |C$$code|, CODE, READONL Yglobal MemStartMemStart;------------------------------------; Disable WatchDog Timer;------------------------------------ldr r0, =WTCONldr r1, =0x0str r1, [r0];------------------------------------; Enable VIC Port @Andrew Huang;------------------------------------mrc p15,0,r0,c1,c0,0orr r0,r0,#(1<<24)mcr p15,0,r0,c1,c0,0b mainDCB "ABCDabcd"; END/****************************************************************************** ******mlcd.c 文件********调用LCD_Init();就可完成初始化,调用LCD_DrawPixel就可以在自定义的x,y 打一个color 颜色的点************///mlcd.c文件#include "s3c6410_addr.h"#include "utils.h"#include "mlcd.h"#define LCD_YSIZE (272)#define LCD_XSIZE (480)#ifdef LCDvolatile unsigned int LCD_BUFFER[272][480];unsigned int addr = (unsigned int)LCD_BUFFER;void LCD_DrawPixel(unsigned int x, unsigned int y, unsigned int color){if((x<480) && (y<272))LCD_BUFFER[y][x] = color;}void LCD_Init(void){//(1)将J管脚的第二功能设为LCD VD、HSYNC 、VSYNC 、VDEN 、VCLK,将I管脚的第二功能设为LCD VD//init gpio func for LCD +rGPECON = 0x00011111; //GPE0: for LCD Backlight ON-OFF. GPE1~4 is GPIO.rGPEDAT = 0x00000001; //Backlight ON (some LCD(3.5) need it ,but NEC 4.3 not) rGPEPUD = 0x00000000;//gpio->GPECONSLP = 0x00000000;//gpio->GPEPUDSLP = 0x00000000;rGPFCON = 0x96AAAAAA; //PWM1: for Backlight Dimming. GPF13 is USB_PWR. GPF0~12 is CAM I/F.// PWM0 Control Buzzer,but now we config it as OUTPUT!!!rGPFDAT = 0x00002000; //USB_PWR ON . Buzzer OFF .rGPFPUD = 0x00000000;//gpio->GPFCONSLP = 0x00000000;//gpio->GPFPUDSLP = 0x00000000;rGPICON = 0xAAAAAAAA;rGPIPUD = 0x00000000;//gpio->GPICONSLP = 0x00000000;//gpio->GPIPUDSLP = 0x00000000;rGPJCON = 0x00AAAAAA;rGPJPUD = 0x00000000;//gpio->GPJCONSLP = 0x00000000;//gpio->GPJPUDSLP = 0x00000000;//init gpio func for LCD -//LCDrSPCON = rSPCON & ~(0x3) | 1;rMIFPCON &= ~(1<<3);rVIDCON0 = (0<<29)|(0<<26)|(0<<17)|(0<<16)|(9<<6)|(0<<5)|(1<<4)|(0<<2);//(0<<29)|(0<<26)|(0<<17)|(1<<16)|(5<<6)|(0<<5)|(1<<4)|(0<<2);rVIDCON1 = 1<<7;//1=RGB 类型LCD 设备在VCLK 上升沿得到视频数据//+设置屏的时序rVIDTCON0 = (0x03<<16)|(0x02<<8)|(0x02<<0);rVIDTCON1 = (0x2d<<16)|(0x04<<8)|(0x06<<0);rVIDTCON2 = (271<<11)|(479<<0);//-rWINCON0 = 11<<2;//窗口格式控制11 24显示8 16位//+VIDOSDxA ,VIDOSDxB:窗口位置控制rVIDOSD0A = (0<<11)|(0);rVIDOSD0B = (479<<11)|(271<<0);rVIDOSD0C = (((480*272)&0xFFFFFF)<<0);//-rVIDW00ADD0B0 = ((addr>>24)<<24)|(addr&0xffffff);rVIDW00ADD1B0 = (addr&0xffffff + 480*272);rVIDW00ADD2 = (0<<13)|(480);rDITHMODE=(1<<5)|(1<<3)|(1<<1);//+开显示rVIDCON0 |= 3;rWINCON0 |= 1;//-}//*****************************************//s3c6410.inc文件//******************************************;; Copyright (c) Microsoft Corporation. All rights reserved.;;; Use of this source code is subject to the terms of the Microsoft end-user; license agreement (EULA) under which you licensed this SOFTWARE PRODUCT. ; If you did not accept the terms of the EULA, you are not authorized to use; this source code. For a copy of the EULA, please see the LICENSE.RTF on your ; install media.;;-------------------------------------------------------------------------------;; Header: s3c6410.inc;; This header only those registers required by the startup; code. All addresses are based off the physical addresses (PA) defined; in s3c6410_base_reg.h (s3c6410_base_reg.inc).;;-------------------------------------------------------------------------------;-------------------------------------------------; CPU Revision Definition ( S3C6410 Has EVT0, EVT1;-------------------------------------------------EVT0 EQU (36410100)EVT1 EQU (36410101);-------------------------------------------------; System Clock Definition;-------------------------------------------------CLK_66_5MHZ EQU 66500000CLK_133MHZ EQU 133000000CLK_150MHZ EQU 150000000CLK_200MHZ EQU 200000000CLK_266MHZ EQU 266000000CLK_300MHZ EQU 300000000CLK_400MHZ EQU 400000000CLK_450MHZ EQU 450000000CLK_532MHZ EQU 532000000CLK_600MHZ EQU 600000000CLK_666MHZ EQU 666000000 ; SyncCLK_667MHZ EQU 667000000 ; ASyncCLK_798MHZ EQU 798000000 ; SyncCLK_800MHZ EQU 800000000 ; ASyncCLK_900MHZ EQU 900000000CLK_1332MHZ EQU 1332000000ECLK_96MHZ EQU 96000000ECLK_84MHZ EQU 84666667 ; for IIS 44.1 KHzECLK_92MHZ EQU 92160000 ; for IIS 48 KHzGBLA CPU_REVISIONGBLA TARGET_ARM_CLKGBLA S3C6410_ECLKGBLL CHANGE_PLL_CLKDIV_ON_EBOOTGBLL CHANGE_PLL_CLKDIV_ON_KERNELGBLL CLEAR_DRAM_ON_EBOOTGBLL CLEAR_DRAM_ON_KERNELCHANGE_PLL_CLKDIV_ON_EBOOT SETL {TRUE}CHANGE_PLL_CLKDIV_ON_KERNEL SETL {TRUE}CLEAR_DRAM_ON_EBOOT SETL {FALSE}CLEAR_DRAM_ON_KERNEL SETL {FALSE};------------------------------------------------------------------------------; Define: SYNCMODE;; SYNCMODE used to set cpu operation mode to syncronous mode or asyncronous mode ;------------------------------------------------------------------------------GBLL SYNCMODESYNCMODE SETL {TRUE};-------------------------------------------------; Change CPU Revision (S3C6410 HAS EVT0, EVT1);-------------------------------------------------CPU_REVISION SETA EVT1;-------------------------------------------------;-------------------------------------------------; Change TARGET_ARM_CLK definition for StartUp code;-------------------------------------------------;TARGET_ARM_CLK SETA CLK_66_5MHZ ; Sync 66.5:66.5:66.5 ;TARGET_ARM_CLK SETA CLK_133MHZ ; Sync 133:133:66.5;TARGET_ARM_CLK SETA CLK_266MHZ ; Sync 266:133:66.5;TARGET_ARM_CLK SETA CLK_400MHZ ; Sync 400:100:50;TARGET_ARM_CLK SETA CLK_450MHZ ; Sync 450:150:65 TARGET_ARM_CLK SETA CLK_532MHZ ; Sync 532:133:66.5;TARGET_ARM_CLK SETA CLK_600MHZ ; Sync 600:150:75;TARGET_ARM_CLK SETA CLK_666MHZ ; Sync 666:133.4:66.5 ;TARGET_ARM_CLK SETA CLK_798MHZ ; Sync 798:133:66.5;TARGET_ARM_CLK SETA CLK_800MHZ ; Sync 800:133.33:66.66 ;TARGET_ARM_CLK SETA CLK_900MHZ ; Sync 900:150:75FIN EQU 12000000;-------------------------------------------------; Include the base register definitions; Fout = MDIV*Fin/(PDIV*2^SDIV); Fvco = MDIV*Fin/PDIVINCLUDE s3c6410_base_regs.inc;-------------------------------------------------; Change S3C6410_ECLK definition for EPLL Fout;-------------------------------------------------;S3C6410_ECLK SETA ECLK_96MHZS3C6410_ECLK SETA ECLK_84MHZ;S3C6410_ECLK SETA ECLK_92MHZ;-------------------------------------------------;-------------------------------------------------; Set Clock Source : MPLL, APLL;-------------------------------------------------; MPLL Setting; 400:100:25 (Asyncronous Mode)[ (TARGET_ARM_CLK = CLK_400MHZ);Fvco=800MHz, Fout=200MHzMPLL_MV AL EQU (400)MPLL_PV AL EQU (6)MPLL_SVAL EQU (2)|; Other Clock use 266Mhz for mDDR in Asynchronous mode;Fvco=1064MHz, Fout=266MHzMPLL_PV AL EQU (3)MPLL_SVAL EQU (2)]MPLL_CLK EQU (((FIN>>MPLL_SVAL)/MPLL_PVAL)*MPLL_MV AL) ; MPLL Clock; APLL Setting[ (TARGET_ARM_CLK = CLK_400MHZ);Fvco=800MHz, Fout=400MHzAPLL_MV AL EQU (400)APLL_PV AL EQU (6)APLL_SV AL EQU (1)][ (TARGET_ARM_CLK = CLK_532MHZ):LOR:(TARGET_ARM_CLK = CLK_266MHZ):LOR:(TARGET_ARM_CLK = CLK_133MHZ):LOR:(TARGET_ARM_CLK = CLK_66_5MHZ);Fvco=1064MHz, Fout=532MHzAPLL_MV AL EQU (266)APLL_PV AL EQU (3)APLL_SV AL EQU (1)][ (TARGET_ARM_CLK = CLK_600MHZ):LAND:(SYNCMODE);Fvco=1200MHz, Fout=600MHzAPLL_MV AL EQU (300)APLL_PV AL EQU (3)APLL_SV AL EQU (1)][ (TARGET_ARM_CLK = CLK_666MHZ)[ (SYNCMODE):LAND:(CPU_REVISION = EVT1);Fvco=1332MHz, Fout=1332MHzAPLL_MV AL EQU (333)APLL_PV AL EQU (3)APLL_SV AL EQU (0)|;Fvco=1332MHz, Fout=666MHzAPLL_MV AL EQU (333)APLL_PV AL EQU (3)APLL_SV AL EQU (1)]][ (TARGET_ARM_CLK = CLK_798MHZ):LAND:(SYNCMODE);Fvco=1596MHz, Fout=798MHzAPLL_PV AL EQU (3)APLL_SV AL EQU (1)][ (TARGET_ARM_CLK = CLK_800MHZ);Fvco=1600MHz, Fout=800MHzAPLL_MV AL EQU (400)APLL_PV AL EQU (3)APLL_SV AL EQU (1)][ ((TARGET_ARM_CLK = CLK_900MHZ):LAND:(SYNCMODE)):LOR:(TARGET_ARM_CLK = CLK_450MHZ);Fvco=900MHz, Fout=900MHzAPLL_MV AL EQU (225)APLL_PV AL EQU (3)APLL_SV AL EQU (0)]APLL_CLK EQU (((FIN>>APLL_SVAL)/APLL_PV AL)*APLL_MV AL) ; APLL Clock;-------------------------------------------------; Set Clock Dividers;-------------------------------------------------MPLL_DIV EQU (2-1) ; DOUT_MPLL = MPLL_Fout/2[ (TARGET_ARM_CLK = CLK_450MHZ):LOR:(TARGET_ARM_CLK = CLK_666MHZ):LOR:(TARGET_ARM_CLK = CLK_266MHZ)APLL_DIV EQU (2-1) ; ARM_CLK = APLL_CLK/2|[ (TARGET_ARM_CLK = CLK_133MHZ)APLL_DIV EQU (4-1) ; ARM_CLK = APLL_CLK/4|[ (TARGET_ARM_CLK = CLK_66_5MHZ)APLL_DIV EQU (8-1) ; ARM_CLK = APLL_CLK/8|APLL_DIV EQU (1-1) ; ARM_CLK = APLL_CLK]]]HCLK_DIV EQU (2-1) ; AHB_CLK = HCLKx2/2[ (TARGET_ARM_CLK = CLK_66_5MHZ)PCLK_DIV EQU (2-1) ; PCLK = HCLKx2/2|PCLK_DIV EQU (4-1) ; PCLK = HCLKx2/4][ (SYNCMODE) ; Use APLL as Memory Clock Source[ (TARGET_ARM_CLK = CLK_532MHZ):LOR:(TARGET_ARM_CLK = CLK_600MHZ):LOR:(TARGET_ARM_CLK = CLK_266MHZ):LOR:(TARGET_ARM_CLK = CLK_133MHZ); ARM:AHB:APB = 4:2:1, HCLKx2 = APLL_CLK/2HCLKx2_DIV EQU (2-1) ; HCLKx2 = APLL_CLK/2][ (TARGET_ARM_CLK = CLK_666MHZ):LAND:(CPU_REVISION = EVT1) ; This setting requires enabling MISC_CON[19]HCLKx2_DIV EQU (5-1) ; HCLKx2 = APLL_CLK/5 = 266.4MHz(Hard wired-PreDivider on EVT1)][ (TARGET_ARM_CLK = CLK_798MHZ):LOR:(TARGET_ARM_CLK = CLK_900MHZ):LOR:(TARGET_ARM_CLK = CLK_450MHZ):LOR:(TARGET_ARM_CLK = CLK_800MHZ); ARM:AHB:APB = 12:2:1, HCLKx2 = APLL_CLK/3HCLKx2_DIV EQU (3-1) ; HCLKx2 = APLL_CLK/3][ (TARGET_ARM_CLK = CLK_66_5MHZ)HCLKx2_DIV EQU (4-1) ; HCLKx2 = APLL_CLK/4]| ; Use MPLL as Memory Clock Source[ (TARGET_ARM_CLK = CLK_400MHZ):LOR:(TARGET_ARM_CLK = CLK_532MHZ):LOR:(TARGET_ARM_CLK = CLK_666MHZ); ARM:AHB:APB = 4:(2:1), HCLKx2 = MPLLHCLKx2_DIV EQU (1-1) ; HCLKx2 = MPLL_CLK]] ; (SYNCMODE)ARM_CLK EQU (APLL_CLK/(APLL_DIV+1))[ (SYNCMODE)HCLK EQU (APLL_CLK/(HCLKx2_DIV+1)/(HCLK_DIV+1))|HCLK EQU (MPLL_CLK/(HCLKx2_DIV+1)/(HCLK_DIV+1))]; EPLL Fout 96 MHz[ S3C6410_ECLK = ECLK_96MHZ;Fout=96MHzEPLL_MV AL EQU (32)EPLL_PVAL EQU (1)EPLL_SVAL EQU (2)EPLL_KVAL EQU (0)] ; 96 MHz; EPLL Fout 84.666667 MHz[ S3C6410_ECLK = ECLK_84MHZ;Fout=84.67MHzEPLL_MV AL EQU (254) EPLL_PVAL EQU (9)EPLL_SVAL EQU (2)EPLL_KVAL EQU (0)] ; 84.666667 MHz; EPLL Fout 92,160,000 Hz[ S3C6410_ECLK = ECLK_92MHZ;Fout=92.16MHzEPLL_MV AL EQU (192) EPLL_PVAL EQU (25)EPLL_SVAL EQU (0)EPLL_KVAL EQU (0)] ; 92.16 MHz;---------------------------; CPSR Mode Bit Definition;---------------------------Mode_USR EQU (0x10)Mode_FIQ EQU (0x11)Mode_IRQ EQU (0x12)Mode_SVC EQU (0x13)Mode_ABT EQU (0x17)Mode_UND EQU (0x1B) Mode_SYS EQU (0x1F)Mode_MASK EQU (0x1F) NOINT EQU (0xC0)I_Bit EQU (0x80)F_Bit EQU (0x40);---------------------------; CP15 Mode Bit Definition;---------------------------R1_iA EQU (1<<31)R1_nF EQU (1<<30)R1_VE EQU (1<<24)R1_I EQU (1<<12)R1_BP EQU (1<<11) ; Z bitR1_C EQU (1<<2)R1_A EQU (1<<1)R1_M EQU (1<<0);---------------------------; Miscellaneous defines;---------------------------WORD_SIZE EQU (4)DW8 EQU (0x0)DW16 EQU (0x1)DW32 EQU (0x2)WAIT EQU (0x1<<2)UBLB EQU (0x1<<3);---------------------------;; SFR Address;;---------------------------;---------------------------; SysCon;---------------------------APLL_LOCK EQU (0x7e00f000) MPLL_LOCK EQU (0x7e00f004) APLL_CON EQU (0x7e00f00c) MPLL_CON EQU (0x7e00f010) EPLL_CON0 EQU (0x7e00f014) EPLL_CON1 EQU (0x7e00f018) CLK_SRC EQU (0x7e00f01c) CLK_DIV0 EQU (0x7e00f020)CLK_OUT EQU (0x7e00f02c)MEM_SYS_CFG EQU (0x7e00f120)OTHERS EQU (0x7e00f900)RST_STAT EQU (0x7E00F904)INFORM0 EQU (0x7E00FA00)INFORM1 EQU (0x7E00FA04)INFORM2 EQU (0x7E00FA08)INFORM3 EQU (0x7E00FA0C)vPWR_CFG EQU (0xB2A0F804)vSLEEP_CFG EQU (0xB2A0F818)vOSC_STABLE EQU (0xB2A0F824)vPWR_STABLE EQU (0xB2A0F828)vRST_STAT EQU (0xB2A0F904)vINFORM0 EQU (0xB2A0FA00)vINFORM1 EQU (0xB2A0FA04)vINFORM2 EQU (0xB2A0FA08)vINFORM3 EQU (0xB2A0FA0C);---------------------------; GPIO;---------------------------GPACON EQU (S3C6410_BASE_REG_PA_GPIO + 0x000);GPHCON0 EQU (S3C6410_BASE_REG_PA_IOPORT + 0x0E0);GPHCON1 EQU (S3C6410_BASE_REG_PA_IOPORT + 0x0E4);GPHDAT EQU (S3C6410_BASE_REG_PA_IOPORT + 0x0E8) ;GPHPUD EQU (S3C6410_BASE_REG_PA_IOPORT + 0x0EC);GPH_OneND EQU 0x2GPNCON EQU (S3C6410_BASE_REG_PA_GPIO + 0x830) GPNDAT EQU (S3C6410_BASE_REG_PA_GPIO + 0x834) GPNPUD EQU (S3C6410_BASE_REG_PA_GPIO + 0x838)MEM1DRVCON EQU (S3C6410_BASE_REG_PA_GPIO + 0x1D4);// 0x7F000000 -> 0x92B00000;vGPHCON0 EQU (0xB2B08000 + 0x0E0);vGPHCON1 EQU (0xB2B08000 + 0x0E4);vGPHDAT EQU (0xB2B08000 + 0x0E8);vGPHPUD EQU (0xB2B08000 + 0x0EC)vGPNCON EQU (0xB2B08000 + 0x830)vGPNDAT EQU (0xB2B08000 + 0x834)vGPNPUD EQU (0xB2B08000 + 0x838);vGPNCON EQU (0xB2B08830)vEINT0CON0 EQU (0xB2B08900);---------------------------; VIC;---------------------------VIC0INTENCLEAR EQU (S3C6410_BASE_REG_PA_VIC0 + 0x14) VIC1INTENCLEAR EQU (S3C6410_BASE_REG_PA_VIC1 + 0x14)vVIC0INTENABLE EQU (0xB0600010) ; VIC0vVIC0INTENCLEAR EQU (0xB0600014) ; VIC0vVIC1INTENABLE EQU (0xB0700010) ; VIC1vVIC1INTENCLEAR EQU (0xB0700014) ; VIC1NFDATA EQU 0x70200010 ; NAND Flash data register;-----------------------------------; Watch Dog Timer;-----------------------------------WTCON EQU (0x7e004000);=================; SMC;=================SMBIDCYR0 EQU 0x70000000SMBWSTRDR0 EQU 0x70000004SMBWSTWRR0 EQU 0x70000008SMBWSTOENR0 EQU 0x7000000cSMBWSTWENR0 EQU 0x70000010SMBCR0 EQU 0x70000014SMBSR0 EQU 0x70000018SMBWSTBRDR0 EQU 0x7000001cSMBIDCYR1 EQU 0x70000020SMBWSTRDR1 EQU 0x70000024SMBWSTWRR1 EQU 0x70000028SMBWSTOENR1 EQU 0x7000002cSMBWSTWENR1 EQU 0x70000030SMBCR1 EQU 0x70000034SMBSR1 EQU 0x70000038SMBWSTBRDR1 EQU 0x7000003cSMBIDCYR2 EQU 0x70000040 SMBWSTRDR2 EQU 0x70000044 SMBWSTWRR2 EQU 0x70000048 SMBWSTOENR2 EQU 0x7000004c SMBWSTWENR2 EQU 0x70000050 SMBCR2 EQU 0x70000054 SMBSR2 EQU 0x70000058 SMBWSTBRDR2 EQU 0x7000005cSMBIDCYR3 EQU 0x70000060 SMBWSTRDR3 EQU 0x70000064 SMBWSTWRR3 EQU 0x70000068 SMBWSTOENR3 EQU 0x7000006c SMBWSTWENR3 EQU 0x70000070 SMBCR3 EQU 0x70000074 SMBSR3 EQU 0x70000078 SMBWSTBRDR3 EQU 0x7000007cSMBIDCYR4 EQU 0x70000080 SMBWSTRDR4 EQU 0x70000084 SMBWSTWRR4 EQU 0x70000088 SMBWSTOENR4 EQU 0x7000008c SMBWSTWENR4 EQU 0x70000090 SMBCR4 EQU 0x70000094 SMBSR4 EQU 0x70000098 SMBWSTBRDR4 EQU 0x7000009cSMBIDCYR5 EQU 0x700000a0 SMBWSTRDR5 EQU 0x700000a4 SMBWSTWRR5 EQU 0x700000a8 SMBWSTOENR5 EQU 0x700000ac SMBWSTWENR5 EQU 0x700000b0 SMBCR5 EQU 0x700000b4 SMBSR5 EQU 0x700000b8 SMBWSTBRDR5 EQU 0x700000bcSMBIDCYR6 EQU 0x700000c0 SMBWSTRDR6 EQU 0x700000c4 SMBWSTWRR6 EQU 0x700000c8 SMBWSTOENR6 EQU 0x700000cc SMBWSTWENR6 EQU 0x700000d0 SMBCR6 EQU 0x700000d4SMBSR6 EQU 0x700000d8 SMBWSTBRDR6 EQU 0x700000dcSMBIDCYR7 EQU 0x700000e0 SMBWSTRDR7 EQU 0x700000e4 SMBWSTWRR7 EQU 0x700000e8 SMBWSTOENR7 EQU 0x700000ec SMBWSTWENR7 EQU 0x700000f0 SMBCR7 EQU 0x700000f4 SMBSR7 EQU 0x700000f8 SMBWSTBRDR7 EQU 0x700000fc;=================; DMC;=================DMC0_BASE EQU 0x7e000000DMC1_BASE EQU 0x7e001000INDEX_MEMSTAT EQU 0x0INDEX_MEMCCMD EQU 0x4INDEX_DIRECTCMD EQU 0x8 INDEX_MEMCFG EQU 0xcINDEX_REFRESH EQU 0x10INDEX_CASLAT EQU 0x14INDEX_T_DQSS EQU 0x18INDEX_T_MRD EQU 0x1cINDEX_T_RAS EQU 0x20INDEX_T_RC EQU 0x24INDEX_T_RCD EQU 0x28INDEX_T_RFC EQU 0x2cINDEX_T_RP EQU 0x30INDEX_T_RRD EQU 0x34INDEX_T_WR EQU 0x38INDEX_T_WTR EQU 0x3cINDEX_T_XP EQU 0x40INDEX_T_XSR EQU 0x44INDEX_T_ESR EQU 0x48INDEX_MEMCFG2 EQU 0x4cINDEX_ID_0_CFG EQU 0x100INDEX_ID_1_CFG EQU 0x104INDEX_ID_2_CFG EQU 0x108INDEX_ID_3_CFG EQU 0x10cINDEX_ID_4_CFG EQU 0x110INDEX_ID_5_CFG EQU 0x114INDEX_ID_6_CFG EQU 0x118INDEX_ID_7_CFG EQU 0x11cINDEX_ID_8_CFG EQU 0x120INDEX_ID_9_CFG EQU 0x124INDEX_ID_10_CFG EQU 0x128INDEX_ID_11_CFG EQU 0x12cINDEX_ID_12_CFG EQU 0x130INDEX_ID_13_CFG EQU 0x134INDEX_ID_14_CFG EQU 0x138INDEX_ID_15_CFG EQU 0x13cINDEX_CHIP0_CFG EQU 0x200INDEX_CHIP1_CFG EQU 0x204INDEX_USER_STAT EQU 0x300INDEX_USER_CFG EQU 0x304;-------------------------------------------------------------------------------; Memory Chip direct command;-------------------------------------------------------------------------------DMC_NOP0 EQU 0x0c0000DMC_NOP1 EQU 0x1c0000DMC_PA0 EQU 0x000000 ; Precharge allDMC_PA1 EQU 0x100000DMC_AR0 EQU 0x040000 ; AutorefreshDMC_AR1 EQU 0x140000DMC_SDR_MR0 EQU 0x080032 ; MRS, CAS 3, Burst Length 4DMC_SDR_MR1 EQU 0x180032DMC_DDR_MR0 EQU 0x080162DMC_DDR_MR1 EQU 0x180162DMC_mDDR_MR0 EQU 0x080032 ; CAS 3, Burst Length 4DMC_mDDR_MR1 EQU 0x180032DMC_mSDR_EMR0 EQU 0x0a0000 ; EMRS, DS:Full, PASR:Full Array DMC_mSDR_EMR1 EQU 0x1a0000DMC_DDR_EMR0 EQU 0x090000DMC_DDR_EMR1 EQU 0x190000DMC_mDDR_EMR0 EQU 0x0a0000 ; DS:Full, PASR:Full ArrayDMC_mDDR_EMR1 EQU 0x1a0000END/*************************************************//image_cfg.inc 文件/*************************************************;//------------------------------------------------------------------------------;// NAMING CONVENTION;//;// The IMAGE_ naming convention ...;//;// IMAGE_<NAME>_<SECTION>_<MEMORY_DEVICE>_[OFFSET|SIZE|START|END] ;//;// <NAME> - WINCE, BOOT, SHARE;// <SECTION> - section name: user defined;// <MEMORY_DEVICE> - the memory device the block resides on;// OFFSET - number of bytes from memory device start address;// SIZE - maximum size of the block;// START - start address of block (device address + offset);// END - end address of block (start address + size - 1);//;//------------------------------------------------------------------------------;// DRAM Base AddressDRAM_BASE_PA_START EQU (0x50000000)DRAM_BASE_CA_START EQU (0x80000000)DRAM_BASE_UA_START EQU (0xA0000000)DRAM_SIZE EQU (0x08000000);//------------------------------------------------------------------------------;// Steploader AreaIMAGE_STEPLOADER_PA_START EQU (0x00000000)IMAGE_STEPLOADER_SIZE EQU (0x00001000);//------------------------------------------------------------------------------;// Eboot AreaIMAGE_EBOOT_OFFSET EQU (0x00030000)IMAGE_EBOOT_PA_START EQU (DRAM_BASE_PA_START+IMAGE_EBOOT_OFFSET)IMAGE_EBOOT_CA_START EQU(DRAM_BASE_CA_START+IMAGE_EBOOT_OFFSET)IMAGE_EBOOT_UA_START EQU (DRAM_BASE_UA_START+IMAGE_EBOOT_OFFSET)IMAGE_EBOOT_SIZE EQU (0x00080000)EBOOT_BINFS_BUFFER_OFFSET EQU (0x000C0000)EBOOT_BINFS_BUFFER_PA_START EQU (DRAM_BASE_PA_START+EBOOT_BINFS_BUFFER_OFFSET)EBOOT_BINFS_BUFFER_CA_START EQU (DRAM_BASE_CA_START+EBOOT_BINFS_BUFFER_OFFSET)EBOOT_BINFS_BUFFER_UA_START EQU (DRAM_BASE_UA_START+EBOOT_BINFS_BUFFER_OFFSET)EBOOT_BINFS_BUFFER_SIZE EQU (0x00030000)EBOOT_USB_BUFFER_OFFSET EQU (0x04000000)EBOOT_USB_BUFFER_PA_START EQU (DRAM_BASE_PA_START+EBOOT_USB_BUFFER_OFFSET)EBOOT_USB_BUFFER_CA_START EQU (DRAM_BASE_CA_START+EBOOT_USB_BUFFER_OFFSET)EBOOT_USB_BUFFER_UA_START EQU (DRAM_BASE_UA_START+EBOOT_USB_BUFFER_OFFSET);//------------------------------------------------------------------------------;// NK AreaIMAGE_NK_OFFSET EQU (0x00100000)IMAGE_NK_PA_START EQU (DRAM_BASE_PA_START+IMAGE_NK_OFFSET)IMAGE_NK_CA_START EQU (DRAM_BASE_CA_START+IMAGE_NK_OFFSET)IMAGE_NK_UA_START EQU (DRAM_BASE_UA_START+IMAGE_NK_OFFSET);gao0129;IMAGE_NK_SIZE EQU (0x03F00000) ; Set Max size, This will be tailored automatically.IMAGE_NK_SIZE EQU (0x02800000);//------------------------------------------------------------------------------;// BSP ARGs AreaIMAGE_SHARE_ARGS_OFFSET EQU (0x00020800)IMAGE_SHARE_ARGS_PA_START EQU (DRAM_BASE_PA_START+IMAGE_SHARE_ARGS_OFFSET)IMAGE_SHARE_ARGS_CA_START EQU(DRAM_BASE_CA_START+IMAGE_SHARE_ARGS_OFFSET)IMAGE_SHARE_ARGS_UA_START EQU (DRAM_BASE_UA_START+IMAGE_SHARE_ARGS_OFFSET)IMAGE_SHARE_ARGS_SIZE EQU (0x00000800);//------------------------------------------------------------------------------;// Sleep Data AreaIMAGE_SLEEP_DA TA_OFFSET EQU (0x00028000)IMAGE_SLEEP_DA TA_PA_START EQU (DRAM_BASE_PA_START+IMAGE_SLEEP_DA TA_OFFSET)IMAGE_SLEEP_DA TA_CA_START EQU (DRAM_BASE_CA_START+IMAGE_SLEEP_DATA_OFFSET)IMAGE_SLEEP_DA TA_UA_START EQU (DRAM_BASE_UA_START+IMAGE_SLEEP_DATA_OFFSET)IMAGE_SLEEP_DA TA_SIZE EQU (0x00002000);//------------------------------------------------------------------------------;------------------------------------------------------------------------------; OEM Stack Layout; EBOOT, STEPLOADER also use this value;------------------------------------------------------------------------------TOP_OF_STACKS_PHYSICAL EQU (DRAM_BASE_PA_START+IMAGE_NK_OFFSET) ; Stack Top is in front of NK Image TOP_OF_STACKS_VIRTUAL EQU (DRAM_BASE_CA_START+IMAGE_NK_OFFSET); Stack Size of Each ModeFIQStackSize EQU 256IRQStackSize EQU 256AbortStackSize EQU 256UndefStackSize EQU 256SVCStackSize EQU 1024;UserStackSize EQU 2048; Stack Location of Each Mode (in Physical Address)FIQStack_PA EQU (TOP_OF_STACKS_PHYSICAL - 0x0)IRQStack_PA EQU (FIQStack_PA - FIQStackSize)AbortStack_PA EQU (IRQStack_PA - IRQStackSize)UndefStack_PA EQU (AbortStack_PA - AbortStackSize)SVCStack_PA EQU (UndefStack_PA - UndefStackSize)UserStack_PA EQU (SVCStack_PA - SVCStackSize); Stack Location of Each Mode (in Virtual Address)FIQStack_V A EQU (TOP_OF_STACKS_VIRTUAL - 0x0)IRQStack_VA EQU (FIQStack_V A - FIQStackSize)AbortStack_V A EQU (IRQStack_V A - IRQStackSize)UndefStack_VA EQU (AbortStack_V A - AbortStackSize)SVCStack_V A EQU (UndefStack_V A - UndefStackSize)UserStack_V A EQU (SVCStack_V A - SVCStackSize);------------------------------------------------------------------------------; Sleep Data Layout;------------------------------------------------------------------------------SleepState_Data_Start EQU (0)SleepState_WakeAddr EQU (SleepState_Data_Start)SleepState_SYSCTL EQU (SleepState_WakeAddr + WORD_SIZE ) SleepState_MMUTTB0 EQU (SleepState_SYSCTL + WORD_SIZE ) SleepState_MMUTTB1 EQU (SleepState_MMUTTB0 + WORD_SIZE ) SleepState_MMUTTBCTL EQU (SleepState_MMUTTB1 + WORD_SIZE ) SleepState_MMUDOMAIN EQU (SleepState_MMUTTBCTL + WORD_SIZE ) SleepState_SVC_SP EQU (SleepState_MMUDOMAIN + WORD_SIZE ) SleepState_SVC_SPSR EQU (SleepState_SVC_SP + WORD_SIZE ) SleepState_FIQ_SPSR EQU (SleepState_SVC_SPSR + WORD_SIZE ) SleepState_FIQ_R8 EQU (SleepState_FIQ_SPSR + WORD_SIZE ) SleepState_FIQ_R9 EQU (SleepState_FIQ_R8 + WORD_SIZE ) SleepState_FIQ_R10 EQU (SleepState_FIQ_R9 + WORD_SIZE ) SleepState_FIQ_R11 EQU (SleepState_FIQ_R10 + WORD_SIZE ) SleepState_FIQ_R12 EQU (SleepState_FIQ_R11 + WORD_SIZE ) SleepState_FIQ_SP EQU (SleepState_FIQ_R12 + WORD_SIZE ) SleepState_FIQ_LR EQU (SleepState_FIQ_SP + WORD_SIZE ) SleepState_ABT_SPSR EQU (SleepState_FIQ_LR + WORD_SIZE ) SleepState_ABT_SP EQU (SleepState_ABT_SPSR + WORD_SIZE ) SleepState_ABT_LR EQU (SleepState_ABT_SP + WORD_SIZE ) SleepState_IRQ_SPSR EQU (SleepState_ABT_LR + WORD_SIZE ) SleepState_IRQ_SP EQU (SleepState_IRQ_SPSR + WORD_SIZE ) SleepState_IRQ_LR EQU (SleepState_IRQ_SP + WORD_SIZE ) SleepState_UND_SPSR EQU (SleepState_IRQ_LR + WORD_SIZE ) SleepState_UND_SP EQU (SleepState_UND_SPSR + WORD_SIZE ) SleepState_UND_LR EQU (SleepState_UND_SP + WORD_SIZE ) SleepState_SYS_SP EQU (SleepState_UND_LR + WORD_SIZE ) SleepState_SYS_LR EQU (SleepState_SYS_SP + WORD_SIZE ) SleepState_VFP_FPSCR EQU (SleepState_SYS_LR + WORD_SIZE) SleepState_VFP_FPEXC EQU (SleepState_VFP_FPSCR + WORD_SIZE) SleepState_VFP_FPINST EQU (SleepState_VFP_FPEXC + WORD_SIZE)SleepState_VFP_FPINST2 EQU (SleepState_VFP_FPINST + WORD_SIZE) SleepState_VFP_S0 EQU (SleepState_VFP_FPINST2 + WORD_SIZE) SleepState_VFP_S1 EQU (SleepState_VFP_S0 + WORD_SIZE) SleepState_VFP_S2 EQU (SleepState_VFP_S1 + WORD_SIZE) SleepState_VFP_S3 EQU (SleepState_VFP_S2 + WORD_SIZE) SleepState_VFP_S4 EQU (SleepState_VFP_S3 + WORD_SIZE) SleepState_VFP_S5 EQU (SleepState_VFP_S4 + WORD_SIZE) SleepState_VFP_S6 EQU (SleepState_VFP_S5 + WORD_SIZE) SleepState_VFP_S7 EQU (SleepState_VFP_S6 + WORD_SIZE) SleepState_VFP_S8 EQU (SleepState_VFP_S7 + WORD_SIZE) SleepState_VFP_S9 EQU (SleepState_VFP_S8 + WORD_SIZE) SleepState_VFP_S10 EQU (SleepState_VFP_S9 + WORD_SIZE) SleepState_VFP_S11 EQU (SleepState_VFP_S10 + WORD_SIZE) SleepState_VFP_S12 EQU (SleepState_VFP_S11 + WORD_SIZE) SleepState_VFP_S13 EQU (SleepState_VFP_S12 + WORD_SIZE) SleepState_VFP_S14 EQU (SleepState_VFP_S13 + WORD_SIZE) SleepState_VFP_S15 EQU (SleepState_VFP_S14 + WORD_SIZE) SleepState_VFP_S16 EQU (SleepState_VFP_S15 + WORD_SIZE) SleepState_VFP_S17 EQU (SleepState_VFP_S16 + WORD_SIZE) SleepState_VFP_S18 EQU (SleepState_VFP_S17 + WORD_SIZE) SleepState_VFP_S19 EQU (SleepState_VFP_S18 + WORD_SIZE) SleepState_VFP_S20 EQU (SleepState_VFP_S19 + WORD_SIZE) SleepState_VFP_S21 EQU (SleepState_VFP_S20 + WORD_SIZE) SleepState_VFP_S22 EQU (SleepState_VFP_S21 + WORD_SIZE) SleepState_VFP_S23 EQU (SleepState_VFP_S22 + WORD_SIZE) SleepState_VFP_S24 EQU (SleepState_VFP_S23 + WORD_SIZE) SleepState_VFP_S25 EQU (SleepState_VFP_S24 + WORD_SIZE) SleepState_VFP_S26 EQU (SleepState_VFP_S25 + WORD_SIZE) SleepState_VFP_S27 EQU (SleepState_VFP_S26 + WORD_SIZE) SleepState_VFP_S28 EQU (SleepState_VFP_S27 + WORD_SIZE) SleepState_VFP_S29 EQU (SleepState_VFP_S28 + WORD_SIZE) SleepState_VFP_S30 EQU (SleepState_VFP_S29 + WORD_SIZE) SleepState_VFP_S31 EQU (SleepState_VFP_S30 + WORD_SIZE) SleepState_Data_End EQU (SleepState_VFP_S31 + WORD_SIZE ) SLEEPDATA_SIZE EQU ((SleepState_Data_End - SleepState_Data_Start) / 4);//------------------------------------------------------------------------------END。

ok6410开发板交叉编译器的安装

ok6410开发板交叉编译器的安装

1.上篇文章中我们说了已经在虚拟机里面的ubuntu12 根目录下建立了

forlinx 文件夹,现将arm-linux-gcc.4.3.2.tgz 拷贝到forlinx 中,我用的是上次建立

好的xftp,相当爽啊2. cd ../../

ls

cd forlinx

mkdir /usr/local/arm

tar zxvf arm-linux-gcc-4.3.2.tgz -C /,注意这里的斜杠不要丢掉

这样解压到了/usr/local/arm

然后运行这个命令gedit /etc/profile

再把以下四行加入文件的头部(尾部我试了反正我的不管用,不知道为啥)

export PATH=/usr/local/arm/4.3.2/bin:$PATH export TOOLCHAIN=/usr/local/arm/4.3.2 export TB_CC_PREFIX=arm-linux- export PKG_CONFIG_PREFIX=$TOOLCHAIN/arm-none-linux-gnueabi

然后reboot,reboot 后terminal 中输入arm-linux-gcc -v 就可以看到信息了很好

tips:感谢大家的阅读,本文由我司收集整编。

仅供参阅!。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

#./configure --prefix=/opt/arm/opencv --host=arm-linux --disable-assembly #make #make install

7、ffmpeg 的交叉编译:

#./configure --prefix= prefix=/opt/arm/opencv --enable-shared --disable-static --enable-gpl --enable-cross-compile --arch=arm --disable-stripping --target-os=linux --enable-libx264 --enable-libxvid --cc=arm-linux-gcc --enable-swscale --extra-cflags=-I/opt/arm/opencv/include --extra-ldflags=-L/opt/arm/opencv/lib #make #make install

解决方法:修改 CMakeCache.txt,WITH_TIFF:BOOL=ON,改成 OFF,重新 编译,错误消除。

#make install 三、测试

测试程序: #include #include #include

int main(int argc,char **argv) {

CvCapture* capture = NULL; IplImage* frame = NULL;

2、libjpeg 的交叉编译:

#./configure --host=arm-linux --prefix=/opt/arm/opencv --enable-shared --enable-static #make install

3、libpng 的交叉编译

#./configure --host=arm-linux --prefix=/opt/arm/opencv --enable-shared --enable-static #make #make install

cmake-2.8.8-Linux-i386.tar,gz

二、opencvΒιβλιοθήκη 2.3.1 的移植过程1、libz 的交叉编译:

# ./configure --prefix=/opt/arm/opencv --shared 修改 makefile CC=arm-linux-gcc AR=arm-linux-ar rc RANLIB=arm-linux-ranlib CDSHARED=arm-linux-gcc -shared -wl, -soname,libz.so.1,--version-script,zl lib.map #make #make install

解决方法: 修改 CMakeCache.txt,CMAKE_EXE_LINKER_FLAGS 原来为空,加上-lpthread -lrt, 重新编译,错误消除

错误二: Linking CXX executable ../../bin/opencv_createsamples ../../lib/libopencv_highgui.so: undefined reference to `_TIFFerrorHandler' ../../lib/libopencv_highgui.so: undefined reference to `_TIFFrealloc' ../../lib/libopencv_highgui.so: undefined reference to `_TIFFmalloc' ../../lib/libopencv_highgui.so: undefined reference to `_TIFFmemcpy' ../../lib/libopencv_highgui.so: undefined reference to `TIFFOpen' ../../lib/libopencv_highgui.so: undefined reference to `_TIFFfree'

if(!(capture = cvCaptureFromCAM(-1))) {

fprintf(stderr, "Can not open camera./n"); return -1; }

cvNamedWindow("video", 1);

while(frame = cvQueryFrame( capture ) ) {

../../lib/libopencv_highgui.so: undefined reference to `_TIFFwarningHandler' ../../lib/libopencv_highgui.so: undefined reference to `_TIFFmemcmp' ../../lib/libopencv_highgui.so: undefined reference to `_TIFFmemset'

opencv2.4.2 移植到 X4412

一、编译环境及库文件

linux 环境:CentOS65 交叉编译:4.5.1 arm 板子:X4412

libz: libjpeg: libpng: libyasm: opencv: libx264: libxvid: lffmpeg: cmake:

zlib-1.2.7 jpegsrc.v7 libpng-1.5.10 yasm-1.2.0 opencv-2.4.2 x264-snapshot-20120608-2245 xvidcore-1.3.2 ffmpeg-0.10.3

8.cmake-gui 安装 到官网上下载已经编译好的 cmake-2.8.8-Linux-i386.tar,gz,解压就可以了

9、opencv2.4.1 的交叉编译:

用到的主要目录说明:

交叉编译工具链所在目录

/opt/toolschain/4.5.1/bin

安装 opencv 的目录

/opt/arm/ffmpeg-arm/opencv-build

cvShowImage("video", frame); }

cvDestroyWindow("video");

cvReleaseCapture(&capture);

return 0; }

编译: #arm-linux-g++ -o opencv_test opencv_test.cpp -I /usr/local/include -L /usr/local/lib -lopencv_core -lopencv_highgui -lpthread -lrt

选择 Build 目录:/home/6410/opencv/opencv-2.4.2/build 点击 Configure,保持 generator 为 Unix Makefiles,选择 Specify options for cross-compiling,点击 Next, Operating System 填写 arm-linux C Compilers 填写 opt/FriendlyARM/toolschain/4.5.1/bin/arm-linux-gcc C++ Compilers 填写 opt/FriendlyARM/toolschain/4.5.1//bin/arm-linux-g++ 程序库的 Target Root 填写 opt/FriendlyARM/toolschain/4.5.1/ 然后点击 Finish。 默认安装目录为/usr/local,点击 Generate 生成 Makefile。

4、yasm 的交叉编译:

#./configure --host=arm-linux --prefix=/opt/arm/opencv --enable-shared --enable-static #make #make install

5、libx264 的交叉编译:

#CC=arm-linux-gcc ./configure --enable-shared --host=arm-linux --disable-asm --prefix=/opt/arm/opencv 修改 config.mak 中 CC=arm-none-linux-gnueabi-gcc AR=arm-none-linux-gnueabi-ar RANLIB=arm-none-linux-gnueabi-ranlib STRIP=arm-none-linux-gnueabi-strip 保持并退出 #make #make install 6、libxvid 的交叉编译:

opencv 源码所在目录

/opt/opencv/opencv-2.3.0/

编译好的 opencv 库所在目

录

/home/6410/opencv/opencv-2.4.2/build

#mkdir build #cd build 安装 cmake 和 cmake-gui 包 #yum install cmake cmake-gui #cmake-gui 选择源代码目录/home/6410/opencv/opencv-2.4.2/

#make

错误一:

Linking CXX executable ../../bin/opencv_createsamples ../../lib/libopencv_core.so: undefined reference to `clock_gettime' ../../lib/libopencv_highgui.so: undefined reference to `_TIFFerrorHandler' ../../lib/libopencv_highgui.so: undefined reference to `_TIFFrealloc' ../../lib/libopencv_core.so: undefined reference to `pthread_key_create