JTAG调试器PCB设计(ppt 50页)

第05讲_第3章JTAG技术_65页

tms=1合肥工业大学计算机与信息学院 tms=0 tms=1 tms=0

JTAG信号

TMS:测试模式选择(Test Mode Select) 通过TMS信号控制JTAG状态机的状态。 TCK:JTAG的时钟信号 TDI:数据输入信号 TDO:数据输出信号 nTRST:JTAG复位信号,复位JTAG的状态机和内 部的宏单元(Macrocell)。

2013-8-9

合肥工业大学计算机与信息学院

12

3.4.3 ARM7TDMI扫描链布局

2013-8-9

合肥工业大学计算机与信息学院

13

ARM7TDMI内核扫描链结构

113位 38位

33位

2013-8-9 合肥工业大学计算机与信息学院 14

边界扫描寄存器(扫描单元)

JTAG接口的IC内部结构

芯片引脚

嵌入式系统结构与设计基础

第5讲 合肥工业大学计算机与信息学院 史久根

第3章 嵌入式微处理器技术基础

本章主要介绍以下内容: 嵌入式微处理器典型技术 主流嵌入式微处理器 嵌入式处理器的调试技术 边界扫描测试技术JTAG

2013-8-9

合肥工业大学计算机与信息学院

2

3.4 边界扫描测试接口JTAG

SAMPLE/PREL 0011 OAD RESTART 0100

CLAMP

2013-8-9

0101

BYPASS

1111

21

合肥工业大学计算机与信息学院

JTAG的指令寄存器

在SHIFT-IR态,将指令寄存器选做TDI和TDO之间串行 路径。见(a) 在UPDATE-IR态,指令寄存器的值成为当前指令。见(b) 在CAPTURE-IR态,将b0001加载到该寄存器。该值在 SHIFT-IR态移位输出。见(c) 复位时,IDCODE(b1110)成为当前指令。见(d) 指令寄存器的最低有效位首先被扫描输入和输出。

构建系统级JTAG链调试电路JTAG技术介绍JTAG技术俗称

构建系统级JTAG链调试电路第一部分: JTAG技术介绍JTAG技术俗称边界扫描技术,是近代发展起来的高级测试技术。

JTAG主要有以下几个方面应用:1).互连测试。

判断互连线路是否存在开路、短路或固定逻辑故障。

2).可编程器件的程序加载。

如FLASH、CPLD、FPGA等器件的加载。

3).可编程器件的在线调试。

如FPGA,DSP等器件在线debug。

4).电路采样。

器件正常工作时,对管脚状态进行采样观察。

JTAG测试一般使用标准的TAP(Test Access Port)连接器,如下图所示。

A).1号脚为TCK。

JTAG测试参考时钟,由JTAG主控制器提供给被测试器件,该信号需要下拉处理,下拉电阻不能小于330ohm,一般选择1Kohm。

之所以TCK要下拉处理,是因为JTAG 测试规范规定:在TCK为低电平时,被测试器件的TAP状态机不得发生变化。

所以,默认状态下,TCK必须为低电平,使TAP状态机保持稳定。

最小驱动电流为2mA。

B).2号脚为GND。

使用时直接连单板的GND即可。

C).3号脚为TDO。

JTAG测试数据输出管脚,JTAG主控制器从此管脚输出测试数据给被测试器件,JTAG主控制器的TDO接被测试器件的TDI。

TDO在TCK的下降沿输出。

JTAG测试规范没有规定如何处理TDO管脚,一般情况下悬空即可,也可以通过4.7Kohm电阻上拉到VCC,已增加驱动TDO的驱动能力。

D).4号脚为VCC。

连接电源,一般为3.3V/2.5V/1.8V等,具体看芯片说明。

在这里特别说明下,在实际使用中,很容易将2号脚的GND与此VCC接反,导致JTAG不可用,所以,大家在设计审查时一定要特别关注这个地方。

以免因低级错误导致设计改板。

E).5号脚为TMS。

TMS是Test Mode Select的缩写,作用是进行测试模式选择,由JTAG主控制器输出给被测试器件。

被测试器件在TCK的上升沿才TMS信号进行采样,根据采样结果来判断是正常模式还是JTAG测试模式(TMS=“0”为正常模式,TMS=“1”为JTAG模式)。

ADPCB设计PPT课件

4

双面板 双面板包括两层:顶层(Top Layer)和底层(Bottom Layer)。 与单面板不同,双面板的两层都有导电铜箔 双面板的每层都可以直接焊接元件,两层之间可以通过穿过的 元件引脚连接,也可以通过过孔实现连接。

20

选择View → Fit Board(热键V,F)将只显示板子形状。 选择File → Save As来将新PCB文件重命名(用*.PcbDoc扩展

名)。指定设计者要把这个PCB保存在设计者的硬盘上的位置, 在文件名栏里键入文件名Multivibrator.PcbDoc并单击保存按钮。

21

表面粘贴式焊盘无须钻孔; 针脚式焊盘要求钻孔,它有过孔直径和焊盘直径两个参数。 在设计焊盘时,要考虑到的影响因素: 元件形状、引脚大小、 安装形式、受力及振动大小等情况。 例如,如果某个焊盘通过电流大、受力大并且易发热,可设计成泪滴状。

12

助焊膜和阻焊膜

助焊膜 ✓为了使印制电路板的焊盘更容易粘上焊锡,通常在焊盘上涂一层 助焊膜。

单击最初的板子范围宽度规则名 Width,将Min Width、Preferred Width 和 Max Width宽度栏均设为12mil

优先级对话框,优先级(Priority) 列的数字越小,优先级越高。可 以按“Decrease Priority”按钮减 少选中对象的优先级,按 “Increase Priority”按钮增加选中 对象的优先级,GND的优先级最 高,Width的优先级最低

Designer都会监测每个动作,并检查设计是否仍然完全符合设计规则。

单片机PCB实验板制作PPT资料

通过JTAG或SWD接口进行 程序下载和调试,确保实验 板功能正常。

实例二:基于ESP32的物联网开发板制作

芯片特性

ESP32是一款低功耗的Wi-Fi/蓝牙双 模芯片,具有高性能和丰富的外设接 口。

模块集成

将ESP32与其他必要元件集成在PCB 上,如Flash存储器、电源管理IC等。

网络编程

利用ESP32的Wi-Fi和蓝牙功能,进 行网络编程和远程控制。

等处理。

PCB制作

将处理好的光绘文件送至PCB工 厂进行制板,确保制板工艺符合

设计要求。

焊接与调试阶段

元件采购与准备

根据原理图和PCB布局,采购 合适的电子元件,并准备焊接

工具和调试设备。

元件焊接

按照PCB上的元件排列顺序, 逐一将元件焊接到对应的焊盘 上,确保焊接质量。

电路调试

通过调试设备(如示波器、万 用表等)对实验板进行测试和 调试,确保电路功能正常。

易于扩展

实验板上留有丰富的扩展接口,方便用户外接其他设备和 传感器。

高度集成

实验板集成了单片机所需的各种外围电路和接口,方便用 户快速搭建实验系统。

易于学习

实验板上的电路和接口都经过精心设计,有助于用户深入 了解单片机的原理和应用。

实验板的应用场景

教学实验

单片机PCB实验板是高校和培训机构 进行单片机教学的理想实验工具,可 用于演示和验证各种单片机原理和应 用。

性能评估与优化

根据测试结果,对实验板性能 进行评估,如有需要可进行优

化和改进。

03

单片机PCB实验板制作技术要 点

元件布局与布线规则

元件布局

按照电路功能和信号流向进行合 理布局,尽量减小元件间的距离 ,提高电路板集成度。

JTAG接口

JTAG接口

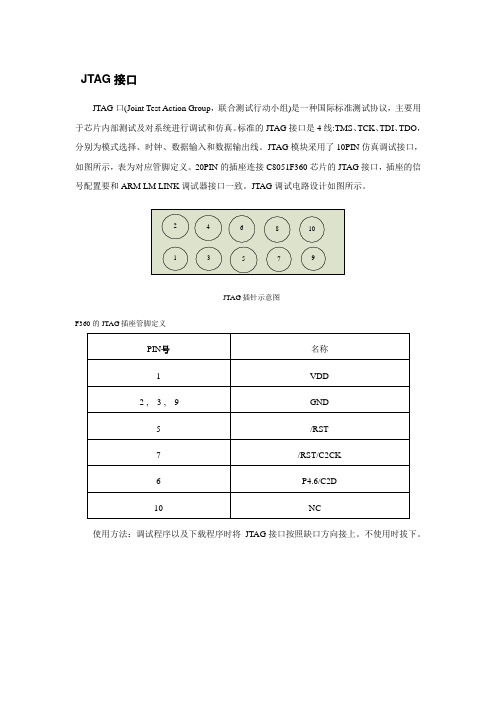

JTAG口(Joint Test Action Group,联合测试行动小组)是一种国际标准测试协议,主要用于芯片内部测试及对系统进行调试和仿真。

标准的JTAG接口是4线:TMS、TCK、TDI、TDO,分别为模式选择、时钟、数据输入和数据输出线。

JTAG模块采用了10PIN仿真调试接口,如图所示,表为对应管脚定义。

20PIN的插座连接C8051F360芯片的JTAG接口,插座的信号配置要和ARM LM LINK调试器接口一致。

JTAG调试电路设计如图所示。

136

79

248

5

10

JTAG插针示意图

F360的JTAG插座管脚定义

PIN号名称

1 VDD

2 ,

3 , 9 GND

5 /RST

7 /RST/C2CK

6 P4.6/C2D

10 NC

使用方法:调试程序以及下载程序时将JTAG接口按照缺口方向接上。

不使用时拔下。

altium designer使用PCB向导来创建PCB详细过程PPT课件

第12页/共15页

• 6.PCB文档显示了一个默认尺寸的白色图纸,要关闭图纸,选择Design → Board Options,在Board Options对话框取消选择Design Sheet。

第13页/共15页

小结:

• 3.1印制电路板的基础知识

• 3.2创建一个新的PCB文件

要把这个PCB保存在设计者的硬盘上的位置,在文件名栏里键入文件名 M u l t i v i b r a t o r. P c b D o c 并 单 击 保 存 按 钮 。

第5页/共15页

• 15.如果添加到项目的PCB是以自由文件 打开的,在Projects面板的Free Documents单元右击PCB文件,选择Add to Project。这个PCB文件已经被列在 Projects下的Source Documents中,并与 其他项目文件相连接。设计者也可以直接 将自由文件夹下的Multivibrator.PcbDoc文 件拖到项目文件夹下。保存项目文件如图 3-12所示。

图3-14 工程变更命令对话框

第10页/共15页

• 3.单击Validate Changes按钮,验证一下有无不妥之处,如果执行成功则在状态列

表(Status)Check中将会显示

符号;若执行过程中出现问题将会显示 符号,

关闭对话框。检查Messages面板查看错误原因,并清除所有错误。

• 4.如果单击Validate Changes 按钮,没有错误,则单击Execute Changes按钮, 将信息发送到PCB。当完成后,Done那一列将被标记。如图3-15所示。

第4页/共15页

• 11.PCB向导现在收集了它需要的所有的信息来创建设计者的新板子。PCB编辑器 将显示一个名为PCB1.PcbDoc的新的PCB文件。

JTAG电路设计规范

JTAG电路设计规范1. JTAG电路简介JTAG的全称是Joint Test Action Group,即联合测试行动小组。

目前,JTAG已成为一种国际标准测试协议,主要用于各类芯片的内部测试。

现在大多数高级器件(包括FPGA、MCU、DSP以及CPU等)都支持JTAG协议,如FPGA、DSP器件等。

标准的JTAG接口是4线接口:TMS、TCK、TDI以及TDO,分别为模式选择、时钟、数据输入和数据输出信号线。

JTAG电路的功能模块如图所示在芯片的核心逻辑(Core)与外界管脚之间加入串行扫描寄存器单元,并将这些单元连接起来,用一个专门的控制器来控制。

因为这些逻辑单元在器件最“边缘”处,形象地称之为“边界扫描测试”。

JTAG最初是用来对芯片进行测试的,基本原理是在器件内部定义一个TAP(T est Access Port,测试访问口)端口,通过专用的JTAG 测试工具对进行内部节点进行测试。

此外,JTAG协议允许多个器件通过JTAG接口串联在一起,形成一个JTAG链,能实现对各个器件分别测试。

此外,JTAG接口还常用于实现ISP(In-SystemProgrammable,在线编程),对FLASH等器件进行编程。

JTAG在线编程的特征也改变了传统生产流程,将以前先对芯片进行预编程再装到板上的工艺简化为:先固定器件到电路板上,再用JTAG编程,从而大大加快工程进度。

1985年,由Philips、Siemens、Ericsson等公司成立JETAG (JointEuropean T est Action Group)1986年,随着一些其他地区公司的加入,更名为:JTAG (JointTest Action Group)1988年,JTAG提出了标准的边界扫描体系结构。

1990年,IEEE正式收录了JTAG标准,命名为:IEEE1149.1-90。

2.JTAG边界扫描电路边界扫描测试(BST:BOUNDARY SEAN TEST)一般采用4线接口(在5线接口中,有一条为主复位信号)。

JTAG接口PCB设计要点

JTAG接口PCB设计要点1、 Keep JTAG traces as short as possible.2、 Either galvanically isolate JTAG ground from offboard equipment or make sure that the PCB and the3、 Add a 3–5 kΩ pull-up resistor to the JTAG interface’sTCK pin to reduce susceptibility to EMI.4、 In noisy systems, add pull-down or pull-up resistorsto every JTAG signal.5、 Place small series resistance on JTAG traces thatare routed to external connectors.4.3.2. The JTAG InterfaceBecause JTAG signals have only a weak on-chip pull-up resistance and are not deglitched, signal traces are particularly susceptible to noise coupling and EMI. Toreduce EMI sensitivity, JTAG traces should be kept asshort as possible. If the PCB is not galvanically isolatedfrom the off-board equipment (see 5. "Isolation And Protection" on page 11), the PCB and equipment mustconnecting a pin of the JTAG header to the PCB ground plane.The JTAG signals can be made more immune to noiseby adding some passive circuitry. External pull-up orpull-down resistors can be added to aid the relativelyweak on-chip pull-ups.Most applications will be sufficiently protected by addinga 3–5 kΩ pull-up resistor to the TCK signal. If the deviceis to be used in a particularly noisy environment, allJTAG signals should have strong external pull-ups or pull-down circuits to digital ground. Please note that placing a pull-down resistor on TCK will make your Capacitive ringing across long JTAG cables can cause small series resistanceon JTAG signals dampens this ringing and improve performance.Silicon Laboratories MCU target boards use a 5x2 header. Figure 11 shows a circuit diagram for the header, along with connections for a JTAG device.。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

增加过孔时,按住shift键同时单击即可实现添加。打开设计工具盒 ,

使用设计工具盒中的布线命令

,最常用的是半自动

布线命令Dynamic Route。单击半自动布线命令后,单击需要连线的焊

盘,布线开始,JTAG调试器布线结果如图29所示。

图29 JTAG调试器PCB设计结果

4. JTAG调试器灌铜区设置

件封装编辑界面下单击File|New命令,弹出对话框,选择“CAE Decal”项,单击OK进入逻辑封装设计窗口。

步骤2:单击绘图工具盒中的封装向导图标,打开CAE Decal Wizard对 话框,设置如图1所示,封装设计结果如图2所示。

图1 25针并口座元件CAE封装向导的设置

图2 25针并口座元件CAE封装设置结果

件类型,保 存名字为“MYDB25”,结果如图9所示。

图7 MYDB25逻辑封装的分配

图8 MYDB25元件PCB封装的指定

图9 MYDB25元件类型建立结果

(2) 74HC244元件类型建立

步骤1:首先分配74HC244的逻辑封装,如图10所示。

图10 74HC244的逻辑封装分配

步骤2:将74HC244的PCB封装指定,如图11所示。分配好逻辑封装和指 定好PCB封装后,单击OK。

安全间距Clearance设置结果如图24所示:

图24 安全间距Clearance设置结果

走线Routing设置结果如图25所示,该电路板为双面走线。

图25 走线Routing设置结果

2. JTAG调试器元件布局

使用设计工具盒 中与元件布局相关的命令,进行元件的布局。首先 选中元件J1将其移动到板框边缘,同时右击选择Query/Modify对话框, 在Glued前打勾,将J1固定,其他元件均以该元件为参照进行布局,如 图26所示。

图4 74HC244元件CAE封装设置结果

பைடு நூலகம்

2.建立元件类型

在JTAG调试器中,元件的PCB封装在PADS库中均存在,故可直接建 立元件的类型。 (1) MYDB25并口插座元件类型建立

在PowerLogic设计窗口,单击Tools|Part Editor命令,进入元件类型 编辑窗口,单击编辑电特性命令,打开Part Information for Part窗口。 步骤1:首先分配MYDB25的逻辑封装,如图7所示。 步骤2:将DB25-HM的PCB封装指定,如图8所示。 步骤3:分配好逻辑封装和指定好PCB封装后,单击OK。 步骤4:单击编辑逻辑门封装命令 ,选择A门后编辑管脚后保存该元

图18 原点处叠放的元件

第三节 JTAG调试器PCB设计

1.相关参数设置

(1)PowerPCB设计环境参数设置 在Global选项卡中,将Design Units中的单位设置为Mils。其他参数使用 软件默认值。Grid选项卡设置如图19所示:

(2)Net显示设置

在PowerPCB设计窗口,单击View|Nets命令,打开View Nets对话框, 选择+5V单击add将+5v添加到View窗口,在View窗口中选中+5V,这时 颜色选项卡由灰色变成可选择的,接下来给电源网络选择黄色作为显示 颜色,如图20所示。

图13 连接器的添加

图14 连接器的管脚类型

步骤2:单击编辑门封装 图标,打开Select Pin Decal对话框,选中 CONIN后单击OK,单击File|Return to Part返回连接器编辑对话窗口, 同样的方法,依次将CONIN1、 CONOUT、 CONOUT1、CON_IO

编辑,最后将结果保存到JTAG库。

图26 DB25移动结果

另外,选中C1电容,右击在弹出的快速菜单中选择Flid Side将其放置于 电路板的Bottom层,其余器件均处于Top层;为了让布局界面清晰,单 击Setup|Selected Color打开颜色设置选项卡,在Other框中将 connection的颜色设置为黑色(图27),当布局结束时,再将其修改为区别 于背景的可见颜色,布局结果如图28所示。

图32 顶层走线

图33 底层走线

图34 顶层丝印

图35 底层丝印

图36 顶层SMD输出显示结果(paste mask)

图37 底层SMD输出显示结果(paste mask)

图38 顶层主焊层输出显示结果solder mask

图39 底层主焊层输出显示结果solder mask

图40 顶层钻孔坐标输出显示结果drill

使用 命令绘制灌铜区边框,修改灌铜区属性,将其指定给Bottom层, 分配给地网络即将灌铜区指定为底层的地网络上。使用右键菜单中Flood 命令,完成灌铜,结果如图30所示。

图30 JTAG调试器灌铜结果

5. JTAG调试器电路的设计验证

在PowerPCB的设计窗口中,单击Tools|Verify Design命令,打开设计验 证窗口,在检查栏目Check下,单击Clearance|Start命令,提示发现错 误,如图31所示。元件的PCB封装外框超过了电路板边框,在这里实际 电路情况需要这样放置,可以不用修改,继续验证其它项目。

图11 74HC244的PCB封装指定

步骤3:单击编辑逻辑门封装命令 ,选择A门编辑管脚后保存该元件 类型,保存名字为“MY244PT”,结果如图12所示。

图12 MY244PT元件类型结果

(3)14芯插头元件类型建立

步骤1:在元件封装编辑界面下单击File|New命令,弹出对话框,选择连 接器“Connector”项,单击OK进入逻辑封装设计窗口。单击门 编辑图标 打开Part Information for Part窗口,在Connector 选项卡中,单击Add按钮,在浏览按钮下打开Browse for Special Symbols对话框,将connect库中的CONIN、 CONIN1、 CONOUT、 CONOUT1、CON_IO添加到Special Symbols栏目下,结果如图13所示,然后在Pin Type中编辑管 脚类型,结果如图14所示。其中排在最前面的是的连接器是默 认为逻辑封装。

表1 14针接口JTAG调试器元件清单

第一节 JTAG调试器元件制作

JTAG调试器电路中需要设计的元件包括25针的并口座、8线缓冲/接收 器74HC244、14座的JTAG插座。

1.元件的CAE封装制作

首先进行 PowerLogic的启动及显示颜色设置,根据用户喜欢可以自 行设置,也可以是使用软件默认环境。其次,单击File|Library|New Library命令,在文件名中输入“JTAG”,建立新的元件库,这样将JTAG 调试器设计相关的元件封装放到这个独立的库中保存。 (1)MYDB25并口插座CAE封装制作 步骤1:单击Tools|Part Editor命令,进入元件封装设计编辑界面,在元

步骤3:单击File|Save As将MYDB25并口插座保存到JTAG库中。

(2) 74HC244的CAE封装制作

单击绘图工具盒中的封装向导图标,打开CAE Decal Wizard对 话框,设置如图3所示,封装设计结果如图4所示,最后将结果保存到 JTAG库。

图3 74HC244元件CAE封装向导设置

图19 Grid选项卡设置结果

图20 电源网络显示设置结果

(3)绘制JTAG调试器电路板边框

在PowerPCB设计窗口中,使用绘图工具盒 中的绘制板框与切割加 工区命令 ,绘制一个2200mil*1600mil的矩形电路板边框。 (4)板层设置Layers Setup 在PowerPCB设计窗口中,单击Setup|Layer Definition命令,打开层定 义对话框Layers Setup,如图21所示。软件默认板层是双面板,在顶层 (Top)和底层(Bottom)之间没有任何层出现。

步骤3:在 PowerLogic设计窗口中,通过元件添加调出该元件如图15所 示。

图15 14芯插头添加到设计窗口过程

注:添加14芯插头时,首先单击放置J1-1,然后再次单击依次出现J1- 2、 3-14,最后将所有的插针按照次序放置,这样如图16所示,每一个 J1-n(1、2…)都是一个元件中的一个门。

图16 14芯插头元件添加到设计窗口

第二节 JTAG调试器原理图绘制

图17 JTAG调试器原理图

注:JTAG调试器原理图参加exam14-5-1。

启动PowerLogic设计窗口,单击Tools|OLE PowerPCB Connection命 令,弹出Connect to PowerPCB对话框。单击New按钮 ,启动新的 PowerPCB窗口,同时弹出OLE动态链接OLE PowerPCB Connection 对话框。单击Design选项卡中的Send Netlist按钮,这时在PowerPCB中 就会看到叠放在原点处的所有元件,如图18所示,网络表传送完成。

JTAG调试器电路板为双面板。

图21 板层设置对话框

(5)Design Rules设置

在PowerPCB设计窗口中,单击Setup|Design Rules命令,弹出如图22 所示的设计规则(Rules)窗口。单击Default打开默认规则对话框如图 23所示。

图22 设计规则对话框

图23 默认规则设置对话框

图31 与外框间距错误提示

6. JTAG调试器电路丝印的调整

在布线完成后,调整元件的参照名等丝印数据。如图16中C2的位置是横 向的,需要调整为正常位置。

7. CAMOUT数据输出

在PowerPCB设计环境中,单击File|CAM命令,弹出CAM文档定义窗 口。在CAM栏目下选择<Creat>,在弹出对话框中输入JTAG后单击 OK,使得JTAG成为当前目录。在CAM文档定义窗口中,单击Add弹出 Add Document窗口,定义输出文件。