VLSI系统设计6

集成电路设计基础第11章数字集成vlsi系统设计基础

通过对时序逻辑电路的输入、输出及状态进行分析,了解其工作原理和特性。

时序逻辑电路设计

根据实际需求,选用合适的触发器和组合逻辑电路,设计出满足特定功能的时序逻辑电路。同时 需要考虑时序问题,确保电路的正确性和稳定性。

03

数字集成VLSI系统关键技术

高性能计算技术

并行处理技术

通过多核处理器、GPU加速等技术提高计算能力。

逻辑综合

将HDL代码转换为门级网表,优化电路性能并降低功 耗。

布局布线

根据电路需求和工艺要求,将门级网映射到具体的 芯片上,实现电路的物理实现。

时序分析

对布局布线后的电路进行时序分析,确保电路时序的 正确性和性能。

仿真验证与测试方法

前仿真

在电路设计阶段进行仿真验证, 检查电路功能和性能是否符合设 计要求。

THANKS

感谢观看

集成电路设计基础第11章数 字集成vlsi系统设计基础

• 数字集成VLSI系统概述 • 数字集成VLSI系统基本原理 • 数字集成VLSI系统关键技术 • 数字集成VLSI系统实现方法

• 数字集成VLSI系统应用实例 • 数字集成VLSI系统前沿研究动态

01

数字集成VLSI系统概述

定义与发展历程

柔性电子在数字集成VLSI中潜在价值

柔性电子器件

利用柔性基底和可弯曲的电 子材料制造柔性电子器件, 实现可穿戴、可折叠的数字

集成VLSI系统。

生物兼容性

柔性电子具有良好的生物兼 容性,可用于生物医学应用 中与人体紧密接触的电子设

备。

轻量化与便携性

柔性电子器件具有轻量化、 薄型化和可弯曲的特点,便 于携带和集成到各种移动设 备中。

应用领域及市场需求

《VLSI设计》实验指导书

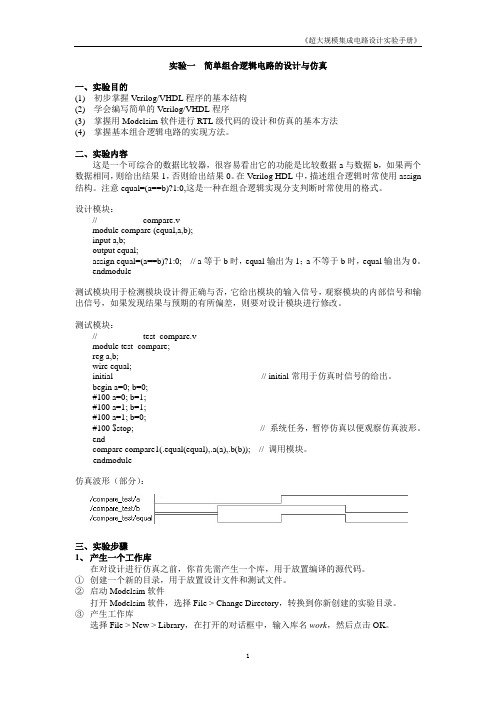

实验一简单组合逻辑电路的设计与仿真一、实验目的(1)初步掌握Verilog/VHDL程序的基本结构(2)学会编写简单的Verilog/VHDL程序(3)掌握用Modelsim软件进行RTL级代码的设计和仿真的基本方法(4)掌握基本组合逻辑电路的实现方法。

二、实验内容这是一个可综合的数据比较器,很容易看出它的功能是比较数据a与数据b,如果两个数据相同,则给出结果1,否则给出结果0。

在Verilog HDL中,描述组合逻辑时常使用assign 结构。

注意equal=(a==b)?1:0,这是一种在组合逻辑实现分支判断时常使用的格式。

设计模块://--------------- compare.v -----------------------module compare (equal,a,b);input a,b;output equal;assign equal=(a==b)?1:0; // a等于b时,equal输出为1;a不等于b时,equal输出为0。

endmodule测试模块用于检测模块设计得正确与否,它给出模块的输入信号,观察模块的内部信号和输出信号,如果发现结果与预期的有所偏差,则要对设计模块进行修改。

测试模块://--------------- test_compare.v-----------------module test_compare;reg a,b;wire equal;initial // initial常用于仿真时信号的给出。

begin a=0; b=0;#100 a=0; b=1;#100 a=1; b=1;#100 a=1; b=0;#100 $stop; // 系统任务,暂停仿真以便观察仿真波形。

endcompare compare1(.equal(equal),.a(a),.b(b)); // 调用模块。

endmodule仿真波形(部分):三、实验步骤1、产生一个工作库在对设计进行仿真之前,你首先需产生一个库,用于放置编译的源代码。

《超大规模集成电路设计》考试习题(含答案)完整版分析

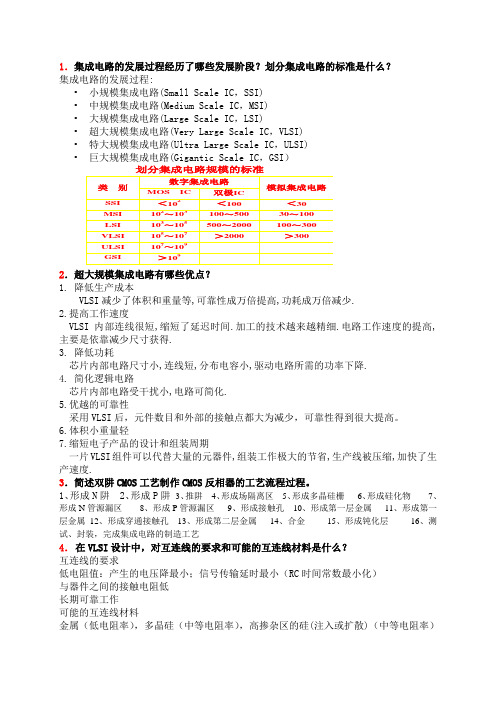

1.集成电路的发展过程经历了哪些发展阶段?划分集成电路的标准是什么?集成电路的发展过程:•小规模集成电路(Small Scale IC,SSI)•中规模集成电路(Medium Scale IC,MSI)•大规模集成电路(Large Scale IC,LSI)•超大规模集成电路(Very Large Scale IC,VLSI)•特大规模集成电路(Ultra Large Scale IC,ULSI)•巨大规模集成电路(Gigantic Scale IC,GSI)划分集成电路规模的标准2.超大规模集成电路有哪些优点?1. 降低生产成本VLSI减少了体积和重量等,可靠性成万倍提高,功耗成万倍减少.2.提高工作速度VLSI内部连线很短,缩短了延迟时间.加工的技术越来越精细.电路工作速度的提高,主要是依靠减少尺寸获得.3. 降低功耗芯片内部电路尺寸小,连线短,分布电容小,驱动电路所需的功率下降.4. 简化逻辑电路芯片内部电路受干扰小,电路可简化.5.优越的可靠性采用VLSI后,元件数目和外部的接触点都大为减少,可靠性得到很大提高。

6.体积小重量轻7.缩短电子产品的设计和组装周期一片VLSI组件可以代替大量的元器件,组装工作极大的节省,生产线被压缩,加快了生产速度.3.简述双阱CMOS工艺制作CMOS反相器的工艺流程过程。

1、形成N阱2、形成P阱3、推阱4、形成场隔离区5、形成多晶硅栅6、形成硅化物7、形成N管源漏区8、形成P管源漏区9、形成接触孔10、形成第一层金属11、形成第一层金属12、形成穿通接触孔13、形成第二层金属14、合金15、形成钝化层16、测试、封装,完成集成电路的制造工艺4.在VLSI设计中,对互连线的要求和可能的互连线材料是什么?互连线的要求低电阻值:产生的电压降最小;信号传输延时最小(RC时间常数最小化)与器件之间的接触电阻低长期可靠工作可能的互连线材料金属(低电阻率),多晶硅(中等电阻率),高掺杂区的硅(注入或扩散)(中等电阻率)5.在进行版图设计时为什么要制定版图设计规则?—片集成电路上有成千上万个晶体管和电阻等元件以及大量的连线。

《超大规模集成电路设计》考试习题(含答案)完整版

1.集成电路的发展过程经历了哪些发展阶段?划分集成电路的标准是什么?集成电路的发展过程:•小规模集成电路(Small Scale IC,SSI)•中规模集成电路(Medium Scale IC,MSI)•大规模集成电路(Large Scale IC,LSI)•超大规模集成电路(Very Large Scale IC,VLSI)•特大规模集成电路(Ultra Large Scale IC,ULSI)•巨大规模集成电路(Gigantic Scale IC,GSI)划分集成电路规模的标准2.超大规模集成电路有哪些优点?1. 降低生产成本VLSI减少了体积和重量等,可靠性成万倍提高,功耗成万倍减少.2.提高工作速度VLSI内部连线很短,缩短了延迟时间.加工的技术越来越精细.电路工作速度的提高,主要是依靠减少尺寸获得.3. 降低功耗芯片内部电路尺寸小,连线短,分布电容小,驱动电路所需的功率下降.4. 简化逻辑电路芯片内部电路受干扰小,电路可简化.5.优越的可靠性采用VLSI后,元件数目和外部的接触点都大为减少,可靠性得到很大提高。

6.体积小重量轻7.缩短电子产品的设计和组装周期一片VLSI组件可以代替大量的元器件,组装工作极大的节省,生产线被压缩,加快了生产速度.3.简述双阱CMOS工艺制作CMOS反相器的工艺流程过程。

1、形成N阱2、形成P阱3、推阱4、形成场隔离区5、形成多晶硅栅6、形成硅化物7、形成N管源漏区8、形成P管源漏区9、形成接触孔10、形成第一层金属11、形成第一层金属12、形成穿通接触孔13、形成第二层金属14、合金15、形成钝化层16、测试、封装,完成集成电路的制造工艺4.在VLSI设计中,对互连线的要求和可能的互连线材料是什么?互连线的要求低电阻值:产生的电压降最小;信号传输延时最小(RC时间常数最小化)与器件之间的接触电阻低长期可靠工作可能的互连线材料金属(低电阻率),多晶硅(中等电阻率),高掺杂区的硅(注入或扩散)(中等电阻率)5.在进行版图设计时为什么要制定版图设计规则?—片集成电路上有成千上万个晶体管和电阻等元件以及大量的连线。

第一章 VLSI设计概论

2011-02-26

VLSI设计

28

28

1.3 今天的IC

半导体业的发展速度 1978年巴黎飞到纽约 的机票价格为900美 元,需要飞7个小时。 如果航空业的发展速度 和半导体业一样的话, 那么今天只需花费1个 便士,不到1秒钟即可 到达!

2011-02-26

VLSI设计

29

29

1.3 今天的IC

2011-02-26

VLSI设计

41

41

1.5 VLSI设计

VLSI设计过程

4、电路设计(Circuit Design) 电路设计是将逻辑设计表达式转换成电路实现。 5、物理设计(Physical Design or Layout Design) 物理设计或称版图设计是VLSI设计中最费时的一步。 它要将电路设计中的每一个元器件包括晶体管、电阻、 电容、电感等以及它们之间的连线转换成集成电路制造 所需要的版图信息。 6、设计验证(Design Verification) 在版图设计完成以后,非常重要的一步工作是版图验 证。主要包括:设计规则检查(DRC)、版图的电路提取 (NE)、电学规则检查(ERC)和寄生参数提取(RPE)。

晶体管的成本

目前制造1个晶体管 的成本大约与在1张 报纸上印制1个字母 的成本相当!

2011-02-26

VLSI设计

30

30

1.3 今天的IC

IC是整个信息产业的火车头

2011-02-26

VLSI设计

31

31

本章纲要

1 2 3 4 5 IC的概念 IC的发展 今天的IC 现代IC设计的特点 VLSI设计

2011-02-26

VLSI设计

35

35

现代VLSI设计-基于IP核的设计第四版课程设计

现代VLSI设计-基于IP核的设计第四版课程设计一、背景介绍现代集成电路设计是电子信息工程学科体系中重要的一环,在现代电子信息领域有着广泛的应用。

随着技术的不断进步,集成度的要求越来越高,逐渐从单个器件转向系统级芯片设计,为此,设计人员要对现代VLSI设计有深入的了解和掌握。

本课程设计基于IP核的设计,旨在通过具体的实际案例,提高学生对现代VLSI设计的理解,并学习如何利用常见IP核优化系统性能,达到减少设计成本、提高设计效率、提高设计可维护性的目的。

二、设计目标本次课程设计的主要目标是掌握VLSI设计的基本原理和流程,学习如何使用IP核进行设计,理解如何对电路进行优化。

三、课程内容3.1 VLSI设计基本原理VLSI(Very Large Scale Integration)是指超大规模集成电路。

VLSI设计主要包括从设计到工艺、测试等多个环节,本部分将学习VLSI设计的基本流程、器件结构、工艺和测试方法等基本知识。

3.2 IP核简介IP核(Intellectual Property)是指独立的设计模块,可以被其他不同的电路利用。

IP核的设计和应用可以大大简化电路设计,提高设计效率和可维护性。

本部分将学习IP核的基本原理、分类和应用场景。

3.3 IP核的设计本部分将围绕基于IP核的设计开展实际操作,涉及IP核的设计和应用。

具体包括如何使用Vivado软件进行IP核的设计和如何利用IP核完成特定功能的设计。

3.4 IP核的优化本部分将介绍如何使用IP核进行电路优化,旨在提高系统设计的性能和可靠性。

具体包括如何对IP核进行定制化、如何进行IP核的性能评估以及如何评估系统的功耗等。

四、课程实践本课程设计将通过实践案例学习VLSI设计、IP核的设计与优化。

4.1 实践案例1:基于IP核的数字信号处理系统设计本案例将指导学生利用IP核进行一个简单的数字信号处理系统设计,包括数据输入输出模块、FIR滤波器模块、FFT模块。

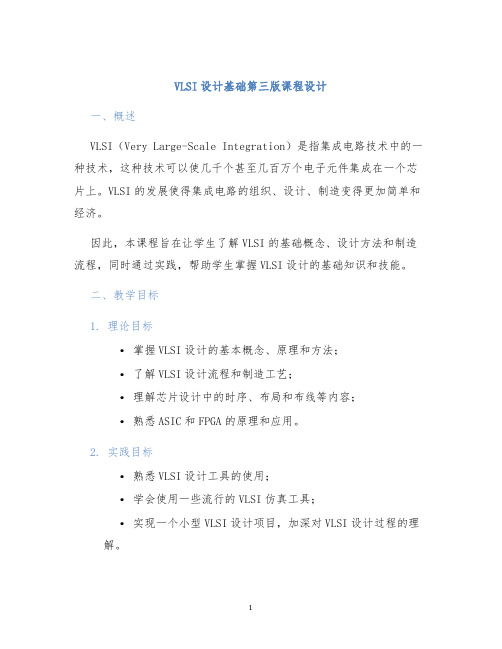

VLSI设计基础第三版课程设计

VLSI设计基础第三版课程设计一、概述VLSI(Very Large-Scale Integration)是指集成电路技术中的一种技术,这种技术可以使几千个甚至几百万个电子元件集成在一个芯片上。

VLSI的发展使得集成电路的组织、设计、制造变得更加简单和经济。

因此,本课程旨在让学生了解VLSI的基础概念、设计方法和制造流程,同时通过实践,帮助学生掌握VLSI设计的基础知识和技能。

二、教学目标1. 理论目标•掌握VLSI设计的基本概念、原理和方法;•了解VLSI设计流程和制造工艺;•理解芯片设计中的时序、布局和布线等内容;•熟悉ASIC和FPGA的原理和应用。

2. 实践目标•熟悉VLSI设计工具的使用;•学会使用一些流行的VLSI仿真工具;•实现一个小型VLSI设计项目,加深对VLSI设计过程的理解。

第一部分:VLSI设计原理1.VLSI概述2.VLSI设计流程3.VLSI芯片设计的基本概念4.芯片布局设计5.芯片布线设计6.阵列设计基础7.数字信号处理器的设计8.软件定义电台的设计9.ASIC设计基础10.FPGA的基本原理和应用第二部分:VLSI设计实践1.FPGA的简单应用2.Verilog HDL及其模块化设计方法3.VHDL语言及其模块化设计方法4.门级元件的设计和实现5.组合逻辑和时序逻辑的设计6.测试的方法和技巧7.系统级仿真本课程将采用以下教学方法:1.理论授课:讲解VLSI设计的基本概念、原理和方法;2.实验实践:通过一些实践操作,将理论知识具体化;3.设计实践:要求学生进行一些小型VLSI设计项目。

五、教学要求1. 学生要求本课程面向电子信息类等专业的学生,建议先修读模拟电子技术、数字电子技术等课程。

因为本课程需要学生具备一定的电路基础知识和编程能力。

2. 教师要求本课程需要教师具备丰富的VLSI设计经验,熟悉VLSI设计流程和常用工具,能够灵活运用各种学习资源,耐心指导学生进行设计项目。

VLSI设计的概述

简

介

Altera集成开发软件,支持Verilog HDL、VHDL和 AHDL 是 ALtera公司继 MAX+ PLUS Ⅱ后新一代开发工具,支持百 万门级设计,适合大规模FPGA开发。软件改善了对第三方 软件的支持。还包含SOPC Builder,可自动添加参数化和 链接IP核,包括嵌入式系统等

2014-4-22 10

路 漫 漫 其 修 远 兮 吾 将 上 下 而 求 索

第1章 VLSI概述

系统级设计

路 漫 漫 其 修 远 兮 吾 将 上 下 而 求 索

混合电路设计

综合与仿真

数字电路设计

EDA工具

模拟电路设计

版图设计

PCB板设计

PLD开发

高速电路设计

图1 – 11

2014-4-22

EDA技术的主要应用范畴

公司名 Cadence Synopsys Mentor Graphics

1999 523.4 491.7 327.8

2000 634.9 415.4 348.9

2001 838.8 332.9 329.8

4

5Avant!ຫໍສະໝຸດ Agilent 全球EDA 市场总计

220.3

50.9 2,274.4

222.3

CAD

2014-4-22

掩模

8

第1章 VLSI概述

①

CAD(Computer Aided Design)阶段

路 漫 漫 其 修 远 兮 吾 将 上 下 而 求 索

CAD阶段:是EDA技术发展的早期阶段。 原因:计算机的功能比较有限(16位),还没有普 及;电子设计软件功能比较弱。 用途:对设计的电路的性能进行一些模拟和预测; 完成PCB板的布局布线及简单的版图绘制。 ② CAE( Computer Aided Engineering)阶段

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

电容变化引起沟 道电荷变化。

Q=CV

和MOS管相比, 工作原理发生变 化。

但仍是四端器件

VLSI系统设计-6 .1 (3)

去除SiO2

MEMS器件

东南大学电子科学与工程学院

6.1 MEMS器件概念

微系统集成的问题

工艺兼容性;

材料复用性; 描述一致性和仿真一致性; 设计复杂性; 处理电路多样性。

东南大学电子科学与工程学院

6.2 集成微系统

3、集成胎压传感器

VLSI系统设计-6 .2 (19)

东南大学电子科学与工程学院

6.2 集成微系统

3、集成胎压传感器

压力使极板间距改变。 导致电容值改变。

VLSI系统设计-6 .2 (20)

东南大学电子科学与工程学院

6.2 集成微系统

4、集成陀螺仪

VLSI系统设计-6 .2 (21)

设计低噪声,抗干扰能力强的微弱信号检测电路 是电容式传感器的关键之一

电容的微小变化量转化为频率,电流,电压… C-F 、 C-I、PWM、C-V (电容电桥、开关电容法、

电荷放大法)

VLSI系统设计-6 .3 (30)

东南大学电子科学与工程学院

6.3 微弱信号处理

C-F方法

充电过程:开关闭合

i c dv dt

T1

C

S V B V A

I1

放电过程:开关断开

T2 CSIV2BI1VA

多谐振荡器 I1<I2

fT21 T1VBIV 1ACS1II1 2

VLSI系统设计-6 .3 (31)

东南大学电子科学与工程学院

6.3 微弱信号处理

东南大学电子科学与工程学院

6.2 集成微系统

4、集成陀螺仪--执行器+传感器

VLSI系统设计-6 .2 (22)

东南大学电子科学与工程学院

6.2 集成微系统

4、集成陀螺仪--执行器+传感器

VLSI系统设计-6 .2 (23)

MEMS陀螺

东南大学电子科学与工程学院

6.2 集成微系统

4、集成陀螺仪--执行器+传感器

东南大学电子科学与工程学院

6.3 微弱信号处理

噪声处理—斩波技术

Vchop t

Vchop

Vos+Vn

f fchop

Vos+Vn

Vchop_d t

Vchop_d

Vin

A

VA

VB

Vout

Vin

VA

VB

Vout

f fchop

f fchop

f fchop

f fchop

使用调制技术将信号转到更高的频率,此频段放大器没有1/f

几种简单的MEMS结构

1. 简单梁结构

VLSI系统设计-6 .1 (6)

东南大学电子科学与工程学院

6.1 MEMS器件概念

几种简单的MEMS结构

2. 简单膜结构

VLSI系统设计-6 .1 (7)

东南大学电子科学与工程学院

6.1 MEMS器件概念

几种简单的MEMS结构

3. 多方向运动结构

VLSI系统设计-6 .1 (8)

噪声,然后在经过放大后解调回基带,由于斩波不会提高白噪

声部分,所以斩波更适合低噪声电路。

VLSI系统设计-6 .3 (39)

东南大学电子科学与工程学院

小结:

MEMS技术将微电子技术和精密机械加工技 术相互融合,实现了微电子与机械融为一体的系 统。从广义上讲,MEMS是指集微型传感器、微 型执行器、信号处理和控制电路、接口电路、通 信系统以及电源于一体的微机电系统。

VLSI系统设计-6 .2 (16)

传感器

东南大学电子科学与工程学院

6.2 集成微系统

2、集成加速度传感器

VLSI系统设计-6 .2 (17)

东南大学电子科学与工程学院

6.2 集成微系统

2、集成加速度传感器

静止极板与运动极板 间距因加速度而变。导 致电容大小改变。

VLSI系统设计-6 .2 (18)

VLSI系统设计-6 .1 (11)

东南大学电子科学与工程学院

6.1 MEMS器件概念

多能域问题和复杂性设计问题

单片集成系统 = MEMS + 电路

描述:

力学 热学 电学 光学…..

仿真: FEM / BEM

电学 &

微电子学

KCL / KVL

版图 &

微电子加工工艺

VLSI系统设计-6 .1 (12)

C-I方法

初始情况:Cs上电压为0;

比较器输出为0,M1、M2截

X

止。 有1 效:Cs上电压不能突变,比

1 Vref

CS

较器反相端为Vref ,比较器输出

2

CP

为Vss,M2导通。 Cs放电,比

较器反相端趋于0,输出趋于0,

M2截止。

vdd

Ch arg e current

M1 Y

A3

M2

vss Disch arg e current

差分 VLSI系统设计-6 .3 (34)

东南大学电子科学与工程学院

6.3 微弱信号处理

C-V法 (开关电容法)

在φ1为高电平时,C1和Cref 放电,Cs充 电。此时存储在Cs两端的电荷Qs为:

QS VrefCS

在φ2为高电平时,C1和Cref 充电,Cs放 电。此时存储在Cref 两端的电荷Qref 为:

陀螺结构与原理

哥氏力产生的非振动方 向的运动引起梳齿相对运 动。导致电容值改变。

VLSI系统设计-6 .2 (24)

东南大学电子科学与工程学院

6.2 集成微系统

5、集成数字微镜DMD --执行器

VLSI系统设计-6 .2 (25)

东南大学电子科学与工程学院

6.2 集成微系统

5、集成数字微镜--执行器

MEMS-采样/放大; 调制-解调; 模数变换; 数字信号处理; ……

VLSI系统设计-6 .1 (4)

东南大学电子科学与工程学院

6.1 MEMS器件概念

几种简单的MEMS结构

1. 简单梁结构

VLSI系统设计-6 .1 (5)

东南大学电子科学与工程学院

6.1 MEMS器件概念

VLSI系统设计-6 .3 (40)

东南大学电子科学与工程学院

VLSI系统设计-6 .2 (26)

东南大学电子科学与工程学院

6.2 集成微系统

5、集成数字微镜---6 .2 (27)

东南大学电子科学与工程学院

6.2 集成微系统

5、集成数字微镜--执行器

DMD是MEMS执行器的应 用示例,利用寻址方式控制静 电驱动方式工作。

QrefVrefCref

C1上电荷Q1为:

Q 1 V reC fS C ref

输出电压为:

V o u V r t e C S f C re/C f1

开关电容电路的形式非 常多,但基本原理相同。

VLSI系统设计-6 .3 (35)

东南大学电子科学与工程学院

6.3 微弱信号处理

6.2 集成微系统

1、集成湿度传感器

瑞士Sensirion公司SHT11/15型湿度/温度传感器

VLSI系统设计-6 .2 (14)

东南大学电子科学与工程学院

6.2 集成微系统

1、集成湿度传感器

VLSI系统设计-6 .2 (15)

东南大学电子科学与工程学院

6.2 集成微系统

1、集成湿度传感器

聚合物感湿材料介电 常数随湿度而改变。导 致电容大小改变。

有2 效:Cs放电到0电压。

ISFSVrefCS

VLSI系统设计-6 .3 (32)

东南大学电子科学与工程学院

6.3 微弱信号处理

PWM方法

传感器以差分电容形式变化

VLSI系统设计-6 .3 (33)

东南大学电子科学与工程学院

6.3 微弱信号处理

C-V 法(电容电桥法)

Vou t RSR 2R2R1R 3R3E

VLSI系统设计-6 .2 (28)

东南大学电子科学与工程学院

6.3 微弱信号处理

电容检测 压阻检测 压电检测 隧道检测 热流式检测技术 谐振式检测技术 光纤式检测技术

VLSI系统设计-6 .3 (29)

东南大学电子科学与工程学院

6.3 微弱信号处理

电容检测

传感电容~pf量级,电容变化~af量级 噪声~信噪比问题

VLSI系统设计-6 .3 (37)

东南大学电子科学与工程学院

6.3 微弱信号处理

载波调制方法—双路载波

两路电荷求和

V ou tC C S f1V inC C S f2V inC S1C fC S2V in

采用高频载波进行调制,可以有效避开1/f 噪声 对电路的影响

VLSI系统设计-6 .3 (38)

VLSI系统设计

第6章 集成微系统(MEMS)

(2019-2019)

VLSI系统设计-6

东南大学电子科学与工程学院

6.1 MEMS器件概念

一个例子:NMOSFET→谐振栅晶体管(RGT)

VLSI系统设计-6 .1 (2)

东南大学电子科学与工程学院

6.1 MEMS器件概念

一个例子:NMOSFET→谐振栅晶体管(RGT)

C-V法(电荷放大法)

VO

Qi Cf

CSVi Cf

dVO 1

dQi

Cf

电阻的作用是为运放提供直流反馈,使得反相输入为零。

VLSI系统设计-6 .3 (36)