计算机原理复习

计算机原理复习题

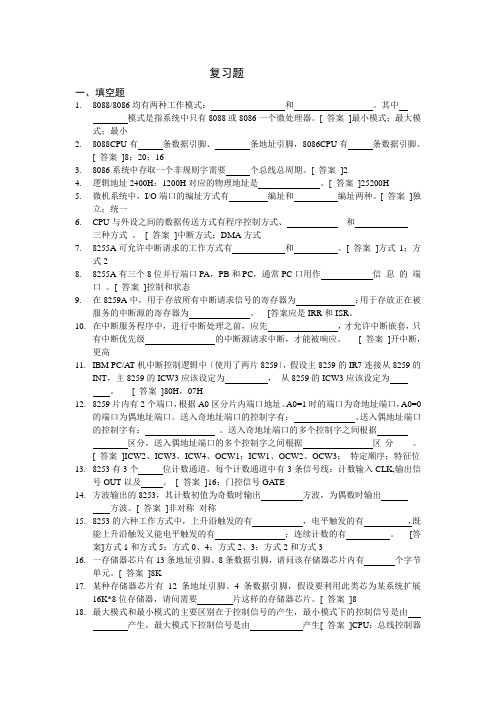

复习题一、填空题1.8088/8086均有两种工作模式:和。

其中模式是指系统中只有8088或8086一个微处理器。

[ 答案]最小模式;最大模式;最小2.8088CPU有条数据引脚、条地址引脚,8086CPU有条数据引脚。

[ 答案]8;20;163.8086系统中存取一个非规则字需要个总线总周期。

[ 答案]24.逻辑地址2400H:1200H对应的物理地址是。

[ 答案]25200H5.微机系统中,I/O端口的编址方式有编址和编址两种。

[ 答案]独立;统一6.CPU与外设之间的数据传送方式有程序控制方式、和三种方式。

[ 答案]中断方式;DMA方式7.8255A可允许中断请求的工作方式有和。

[ 答案]方式1;方式28.8255A有三个8位并行端口PA,PB和PC,通常PC口用作信息的端口。

[ 答案]控制和状态9.在8259A中,用于存放所有中断请求信号的寄存器为;用于存放正在被服务的中断源的寄存器为。

[答案应是IRR和ISR。

10.在中断服务程序中,进行中断处理之前,应先,才允许中断嵌套,只有中断优先级的中断源请求中断,才能被响应。

[ 答案]开中断,更高11.IBM PC/AT机中断控制逻辑中〔使用了两片8259〕,假设主8259的IR7连接从8259的INT,主8259的ICW3应该设定为,从8259的ICW3应该设定为。

[ 答案]80H,07H12.8259片内有2个端口,根据A0区分片内端口地址。

A0=1时的端口为奇地址端口,A0=0的端口为偶地址端口。

送入奇地址端口的控制字有:。

送入偶地址端口的控制字有:。

送入奇地址端口的多个控制字之间根据区分,送入偶地址端口的多个控制字之间根据区分。

[ 答案]ICW2、ICW3、ICW4、OCW1;ICW1、OCW2、OCW3;特定顺序;特征位13.8253有3个位计数通道,每个计数通道中有3条信号线:计数输入CLK,输出信号OUT以及。

[ 答案]16;门控信号GA TE14.方波输出的8253,其计数初值为奇数时输出方波,为偶数时输出方波。

计算机组成原理复习资料

一、单项选择题:

1虚地址是( )。

A、不存在的地址

B、用户编程可使用的地址

C、主存地址

D、磁盘地址

2、在机器数()中,零的表示形式是惟一的。

A、原码

B、补码

C、反码

D、原码和反码

3、挂接在总线上的多个部件( )。

A、只能分时向总线发送数据,并只能分时从总线接收数据

B、可同时向总线发送数据,但只能分时从总线接收数据

12、按产生控制信号的方式不同,控制器可分为________控制器与________控制器。

13、任何一条指令的执行都要经过________、________和________三个阶段。

14、按数据传送方式,接口可分为________接口与________接口。按时序控制方式分类,接口要分为________接口与________接口。

2、计算机系统是一种________,用于控制和管理计算机系统的资源,是________的接口。

3、PSW是指令部件中________。

4、1101.1001B=________H

5、主存储器和CPU之间增加高速缓冲器的主要目的是________。

6、使CPU与I/0设备完全并行工作方式是________方式。

7、在CPU中跟踪下一条指令地址的寄存器________。

8、冯.诺依曼机的基本特征是________。

9、每条指令由两部分组成,即________部分和________部分。

10、已知字符A的ASCII码的十进制为41,则字符D的ASCII码的十进制为________。

11、在CPU中,指令寄存器(IR)用来________,它的位数与________有关。

计算机组成原理复习题带答案

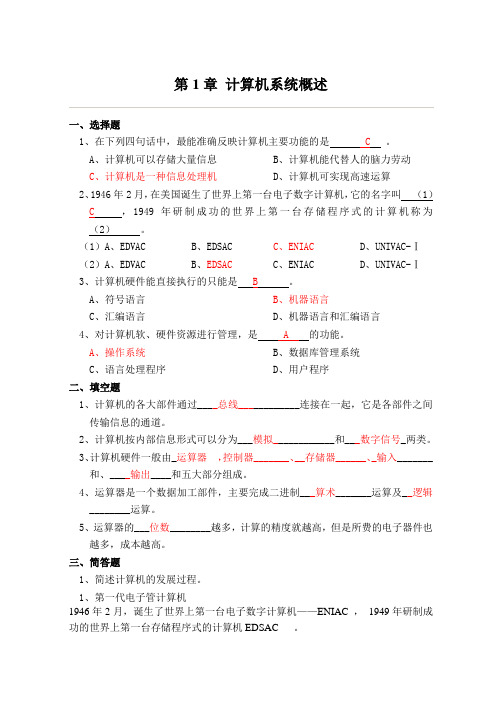

第1章计算机系统概述一、选择题1、在下列四句话中,最能准确反映计算机主要功能的是 C。

A、计算机可以存储大量信息B、计算机能代替人的脑力劳动C、计算机是一种信息处理机D、计算机可实现高速运算2、1946年2月,在美国诞生了世界上第一台电子数字计算机,它的名字叫(1)C,1949年研制成功的世界上第一台存储程序式的计算机称为(2)。

(1)A、EDVAC B、EDSAC C、ENIAC D、UNIVAC-Ⅰ(2)A、EDVAC B、EDSAC C、ENIAC D、UNIVAC-Ⅰ3、计算机硬件能直接执行的只能是B。

A、符号语言B、机器语言C、汇编语言D、机器语言和汇编语言4、对计算机软、硬件资源进行管理,是 A 的功能。

A、操作系统B、数据库管理系统C、语言处理程序D、用户程序二、填空题1、计算机的各大部件通过____总线____________连接在一起,它是各部件之间传输信息的通道。

2、计算机按内部信息形式可以分为___模拟____________和___数字信号_两类。

3、计算机硬件一般由_运算器,控制器_______、__存储器______、_输入_______和、____输出____和五大部分组成。

4、运算器是一个数据加工部件,主要完成二进制___算术_______运算及__逻辑________运算。

5、运算器的___位数________越多,计算的精度就越高,但是所费的电子器件也越多,成本越高。

三、简答题1、简述计算机的发展过程。

1、第一代电子管计算机1946年2月,诞生了世界上第一台电子数字计算机——ENIAC ,1949年研制成功的世界上第一台存储程序式的计算机EDSAC 。

2、第二代晶体管计算机1947年在贝尔实验室制成第一个晶体管,进入20世纪50年代全球出现一场以晶体管代替电子管的革命。

3、第三代集成电路计算机4、大规模集成电路计算机5、超大规模集成电路计算机3、冯.诺依曼计算机的特点是什么?它包括哪些主要组成部分?各部分的功能是什么?1、计算机由运算器、存储器、控制器、输入设备和输出设备五大部件组成2、指令和数据以同等的地位存放在存储器内,并可以按地址寻访3、指令和数据均用二进制数表示4、指令由操作码和地址组成。

计算机原理复习题(最终版)

《计算机原理及应用》复习题一、选择题1.当()时,8088CPU工作在最小模式之下。

()A.芯片引线最少B.MN/--MX=0C.MN/--MX=1 D.使用多处理器2、二进制数 10010110.10B 的十进制数值可表示为()A、 96.8B、 150.5C、 96.5D、 160.53.由段寄存器、段偏移地址所确定的物理地址是这样产生的()。

A.物理地址=段寄存器的内容×8+偏移地址B.物理地址=偏移地址×8C.物理地址=段寄存器内容×20+偏移地址D.物理地址=段寄存器内容×16+偏移地址4、RAM 6116芯片有2K×8位的容量,它的片内地址选择线和数据线分别是()A、A0~A15和D0~D15B、A0~A10和D0~D7C、A0~A11和D0~D7D、A0~A11和D0~D155、8086 CPU在响应中断时顺序将()内容压入堆栈。

A、CS.IP.PSWB、IP.CS.PSWC、PSW.CS.IPD、PSW.IP.CS6.若READY为低电平,此时CPU执行哪一个周期?()A.T3周期B.等待的时钟周期TWC.T4周期D.T1周期7.寄存器寻址的操作数包含在()中。

A.CPU的内部寄存器B.内部存贮器C.指令D.外部存贮器8.在CPU内部寄存器之间传送数据(除代码段寄存器CS和指令指针IPC以外)的是()A.ADD B.MOVC.SUB D.MUL9.若要对操作数清0,一般对操作数进行()运算。

A.相与B.相或C.异或D.移位10.外设与内存独立编址方式中,用于外设的指令功能()。

A.较强B.较弱C.与用于内存的指令相同D.以上都不是11、8086能够访问的存储空间的大小是()。

A. 64kB.1MC. 256D.16M12、8253 是可编程定时、计数器芯片,它内部有()。

A、三个定时器B、四个定时器C、二个计数器D、四个计数器13、相邻段地址之间的最小距离为()A、16个字节B、64K字节C、1K字节D、256字节14、8086 CPU的NMI引脚上输入的信号是()A、可屏蔽中断请求B、非屏蔽中断请求C、中断相应D、总线请求15、8086 CPU在()时刻采样READY信号决定是否插入等待周期。

计算机组成原理背诵知识点

计算机组成原理背诵知识点

计算机组成原理涉及的知识点非常广泛,包括但不限于CPU、

存储器、输入输出设备、总线、指令系统、微程序控制、并行处理、操作系统等。

以下是一些常见的知识点:

1. CPU,中央处理器是计算机的核心部件,负责执行指令、数

据处理和控制计算机的操作。

2. 存储器,包括内存和外存,用于存储数据和程序。

3. 输入输出设备,键盘、鼠标、显示器、打印机等,用于与外

部世界进行交互。

4. 总线,连接各个部件的通信通道,包括数据总线、地址总线

和控制总线。

5. 指令系统,CPU执行的指令集合,包括数据传输、算术运算、逻辑运算等指令。

6. 微程序控制,控制指令执行的微操作序列,实现指令的解码

和执行。

7. 并行处理,利用多个处理器同时处理任务,提高计算机的性能。

8. 操作系统,管理计算机硬件和软件资源,提供用户界面和服务。

以上是计算机组成原理中的一些常见知识点,涉及到硬件和软件方面的内容。

希望这些信息能够帮助您更好地理解计算机组成原理。

中职《计算机原理》复习题

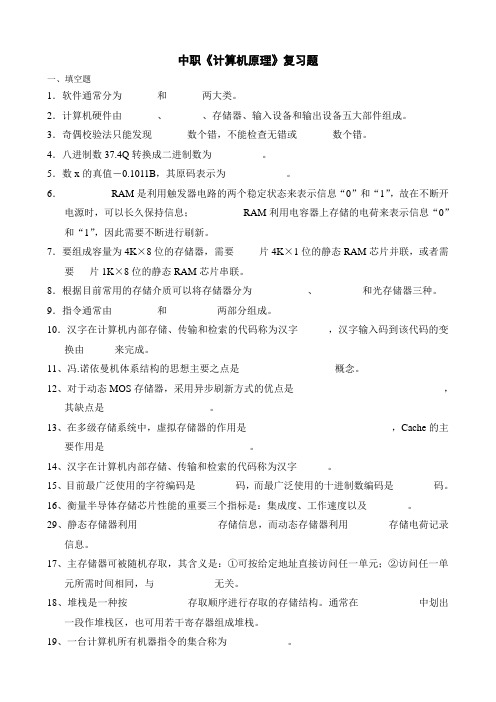

中职《计算机原理》复习题一、填空题1.软件通常分为_______和_______两大类。

2.计算机硬件由_______、_______、存储器、输入设备和输出设备五大部件组成。

3.奇偶校验法只能发现_______数个错,不能检查无错或_______数个错。

4.八进制数37.4Q转换成二进制数为__________。

5.数x的真值-0.1011B,其原码表示为____________。

6.__________RAM是利用触发器电路的两个稳定状态来表示信息“0”和“1”,故在不断开电源时,可以长久保持信息;__________RAM利用电容器上存储的电荷来表示信息“0”和“1”,因此需要不断进行刷新。

7.要组成容量为4K×8位的存储器,需要_____片4K×1位的静态RAM芯片并联,或者需要___片1K×8位的静态RAM芯片串联。

8.根据目前常用的存储介质可以将存储器分为___________、_________和光存储器三种。

9.指令通常由_________和__________两部分组成。

10.汉字在计算机内部存储、传输和检索的代码称为汉字______,汉字输入码到该代码的变换由______来完成。

11、冯.诺依曼机体系结构的思想主要之点是__________________概念。

12、对于动态MOS存储器,采用异步刷新方式的优点是______________________________,其缺点是_____________________。

13、在多级存储系统中,虚拟存储器的作用是_____________________________,Cache的主要作用是_____________________________。

14、汉字在计算机内部存储、传输和检索的代码称为汉字______。

15、目前最广泛使用的字符编码是________码,而最广泛使用的十进制数编码是________码。

《计算机原理》总复习题

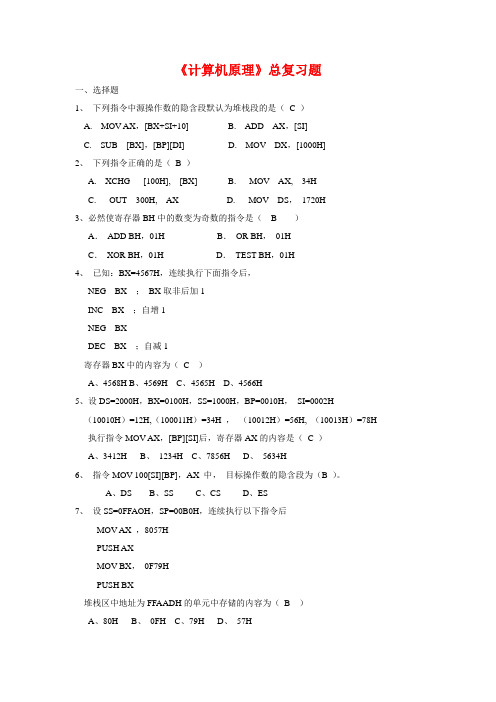

《计算机原理》总复习题一、选择题1、下列指令中源操作数的隐含段默认为堆栈段的是(C )A. MOV AX,[BX+SI+10]B. ADD AX,[SI]C. SUB [BX],[BP][DI]D. MOV DX,[1000H]2、下列指令正确的是(B )A. XCHG [100H], [BX]B. MOV AX, 34HC. OUT 300H, AXD. MOV DS,1720H3、必然使寄存器BH中的数变为奇数的指令是(B)A.ADD BH,01H B.OR BH,01HC.XOR BH,01H D.TEST BH,01H4、已知:BX=4567H,连续执行下面指令后,NEG BX ;BX取非后加1INC BX ;自增1NEG BXDEC BX ;自减1寄存器BX中的内容为( C )A、4568HB、4569HC、4565HD、4566H5、设DS=2000H,BX=0100H,SS=1000H,BP=0010H,SI=0002H(10010H)=12H,(100011H)=34H ,(10012H)=56H, (10013H)=78H 执行指令MOV AX,[BP][SI]后,寄存器AX的内容是(C )A、3412HB、1234HC、7856HD、5634H6、指令MOV 100[SI][BP],AX 中,目标操作数的隐含段为(B )。

A、DSB、SSC、CSD、ES7、设SS=0FFAOH,SP=00B0H,连续执行以下指令后MOV AX ,8057HPUSH AXMOV BX,0F79HPUSH BX堆栈区中地址为FFAADH的单元中存储的内容为( B )A、80HB、0FHC、79HD、57H8、BUF DB 12H DUP (0, 2 DUP (1, 2) , 3)上述语句汇编后,为变量BUF分配的存储单元字节数是( B )A. 60HB. 6CHC. 12HD. 24H9、段定义语句以( B ) 语句结束。

计算机原理复习题

计算机原理复习题习题一、单项选择题1.目前的计算机,从原理上谈c。

a.指令以二进制形式存放,数据以十进制形式存放b.指令以十进制形式存放,数据以二进制形式存放c.指令和数据都以二进制形式存放d.指令和数据都以十进制形式存放2.存储器就是计算机系统的记忆设备,主要用作d。

a.存放程序b.存放软件c.存放微程序d.存放程序和数据3.在cpu中,跟踪后继指令地址的寄存器是b。

a.指令寄存器b.程序计数器c.地址寄存器d.状态条件寄存器4.完备的计算机系统应当包含d。

a.运算器、存储器、控制器b.外部设备和主机c.主机和实用程序d.配套的硬件设备和软件系统5.运算器虽然有许多部件组成,但核心部件是c。

a.数据总线b.多路控制器c.算术和逻辑单元d.寄存器6.中央处理器(cpu)就是指c。

a.运算器b.控制器c.运算器、控制器d.运算器、控制器和内部存储器7.计算机的外围设备是指d。

a.输出/输出设备b.外存储器c.远程通信设备d.除了cpu和内存以外的其它设备二、填空题1.计算机中的指令、数据或状态等信息,它们在的形式上没有区别,都是“0”和“1”组成的数据,但其含义不同。

2.存储程序就是计算机能够自动工作的所在。

计算机不同于的显然区别,是后者的解题步骤(即为程序)就是在机器外由人工干预和掌控的。

3.程序是计算机操作的步骤,它由一条一条的指令组成,每条指令都是计算机可以执行的基本。

数据则是计算机操作的。

4.计算机工作时,其中存有两股信息在流动:一股就是掌控信息,即为微操作命令,其发源地就是,它集中流向各个部件。

另一股就是数据信息,它受到的掌控,从一个部件流向另―个部件,边流动边被加工处置。

5.计算机的硬件与软件已经相辅相成,浑然一体。

从设计制造的角度看,在基本硬件的基础上,软件与硬件在逻辑上是的,是可以互相的。

三、简答题1.计算机的发展历史经历了哪三个发展阶段?2.冯诺依曼思想体制的基本思想是什么?3.控制器应该具有哪两项主要任务?4.计算机系统的层次结构主要包含哪些层次?5.解释下列术语:硬件、软件、总线、机器字长、虚拟机。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

(1)定点原码整数表示 最大正数值=(215-1)10=(+32767)10 最小负数值=-(215-1)10=(-32767)10 (2)定点原码小数表示 最大正数值=(1-2-15)10=(+0.111...11)2 最小负数值=-(1-2-15)10=(-0.111..11)2 注:1符号,15数字

2013-7-25

19

3.2 SRAM存储器

存储体(256×128×8)

通常把各个字的同一个字的同一位集成在一个芯 片(32K×1)中,32K位排成256×128的矩阵。 8个片子就可以构成32KB。 采用双译码的方式(减少选择线的数目)。 A0~A7为行地址译码线 A8~A14为列地址译码线

地址译码器

2013-7-25

20

多个用户共享主存时,系统应提供存储保护。 通常采用的方法是存储区域 保护和访问方式 保护,并用硬件来实现。

2013-7-25

21

例1P70:图3.5(a)是SRA的写入时序图。其中R/W是 读/写命令控制线,当R/W线为低电平时,存储器按 给定地址把数据线上的数据写入存储器。请指出图 3.5(a)写入时序中的错误,并画出正确的写入时序图。

2013-7-25 3

例9 假设由S,E,M三个域组成的一个32位二进制字所表示的非零规 格化浮点数x,真值表示为(非IEEE754标准): x=(-1)s×(1.M)×2E-128 问:它所表示的规格化的最大正数、最小正数、最大负数、最小负数 是多少?

2013-7-25

(1)最大正数 0 1111 1111 111 1111 1111 1111 1111 1111 x=[1+(1-2-23)]×2127 (2)最小正数 000 000 000000 000 000 000 000 000 000 00 x=1.0×2-128 (3)最小负数 111 111 111111 111 111 111 111 111 111 11 x=-[1+(1-2-23)]×2127 (4)最大负数 100 000 000000 000 000 000 000 000 000 00 x=-1.0×2-128

原因是什么呢?

[ x y ]移 [ x ]移 [ y ]补 [ y ]移 [ x ]补

2013-7-25

(mod 2 n 1 )

11

2.6.2 浮点乘法和除法运算

移码采用双符号位,为了对溢出进行判断 01 为正 00 为负 10 上溢 11 下溢

x=+011,y=+110,求[x+y]移 和 [x-y]移,并判断是否溢出。

计算机原理复习

2013-7-25

1

[例7]将十进制真值(-127,-1,0,+1, +127)列表表示成二进制数及原码、 反码、补码、移码值。

2013-7-25

2

[例8]设机器字长16位,定点表示,尾数15位,数 符1位,问:(1)定点原码整数表示时,最大正数 是多少?最小负数是多少?(2)定点原码小数表 示时,最大正数是多少?最小负数是多少?

2013-7-25

2.6.2 浮点乘法和除法运算

设有浮点数x=2-5×0.0110011,y= 23×(-0.1110010),阶码用4位移码表示,尾数 (含符号位)用8位补码表示。求[x×y]浮。要 求用补码完成尾数乘法运算,运算结果尾数保 留高8位(含符号位),并用尾数低位字长值处理 舍入操作。

[x]移=01 011, [y]补=00 110, [-y]补=11 010 [x+y]移=[x]移+[y]补=10 001, 结果上溢。 [x-y]移=[x]移+[-y]补=00 101, 结果正确,为-3。

2013-7-25 12

2.6.2 浮点乘法和除法运算

尾数处理

截断 舍入 尾数用原码表示时

解:点击上图

2013-7-25 22

3.3 DRAM存储器

2013-7-25

23

3.3 DRAM存储器

五、存储器容量的扩充 1、字长位数扩展 给定的芯片字长位数较短,不满足设计要求的存 储器字长,此时需要用多片给定芯片扩展字长位数。 三组信号线中,地址线和控制线公用而数据线单独分 开连接。 d=设计要求的存储器容量/选择芯片存储器容量 [例2] 利用1M×4位的SRAM芯片,设计一个存储容量 为1M×8位的SRAM存储器。 解:所需芯片数量=(1M×8)/(1M×4)=2片

解:顺序存储器和交叉存储器连续读出m=4个字的信息 总量都是: q=64b×4=256b 顺序存储器和交叉存储器连续读出4个字所需的时间分 别是: t2=mT=4×200ns=800ns=8×10-7s t1=T+(m-1)=200ns+350ns=350ns=35×10-7s 顺序存储器和交叉存储器的带宽分别是: W2=q/t2=256b÷(8×10-7)s=320Mb/s W1=q/t1=256b÷(35×10-7)s=730Mb/s

2013-7-25 27

3.6 Cache存储器

cache基本原理小结: cache是介于CPU和主存M2之间的小容量存储器,但存取速度比 主存快。主存容量配置几百MB的情况下,cache的典型值是几百 KB。cache能高速地向CPU提供指令和数据,从而加快了程序的 执行速度。从功能上看,它是主存的缓冲存储器,由高速的SRAM 组成。为追求高速,包括管理在内的全部功能由硬件实现,因而 对程序员是透明的。 Cache的设计依据:CPU这次访问过的数据,下次有很大的可能也 是访问附近的数据。 CPU与Cache之间的数据传送是以字为单位 主存与Cache之间的数据传送是以块为单位 CPU读主存时,便把地址同时送给Cache和主存,Cache控制逻辑 依据地址判断此字是否在Cache中,若在此字立即传送给CPU , 否则,则用主存读周期把此字从主存读出送到CPU,与此同时, 把含有这个字的整个数据块从主存读出送到cache中。

10

2013-7-25

2.6.2 浮点乘法和除法运算

浮点数的阶码运算(移码的运算规则) [X]移+[Y]移=2n+[X+Y]移

[ x y ]移 [ x ]移 [ y ]移 2 n [ x ]移 [ y ]补 [ y ]移 [ x ]补 (mod 2 n 1 )

1、0操作数检查(非0) 2、对阶:阶码对齐后才能加减。规则是阶码小的向阶码大的数 对齐; 若△E=0,表示两数阶码相等,即Ex=Ey; 若△E>0,表示Ex>Ey; 若△E<0,表示Ex>Ey。 当Ex≠Ey 时,要通过尾数的移动以改变Ex或Ey,使之相 等。

2013-7-25

6

2.6.1 浮点加法、减法运算

按信息的可保存性分类:永久性和非永久性的 按存储器系统中的作用分类:主/辅/缓/控

17

2013-7-25

3.1.2 存储器分级结构

分层存储器系统之间的连接关系

2013-7-25

18

3.2 SRAM存储器

主存(内部存储器)是半导体存储器。根据信 息存储的机理不同可以分为两类:

静态读写存储器(SRAM):存取速度快 动态读写存储器(DRAM):存储容量不如DRAM大。

2013-7-25 25

3.3 DRAM存储器

[例4] CDRAM内存条组成实例。 一片CDRAM的容量为1M×4位,8片这样 的芯片可组成1M×32位4MB的存储模块,其 组成如下图所示。

2013-7-25

26

例5 设存储器容量为32字,字长64位,模块数m=4,分别用顺序方式 和交叉方式进行组织。存储周期T=200ns,数据总线宽度为64位,总 线传送周期=50ns。若连续读出4个字,问顺序存储器和交叉存储器 的带宽各是多少?

2013-7-25 9

2.6.2 浮点乘法和除法运算

① ② ③ ④

设有两个浮点数x和y: x=2Ex·x M y=2Ey·y M x×y=2(Ex+Ey)· x×My) (M x÷y=2(Ex-Ey)· x÷My) (M 乘除运算分为四步

0操作数检查 阶码加减操作 尾数乘除操作 结果规格化和舍入处理

2013-7-25

14

[解:] 移码采用双符号位,尾数补码采用单符号位,则有 [Mx]补=0.0110011, [My]补=1.0001110, [Ey]移=01 011, [Ey]补=00 011, [Ex]移=00 011, [x]浮=00 011, 0.0110011, [y]浮=01 011, 1.0001110 (1)判断操作是否为”0”,求阶码和 [Ex+Ey]移=[Ex]移+[Ey]补=00 011+00 011=00 110, 值为移码形式-2。 (2) 尾数乘法运算可采用补码阵列乘法器实现,即有 [Mx]补×[My]补=[0.0110011]补×[1.0001110]补 =[1.1010010,1001010]补 (3) 规格化处理 乘积的尾数符号位与最高数值位符号相同,不是规格化的数,需 要左规,阶码变为00 101(-3), 尾数变为 1.0100101,0010100。 (4) 舍入处理 尾数为负数,取尾数高位字长,按舍入规则,舍去低位字长,故 尾数为1.0100101 。 最终相乘结果为 [x×y]浮=00 101,1.0100101 其真值为 2013-7-25 15 x×y=2-3×(-0.1011011)

2013-7-25 8

2.6.1 浮点加法、减法运算

[x]浮=0001,00.1101 [y]浮=0011,11.0110 阶差=1110 即为-2 Mx应当右移2位, [x]浮=0011,00.0011(01) 尾数和为11.1001(01) 左规11.0010(10),阶码减1为0010 舍入(就近舍入)11.0011 丢弃10 x+y=-0.1101*210