vcs常用命令

VCS异地容灾常用命令

VCS异地容灾的常用命令1. VM相关命令如下1、查看配置结果:#vxdisk list#vxdisk path2、查看磁盘信息:#fdisk -l3、查看磁盘使用情况:#df -h4、查看文件系统跟磁盘的关系# more /etc/vfstab5、磁盘vxdisk 管理配置:# vxdiskadm6、卷标查看:# vxassist list7、VEA磁盘界面配置命令:#vea8、创建Disk Group# vxdisksetup -if sdb(设备名称)9、初始化Disk Group内磁盘# vxdg init netnumendg lv01=sdb10、在Disk Group内磁盘上创建卷标#/usr/sbin/vxassist -g netnumendg -b make netnumen 30g layout=nostripe11、创建文件系统# newfs mkfs -t vxfs /dev/vx/rdsk/netnumendg/netnumen12、查看机器设备信息:# devfsadm -C# cfgadm -al2. RVG相关命令如下1. 查看双机RVG的状态:#vradmin -l printrvg#vradmin -g netnumendg repstatus netnumenrvg2. RVG主备切换:#vradmin -g netnumendg migrate netnumenrvg3. RVG出现双主状态时修复命令:#vradmin -g netnumendg fbsync netnumenrvg执行后,原先的备机将变成主机。

4. RVG启动和停止Replication#vradmin -g netnumendg -f startrep netnumenrvg# vradmin -g netnumendg -f stoprep netnumenrvg5. 核实VVR Replicatikon State#vxprint -g netnumendg netnumenrvg6. 创建主RVG# vradmin -g netnumendg createpri netnumenrvg netnumen_vol,emsoracle_vol,emsuep_vol,emsn31_vol,emscn_vol,SPN_FMS_vol,emsnmsi_vol, srl_vol7. 添加副RVG# vradmin -g netnumendg addsec netnumenrvg 错误!未找到引用源。

vcs使用手册

vcs使用手册版本控制系统(Version Control System,简称VCS)是软件开发中非常重要的工具,用于管理和跟踪代码的版本和变更。

本手册将介绍VCS的基本概念、常用命令和最佳实践,以帮助开发人员更好地使用版本控制系统。

一、基本概念1. 仓库(Repository)仓库是VCS存储代码的地方,包括所有版本的代码和历史记录。

2. 分支(Branch)分支是仓库中的一个独立的代码副本,用于开展不同的开发工作,例如新功能开发、修复bug等。

3. 提交(Commit)提交是对代码进行的修改操作,每次提交都会记录代码的状态和变更信息。

4. 标签(Tag)标签是用于标记特定版本的标识符,通常用于发布版本。

二、常用命令1. 初始化仓库:`git init`2. 添加文件到仓库:`git add <file>`3. 提交变更:`git commit -m "commit message"`4. 查看提交历史:`git log`5. 切换分支:`git checkout <branch>`6. 创建分支:`git branch <branch>`7. 合并分支:`git merge <branch>`8. 标签管理:`git tag <tag>`9. 查看标签:`git tag`10. 推送分支到远程仓库:`git push origin <branch>`11. 拉取远程仓库的分支:`git pull origin <branch>`三、最佳实践1. 遵循简洁的提交信息:在提交信息中简要描述变更内容,方便日后查看和理解。

2. 分支管理规范:合理使用分支,避免在主分支上进行日常开发,及时合并分支。

3. 定期推送和拉取代码:保持本地仓库与远程仓库同步,避免出现冲突。

4. 使用标签管理版本:为每个发布版本打上标签,方便回溯和发布。

VCS维护命令

# /sbin/lltconfig

在运行的话,会显示

LLT /gabconfig –a

1 启动图形界面

# hagui &

用户名/密码: admin/password 进入图形管理界面

2 查看资源组和资源状态

# hastatus

要按 ctrl+c 退出查看模式

或者使用 hastatus -sum 看简要模式。

3 启动资源组

# hagrp -online 资源组名(可用命令2 查到) -sys 系统名(dbsrv1)

4 停止资源组

# hagrp -offline 资源组名(可用命令2 查到) -sys 系统名(dbsrv1)

8 关闭配置模式

# haconf -dump -makero

9 停止双机软件和服务

# hastop -all -force

10 启动双机软件和服务组(在2台主机上都要执行)

# hastart

�

a.查看vcs的进程

# ps –ef | grep ha

会有had,hashadow两个进程

b.启动vcs的图形界面

# /opt/VRTSvcs/bin/hagui &

按照提示输入:用户,passwd(缺省用户:admin,缺省passwd:password)

c.看vcs的启动状态

# /opt/VRTSvcs/bin/hastatus

d.手动启动vcs

# /opt/VRTSvcs/bin/hastart (两台主机上都要运行)

e.手动停止vcs

# /opt/VRTSvcs/bin/hastop(两台主机上都要运行)

vcs使用——精选推荐

vcs使⽤(⼀)编译$vcs file_name 加各种开关选项1.基本选项-Mupdate :增量编译再次编译时只编译改变的⽂件-R :编译后继续进⾏仿真-gui :打开DVE图形界⾯-l<filename>:set log file name,⽤于写编译信息⽣成log⽂件⼀般在仿真⼤型⽂件时⽤到-sverilog :⽀持system verilog 语⾔+v2k :⽀持verilog语⾔2.⼯艺库相关选项-v lib_file :RTL代码⾥涉及到这个⼯艺库-y dir_file :告诉vcs去哪⾥找这个⼯艺库⼯艺库的路径+libext+lib_ext :当⽤到很多库,代替-v+incdir+inc_dir :代码⾥如果有include,使⽤这个命令告诉vcs包含⽂件的位置。

verilog代码⾥⾯写`include "filename.vh" 3.⽂件可选项-f file :有很多⽂件时把多个⽂件整合到这⼀个⽂件夹中4.修改⽂件名-o foo :修改可执⾏⽂件的名字⽂件原名为simv⽂件5.define 定义⼀个宏+define +<macro_name>=<value> :macro_name 宏名;value 初始化值;如+define+INCR_COUNTER(⼆)仿真$simv 加⼀些仿真开关选项./sim -gui &(./指在当前⽂件,sim指编译得到的可执⾏⽂件,gui指打开vcs的gui界⾯-dve,&指后台执⾏)将会得到执⾏的PID值 -s 结束仿真时间$plusargs()动态接收参数-E echo-l logfile 把仿真信息写⼊logfile⽂件⾥(三)VCS Debug的三种⽅法1.系统任务法 system task calls $display 打印变量赋值前值 $montor 打印变量赋值后值,变量值改变,打印值也变 $time 仿真时间 $readmemb 将⽂件⾥的内容读⼊存储器中,读⼆进制binary $readmemh 将⽂件⾥的内容读⼊存储器中,读⼗六进制hexadmecimal2.UCLI命令⾏法$vcs filename +v2k -ucli -R 3.VCS DVE。

VCS命令详解(一):编译命令

VCS命令详解(⼀):编译命令VCS仿真命令详解本⽂中所有命令基于VCS2014版编译时候的命令(按字母排序)A-ams:允许在VCS两步模式下使⽤Verilog-AMS代码。

-ams_discipline <discipline_name>:在VCS两步模式下,指定VerilogAMS中的默认离散规则。

-ams_iereport:在VCS 两步模式下提供⾃动插⼊的连接模块(AICM)信息。

-as :指定备⽤汇编器。

仅适⽤于增量编译模式,这是默认设置。

IBM RS / 6000 AIX不⽀持。

-ASFLAGS :将选项传递给汇编器。

IBM RS / 6000 AIX不⽀持。

-assert <keyword_argument>keyword_argument如下disable_cover:禁⽤SVA覆盖率的报表。

dumpoff:禁⽌在VPD波形⽂件中存储SVA信息。

dve:在您加载到DVE中的VPD⽂件中启⽤SystemVerilog断⾔跟踪。

通过此跟踪,您可以查看断⾔图。

enable_diag:使⽤运⾏时选项进⼀步控制SystemVerilog断⾔结果报告。

filter_past:忽略包含尚未超过历史记录阈值的过去运算符的SystemVerilog断⾔⼦序列。

vpiSeqBeginTime:使您能够查看使⽤Debussy时SystemVerilog断⾔序列开始的仿真时间。

vpiSeqFail:使您可以查看使⽤Debussy时SystemVerilog断⾔序列不匹配的仿真时间。

+acc + 1 | 2 | 3 | 4旧样式的⽅法可在整个设计中启⽤PLI ACC功能。

1启⽤除断点和延迟注释之外的所有功能。

2启⽤1启⽤的功能,再加上⽹络和寄存器的值更改的断点。

3启⽤2启⽤加上模块路径延迟注释。

4启⽤3启⽤加上门延迟注释。

+ad = <分区⽂件名>:指定⽤于混合信号仿真的分区⽂件。

vcs常用命令

SYNOPSYS VCS常用命令使用详解(2013-01-18 09:28:08)转载▼分类:工具标签:vcs杂谈VCS对verilog模型进行仿真包括两个步骤:1. 编译verilog文件成为一个可执行的二进制文件命令为:vcs source_files2. 运行该可执行文件:./simv类似于NC, 也有单命令行的方式:vcs source_files -R-R 命令表示, 编译后立即执行。

vcs常用的命令选项如下:-cm line|cond|fsm|tgl|obc|path 设定coverage的方式+define+macro=value+ 预编译宏定义-f filename RTL文件列表+incdir+directory+ 添加include 文件夹-I 进入交互界面-l logfile文件名-P pli.tab 定义PLI的列表(Tab)文件+v2k 使用推荐的标准-y 定义verilog的库-notice 显示详尽的诊断信息-o 指定输出的可执行文件的名字,缺省是simv+ nospecify 不对SPECIFY 模块进行时序检查和路径延时计算+ notimingcheck 不进行时序检查;但是还是把path延时加入仿真中Summary of vcs compile options:-ASFLAGS "opts" pass 'opts' to the assembler-B generate long call instructions in native assembly code (HP only)-CC "opts" pass 'opts' to C compiler-CFLAGS "opts" pass 'opts' to C compiler-LDFLAGS "opts" pass 'opts' to C compiler on load line only-I enable interactive/postprocessing debugging capabilities-ID get host identification information-M enable incremental compilation (see manual)-Mupdate enable incremental compilation and keep the Makefile up-to-date-Marchive[=N] create intermediate libs to reduce link line length; N objs per lib-P plitab compiles user-defined pli definition table 'plitab' -PP enable optimizer postprocessing capabilities for vcd+-R after compilation, run simulation executable-RI after compilation, run simulation under xvcs (Implies -I)-RIG run simulation under xvcs without compiling (executable has to exist)-RPP run xvcs in postprocessing mode (requires file created by vcdpluson)-V[t] verbose mode; with 't', include time information -as foo use foo as the assembler-cc foo use foo as the C compiler-cpp foo use foo as the C++ compiler-e specify the name of your main() routine. (see manual section 7-11 for more details).-f file reads 'file' for other options-gen_c generate C code (for HP and Sun, default is-gen_obj)-gen_asm generate native assembly code (HP and Sun only) -gen_obj generate native object code (HP and Sun only)-ld foo use foo as the linker. (refer vcs manual for compatibility with -cpp option)-line enable single-stepping/breakpoints for source level debugging-lmc-swift include lmc swift interface-lmc-hm include lmc hardware modeler interface-vera add VERA 4.5+ libraries-vera_dbind add VERA 4.5+ libraries for dynamic binding-location display full pathname to vcs installation for this platform.-vhdlobj generate a vhdl obj for simulating in a vhdl design-mixedhdl include MixedHDL-1.0 interface-mhdl include MixedHDL-2.0 interface and library-q quiet mode-platform. display name of vcs installation subdirectory for this platform.-syslib 'libs' specify system libraries (placed last on the link line) eg -lm-o exec name the executable simulation model 'exec' (default is 'simv')-u treat all non text string characters as uppercase-v file search for unresolved module references in'file'-y libdir search for unresolved module references in directory 'libdir'+acc enable pli applications to use acc routines (see manual)+ad include anlog simulation interface and library+adfmi="files" ADFMI support for vcs-ace+cliedit enable command line edit/recall (seedoc/readline.ps)+cli enable command line interactive debugging (see manual)+cmod Enabling cmodule feature+cmodext+cmodext Changing cmodule extension to cmodext+cmodincdir+cmoddir Cmodule Include directory+cmoddefine+macro define cmodule source 'macro' in the form. of XX=YY+define+macro define hdl source 'macro' to have value "macro" +plusarg_save hardwire the plusargs, which follow this flag, into simv+plusarg_ignore turn off +plusarg_save+prof tells vcs to profile the the design and generate vcs.prof file+race tells vcs to generate a report of all race conditions and write this report in the race.out file+rad+1 enable level 1 radiant optimizations (See Release Notes)+rad+2 enable level 2 radiant optimizations (See Release Notes)+libext+lext use extension 'lext' when searching library directorys+librescan search from beginning of library list for allundefined mods+incdir+idir for `include files, search directory 'idir' +nospecify suppress path delays and timing checks+notimingchecks suppress timing checks+optconfigfile+foo use 'foo' as the optimization config file (See Release Notes)+vcsd enable the VCS Direct sim kernel interface-cmhelp enable CoverMeter help-cm enable VCS to first run cmSource to instrument the Verilog source files on the command line-cm_all enable VCS to link CoverMeter into the VCS executable in a way that enables all coverages-cm_lineonly enable VCS to link CoverMeter into the VCS executable in a way that only enables line coverage。

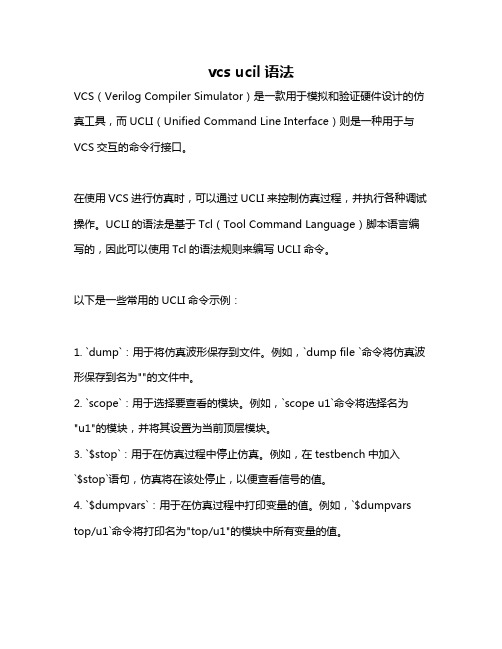

vcs ucil语法

vcs ucil语法

VCS(Verilog Compiler Simulator)是一款用于模拟和验证硬件设计的仿真工具,而UCLI(Unified Command Line Interface)则是一种用于与VCS交互的命令行接口。

在使用VCS进行仿真时,可以通过UCLI来控制仿真过程,并执行各种调试操作。

UCLI的语法是基于Tcl(Tool Command Language)脚本语言编写的,因此可以使用Tcl的语法规则来编写UCLI命令。

以下是一些常用的UCLI命令示例:

1. `dump`:用于将仿真波形保存到文件。

例如,`dump file `命令将仿真波形保存到名为""的文件中。

2. `scope`:用于选择要查看的模块。

例如,`scope u1`命令将选择名为"u1"的模块,并将其设置为当前顶层模块。

3. `$stop`:用于在仿真过程中停止仿真。

例如,在testbench中加入

`$stop`语句,仿真将在该处停止,以便查看信号的值。

4. `$dumpvars`:用于在仿真过程中打印变量的值。

例如,`$dumpvars top/u1`命令将打印名为"top/u1"的模块中所有变量的值。

5. `$set`:用于设置仿真参数。

例如,`$set debug_level 3`命令将设置调试级别为3。

6. `$run`:用于开始仿真。

例如,`$run 100ms`命令将运行仿真100毫秒。

以上是一些常用的UCLI命令示例,但UCLI还提供了许多其他命令和功能,可以根据需要进行学习和使用。

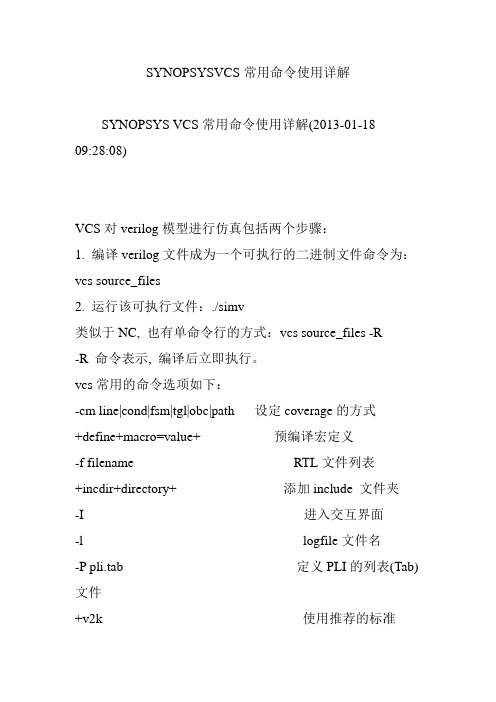

SYNOPSYSVCS常用命令使用详解

SYNOPSYSVCS常用命令使用详解SYNOPSYS VCS常用命令使用详解(2013-01-1809:28:08)VCS对verilog模型进行仿真包括两个步骤:1. 编译verilog文件成为一个可执行的二进制文件命令为:vcs source_files2. 运行该可执行文件:./simv类似于NC, 也有单命令行的方式:vcs source_files -R-R 命令表示, 编译后立即执行。

vcs常用的命令选项如下:-cm line|cond|fsm|tgl|obc|path 设定coverage的方式+define+macro=value+ 预编译宏定义-f filename RTL文件列表+incdir+directory+ 添加include 文件夹-I进入交互界面-l logfile文件名-P pli.tab定义PLI的列表(Tab)文件+v2k 使用推荐的标准-y 定义verilog的库-notice 显示详尽的诊断信息-o 指定输出的可执行文件的名字,缺省是simv+ nospecify 不对SPECIFY 模块进行时序检查和路径延时计算+ notimingcheck 不进行时序检查;但是还是把path延时加入仿真中Summary of vcs compile options:-ASFLAGS "opts" pass 'opts' to the assembler-B generate long call instructions in native assembly code (HP only)-CC "opts" pass 'opts' to C compiler-CFLAGS "opts" pass 'opts' to C compiler-LDFLAGS "opts" pass 'opts' to C compiler on load line only-I enable interactive/postprocessing debugging capabilities-ID get host identification information-M enable incremental compilation (see manual)-Mupdate enable incremental compilation and keep the Makefile up-to-date-Marchive[=N] create intermediate libs to reduce link line length; N objs per lib-P plitab compiles user-defined pli definition table 'plitab'-PP enable optimizer postprocessing capabilities for vcd+-R after compilation, run simulation executable-RI after compilation, run simulation under xvcs (Implies -I)-RIG run simulation under xvcs without compiling (executable has to exist)-RPP run xvcs in postprocessing mode (requires file created by vcdpluson)-V[t] verbose mode; with 't', include time information-as foo use foo as the assembler-cc foo use foo as the C compiler-cpp foo use foo as the C++ compiler-e specify the name of your main() routine. (see manualsection 7-11 for more details).-f file reads 'file' for other options-gen_c generate C code (for HP and Sun, default is -gen_obj)-gen_asm generate native assembly code (HP and Sun only)-gen_obj generate native object code (HP and Sun only)-ld foo use foo as the linker. (refer vcs manual for compatibility with -cpp option)-line enable single-stepping/breakpoints for source level debugging-lmc-swift include lmc swift interface-lmc-hm include lmc hardware modeler interface-vera add VERA 4.5+ libraries-vera_dbind add VERA 4.5+ libraries for dynamic binding-location display full pathname to vcs installation for this platform.-vhdlobj generate a vhdl obj for simulating in a vhdl design-mixedhdl include MixedHDL-1.0 interface-mhdl include MixedHDL-2.0 interface and library-q quiet mode-platform. display name of vcs installation subdirectory for this platform.-syslib 'libs' specify system libraries (placed last on the link line) eg -lm-o exec name the executable simulation model 'exec' (default is 'simv')-u treat all non text string characters as uppercase-v file search for unresolved module references in 'file'-y libdir search for unresolved module references in directory 'libdir'+acc enable pli applications to use acc routines (see manual)+ad include anlog simulation interface and library+adfmi="files" ADFMI support for vcs-ace+cliedit enable command line edit/recall(see doc/readline.ps)+cli enable command line interactive debugging (see manual)+cmod Enabling cmodule feature+cmodext+cmodext Changing cmodule extension to cmodext+cmodincdir+cmoddir Cmodule Include directory+cmoddefine+macro define cmodule source 'macro' in the form. of XX=YY+define+macro define hdl source 'macro' to have value "macro"+plusarg_save hardwire the plusargs, which follow this flag, into simv+plusarg_ignore turn off +plusarg_save+prof tells vcs to profile the the design and generate vcs.prof file+race tells vcs to generate a report of all race conditions and write this report in the race.out file+rad+1 enable level 1 radiant optimizations (See Release Notes)+rad+2 enable level 2 radiant optimizations (See Release Notes)+libext+lext use extension 'lext' when searching library directorys+librescan search from beginning of library list for all undefined mods+incdir+idir for `include files, search directory 'idir'+nospecify suppress path delays and timing checks+notimingchecks suppress timing checks+optconfigfile+foo use 'foo' as the optimization config file (See Release Notes)+vcsd enable the VCS Direct sim kernel interface-cmhelp enable CoverMeter help-cm enable VCS to first run cmSource to instrument the Verilog source files on the command line-cm_all enable VCS to link CoverMeter into the VCS executable in a way that enables all coverages-cm_lineonly enable VCS to link CoverMeter into the VCS executable in a way that only enables line coverage。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

目前的集群软件很多,在大型系统中应用较广泛的是VCS(全称是Veritas Cluster Server)和Sun Cluster,VCS提供了较开放的定制接口,可以根据自身业务系统的需要定制其监控、启停和倒换的动作,这些属于集群或高可靠系统设计和开发的范畴了,在这之前有必要先熟悉VCS的常用操作,这在后期的维护中也是很常用的。

接下来就一起看看这些命令:

安装加载VCS license

vxlicinst

启动单个节点的VCS服务,如果要启动所有节点的VCS服务,或者说要启动整个集群,那么就需要到集群内各个节点上分别执行hasart

hastart

停止单个节点的业务:

hastop -local

停止整个集群的业务:

hastop -all

只关闭VCS相关进程,而不停止VCS所保护的业务进程:

hastop -local -force (单个节点)

hastop -all -force (整个集群)

查看集群状态:

hastatus

hastat -sum

查看资源状态:

hares -state

查看资源组状态:

hagrp -state

查询指定的资源组service_group状态:

hagrp -state [service_group] -sys [system]

强制VCS读取system上$VCS_CONF/conf/config目录下的配置文件进行启动集群工作:hasys -force systemname

使配置文件可读写:

haconf -makerw

使配置文件只读:

haconf -dump -makero

查询资源resource及其相关参数(hagrp类似):

hares -display [resource]

hares -display -attribute [attribute]

hares -display -group [service_group]

hares -display -type [resource_type]

hares -display -sys [system]

查询主机列表:

hasys -list

hasys -display [system]

haclus -value attribute

haclus –display

查询集群日志:

hamsg -list

hamsg -info [-path path_name] LDF

基本管理操作示例:

启动服务组及使服务联机:

hagrp -online service_group -sys system

关闭服务组及使服务脱机:

hagrp -offline service_group -sys system

将服务组切换到另一个系统上:(只对failover组有效,且当服务组中服务部分或全部联机时):

hagrp -switch service_group -to system

冻结服务组(disable onlining, offlining, and failover),option -persistent 是使cluster重启时freeze:

hagrp -freeze service_group [-persistent]

解冻被冻结的服务组(reenable onlining, offlining, and failover)

hagrp -unfreeze service_group [-persistent]

激活服务组:(服务组激活后才能进行联机操作)

hagrp -enable service_group [-sys system]

禁用服务组:(服务组禁用后不能进行联机或切换操作)

hagrp -disable service_group [-sys system]

激活服务组中资源:

hagrp -enableresources service_group

禁用服务组中资源:(如资源为disable时agents不监控资源组)

hagrp -disableresources service_group

清除故障状态

hagrp -clear [service_group] -sys [system] (资源组)

hares -clear [resource] (资源)

管理资源操作:

使资源服务启动:

hares -online resource -sys system

使资源服务停止:

hares -offline resource -sys system

在ADMIN_W AIT状态下强制主机加载集群,此命令会覆盖正在使用的集群配置,使用前请确认准备使用的主机的集群配置文件是否有效:

hacf –verify /etc/VRTSvcs/conf/concig

hasys -force system

修改主机的属性,一些属性是VCS的内部属性,不能修改:

hasys -modify modify_options

冻结主机(防止主机进行联机或切换操作)

hasys -freeze [-persistent] [-evacuate] system

解冻被冻结的主机(使主机可以进行联机或切换操作)

hasys -unfreeze [-persistent] system

管理集群:

haclus [-help [-modify]]。