COA编程题

c语言编程题经典关于工作工资100例

c语言编程题经典关于工作工资100例C语言是一种非常重要的编程语言,对于计算机专业的学生来说,掌握C语言编程是非常重要的一项技能。

在学习C语言编程的过程中,经典的编程题目是非常有帮助的,特别是关于工作工资的题目,可以帮助学生更好地理解C语言的应用和实际场景中的运用。

以下是关于工作工资的100个经典C语言编程题例:1. 计算员工的基本工资和加班工资;2. 根据销售额计算销售员的提成工资; 3. 根据工作年限计算员工的年终奖; 4. 根据考勤情况计算员工的绩效工资; 5. 根据工作岗位计算员工的岗位工资; 6. 根据工作地点计算员工的地域工资差异; 7. 根据工作性质计算员工的工作性质津贴; 8. 根据学历情况计算员工的学历工资; 9. 根据工龄情况计算员工的工龄工资; 10. 根据职称情况计算员工的职称工资; 11. 根据加班情况计算员工的加班工资; 12. 根据请假情况计算员工的请假工资; 13. 根据出差情况计算员工的出差工资; 14. 根据加班情况计算员工的加班工资; 15. 根据绩效情况计算员工的绩效工资; 16. 根据工作量情况计算员工的工作量工资; 17. 根据工作质量情况计算员工的工作质量工资; 18.根据项目情况计算员工的项目奖金; 19. 根据加班情况计算员工的加班工资; 20. 根据绩效情况计算员工的绩效工资; 21. 根据工作量情况计算员工的工作量工资; 22. 根据工作质量情况计算员工的工作质量工资; 23. 根据项目情况计算员工的项目奖金; 24. 根据加班情况计算员工的加班工资; 25. 根据绩效情况计算员工的绩效工资; 26. 根据工作量情况计算员工的工作量工资; 27. 根据工作质量情况计算员工的工作质量工资; 28. 根据项目情况计算员工的项目奖金; 29. 根据加班情况计算员工的加班工资; 30. 根据绩效情况计算员工的绩效工资; 31. 根据工作量情况计算员工的工作量工资; 32. 根据工作质量情况计算员工的工作质量工资;33. 根据项目情况计算员工的项目奖金; 34. 根据加班情况计算员工的加班工资; 35. 根据绩效情况计算员工的绩效工资; 36. 根据工作量情况计算员工的工作量工资; 37. 根据工作质量情况计算员工的工作质量工资; 38. 根据项目情况计算员工的项目奖金;39. 根据加班情况计算员工的加班工资; 40. 根据绩效情况计算员工的绩效工资; 41. 根据工作量情况计算员工的工作量工资; 42. 根据工作质量情况计算员工的工作质量工资; 43. 根据项目情况计算员工的项目奖金; 44. 根据加班情况计算员工的加班工资; 45. 根据绩效情况计算员工的绩效工资; 46. 根据工作量情况计算员工的工作量工资; 47. 根据工作质量情况计算员工的工作质量工资;48. 根据项目情况计算员工的项目奖金; 49. 根据加班情况计算员工的加班工资; 50. 根据绩效情况计算员工的绩效工资; 51. 根据工作量情况计算员工的工作量工资; 52. 根据工作质量情况计算员工的工作质量工资; 53. 根据项目情况计算员工的项目奖金;54. 根据加班情况计算员工的加班工资; 55. 根据绩效情况计算员工的绩效工资; 56. 根据工作量情况计算员工的工作量工资; 57. 根据工作质量情况计算员工的工作质量工资; 58. 根据项目情况计算员工的项目奖金; 59. 根据加班情况计算员工的加班工资; 60. 根据绩效情况计算员工的绩效工资; 61. 根据工作量情况计算员工的工作量工资; 62. 根据工作质量情况计算员工的工作质量工资;63. 根据项目情况计算员工的项目奖金; 64. 根据加班情况计算员工的加班工资; 65. 根据绩效情况计算员工的绩效工资; 66. 根据工作量情况计算员工的工作量工资; 67. 根据工作质量情况计算员工的工作质量工资; 68. 根据项目情况计算员工的项目奖金;69. 根据加班情况计算员工的加班工资; 70. 根据绩效情况计算员工的绩效工资; 71. 根据工作量情况计算员工的工作量工资; 72. 根据工作质量情况计算员工的工作质量工资; 73. 根据项目情况计算员工的项目奖金; 74. 根据加班情况计算员工的加班工资; 75. 根据绩效情况计算员工的绩效工资; 76. 根据工作量情况计算员工的工作量工资; 77. 根据工作质量情况计算员工的工作质量工资;78. 根据项目情况计算员工的项目奖金; 79. 根据加班情况计算员工的加班工资; 80. 根据绩效情况计算员工的绩效工资; 81. 根据工作量情况计算员工的工作量工资; 82. 根据工作质量情况计算员工的工作质量工资; 83. 根据项目情况计算员工的项目奖金;84. 根据加班情况计算员工的加班工资; 85. 根据绩效情况计算员工的绩效工资; 86. 根据工作量情况计算员工的工作量工资; 87.根据工作质量情况计算员工的工作质量工资; 88. 根据项目情况计算员工的项目奖金; 89. 根据加班情况计算员工的加班工资; 90. 根据绩效情况计算员工的绩效工资; 91. 根据工作量情况计算员工的工作量工资; 92. 根据工作质量情况计算员工的工作质量工资;93. 根据项目情况计算员工的项目奖金; 94. 根据加班情况计算员工的加班工资; 95. 根据绩效情况计算员工的绩效工资; 96. 根据工作量情况计算员工的工作量工资; 97. 根据工作质量情况计算员工的工作质量工资; 98. 根据项目情况计算员工的项目奖金;99. 根据加班情况计算员工的加班工资; 100. 根据绩效情况计算员工的绩效工资。

计算机组织与结构 COA考试习题 (6)

Chapter 10 and Chapter 111: In instruction, the number of addresses is 0, the operand(s)’ address is implied, which is(are) in_______.A. accumulatorB. program counterC. top of stackD. any register2. The address of the top of stack is stored in _________________.A. PCB. AccumulatorC. SPD. Base Register3: In index-register addressing mode , the address of operand is equal toA.The content of base-register plus displacementB.The content of index-register plus displacementC.The content of program counter plus displacementD.The content of AC plus displacement4: The address of operand is in the instruction, it is_________ ?A.Direct addressing modeB.Register indirect addressing modeC.Stack addressing modeD.Displacement addressing mode5: Which the following is not the area that the source and result operands can be stored in ?A.Main or virtual memoryB.CPU registerC.I/O deviceD.Instruction6: Compared with indirect addressing mode , the advantage of register indirect addressing mode isrge address spaceB.Multiple memory referenceC.Limit address spaceD.Less memory access7:With base-register ADDRESSING , the ______________ register can be used.A. BASEB. INDEXC. PCD. ANY8:The disadvantage of INDIRECT ADDRESSING is ____________.A. large addressing rangeB. no memory accessC. more memory accessD. large value range9:Which is not an advantage with REGISTER INDIRECT ADDRESSING?A. just one times of operand’s accessB. large memory spaceC. large value rangeD. no memory reference10:The REGISTER ADDRESSING is very fast, but it has _________________.A. very less value rangeB. very less address spaceC. more memory accessD. very complex address’ calculating11:The disadvantage of IMMEDIATE ADDRESSING is ___________.A. limited address rangeB. more memory accessC. limit value rangeD. less memory access12:In instruction, the number of addresses is 2, one address does double duty of_________.A. a result and the address of next instructionB.an operand and a resultC.an operand and the address of next instructionD.two closed operands13.In instruction, the number of addresses is 3, which are _______________.A. two operands and one resultB. two operands and an address of next instructionC. one operand, one result and an address of next instructionD. two operands and an address of next instruction14.The address is known as a type of data, because it is represented by __________.A. a number of floating pointB. a signed integerC. an unsigned integerD. a number of hexadecimal15.Which is not a feature of Pentium .A. complex and flex addressingB. abundant instruction setC. simple format and fixed instruction lengthD. strong support to high language16. Which is not a feature of Power PC .A. less and simple addressing modeB. basic and simple instruction setC. variable instruction length and complex formatD. strong support to high language17. The advantage of IMMEDIATE ADDRESSING is ___________.A. limited address rangeB. more memory accessC. limit value rangeD. no memory access18. In computer, the address is viewed as a(n) ________________.A. unsigned integerB. signed integerC. floating-pointD. character19. Indirect addressing mode is viewed as the worst because it _________A. has a large address rangeB. can access flexibly memoryC. wastes a lot of memory access timeD. can’t get standard data20. Pentium MMX instructions can deal with ____________.A. multi-media dataB. mixed integer and floating-pointC. multiplicand and multiplier (被乘数和乘数)D. multi-disk’s data21.A branch instruction performed by CPU is to update ____.A MBR to contain the instructionB Program counter to contain the address of next instructionC MAR to contain the address of current instructionD IR to contain the instruction that just fetched from memory22.Each instruction must contain the information required by CPU for execution. Which is not element of instruction? ____.A operation codeB source operand referenceC next instruction referenceD operand address calculation23. The address of operand is in _____________, it is direct addressing mode.A. the instructionB. the register RC. the main memoryD. virtual memory24. Which element of an Instruction can’t be implicit?A. Operation codeB. Source Operand referenceC. Result Operand referenceD. Next Instruction Reference25 Compared with register indirect addressing mode, the disadvantage of indirect addressing mode is___________.A. Large address spaceB. Multiple memory referenceC. Limit address spaceD. Less memory access26.Which addressing mode does not belong to displacement addressing? ____.A relative addressingB base-register addressingC index addressingD register indirect addressing27.In register indirect addressing, the effective address of operand is stored in __ __.A registerB main memoryC instruction D. PC28. Consider a machine-language instruction CALL X, which stands for calling procedure at location X. If the return address is saved on the top of stack, the saved location is pointed by ___________.A. SPB. PCC. MARD. MBR29. Which addressing mode is similar to direct addressing? The only difference is that the address field does not refer a main memory address. ___________.A. RegisterB. DisplacementC. Register indirectD. stack30. The REGISTER ADDRESSING has very less address space, but it has (is) _________________.A. very less value rangeB. very fastC. more memory accessD. complex address calculation。

编程选择题40道:控制结构:流程控制语句与循环.Tex

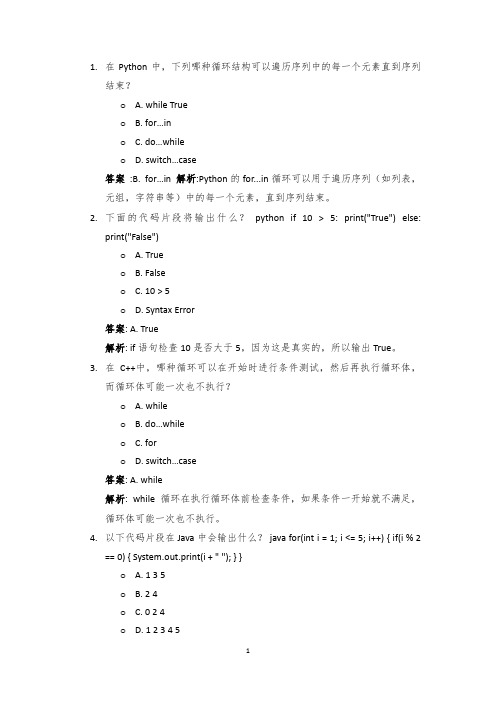

1.在Python中,下列哪种循环结构可以遍历序列中的每一个元素直到序列结束?o A. while Trueo B. for…ino C. do…whileo D. switch…case答案:B. for…in 解析:Python的for...in循环可以用于遍历序列(如列表,元组,字符串等)中的每一个元素,直到序列结束。

2.下面的代码片段将输出什么?python if 10 > 5: print("True") else:print("False")o A. Trueo B. Falseo C. 10 > 5o D. Syntax Error答案: A. True解析: if语句检查10是否大于5,因为这是真实的,所以输出True。

3.在C++中,哪种循环可以在开始时进行条件测试,然后再执行循环体,而循环体可能一次也不执行?o A. whileo B. do…whileo C. foro D. switch…case答案: A. while解析: while循环在执行循环体前检查条件,如果条件一开始就不满足,循环体可能一次也不执行。

4.以下代码片段在Java中会输出什么? java for(int i = 1; i <= 5; i++) { if(i % 2== 0) { System.out.print(i + " "); } }o A. 1 3 5o B. 2 4o C. 0 2 4o D. 1 2 3 4 5答案: B. 2 4解析: 此代码打印出1到5中所有偶数。

5.在Python中,如何退出一个无限循环?o A. 使用break语句o B. 使用continue语句o C. 使用goto语句o D. 使用return语句答案:A. 使用break语句解析:break语句可以用于退出当前循环,无论循环条件如何。

大连交通大学coa考试题1

大连交通大学coa考试题11.In floating-point arithmetic,multiplication can divide to4steps:A.Check for zero,add exponets,multiply significands,normalize,and roundB.Fetch instrution,indirectly address operand,execute instrction and interruptC.process scheduling states:creats,get ready,is running and is blocked.D.load first operand,add second operand,check overflow and store result2.Which the following is not the area that the source and result operands can be stored in_______?A.Main or virtual memoryB.CPU registerC.I/O deviceD.Instruction3.The advantage of Immediate Addressing is_______A.limited address rangeB.more memory accessC.limit value rangeD.no memory access4.The address is known as a type of date,because it is represented by____.A.twos complementB.a signed integerC.an unsigned integerD.a number of hexadecimal5.In direct addressing mode,the operanad is in____A.the main memoryB.the register RC.the instructionD.none6.In____sub-cycle,CPU fetch the operand’s address from memory.A.indirectB.fetchC.executeD.interrupt7.Which is not in the ALU?_____A,shifterB.adder/doc/d713175377.html,plementerD.accumulator8.Instruction pipeline can improve______A.processing speed of programB.accessing speed of memoryC.accessing speed of I?OD.accessing speed of RAID9.The protocol“mesi”is alse called_______.A.write back policyB.write-update protocolC.write-invalidate protocolD.write through policy10.MESI protocol can solve the______.A.problem of cache coherenceB.problem of memory write bottle-nek/doc/d713175377.html,munication problem of person-computerD.volatile problem of DRAM11.At the end of fetch cycle,IR holds______.A.instructionB.operandC.address of operandD.address of instruction12.There are three kinds of BUS,Which does not belong to themA.address busB.system busC.data busD.control bus13.Cache’s write-back policy means write operation to main memory_____.A.as well as to cacheB.only when the relative cache is replacedC.when the difference between cache and main mimory is foundD.only when using direct mapping14.A four-way set associative chache has63k words,main memory has256M words and divided32M blocks.line size is_____words.A.4B.8C.16D.3215.In the following description,which is NOT right6?________.A.SRAM is faster than DRAMB.DRAM needs periodic charg refreshing circuitC.DRAM is slower than FlashD.ROM does not require power supplied continuously16.Which RAID level make use of parallel access technique?______.A.RAID0B.RAID2C.RAID4D.RAID617.RAID stored_____information that enable the recovery of data lost due to a disk failure.A.parity/doc/d713175377.html,er dataC.OSD.interrupt18.The signals of interrupt request and acknowledgement exchange between CPU and requesting I?O module.The rason of CPU’s acknowledgement is______.A.to let the I?O module remove request signalB.to let CPU get the vector from data busC.both A&BD.other aims19.In DMA,the DMA module takes over the operations of data transferring from CPU,it means_______.A.the DMA module can fetch and execute instructions like CPU doesB.the DMA module can control the bus to transfer data to or from meory using stealing cycle techniqueC.the DMA module and CPU work together(co-operate)to transfer data into or from memoryD.the DMA module get ready,it issues interrupt request signal to CPU for getting interrupt service20.In twos complement,two positive intergers add,when does overflow occur?A.There is a carryB.Sign bit of result is1C.There is a carry,and sign bit of result is0D.Can’t determine21.The8-bits twos complement-128is10000000,its16-bits twos complement is___A.1000000010000000B.0000000010000000C.1111111110000000D.100000000000000022.The address of the top of stack is stored in____registerA.PCB.ACC.SPD.BP23.The REGISTER ADDRESSING is very fast,but it has_______.A.very less value rangeB.very less address spaceC.more memory accessD.very c omplex address’calculating24.In instrucion,the number of addressed is2,One address doubles as____A.a result and the address of next instructionB.an operand and a resultC.an operand and the address of next instructionD.two closed operands25.A branch instruction performed by CPU is to updatae______.A.MBR to contain the instructionB.Program counter to contain the address of next instructionC.MAR to contain the address of current instructionD.IR to contain the instruction that just fetched from memory26.In register indirect addressing,the effective address of operand is stored in____.A.registerB.main memoryC.instructionD.PC27.The Memory Address Register of CPU connects to______BUSA.systemB.addressC.dataD.control28.The Accumulator is a(n)______register in8086A.general purposeB.DataC.addressD.control29.Which is the worst instruction to limit instruction pipeline?A.ADD AX,XB.MOV AX,[X]C.RETURND.ISZ X30.In MESI protocol,the line in the cache is the same as that in main memory and is not present in other cache,which state is the line in______.A.ModifiedB.exclusiveC.sharedD.invalid31.Which of the following attributes associated with architectureA.Control signalsB.interfacesC.Instruction setD.memory technology32.Which of the following statement is not correct?A.N bits binary address coding can be2N storage word to identify a wordB.N bits unsigned binary number can represent a value in the range between0to 2N-1C.The length of address is32bits,so addressing range is4GD.8086has20bite address bus giving220-1address space/doc/d713175377.html,puter memory is organized into a hierarchy.At the top level are the_____.A.registers B cache C.main memory D.external memory34.On address mapping of cache,the data in any block of main memory can be mapped to______of cache,it is direct mapping.A.any lineB.fixed lineC.fixed set any lineD.A and B35.Which is the nonvolatile and permanent storge semiconductor memory?___A.SRAMB.CD-ROMC.FLASHD.DRAM36.In hamming code,if syndrome contains one&only one1,it means____.A.the old correct bit is errorB.the data is errorC.more than one errorD.nor error37.In_____,two copies of each stripe on separate disks,read from either and write to both.A.RAID1B.RAID2C.RAID3D.RAID438.When aprocessor access to the disk physical block,it must know that the physical blocks on the disk location of three parameters:________.A.side,head and trackB.side,sector and cylinderC.cylinder,sector and trackD.side,sector and platter39.There are three types of the Input Output Techniques,Which one is not belong them?______.A.Interrupt-driven I/OB.programmed I/O\C.direct I/O accessD.DMA40.In DMA,when does DMA module issue interrupt request signal to CPU?A.before DMA module transfers a block dataB.after DMA module finishes a block data transferC.before DMA module seizes to use busD.after DMA module ends to size bus12345678910 D D D C A A D A C A 11121314151617181920 A B B B C B A C B B 21222324252627282930 C C B B B B B A D B 31323334353637383940 C D A B C A A B C BII Answer the following questions1)Interrupt Processing,The CPU save information of current program to stack forresuming it.What is the important information?2)In MESI protocol,READ MISS,initiating in invalid and snooping in modified,fill in the following table.initiating snoopingState in beginning invalid ModifyactionState in end3)In Displacement Addressing,EA=A+(R),what is the R register holds?In RelativeAddressing,what is the R register?1)PC,PSW(4分)2)initiating SnoopingBegin invalid ModifiedAction Read data from……Write to memoryEnd shared shared(4分)3)base or displacement,PC(4分)得分15III A four-way set associative main memory has256Mwords,cache has4M words and block size is32-words.Please answer the following questions:1)Show the format of main memory addresses2)Which set of cache is memory location FCB5C6AH mapped to?What is the tag?3)Which words of main memory may be mapped to cache set6E8A and tag value is B5H?1)-2分-Line size=Block size=32words=25words=>Word#=5bits(2)-3分-Number of sets=4M/32lines/4lines/set=215sets=>Set#=15bits(3)-2分-Memory size=256Mwords=228words=>Length of RA=28bits =>Tag=28-5-15=8bitsTag8itb Set#15bit Word#5bit-1分-2)(3分)FCB5C6AH=1111110010110101110001101010is mapping to set# 5AE3,tag#FC3)(4分)B56E8A 1011010111011101000101000000 1011010111011101000101011111words of main memory:B5DD140~B5DD15IV According to the instruction of the following,Answer the questions.1)Show all the micro-operations for the following instruction:BSA X -Branch and save addressAddress of instruction following BSA is saved in X Execution continues from X+12)Which addressing mode is included in this instruction?Please draw the figure of its addressing mode3)According to the initial value of the following figure ,at the end of Execute cycle,what is the value of PC,MBU,MAR and IR holdⅣAnswer:2)(4分)PC:2012MAR:2012(应该是2011)MBR:1124IR:BSA 20113)(4分)Direct Addressing1)(10分)Fetch cycle t1:(PC)->MARt2:(MAR)--->Memory read --->Memory t3:Memory --->MBR t4:(MBR)->IR (PC)+1->PC Execute cyclet1:Ad(MBR)->MAR t2:(PC)->MBRt3:(MAR)->Memory(MBR)->Memory write ->Memory t4:(MAR)+1->PCFor the8-bit data00111001,Using the Hamming algorithm,the check bits stored with it.Suppose when the word is read from memory,the check bit are calculated to be 1101.1)What is the data word that was read from memory?2)Write the correct Hamming code(1)(2分)2k-1≥m+k=>k=4-bit(2)(4分)Set up a tableBit Position PositionnumberCheckbitDatabit121100D80111011D70101010D6191001D5181000C870111D4160110D3050101D2040100C430011D1120010C210001C1(3)(4分)Calculates old check bits:C1(1,2,4,5,7)=1⊕0⊕1⊕1⊕0=1C2(1,3,4,6,7)=1⊕0⊕1⊕1⊕0=1C4(2,3,4,8)=0⊕0⊕1⊕0=1C8(5,6,7,8)=1⊕1⊕0⊕0=0old check bits:C8C4C2C1=0111(4)(2分)Syndrome word:0111⊕1101=1010 =>D6is wrong,so the data from memory is 00011001.2)(3分)001101001111。

COA练习题

COA练习题ⅠSelect the best answer based on this course (this part 30 questions, each 1 point, total 30 points)1. __B___ observed that the number of transistors that could be put on a single chip was doubling every 18 months in the 1970s.A. Bill GatesB. Gordon MooreC. John von NeumannD. John Mauchly2. In each instruction, _____C_____specifies the operation to be performed. A. operand B. address C. opcode D. register3. Interrupt process steps are ____C______.A. suspending , resuming , branching & processingB. branching , suspending , processing & resumingC. suspending , branching , processing & resumingD. processing , branching , resuming & suspending4. The characteristics of external memory compared to internal memory are ___B____ .A.Big capacity, high speed, low costB.Big capacity, low speed, low costC.small capacity, high speed, high costD.small capacity, high speed, low cost5.On address mapping of cache, the data in any block of main memory can be mapped to __B___ of cache, it is associative mapping . A.any line B.fixed line C.fixed set D.A and C6.If a procsser modified a word of cache 5 times, that is different with main memory. _____ can modify main memory only once. A.write back B.write through C.write valid D.write update7.Im memory system, main memory is _____. A.random access. B.associative access C.sequential access D.direct access8.which type of memory is volatile? _____ A.ROM B. E2PROMC. DRAMD. flash memory9. _____ check bits are needed if the Hamming error correction code is used to detect single bit error in a 256-bit data wordA. 10B. 9C. 8D. 710.Hamming code is used for the 4-bit word 0011, the leftmost bit and the rightmost bit of the old check bits respectively are _____ . A.0 and 0 B. 0 and 1 C. 1 and 0 D. 1 and 111. On a movable head system, the time it takes to position the head to the right track is known as______.A. seek timeB. rotational delayC. access timeD. transfer time12. Assume a 10-drive RAID configuration and RAID 6, the storage density is ______.A.100% B.90% C.80% C.50%13. With _________, the bits of an error correcting code are stored in the corresponding bit position on multiple parity disk.A. RAID 1B. RAID 2C. RAID 3D. RAID 414.To input a word from keyboard, WHICH I/O technique should be taken?___________.T o output a data block of somesectors to hard disk, WHICH I/O technique should be taken? ___________A. DMA and programmed I/OB. programmed I/O and interrupt-driven I/OC. both interrupt-driven I/OsD. interrupt-driven I/O and DMA15. Which is false the following description about DMA? _________.A. DMA controller takes over bus for a cycle, then transfers one word of dataB. DMA module can fetch and execute instructions like that CPU does.C. CPU is suspended just before DMA controller accesses busD. Slows down CPU, but not as much as CPU doing transfer16. In interrupt driven I/O, the stack uses _________technique to save and resume the contents of PC and PSW and remainder.A. first in first outB. randomC. last in first outD. sequenced17. Overflow occurs sometimes in ______arithmetic operation.A. addB. subtractC. add and subtractD. multiply18. The 8-bit twos complement 1001 0011 is stored in 16-bit. It’s equal to____.A.1000 0000 1001 0011B. 0000 0000 1001 0011C.1111 1111 1001 0011D.1111 1111 0110 1101 1119. The range of n-bit twos complement representation is ___________.A. 0 ~ 2n-1B. -2n-1 ~ 2n-1C. -2n-1 ~ 0D. -2n-1 ~ 2n-1-120. In instruction, the number of addresses is 0, the operand(s)’ address is implied, which is(are) in_______.A. accumulatorB. program counterC. top of stackD. any register/doc/92449258.html,pared with indirect addressing mode , the advantage of register indirect addressing mode is/doc/92449258.html,rge address spaceB.Multiple memory referenceC.Limit address spaceD.Less memory access22. The address of operand’s address is in the instruction, it is .A. Register addressing modeB. Displacement addressing modeC. Stack addressing modeD. Indirect addressing mode23. The correct instruction cycle sequence is _________________ .A. Fetch , Indirect , Execute and InterruptB. Fetch , Execute , Indirect and InterruptC. Fetch , Indirect , Interrupt and ExecuteD. Indirect , Fetch , Execute and Interrup24.The aim of the indirect cycle is to get __________________.A. an operandB. an instructionC. an address of an instructionD. the address of an operand25. The correct cycle sequence is .A. Indirect , Fetch , Execute and InterruptB. Fetch , Execute , Indirect and InterruptC. Fetch , Indirect , Interrupt and ExecuteD. Fetch, Indirect , Execute and Interrupt26. The number of pipeline stages is the larger, the speedup factor will _____ .A. be the greaterB. tend to pipeline stagesC. be the smallerD. tend to the number of instructions27. Which is the worst instruction to limit instruction pipeline?_____.A. BRZ X B. JUMP X C. RETURN D. ISZ Y28. _____ is refused by RISC.A. A small number of data addressing modeB. Large number of general purpose registersC. No operations that combine load/store with arithmeticD. More than one memory-addressed operand per instruction29. The key input signals of control unit are_____ , the clock, flags, and control bus signals.A. the status of the processorB. the instruction registerC. acknowledgmentsD. the outcome of previous ALU operations30.In SMP system, processors share bus ______ .A. , main memory and I/O facilitiesB. , main memory and cacheC. and main memoryD. and cache In MESIⅡJudgment. (This part 10 questions, each 1 point, total 10 points, true is T, false is F.)/doc/92449258.html,pared with RAID4, the advantage of RAID5 is that it avoids the bottleneck.( )2. When DMA module transfers one word, there is an interrupt.( )3.Carry and overflow are the same. ( )4.After the information flow of indirect cycle, the content of MAR is address of operand. ( )5.MESI protocol is a method to solve cache coherence problem. ( )6.protocol, the state of “Exclusive” means that the line in the cache is the same as that in main memory and is not in any other cache. ( )7.More than one module may control bus at one time. ( )8.When a new block is brought into cache, one of the existing blocks must be replaced. For direct mapping, there is more than one possible line for any particular block. ( )9.Adder is the leading part of the Arithmetic and Logic Unit.( )10.In an instruction cycle, decode operation doesn’t relate with main memory.( )ⅢAnswer the following questionsa) Simply describe all the actions when using Interrupt-drivenI/O technique to transfer data with I/O module.b) draw the figure of the indirect and direct addressing mode.Ⅳ A four-way set associative cache consists of 8k lines, Main memory has 256M words and block size is8 words. Answer the following questions:1. Show the mapping format of the main memory address.2. Which set of cache is main memory location ABCDE8FH mapped to?what is the tag?3. How to determine a cache hit/miss.A 4-way set associative cache consists of 16k lines, memory has 4G words and block size is 256 words. Answer:1. Show the mapping format of the main memory address.2. Which set of cache is main memory location ABCDE8F8H mapped to?what is the tag?ⅤSuppose the 12-bit Hamming code 0101 1101 0101 is just read from main memory. Please use theHamming algorithm to determine what the real 8-bit data is.12-bit Hamming code 0011 0110 1111 is just read from memory. Please use the Hamming algorithm to determine what the real data is.ⅥWrite down all micro-operations of the following instruction:ISZ X ----increment and skip if zero.INC X; —Add 1 to the operand of location X in memory.。

codeforces round 900 题解

Codeforces Round 900 题解一、概述Codeforces是一个知名的上线编程比赛评台,每周都有各种比赛活动,吸引了全球各地的程序员参与。

而Round 900则是其中一次比赛,本文将对该比赛中的题目进行详细解析,希望能帮助读者更好地理解并掌握相关算法知识。

二、题目解析1. 题目 1题目描述:给定一个长度为n的字符串,将其所有字母进行重新排列,使得相邻的字母不相同。

求重新排列后的最长长度。

解题思路:利用贪心算法,遍历字符串,尽可能地将相同字母进行分割,重新排列。

最终得到的字符串长度即为所求。

2. 题目 2题目描述:给定一个n行m列的矩阵,每个单元格中有一个非负整数。

将矩阵中的某一行或某一列中所有元素都加上一个给定的值k,求经过加值操作后矩阵中的最大元素。

解题思路:遍历矩阵,求得每一行和每一列的最大值,然后再根据题意进行加值操作,最终得到的矩阵中的最大元素即为所求。

3. 题目 3题目描述:给定一个长度为n的整数序列,求其中的一个连续子序列,使得该子序列的元素之和尽可能大,同时要求子序列的长度不超过k。

解题思路:利用动态规划算法,维护一个长度为k的滑动窗口,遍历整个序列,不断更新窗口中元素之和的最大值,最终得到的和即为所求。

4. 题目 4题目描述:给定一个长度为n的字符串,求其中的一个最长回文子串。

解题思路:利用动态规划算法,遍历字符串,维护一个二维数组表示子串的回文性,根据动态转移方程不断更新数组,最终得到的最长回文子串即为所求。

5. 题目 5题目描述:给定一个无向图,求其中的一条最短路径,使得路径上经过的边的权值的异或和尽可能大。

解题思路:利用Dijkstra算法求最短路径,同时维护最大异或和,最终得到的路径即为所求。

三、算法实现1. 题目 1的贪心算法实现```c++string rearrangeString(string s) {int n = s.size();vector<int> count(26, 0);for (char c : s) {count[c - 'a']++;}priority_queue<p本人r<int, char>> pq; for (int i = 0; i < 26; ++i) {if (count[i] > 0) {pq.push({count[i], i + 'a'});}}string res = "";p本人r<int, char> prev = {-1, '#'};while (!pq.empty()) {p本人r<int, char> cur = pq.top();pq.pop();res += cur.second;if (prev.first > 0) {pq.push(prev);}cur.first--;prev = cur;}if (n != res.size()) {return "";}return res;}```2. 题目 2的矩阵操作实现```c++int maxAfterAddition(vector<vector<int>> mat, int k) { int n = mat.size(), m = mat[0].size();vector<int> rowMax(n, INT_MIN), colMax(m, INT_MIN); for (int i = 0; i < n; ++i) {for (int j = 0; j < m; ++j) {rowMax[i] = max(rowMax[i], mat[i][j]);colMax[j] = max(colMax[j], mat[i][j]);}}int ans = INT_MIN;for (int i = 0; i < n; ++i) {for (int j = 0; j < m; ++j) {int newMax = max(rowMax[i]+k, colMax[j]+k);ans = max(ans, newMax);}}return ans;}```3. 题目 3的动态规划实现```c++int maxSumSubarray(vector<int> nums, int k) { int n = nums.size();vector<int> dp(n, 0);int sum = 0, maxSum = 0;for (int i = 0; i < n; ++i) {sum += nums[i];if (i >= k) {sum -= nums[i-k];}maxSum = max(maxSum, sum);dp[i] = maxSum;}return maxSum;}```4. 题目 4的动态规划实现```c++string longestPalindromeSubstr(string s) {int n = s.size();vector<vector<bool>> dp(n, vector<bool>(n, false)); int maxLen = 1, start = 0;for (int i = 0; i < n; ++i) {dp[i][i] = true;}for (int len = 2; len <= n; ++len) {for (int i = 0; i < n-len+1; ++i) {int j = i+len-1;if (len == 2) {if (s[i] == s[j]) {dp[i][j] = true;maxLen = len;start = i;}} else {if (s[i] == s[j] dp[i+1][j-1]) {dp[i][j] = true;maxLen = len;start = i;}}}}return s.substr(start, maxLen);}```5. 题目 5的Dijkstra算法实现```c++int findMaxXor(vector<vector<p本人r<int, int>>> graph, int n, int start, int end) {priority_queue<p本人r<int, int>> pq;pq.push({start, 0});vector<int> dist(n, INT_MAX);dist[start] = 0;while (!pq.empty()) {p本人r<int, int> cur = pq.top();pq.pop();int u = cur.first, dis = -cur.second;if (u == end) {return dis;}for (auto e : graph[u]) {int v = e.first, w = e.second;if (dist[v] > (dist[u] ^ w)) {dist[v] = dist[u] ^ w;pq.push({v, -dist[v]});}}}return -1;}```四、总结通过对Codeforces Round 900中的五道题目进行详细解析,我们不仅学习了相关算法思想和技巧,还掌握了如何运用这些算法来解决实际问题。

noc python初赛题目

noc python初赛题目

NOC Python 初赛题目是由冰岩编程整理汇总的,包含了 Python 基础进阶考题 110 题答案和源码全汇总。

这些题目难度适中,适合学习和竞赛辅导使用。

题目及解析逻辑清晰易懂,所有代码运行完好。

其中包括以下题目:

1. 输入一个字符串,输出它的反转字符串。

2. 输入一个整数,输出它的各位数字的和。

3. 输入一个整数,输出它的奇偶性。

4. 输入一个整数,输出它的平方。

5. 输入一个字符串,输出所有数字的出现次数。

6. 输入一个整数数组,输出其中偶数的数量。

7. 输入一个整数数组,输出其中奇数的数量。

8. 输入一个数组,输出其中任意两个数字的和。

9. 输入一个字符串,输出所有空格的字符串。

10. 输入一个字符串,输出其中任意两个字符的和。

这些题目涵盖了 Python 编程的基础知识和应用,适合初学者和有一定编程基础的人群。

如果想了解更详细的题目信息和答案,可以前往冰岩编程公众号查看。

50道C++编程练习题及解答-c编程例题

50道C++编程练习题及解答-c编程例题C++作为一种广泛应用的编程语言,通过不断的练习可以帮助我们更好地掌握其语法和编程思维。

以下是为您精心准备的 50 道 C++编程练习题及详细解答,希望能对您的学习有所帮助。

练习题 1:计算两个整数之和题目描述:编写一个 C++程序,输入两个整数,计算并输出它们的和。

```cppinclude <iostream>using namespace std;int main(){int num1, num2, sum;cout <<"请输入第一个整数:";cin >> num1;cout <<"请输入第二个整数:";cin >> num2;sum = num1 + num2;cout <<"两个整数之和为:"<< sum << endl;return 0;}```练习题 2:判断一个数是否为偶数题目描述:编写一个 C++程序,输入一个整数,判断它是否为偶数。

```cppinclude <iostream>using namespace std;int main(){int num;cout <<"请输入一个整数:";cin >> num;if (num % 2 == 0) {cout << num <<"是偶数" << endl;} else {cout << num <<"不是偶数" << endl;}return 0;}```练习题 3:找出三个数中的最大值题目描述:编写一个 C++程序,输入三个整数,找出并输出其中的最大值。

```cppinclude <iostream>using namespace std;int main(){int num1, num2, num3, max;cout <<"请输入第一个整数:";cin >> num1;cout <<"请输入第二个整数:";cin >> num2;cout <<"请输入第三个整数:";cin >> num3;max = num1;if (num2 > max) {max = num2;}if (num3 > max) {max = num3;}cout <<"三个数中的最大值为:"<< max << endl;return 0;}```练习题 4:计算阶乘题目描述:编写一个 C++程序,输入一个正整数,计算并输出它的阶乘。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

题目(第1,2题为必做题。

其余有时间可以选做,如果1,2题没有完成,其余题目不予评分。

正确完成1,2题即可以得到实验考核的满分。

)

1.考核时间:19:00-19:45,上传时间:19:45-20:00. 逾期

1-15分钟上传的报告予以扣10分处理。

逾期15分钟以上,不予处理,实验考核0分处理。

2.如有网络或其他任何问题,请在19:00之前对教师说明,

否则之后不接受延迟上传的理由。

3.上传考核报告请使用Word文档或者PDF格式,文件名和

正文都要表明学号和姓名,否则不予处理!!!

学号:

姓名:

联系电话:

注意,Number请使用学号替代,如0x(04010001). 学号被认为是16进制表示的数据。

1.编写VHDL或Verilog-HDL程序,将32位输入数据按位取非,之后进行逻辑右移,右移位数为学号最后一位,如果学号以0结尾,则右移位数为学号倒数第二位。

编完程序后,请使用你的学号Number作为输入数据进行仿真测试,并给出仿真过程和

结果。

2.请计算(10+13+16+19+….31)-Number 并给出存放在RAM中的程序段并说明含义,同时给出仿真过程与结果。

注意,仿真过程截图放入报告,要每一段仿真过程都可以看清楚。

3.请给出你的程序中指令STORE的微程序执行流程图。

4.请贴出你的POC程序的查询方式下的仿真波形并给予解释说明。

5.编写VHDL或VerilogHDL程序,将32位输入数据按位取非,之后进行算术右移(带正负符号的移位),右移位数为学号最后一位,如果学号以0结尾,则右移位数为学号倒数第二位。

编完程序后,请使用你的学号Number作为输入数据进行仿真测试,并给出仿真结果。