实验一 两个多位十进制数相加的实验

组合逻辑电路实验分析

实验四组合逻辑电路实验分析一、实验目的1.掌握组合逻辑电路的分析方法与测试方法;2.了解组合电路的冒险现象及消除方法;3.验证半加器、全加器的逻辑功能。

二、预习要求1.复习组合逻辑电路的分析方法;2.复习用与非门和异或门等构成的半加器、全加器的工作原理;3.复习组合电路冒险现象(险象)的种类、产生原因,如何消除?三、实验原理1.组合逻辑电路由很多常用的门电路组合在一起,实现某种功能的电路,它在任意时刻的输出,仅取决于该时刻输入信号的逻辑取值,而与信号作用前电路原来的状态无关。

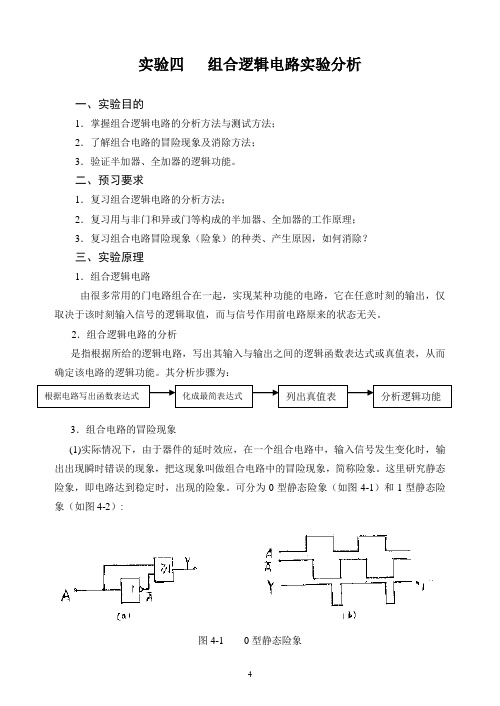

2.组合逻辑电路的分析是指根据所给的逻辑电路,写出其输入与输出之间的逻辑函数表达式或真值表,从而确定该电路的逻辑功能。

其分析步骤为:3.组合电路的冒险现象(1)实际情况下,由于器件的延时效应,在一个组合电路中,输入信号发生变化时,输出出现瞬时错误的现象,把这现象叫做组合电路中的冒险现象,简称险象。

这里研究静态险象,即电路达到稳定时,出现的险象。

可分为0型静态险象(如图4-1)和1型静态险象(如图4-2):图4-1 0型静态险象其输出函数Y=A+A,在电路达到稳定时,即静态时,输出Y总是1。

然而在输入A变化时,输出Y的某些瞬间会出现0,Y出现窄脉冲,存在有静态0型险象。

图4-2 1型静态险象其输出函数Y=A+A,在电路达到稳定时,即静态时,输出Y总是O。

然而在输入A变化时,在输出Y的某些瞬间会出现1,Y出现窄脉冲,存在有静态1型险象。

(2)进一步研究得知,对于任何复杂的组合逻辑电路,只要能成为A+A或A A的形式,必然存在险象。

为了消除险象,通常用增加校正项的方法,如果表达式中出现A+A形式的电路,校正项为被赋值各变量的“乘积项”;表达式中出现A A形式的电路,校正项为被赋值各变量的“和项”。

例如:逻辑电路的表达式为Y=A B+AC;当B=C=1时,Y=A+A,Y正常情况下,稳定后应输出1,但实际中出现了0型静态险象。

这时可以添加校正项BC,则Y A B+AC+ BC=A+A+1=1,从而消除了险象。

多位十进制数加法实验报告

多位十进制数加法实验报告实验一两个多位十进制数相加的实验实验一两个多位十进制数相加的实验一、实验目的1、学习数据传送和算术运算指令的用法。

2、熟悉在PC机上建立、汇编、链接、调试和运行8088汇编语言程序的过程。

二、实验内容将两个多位十进制数相加。

要求被加数均以ASCII码形式各自顺序存放在以DATA1和DATA2为首的5个内存单元中(低位在前),结果送回DATA1处。

三、程序框图四、程序清单CRLF MACROMOV DL,0DHMOV AH,02HINT21HMOV DL,0AHMOV AH,02HINT21HENDMDATA SEGMENTDATA1DB 33H,39H,31H,37H,34HDATA2DB 36H,35H,30H,38H,32HDATA ENDSSTACKSEGMENTSTA DB20 DUP(?)TOP EQU LENGTH STASTACKENDSCODE SEGMENTASSUME CS:CODE,DS:DATA,SS:STACK,ES:DATA START:MOV AX,DATAMOV DS,AXMOV AX,STACKMOV SS,AXMOV AX,TOPMOV SP,AXMOV SI,OFFSET DATA2MOV BX,05CALL DISPLCRLFMOV SI,OFFSET DATA1MOV BX,05CALL DISPLCRLFMOV DI,OFFSET DATA2CALL ADDAMOV SI,OFFSET DATA1MOV BX,05CALL DISPLCRLFMOV AX,4C00HINT21HDISPLPROC NEARDS1: MOV AH,02MOV DL,[SI+BX-1]INT21HDEC BXJNZ DS1RETDISPLENDPADDA PROC NEARMOV DX,SIMOV BP,DIMOV BX,05AD1: SUBBYTE PTR [SI+BX-1],30HSUBBYTE PTR [DI+BX-1],30HDECBXJNZAD1MOV SI,DXMOV DI,BPMOV CX,05CLCAD2: MOV AL,[SI]MOV BL,[DI]ADC AL,BLAAAMOV [SI],ALINCSIINCDILOOP AD2MOV SI,DXMOV DI,BPMOV BX,05AD3: ADDBYTE PTR [SI+BX-1],30H ADDBYTE PTR [DI+BX-1],30HDECBXJNZ AD3RETADDA ENDPCODE ENDSEND START五、实验要求1.读懂源程序,写出源程序注释。

多位十进制数加法器设计.

深圳大学实验报告课程名称:微机原理及应用实验实验项目名称:多位十进制数加法器设计学院:物理科学与技术学院专业:应用物理指导教师:报告人:学号:班级:应用物理班实验时间:2015-10-19实验报告提交时间:2015-11-02教务处制五、程序说明(预习)七、实验源程序清单(实验后以电子报告形式存储到指定位置)1.源程序路径及文件名:ADD2.ASM ADD1.ASM2.可执行程序路径及文件名:八、上机调试情况说明EMU8086:一:没有键盘录入1.结果显示如下:2.程序运行时的各段地址:3.两个子程序IP入口:4.改变两个加数数值5.子程序格式及其调用方法和宏汇编区别子程序格式:子程序名称PROC NEAR ; 子程序定义; …子程序内容RET ;子程序返回子程序名称ENDP ;子程序结束调用格式:CALL 子程序名称注意事项:1、子程序不能直接传递参数,需要自行定义变量。

2、注意保护现场和恢复现场。

宏汇编与子程序的区别:1、宏汇编有宏展开,子程序没有2、宏汇编可以传递参数。

二:键盘录入DOS:例如:250+250=500例如:62142+63123=125265九、实验结果与分析结果如下:十、实验总结(必备部分,评分重要依据之一)本次实验实则是对实验二的加强巩固基础上,进行更加友好的人机交互设计;通过本次实验不仅在程序中首先把两个加数固定,在实验二的基础上扩展位数,考虑到最高位进位的情况,并最终得出正确结果;后来又通过键盘录入两个加数,增加了人机交互的设计,如此一来,更加加深了对寄存器的使用,汇编语言宏定义,子程序调用以及DOS功能调用的学习。

同时,通过本次实验的学习,更加熟练了EMU8086工具的使用,也把理论课上学习到的汇编操作指令实际操作,对汇编语言的风格加深认识。

MOV DL,BLINT 21HCRLFJMP BEGINERROR:CRLFMOV AH,09H ;显示输入错误LEA DX,STRING3INT 21HCRLFJMP BEGINEXIT:CRLFMOV AH,09H ;显示成功退出LEA DX,STRING4INT 21HMOV AH,4CHINT 21HCODE ENDSEND START(2)请问你的程序能否处理加数和被加数都介于0~65535范围但计算结果超出该范围的情况?如何改进?可以,如图:主要考虑到最高位是否进位,可以设置一个进位变量加以判断。

微机原理及实验指导

实验一、I/O程序设计一.实验内容:I/O程序设计(一)实验内容:1.编程由键盘输入任意一个字符,将该字符的ASCII码值显示在屏幕上。

2.从键盘输入两个1位十进制数,计算二者之和,并将结果显示在屏幕上。

3.编程由键盘输入任意一位数,将该数以二进制数形式显示在屏幕上,例:5=00000101B (二)实验步骤: 1. 画出实验流程图。

2. 运行Tddebug软件,选择Edit菜单编写实验程序 3. 使用Compile菜单中的Compile和Link对实验程序进行汇编、连接,生成执行文件。

4. 使用Rmrun菜单中的Run运行程序,观察运行结果。

5. 使用Rmrun菜单中的Debug调试程序。

单步执行指令,观察各寄存器及数据区的内容。

6. 更改数据区中的数据,考察程序的正确性。

二.分析设计思想。

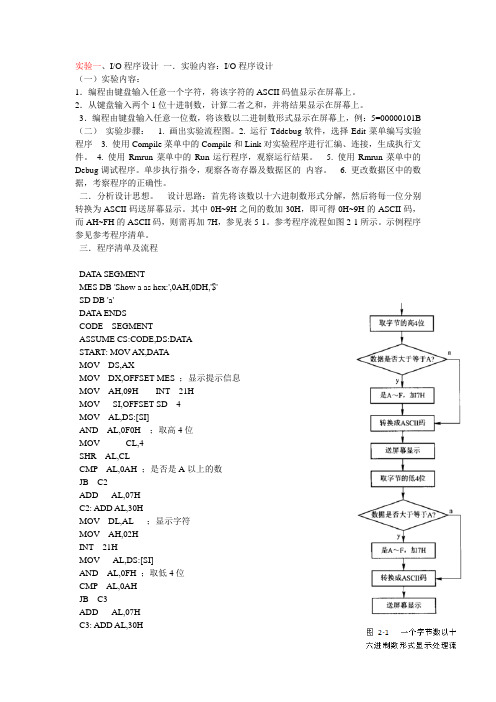

设计思路:首先将该数以十六进制数形式分解,然后将每一位分别转换为ASCII码送屏幕显示。

其中0H~9H之间的数加30H,即可得0H~9H的ASCII码,而AH~FH的ASCII码,则需再加7H,参见表5-1。

参考程序流程如图2-1所示。

示例程序参见参考程序清单。

三.程序清单及流程DATA SEGMENTMES DB 'Show a as hex:',0AH,0DH,'$'SD DB 'a'DA TA ENDSCODE SEGMENTASSUME CS:CODE,DS:DA TASTART: MOV AX,DATAMOV DS,AXMOV DX,OFFSET MES ;显示提示信息MOV AH,09H INT 21HMOV SI,OFFSET SD 4MOV AL,DS:[SI]AND AL,0F0H ;取高4位MOV CL,4SHR AL,CLCMP AL,0AH ;是否是A以上的数JB C2ADD AL,07HC2: ADD AL,30HMOV DL,AL ;显示字符MOV AH,02HINT 21HMOV AL,DS:[SI]AND AL,0FH ;取低4位CMP AL,0AHJB C3ADD AL,07HC3: ADD AL,30HMOV DL,AL ;显示字符MOV AH,02HINT 21HMOV AH,4CH ;返回DOSINT 21HCODE ENDSEND START四.实验结果。

数字逻辑电路课程课程设计--简易加减计算器

摘要本次课程设计的任务是设计一个具有加减运算功能的简易计算器,并通过合适的方式来显示最后的计算结果。

此次设计电路的完成主要是利用简单的数字电路和电路逻辑运算来进行的。

简易加减计算器电路主要是对数据的输入与显示,数据的加减运算,数据的输出与显示三个主要的方面来设计研究完成的。

在输入电路的部分,我们通过开关的闭合与断开来实现数据的输入,开关闭合接入高电平“1”,断开接入低电平“0”。

而输入的数据将通过显示译码管以十进制的形式显示出来。

由于输入二进制的位数较多,我们采用个位十位分别输入的方式来简化电路。

加减运算电路则主要通过加法器来实现的。

设计电路时,我们将个位和个位、十位和十位分别接入一片加法器。

在进行加法运算时我们所选择的加法器是完全符合要求的,但是在进行减法运算时加法器就不能满足我们的设计要求了。

因此我们将减法转换为加法进行运算,运算时采用补码的形式。

在进行减法时通过异或门将减数的原码全部转换为补码,输入加法器中进行相加。

最后将进位信号加到十位的运算电路上就实现了加减法的运算电路。

在显示电路中,由加法器输出的数据是二进制码。

这些码可能表示超过十的数字,所以显示译码管就不能正确的显示出数字了。

此时要将二进制转化成BCD码,再将BCD 码送到显示译码管中就可以将计算所得的数字显示出来了。

概述1.1设计题目:简易加减计算器1.2设计任务和要求:1)用于两位以下十进制数的加减运算。

2)以合适的方式显示输入数据及计算结果。

1.3设计方案比较:方案一:输入十进制的数字,再通过编码器对十进制的数字进行编码,输出二进制的数据。

运用显示译码器对输入的数字以十进制的形式进行显示。

在进行加减计算的时候将二进制数字运用数模转换,然后再进行相加减。

然后将这些模拟信号再次转换成数字信号转换成数字信号,再将数字信号输入到显示译码管中来显示数剧。

这个方案中要进行数模转换和模数转换所需要的电路器件有些复杂,并且转换的时候需要很长的时间,而且转换以后数值的精度不高。

EAT实验指导书电子

EAT实验指导书电子_88实验指导书目录第一章系统安装和启动一实验系统工作方式爱迪克实验系统工作在 88串口实验方式用户根据实验要求,进行-88单片机实验时,将-板正面朝上插到实验机的仿真头和实验的四个插座上,板上的两位拨动开关SB1打到88端用实验机配套的串行通讯电缆,将9芯电缆的一端与实验机上的9芯仿真机通讯口插座相连,另一端与PC机的串行口相连打开电源,在PC机上打开88软件,运行实验程序,具体操作参见《_88使用说明》二实验系统工作在88方式下开关初始状态仿真头插座和实验板插座插_板,板上的两位拨动开关SB1打到88端 XB34 : 短路套向上插(端),第○17模块处于放音功能第○30模块中:短路套全部套向右边,由来控制键盘、显示 SA9:八位开关打到1_88实验指导书目录第二章 88硬件实验实验三实验一实验要求编写程序,以作为输出口控制8个单色灯二实验目的1学习在单板方式下扩展简单I/O接口的方法 2学习编制数据输出程序的设计方法三实验电路及连线PC0~PC7连L0~L7CS连H四实验说明工作于方式0,此时PA、PB、PC均为可独立输入/输出的并行口的各寄存器对应的口地址为:PA口: H PB口: HPC口: H 控制寄存器:H由于各PC机速度不同为达到较好的实验效果,可适当调节亮灭的延时时间2_88实验指导书目录五实验程序框图示例程序见3_88实验指导书目录第三章 88软件实验本指导书提供20个软件实验,可以脱离T实验机运行,调试工具用程序,建议运行环境为纯也可运行88ET集成调试界面,打开要调试的程序,然后进入“工具”菜单下的“方式”,程序即自动加载,这时用户可用的各种命令对程序进行调试实验一两个多位十进制数相减实验一实验要求将两个多位十进制数相减,要求被减数,减数均以码形式按顺序存放在以1和2为首的5个内存单元中,结果送回1处二实验目的1 学习数据传送和算术运算指令的用法2 熟悉在PC机上建立、汇编、链接、调试和运行汇编语言程序的过程三实验程序框图开始显示减数和被减数被减数和减数转换成十六进制数设置计数值清除最低进位位带进位减结果送被减数区调整偏移量N计数值-1=0Y结果转换成码字符串显示结果结束4_88实验指导书目录实验二从键盘输入数据并显示一实验要求编写程序,将键盘接收到的四位十六进制数转换为等值的二进制数,再显示在屏幕上若输入的不是0-F间的数字则显示出错信息并要求重新输入二实验目的掌握接收键盘数据的方法,并了解将键盘数据显示时须转换为码的原理并在程序中设置错误出口三实验程序框图开始初始化。

《汇编语言程序设计》实验指导书

实验一简单程序编制和上机过程一.实验目的1.掌握计算机常用代码的软件转换技术。

2.熟悉DEBUG软件的使用。

3.掌握简单程序的编程方法。

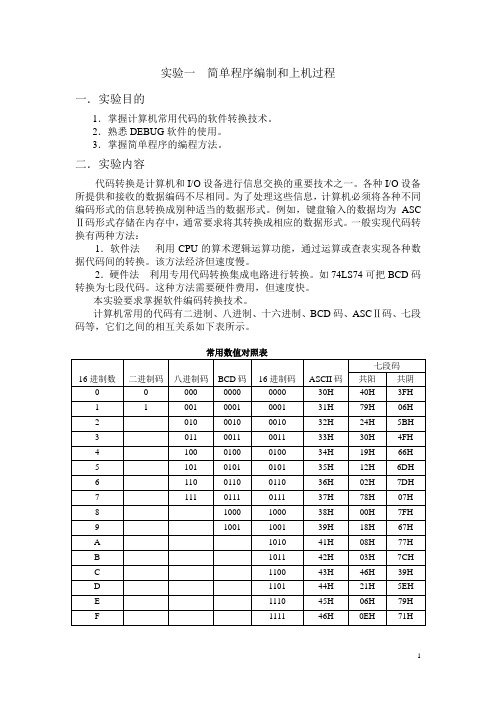

二.实验内容代码转换是计算机和I/O设备进行信息交换的重要技术之一。

各种I/O设备所提供和接收的数据编码不尽相同。

为了处理这些信息,计算机必须将各种不同编码形式的信息转换成别种适当的数据形式。

例如,键盘输入的数据均为ASC Ⅱ码形式存储在内存中,通常要求将其转换成相应的数据形式。

一般实现代码转换有两种方法:1.软件法利用CPU的算术逻辑运算功能,通过运算或查表实现各种数据代码间的转换。

该方法经济但速度慢。

2.硬件法利用专用代码转换集成电路进行转换。

如74LS74可把BCD码转换为七段代码。

这种方法需要硬件费用,但速度快。

本实验要求掌握软件编码转换技术。

计算机常用的代码有二进制、八进制、十六进制、BCD码、ASCⅡ码、七段码等,它们之间的相互关系如下表所示。

本次试验的内容是ASCⅡ码转换为未组合BCD码设从键盘输入十进制数的ASCⅡ码已存放在起始地址CS :150H的单元中,把它转换成未组合BCD码后,再分别存入起始地址为CS:15AH的单元中。

若输入的不是十进制数的ASCⅡ码,则相应存放结果单元的内容为“FF”。

提示:1.组合BCD码是一位十进制数字占一个字节,高半字节为0,低半字节为该十进制数字的BCD码。

ASCⅡ码转换为未组合BCD码只需减30H。

2.程序框图如下图所示。

3.程序执行前,需要在CS:150H内存缓冲区写入待转换的ASCⅡ码。

方法如下:方法一:用A命令-ACS:150 DB 35,39,30,41,32CS:155 ∧C方法二:用E 命令-ECS:150,35,39,30,41,32方法三:用F命令-FCS:150 L5 35,39,30,41,321.执行程序后检查执行结果可用D命令:-DCS:15ACS:15A 05,09,00,FF,02ASCⅡ码转换为未组合BCD码的程序流程图参考程序如下:ORG 100HMOV CX,0005HMOV DI,150HBB:MOV BL,0FFHMOV A,[DI]CMP AL,3AHJNB DONESUB AL,30HJB DONEMOV BL,ALDONE:MOV AL,BLMOV [DI+0AH],ALINC DILOOP BBINT 20HORG 150HDB 35H,39H,30H,41H,32H实验二顺序结构的程序设计一.实验目的1.掌握计算机常用代码的软件转换技术。

数字电路课程设计样本

数字电路课程设计一、概述任务:通过解决一两个实际问题,巩固和加深在课程教学中所学到知识和实验技能,基本掌握惯用电子电路普通设计办法,提高电子电路设计和实验能力,为此后从事生产和科研工作打下一定基本。

为毕业设计和此后从事电子技术方面工作打下基本。

设计环节:依照题目拟定性能指标,电路预设计,实验,修改设计。

衡量设计原则:工作稳定可靠,能达到所规定性能指标,并留有恰当裕量;电路简朴、成本低;功耗低;所采用元器件品种少、体积小并且货源充分;便于生产、测试和维修。

二、惯用电子电路普通设计办法惯用电子电路普通设计办法是:选取总体方案,设计单元电路,选取元器件,计算参数,审图,实验(涉及修改测试性能),画出总体电路图。

1.总体方案选取设计电路第一步就是选取总体方案。

所谓总体方案是依照所提出任务、规定和性能指标,用品有一定功能若干单元电路构成一种整体,来实现各项功能,满足设计题目提出规定和技术指标。

由于符合规定总体方案往往不止一种,应当针对任务、规定和条件,查阅关于资料,以广开思路,提出若干不同方案,然后仔细分析每个方案可行性和优缺陷,加以比较,从中取优。

在选取过程中,惯用框图表达各种方案基本原理。

框图普通不必画得太详细,只要阐明基本原理就可以了,但有些核心某些一定要画清晰,必要潮流需画出详细电路来加以分析。

2.单元电路设计在拟定了总体方案、画出详细框图之后,便可进行单元电路设计。

(1)依照设计规定和已选定总体方案原理框图,拟定对各单元电路设计规定,必要时应详细拟定重要单元电路性能指标,应注意各单元电路互相配合,要尽量少用或不用电平转换之类接口电路,以简化电路构造、减少成本。

(2)拟定出单元电Array路规定后,应全面检查以遍,的确无误后方可按一定顺序分别设计各个单元电路。

(3)选取单元电路构造形式。

普通状况下,应查阅关于资料,以丰富知识、开阔眼界,从而找到合用电路。

如果的确找不到性能指标完全满足规定电路时,也可选用与设计规定比较接近电路,然后调节电路参数。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验一两个多位十进制数相加的实验

一、实验目的

1、学习数据传送和算术运算指令的用法。

2、熟悉在PC机上建立、汇编、链接、调试和运行汇编语言程序的过程。

二、实验内容

将两个多位十进制数相加,要求被加数和加数均以ASCII码形式各自顺序存放在以DATA1、DATA2为首的5个内存单元中(低位在前),结果送回DATA1处。

三、程序框图

四、程序清单

DATA SEGMENT ;定义数据段

DATA1 DB 33H,39H,31H,37H,34H ;被加数

DATA1END EQU $-1

DATA2 DB 34H,35H,30H,38H,32H ;加数

DATA2END EQU $-1

SUM DB 5 DUP(?) ;定义5个空字节

DATA ENDS

STACK SEGMENT ;定义堆栈段

STA DB 20 DUP(?) ;取从STA开始的20个字节为堆栈段TOP EQU LENGTH STA ;将堆栈段长度存放在TOP中

STACK ENDS ;堆栈段定义结束

CODE SEGMENT ;定义程序代码段

ASSUME CS:CODE,DS:DATA,SS:STACK,ES:DATA ;表明程序代码段与段地址之间的关系START: MOV AX,DATA

MOV DS,AX ;将段地址送入段地址寄存器

MOV AX,STACK

MOV SS,AX ;将当前堆栈段首地址送入SS

MOV SP,AX ;将堆栈段首地址送入堆栈指针寄存器

MOV SI,OFFSET DATA1END ;将DATA1的偏移地址送入SI

MOV DI,OFFSET DATA2END ;将DATA2的偏移地址送入DI

CALL ADDA ;调用子程序ADDA

MOV AX,4C00H

INT 21H ;中断调用

ADDA PROC NEAR ;子程序段

MOV DX,SI ;DX=0004H

MOV BP,DI ;BP=0009H

MOV BX,05H ;程序调用次数

AD1: SUB BYTE PTR[SI],30H ;将被加数的ASCII码转换成十六进制数SUB BYTE PTR[DI],30H ;将加数的ASCII码转换成十六进制数

DEC SI ;SI中的内容自减1

DEC DI ;DI中的内容自减1

DEC BX ;程序调用次数自减1

JNZ AD1 ;条件转移

MOV SI,DX ;回到初始位置

MOV DI,BP

MOV CX,05H ;循环次数控制

CLC ;清除CF位

AD2: MOV AL,[SI]

MOV BL,[DI]

ADC AL,BL ;从低位开始进行带进/借位的加法运算

AAA ;转换成非压缩BCD码,低位存于AL,高位存于AH

MOV [SI],AL ;将AL中的内容存入SI所在地址

DEC SI ;偏移地址自减

DEC DI ;偏移地址自减

LOOP AD2 ;循环控制指令

MOV SI,DX

MOV DI,BP

MOV BX,05H

AD3: ADD BYTE PTR[SI],30H ;将16进制数转换为ASCII码表示

ADD BYTE PTR[DI],30H

DEC SI ;偏移地址自减

DEC DI

DEC BX

JNZ AD3

RET ;返回指令

ADDA ENDP ;结束子程序

CODE ENDS ;结束程序代码段

END START

五、实验结果(截屏--软件实验或者拍照---硬件实验)

六、实验结果分析(预期结果与实际结果的对照)

1、数据段分析

用ASCII码值的形式表示被加数和加数

被加数=39174;加数=45082

2、堆栈段分析

用于存放计算过程中的过程量。

3、程序代码段分析

1)从低位起,将被加数和加数转换成十六进制数

被加数和加数转换各位转换成十六进制数表示。

2)从低位起进行各个位上的带进位的加法运算

得到的结果的各位上的十六进制表示形式。

3)将结果的各个位上的数转换成ASCII码的形式得到最后的结果

实验得到的最后的结果是39174+45082=84256。

七、实验心得体会

通过本次实验,我对汇编有了更物理化的认识,也明白了汇编中各个寄存器的作用及寄存器间是怎样联系的,也初步明白了什么是段地址,什么是堆栈,以及汇编的基本结构和循环结构的基本运用。

但是,我的了解只是初步的,汇编中还有很多我不明白和不了解的地方,最重要的是,汇编语句掌握不牢固,不能很快的知道一些专用的汇编语句的意义,对于宏方面的认识也非常薄弱,还需要在今后的实验和学习中不多的学习和练习。