orCAD使用心得

AUTOCAD使用心得

AUTOCAD使用心得连载之一使用的三个基本方面目前,我公司的设计文件,特别是图纸,都是用AUTOCAD软件绘制的。

但是,现在还有很多人对CAD并不是非常熟悉,或者说使用起来并非得心应手,以至于效率并不是很高,可以说,在我们公司,绘制同样的一张图纸,速度快的和慢的在耗时上可能会相差好几倍。

同时,每个人绘制出来的图纸看上去感觉都不经相同,有些图纸看上去一目了然、清晰漂亮,而有些图纸不但表达不清,过分点可以用惨不忍睹来形容。

从本期工程设计开始,本人会将十几年绘图经验的点点滴滴作为连载,以飨大家,希望对大家能有所借鉴,从中能吸取一二,养成良好的绘图习惯、提高绘图速度。

同时,本人也希望这是抛砖引玉,借助这个机会和载体,能够使得大家对CAD的使用展开一次交流和讨论,相互提高。

另外,因为本人是建筑专业的,对其他专业不胜了解,因此,今后的举例将主要是和建筑专业有关的,希望大家能举一反三。

不知大家认为,使用CAD画图,最重要的是什么?对这个问题,每个人都有可能理解不同,但在我看来,最重要的是时时刻刻记住自己使用CAD画图的目的是什么。

我们进行工程设计,不管是什么专业、什么阶段,实际上都是要将某些设计思想或者是设计内容,表达、反映到设计文件上。

而图纸,就是一种直观、准确、醒目、易于交流的表达形式。

所以我们完成的东西(不管是最终完成的设计文件,还是作为条件提交给其他专业的过程文件,一定需要能够很好的帮助我们表达自己的设计思想、设计内容。

有了这个前提,我们就应该明白,好的计算机绘制的图纸应该具有以下两个特征:清晰、准确。

清晰:我们要表达的东西必须清晰,好的图纸,看上去一目了然。

一眼看上去,就能分得清哪是墙、哪是窗、哪是留洞、哪是管线、哪是设备;尺寸标注、文字说明等清清楚楚,互不重叠……。

除了图纸打印出来很清晰以外,在显示器上显示时也必须清晰。

图面清晰除了能清楚的表达设计思路和设计内容外,也是提高绘图速度的基石。

准确:200宽的墙体不能画成240;留洞不能尺寸上标注的是1000X2000,而实际量量是1250X2100;更常见的错误是分明是3000宽的一条线,量出来却是2999.87。

cad画图心得体会(5篇)

cad画图心得体会(5篇)cad画图心得体会篇1通过这几周的cad技能训练我真实地体会到了这种绘图系统的有用性。

同时也感觉到,绘图作为土木工程中设计思想的载体,具备良好的绘图力量是每一个设计人员最根本的素养。

虽然训练已经完毕,但我觉得自己的学习过程还没有完毕,还有许多地方可以提高。

这次学习培育了我的动手力量。

在此,对自己学习cad的一些感悟和体会归纳如下:本次专业技能训练一共绘制了五张图纸,分别为首层平面图、11-1立面图、1-1剖面图、二楼楼层构造平面布置图、平面布置图。

在整个绘图的过程中,坚守着不断学习,不断进步,最大程度把握autocad的根本原那么,排解一切困难,做好本次专业技能训练。

其中,遇上了许多料想不到的困难。

比方说在考虑整个图纸的布局和打印要求方面颇为繁琐,既要考虑到整个图纸总体的美观性,还要兼顾到详细详情的正确无误。

可能在计算机中绘制的模型空间里觉察不了问题,但是打印出来的实际效果却是不抱负。

这就需要我们不断地改进图纸的各种参数和详情,保证出图的准确无误和美观。

还有各种线型的参数设置,常用标示符号的大小规格,都要参照国家的相关要求。

了解把握了一些cad的指令1、菜单栏中的指令包含了全部对软件的操作指令如:直线是l 矩形rec等等。

要用cad画图,了解和熟识cad 绘图指令,这是最根本的起点。

cad中执行根本的操作指令有3种方式:左边的绘图栏中的指令按钮,指令窗口中直接输入指令和在上边的工具栏中点绘图做相应的图形。

2、使用多种方法提高制图效率首先是会用块。

外部图块,学习图形块如何定义、创立块、在工程图形中插入图块、图块的编辑等。

块的作用是避开用户屡次创立相同的图形铺张时间。

此外还有镜像,矩阵方法。

使用它们可以绘制左右对称的图形以及形同的规章的图形等。

多使用这几种方法绘制可以大幅度提高制图效率。

3、在平常的学习中加强cad制图练习,提高制图的水平通过对cad制图的练习,娴熟的把握和运用指令,使自己的制图力量有更大的进步。

ORCAD小技巧

ORCAD小技巧1. 快捷键:学会使用快捷键可以显著提高设计效率。

ORCAD提供了很多快捷键,例如Ctrl+C用于复制、Ctrl+V用于粘贴、Ctrl+Z用于撤销等。

你可以通过查看ORCAD的帮助文档或在工具栏菜单中找到更多的快捷键。

2.元件的选择:在ORCAD的库中有很多元件可供选择。

当你需要在设计中添加元件时,可以通过在库中输入元件的名称或型号快速找到所需元件。

你也可以通过在库中使用过滤器来缩小范围。

3.右键菜单:在ORCAD的设计界面中,右键点击鼠标可以打开一个方便的菜单。

这个菜单中包含了许多常用的功能选项,如复制、粘贴、旋转等。

你可以使用右键菜单来加快操作速度,减少通过菜单栏查找选项的时间。

4.脚本和自动化:ORCAD支持使用脚本来执行一系列的操作。

脚本可以帮助你快速完成一些重复性的任务,例如自动添加特定元件、连接电路等。

你可以学习ORCAD的脚本语言,编写一些自定义的脚本来提高工作效率。

5.快速布线:在进行PCB布局设计时,ORCAD提供了快速布线功能。

通过点击元件上的引脚,ORCAD可以根据连接关系自动布线。

这个功能可以节省大量的时间,特别是在复杂的PCB设计中。

6.分析工具:ORCAD提供了许多强大的分析工具,如直流电路分析、交流电路分析、传输线分析等。

学会使用这些分析工具可以帮助你更好地了解电路的性能和特性,并进行相应的优化。

7.模块化设计:使用ORCAD时,可以将电路分解为多个模块,并进行分开设计和仿真。

这种模块化的设计方法可以大大简化复杂电路的设计过程,并提高设计的可维护性和可重用性。

8. 可编程逻辑器件:ORCAD支持可编程逻辑器件(如FPGA、CPLD)的设计和仿真。

如果你需要设计复杂的逻辑电路,可以使用ORCAD的可编程逻辑器件功能,同时结合硬件描述语言(如VHDL、Verilog)进行设计和仿真。

9.历史版本管理:ORCAD提供了版本管理工具,可以帮助你管理电路设计的不同版本。

orcad期末课程总结

orcad期末课程总结

1.课程总结

本课程设计的带滤波电路的三相整流电路的优点是此电路能够完成整流和滤波的工作,在现代AC-AC变频领域大多采用不可控的二极管作为整流器件,所以此电路是可以应用于交交变频电路中的AC-DC的变换过程中的。

但此电路也存在这一些不足,相对于现代电力电子设计的要求还存在很多不足,滤波器的设计只是跟随滤波后的输入信号,而不能起到放大的作用,是输出电压在滤波后降幅过大。

改进:可以在二阶滤波后加入增益>1的同相比例放大器即可。

当然电路设计还有很多需要细化的地方,在以后的学习研究中要不断的弥补。

⒉课程心得

对于电气的学生,未来发展无非两种选择1软件方向2硬件方向。

我比较倾向于硬件设计方向。

在使用了ORCAD之后,发现这是一个功能很强大的软件。

尤其是它可以和 Matlab进行协同仿真。

但ORCAD中有太多奥妙,仍然需要更多地时间去摸索学习。

AutoCAD心得体会

AutoCAD心得体会第一篇:AutoCAD心得体会AutoCAD学习心得体会随着计算机技术的飞速发展,CAD已得到快速发展。

我们可以利用CAD技术设计图纸,用CAD 强大的辅助图形设计和三维实体造型功能改变传统的绘图方式,使我们化工类的学生既能摆脱传统机械制图学习的抽象和枯燥,又能使我们的绘图学习变得更轻松而高效,并且更能适应现在社会对技术性人员的需求。

经过不断地完善,现已成为国际上广为流行的工程制图工具计算机CAD技术已经深入各个行业中.学习了AutoCAD这门课程,我对我们的专业又有了更深的了解,CAD是我们专业所必学的一个软件,这个软件不仅广泛用于工程、工业制图中的建筑工程、装饰设计、环境艺术设计、水电工程、土木施工等等。

精密零件、模具、设备等,还广泛应用于土木建筑、装饰装潢、城市规划、园林设计、电子电路、机械设计、服装鞋帽、航空航天、轻工化工等诸多领域。

AutoCAD是由美Autodesk公司开发的通用计算机辅助设计软件,具有易于掌握、使用方便、体系结构开放等优点,能够绘制二维图形与三维图形、标注尺寸、渲染图形以及打印输出图纸,在化工行业中有着重要的应用,AutoCAD是当前最流行的计算机辅助设计软件之一,具有强大的绘图功能。

一方面,机械制图是AutoCAD的基础。

比如设计图纸、设计流程。

另一方面,AutoCAD 是促进制图教学的有效工具。

它取代了手工制图方法,利用其强大的绘图功能和编辑修改功能,可以快速、准确、美观地表达出所要画的机械图样,极大地提高了绘图效率和绘图质量。

除了应用于化工行业之外,甚至被广泛应用于机械、建筑、电子、航天、造船、石油化工、土木工程、冶金、地质、气象、纺织、轻工、商业等诸多领域。

学习了CAD制图,我也总结了自己的一些学习经验和方法:首先,我认为基础很重要,学习CAD,需要一定的画法几何的知识和能力,需要一定的识图能力,尤其是几何作图的能力,所以,我认为学好《化工制图》是基础,《化工制图》学的好的学生CAD制图学起来会轻松容易的多。

AutoCAD学习心得及经验.txt.doc

1、基础很重要实践证明,“手工图板”绘图能力是计算机绘图能力的基础,学习《AutoCAD》,需要一定的画法几何的知识和能力,需要一定的识图能力,尤其是几何作图能力,一般来说,我所在的班级中,《工程制图》水平好的学员,学起来较容易些,效果较好!2、循序渐进整个学习过程应采用循序渐进的方式,先了解计算机绘图的基本知识,如相对直角坐标和相对极坐标等,使自己能由浅入深,由简到繁地掌握AutoCAD 2000的使用技术。

3、学以致用在学习AutoCAD 2000命令时始终要与实际应用相结合,不要把主要精力花费在各个命令孤立地学习上;要把学以致用的原则贯穿整个学习过程,以使自己对绘图命令有深刻和形象的理解,有利于培养自己应用AutoCAD 2000独立完成绘图的能力。

4、熟能生巧配套的《计算机绘图习题集》作为上机实验书,它能使我们更加深入地理解、熟练AutoCAD 2000的命令。

要强迫自己做几个综合实例,分别详细地进行图形的绘制,使自己可以从全局的角度掌握整个绘图过程,力争使自己学习完AutoCAD 2000课之后就可以投身到实际的工作中去。

掌握技巧1、常见问题要弄懂(1)同样画一张图,有的同学画的大小适中,有的同学画的图形就很小,甚至看不见,这是为什么?这是因为绘图区域界限的设定操作没有做,或虽用LIMITS命令进行了设定,但忘记了用ZOOM命令中的ALL选项对绘图区重新进行规整。

绘图区域的设定是根据实际的绘图需要来进行的。

(2)有同学用线型名称为“HIDDEN”的线型画线段,但发现画出的线段看上去像是实线,这是什么原因引起的?这是“线型比例”不合适引起的,也就是说“线型比例”太大,也可能是太小。

解决问题的办法是将线型管理器对话框打开,修改其“全局比例因子”至合适的数值即可。

(3)在进行尺寸标注以后,有时发现不能看到所标注的尺寸文本,这是什么原因引起的?这是因为尺寸标注的整体比例因子设置得太小,将尺寸标注方式对话框打开,修改其数值变大即可。

ORCAD 使用心得笔记1

ORCAD 使用心得笔记1.元件如何上下、左右镜向?如何旋转?选中元件后,按V键可上下镜向,H键左右镜向,R键旋转。

2.如何找元件?按P键后,可在对话框中查找,支持通配符,可以模糊查找。

3.如何快速的复制元件?如何移动已连接线路的元件?在同一张图纸上,可以按住Ctrl键再点击元件拖动复制,不在同一张图纸上可以用一般的Ctrl+C与Ctrl+V的方法复制元件。

想要移动已有连接线路的元件,可以按住Alt 键再用鼠标左键拖动,这样连线不会跟随一起移动。

4.如何在一个文本框中输入多行文本文字?输完一行后,按Ctrl+Enter键可重新另起一行。

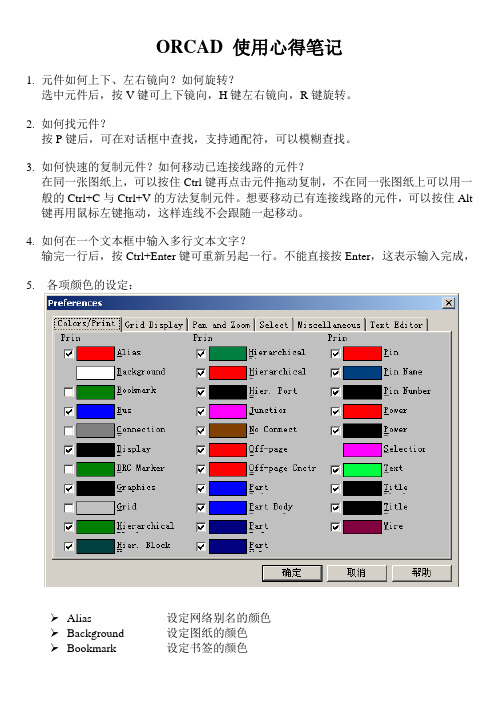

不能直接按Enter,这表示输入完成,5. 各项颜色的设定:Alias 设定网络别名的颜色Background 设定图纸的颜色Bookmark 设定书签的颜色Bus 设定总线的颜色Connection 设定连接器的颜色Display 设定显示属性的颜色DRC Marker 设定规则检查标记的颜色Graphics 设定图案的颜色Grid 设定网格的颜色Hierarchical 设定层次图的颜色Hier.Port 设定层次图的I/O端口文字的颜色Junction 设定结点的颜色No Connect 设定不连接指示的颜色Off-page 设定(页)端点连接器的颜色Off-page Cnctr 设定(页)端点连接器文字的颜色Part 设定元件相关属性的颜色Pin 设定管脚的颜色Pin Name 设定管脚名称的颜色Pin Number 设定管脚编号的颜色Power 设定电源符号的颜色Selection 设定选取图件的颜色Text 设定说明文字的颜色Title 设定标题栏属性的颜色Wire 设定导线的颜色这些颜色的设定真的很方便很重要,做图一开始有一连串的设定,颜色设定也是其中的一种,这里的设定,相当于设定default值的颜色,还可以对个别单独修改。

6. 显示栅格样式与锁定栅格的设定:表示在电路图中显示或不显示栅格表示以点或线的形式显示栅格表示是否锁定栅格。

电路OrCAD实习报告

OrCAD/PSpice电路分析实习报告学院:电气信息工程学院专业:电子信息工程班级:信息10—1姓名:学号:目录一、实习目的二、实习的基本要求三、实习方式四、ORCAD简介五、OrCAD的优点六、OrCAD的特色七、OrCAD软件系统的功能及特点八、实习内容1. OrCAD 简介2。

电路图绘制实例3。

电路图绘制技巧4。

电路特性分析九、实习心得一、实习目的《电子电路CAD》是一门实践性很强的课程。

ORCAD 是由ORCAD公司于八十年代末推出的EDA软件,它是世界上使用最广的EDA软件,每天都有上百万的电子工程师在使用它,相对于其它EDA软件而言,它的功能也是最强大的。

通过实训,使学生能够熟练掌握该软件的基本功能(绘制电路图、创建元器件、创建封装图、合理布局布线、设置障碍物、PCB后续处理等),能使用该软件设计出具有一定专业水平的PCB板。

1、学会使用OrCAD软件,绘制各种基本电路图形,绘制原理图.2、学会创建元器件库和元器件。

3、学会应用OrCAD软件制作PCB板。

二、实习要求1、这是对本期所学ORCAD知识进行的一次全面的演练,本次实习训需要用到ORCAD的许多基础知识和操作技能。

2、熟悉OrCAD软件的正确应用,绘制相应阴的原理图。

3、爱护公物,不准乱动实习场所的设备,护计算机房的清洁卫生,遵守机房规章制度.4、实习期间,严格按学校的作习时间进行实习,不准迟到早退。

5、实习训结束后,每位同学除上交本次实训成果以外,还要写出一份实训报告。

三、实习方式1、听取专业人员的讲解.2、查阅相关资料。

3、上机操作。

四、ORCAD简介ORCAD是由ORCAD公司于八十年代末推出的EDA软件,它是世界上使用最广的EDA软件,每天都有上百万的电子工程师在使用它,相对于其它EDA软件而言,它的功能也是最强大的,由于ORCAD软件使用了软件狗防盗版,因此在国内它并不普及,知名度也比不上PROTEL,只有少数的电子设计者使用它,它进入国内是在电脑刚开始普及的94年。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

** copyright (c) 2005 华北电力大学(北京)自动化系现场总线实验室* All rights reserved**文件名: ORCAD使用心得.DOC*文件标识:*摘要:本文写了写我自己的ORCAD使用心得。

文中每一条每*一段都记录了这一段时间以来焚膏继晷、暑寒相接、痛苦并快乐的探索历程。

今天用了一整天时间把此草稿写完,也算是对自*己有个交待,且对后来人有所启示。

不幸的是,这些天茶余饭*后总为发表有ISBN标记的论文而发愁,没有太多心思弄别的.*就写这么多吧。

学术腐败,郁闷!! 中国人的悲哀,诺贝尔的遗憾。

*当前版本:1.0.0*作者:秦宇飞*完成日期:2005年10月28日**/ORCAD使用心得我自2005年8月25号起,到2005年10月22日止,用CAPTURE和ALLEGR画板,增删数次,校审N回,终成两块电路板。

郁闷与欢喜之余,深感ORCAD功能强大,熟练使用真是享受呀。

现将我的使用心得写出来,供大家参考。

因网上已有许多介绍CAPTURE和ALLEGR操作的文章,这里就不详述具体的操作步骤。

零、ORCAD的安装注意事项ORCAD的安装涉及CADENCE LICENSE MANAGER安装的问题。

选择ALLEGRO程序里的CADENCE LICENSE MANAGER,如果选择CAPTURE里的CADENCE LICENSE MANAGER,会提示IKERNEL错误,这样CADENCE LICENSE MANAGER总也装不上去,程序也无法使用。

我也弄不明白为什么CAPTURE 和ALLEGRO里同样的CADENCE LICENSE MANAGER安装程序会有不同的结果。

至于其它步骤请看程序中的破解文档吧。

一、CAPTURE1、 CAPTURE版本选择CAPTURE建议使用10.0以上版本。

因为9.0的撤消只有一次,用得很郁闷。

此外CAPTURE10.0以上版本对ALLEGRO的支持更好。

CAPTURE10.0以上版本增加了从网上原理图库中找元件封装的功能。

虽然元件不是很多,但是比自己画方便了很多。

我是在画完原理图之后才发现这个功能的,“超级郁闷”(童同学语)。

操作:在原理图编辑窗口点右键,PLACE DATABASE PART再点ICA,然后搜索零件就行了。

可以直接放到原理图。

2、命名(1)、元件编号一定不要重名,虽然文档里不同文件夹内的元件编号可以相同,但是这样会在DRC检测时出问题,所以最好不要这么做。

(2)、CAPTURE的元件库中有两个“地”易弄混。

虽然它们的符号不一样。

一个叫GND_SIGNAL,另一个叫GND,这个要在使用中要注意。

3、元件封装(1)、元件封装的引脚不可重名。

如GND,要命名为GND_1,GND_2。

(2)、为了使原理图摆放更合理,使线交叉更少,经常要调整引脚位置。

调整位置的时候建议不要更改库里的东东(如果库里的东东没有大问题),只改放在原理图上的INSTANCE就行了。

操作:在元件上点右键EDIT PART。

(3)、也可以改库里的元件,但会使CACHE里的元件与库里的不一样,想让库里的元件刷新CACHE 里的,或删掉CACHE里的,可进行如下操作。

点CACHE里的元件,DESIGH->Replace Cache 或Update Cache.(4)、Cadence不允许符号 . / 而Protel可以,如AXIAL0.4在CAPTURE里要改为AXIAL04或其它名称。

4、方向键使用CAPTURE的上下左右方向键可以控制鼠标每次移动一个栅格。

合理使用方向键可以大大画图效率。

例如要添加总线各分支的NET,可以点一次下键,再按一下鼠标左键。

4、模块的使用模块看起来很舒服的,它直观地表示了各个模块的连接。

比只用NET表示要舒服得多,至少我这么认为。

块的原理图可用多次,借用C++的概念,定义了块相当于定义一种数据类型,并未实例化,应用才算实例化。

新建模块时,REFERENCE里写编号,只有一个Reference,Implementation Type里选Schematic View,Implementation name里写模块所放文件夹的名称,而不是模块文件名。

如果一切正确,拖出模块之后,模块的端口会自动出现。

根据原理图放置位置再调一下就可以了。

5、防止误连有时会不小心把某条线拖到其它地方,或者一不小心动了某个元件。

这样就可能使这条线与其它线连在一起。

所以一定要小心。

否则会导出非计划的网表,会超级郁闷的。

有时觉得ALLEGRO设计的有道理,它的思路是选指令之后再进行具体操作。

偶像肖博士说,ALLEGRO的这种程序更好编,我目前的VC水平还无法理解,今晚要发奋学C了。

6、 DRC检测DRC检测可以发现设计中的许多错误,强烈建议使用。

7、生成ALLEGRO专用网表在元件属性中,设置PCB FOOTPRINT为封装。

封装名称要与ALLEGRO库中的名称对应。

正确生成网表的条件:(1)、每个出现在原理图的元件都要有封装。

如果此条件不满足,生成网表的过程就会出错。

(2)、原理图的封装引脚要与ALLEGRO库中元件封装的引脚相一致。

如果此条件不满足,则在ALLEGRO摆元件时,元件不会出现。

导致这种现象还有另外一个原因。

ALLEGRO库里没有这个封装,或者库的搜索路径没有设。

ALLEGRO专用网表生成之后会放在当前的工程文件夹内,默认为.\ALLEGRO。

文件是pstxnet.dat、pstchip.dat、 pstxprt.dat,对一般使用者意义不大。

8、 CAPTURE和ALLEGRO联合使用要注意凡是ALLEGRO里出现的东东,在CAPTURE里一定要有。

这样会避免ALLEGRO里出现未连的线。

因为如果只在ALLEGRO里加元件而CAPTURE里没有元件,就不会有飞线显示。

没有飞线易把这些后来加的导线忘掉。

9、其它CAPTURE非常好用,简单易学。

祝大家使用顺利。

ENJOY。

二、 ALLEGRO总述:与CAPTURE 相比,ALLEGRO要复杂一点。

ALLEGRO的特点是灵活,它为用户提供了很大的发挥空间。

用户可以设置电路板的很多细节。

使用ALLEGRO生成GERBER文件,再交给制板厂制板。

从本质上讲,PCB软件的目的就是生成GERBER文件和钻孔文件,所以至于在GERBER之前用什么软件无所谓。

GERBER文件是按层组织的,制板厂制板也是按层来做板,所以出GERBER还是比较接近生产实际的。

其实用PROTEL画完的板子交给制板厂之后也是要出GERBER的。

只不过PROTEL在中国大陆地区使用太多,制板厂为了方便用户就直接收PROTEL格式的文件了。

有的光绘机可直接读PROTEL格式文件。

我觉得用ALLEGRO画完板子之后,最大的进步是把电路板当成一层一层看了。

评价一个PCB软件的好坏,据偶像翟博士说是看这个软件拉线的水平怎样,偶像说的,一定有道理。

沉思中。

1、操作快速入门:(1)、ALLEGRO使用的是先发出指令再执行选择的方式。

发出指令之后,要特别注意OPTION栏内的参数。

如执行MOVE指令,在OPTION里可以设置指令选项,在FIND一档里可以设置选择的对象,如设本次操作的对象为TEXT,或VIAS等。

Find的最下面的一栏是Find by name,它支持通配符查找象。

如果找不到某个元件的位置,可以用这个功能快速查找。

Visibility里用于设置开关当前显示的层,但不是很全。

(2)、SLIDE命令拉完线之后,用于移动导线。

它也可以一次SLIDE选择的所有导线。

这是画板后期最常用的一个命令。

(3)、MIRROR将元件从TOP层移动到BOTTOM层或移回来。

(2)、显示某些元件的飞线。

这个功能刚开始拉线的时候可以只看想看的元件飞线,你的眼前将出现一片红樱桃,绿芭蕉,特清楚。

操作:Display->Show Rats->Components(2)、经常使用的快捷键。

F9:全局显示,类似于AUTOCAD里的Z (空格)A(空格) ;F10:放大,相当于CAPTURE里的I;F11:缩小,相当于CAPTURE里的O;F12:更改对象属性。

这里的属性不同于一般的属性概念。

较常用的是FIXED,如果将些属性值设为TRUE,则此对象将被固定。

Shift + F5: Measure测距;(3)、有特色的命令。

A、 F3,OOPS:在一个操作中撤消一小步。

例如删除指令是一个操作,在这个操作中删除了许多封装,若要撤消删除前一个封装的操作,使用OOPS指令,如果要撤消整个删除操作,就用撤消指令。

B、 Tools->Utilities->Stoke Editor: 我最喜欢的一个工具。

它完成的功能是按住右键在屏幕上画图形,如果图形和已经设好的图形类似,则执行预定的功能。

这个功能很好玩。

My favorite !C、 Z-COPY :将属于某一层的对象移动到另一层,并且可以放大或者缩小。

画板框的时候使用。

如画好了OUTLINE,要把这个范围COPY到Route Keepin层,用这个指令,就不用再画一遍。

(4)、Setup->Constrains设置DRC校验规则。

这个DRC校验的功能很强大。

Spacing rule set 设置线线间距或线与焊盘间距等间距规则;Physical rule set 用于设置最小线宽等。

2、 ALLEGRO中的文件(1)、文件名:*.dra: ALLEGRO绘图的图形文件,供编辑用,不可被ALLEGRO数据库调用。

做一个封装、焊盘等都要有这种格式的文件;*.psm:封装文件,画好*.dra文件后,手动生成;(2)、库文件。

最好建一个自己的库,将搜索路径指向那里。

操作:Setup->User Preferences->PATH。

元件的管理方式与PROTEL不一样,所有元件和焊盘都以单独的文件存储起来的。

可以单独编辑。

3、 ALLEGRO中的层ALLEGRO里的层太多,以前认为PROTEL中的层已经够多得了,见了ALLEGRO之后,顿觉PROTEL 中层真是太稀少了。

把思路拉到画PCB的目的中去,可以这样理解层:制板厂要什么层,PCB软件就生成什么层。

其它层起到的只是辅助作用。

以下几层是制板厂要的层:Silkscreen Top :Silkscreen Bottom :Top Layer ….Second Layer…..Bottom Layer :Soldermask Top :阻焊层顶层Soldermask Bottom : 阻焊层底层Pastemask Top :助焊层顶层。

助焊层对于只做两块板的用户来说是用不着的,用户自己焊就行。