计算机设计与实践——MIPS基本指令

mips指令集(24条指令)的字段和功能描述

MIPS指令集(24条指令)的字段和功能描述指令集概述M I PS(M ic ro pr oc es s or wi th ou tI nt erl o ck ed Pi pe li ne dSt a ge s)指令集是一种精简指令集(R IS C)体系结构,广泛应用于计算机体系结构的教学和实践中。

本文将介绍M IP S指令集中的24条常用指令,并对它们的字段和功能进行详细描述。

加载和存储指令1.l w指令字段描述:-指令格式:lw$r t,o f fs et($rs)-r s(源寄存器):指定存储单元的基址寄存器-r t(目标寄存器):指定目标寄存器,用于存储从存储单元中加载的数据-o ff se t:用于指定存储单元的偏移量,计算出实际地址功能描述:l w指令用于从存储单元中加载数据到目标寄存器。

它通过基址寄存器和偏移量计算出实际地址,并将存储单元中的数据加载到目标寄存器中。

2.s w指令字段描述:-指令格式:sw$r t,o f fs et($rs)-r s(源寄存器):指定存储单元的基址寄存器-r t(目标寄存器):指定源寄存器,用于存储到存储单元中的数据-o ff se t:用于指定存储单元的偏移量,计算出实际地址功能描述:s w指令用于将源寄存器中的数据存储到指定的存储单元中。

它通过基址寄存器和偏移量计算出实际地址,并将源寄存器中的数据存储到该地址对应的存储单元中。

算术和逻辑指令3.a d d指令字段描述:-指令格式:ad d$rd,$rs,$rt-r s(源寄存器1):参与运算的第一个源寄存器-r t(源寄存器2):参与运算的第二个源寄存器-r d(目标寄存器):用于存储运算结果功能描述:a d d指令用于将两个源寄存器中的数据相加,并将结果存储到目标寄存器中。

4.s u b指令字段描述:-指令格式:su b$rd,$rs,$rt-r s(源寄存器1):参与运算的第一个源寄存器-r t(源寄存器2):参与运算的第二个源寄存器-r d(目标寄存器):用于存储运算结果功能描述:s u b指令用于将源寄存器2中的数据从源寄存器1中的数据减去,并将结果存储到目标寄存器中。

mips汇编语言指令

mips汇编语言指令MIPS(Microprocessor without Interlocked Pipeline Stages)是一种精简指令集(RISC)架构的计算机处理器。

它的指令集被广泛应用于各种领域,包括嵌入式系统、操作系统和编译器等。

本文将介绍一些常见的MIPS汇编语言指令。

1. 加载和存储指令MIPS提供了一系列用于数据传输的指令。

其中,lw(load word)指令用于从内存中加载一个字(32位数据)到寄存器中,sw(store word)指令用于将一个字存储到内存中。

例如,lw $t0, 0($s0)表示将从地址$s0偏移量为0的内存位置加载一个字到$t0寄存器中。

2. 算术和逻辑指令MIPS提供了一系列用于算术和逻辑运算的指令。

例如,add指令用于将两个寄存器中的值相加,并将结果存储到目标寄存器中。

而and 指令用于对两个寄存器中的值进行按位与操作,并将结果存储到目标寄存器中。

例如,add $t0, $s0, $s1表示将$s0和$s1中的值相加,并将结果存储到$t0寄存器中。

3. 分支和跳转指令MIPS提供了一系列用于控制程序流程的指令。

其中,beq(branch if equal)指令用于在两个寄存器中的值相等时跳转到目标地址。

而j (jump)指令用于无条件跳转到目标地址。

例如,beq $t0, $t1, label表示如果$t0和$t1中的值相等,则跳转到标签为label的位置。

4. 移位指令MIPS提供了一系列用于移位操作的指令。

其中,sll(shift left logical)指令用于将一个寄存器中的值左移指定的位数,并将结果存储到目标寄存器中。

例如,sll $t0, $s0, 2表示将$s0中的值左移2位,并将结果存储到$t0寄存器中。

5. 系统调用指令MIPS提供了一系列用于进行系统调用的指令。

其中,syscall指令用于触发系统调用,并根据不同的系统调用号执行相应的操作。

mips基础指令

mips基础指令MIPS(Microprocessor without Interlocked Pipeline Stages)是一种高性能的RISC(Reduced Instruction Set Computing)指令集架构,其指令集被广泛应用于工业控制、嵌入式系统、服务器等领域。

MIPS指令集的特点是指令精简、寄存器丰富、执行效率高。

本文将主要介绍MIPS基础指令,帮助初学者快速入门。

一、MIPS基础指令结构MIPS指令的格式为“操作码r1,r2,r3”,其中操作码指示了该指令的功能,而r1、r2、r3分别指定了指令所需的操作数,通常为寄存器或常数。

以下是MIPS指令的分类:1.算术指令算术指令主要包括加、减、乘、除等指令,其中最基本的指令为ADD指令,格式为“ADD r1,r2,r3”,表示将r2和r3的值相加,存放到r1中。

其他的算术指令根据功能的不同,指定相应的操作码。

2.逻辑指令逻辑指令主要包括与、或、非、异或等指令,同样地,最基本的指令为AND指令,格式为“AND r1,r2,r3”,表示将r2和r3的值进行与运算,存放到r1中。

其他的逻辑指令根据功能的不同,指定相应的操作码。

3.移位指令移位指令主要包括逻辑左移、逻辑右移以及算术右移等指令,其中最基本的指令为SLL指令,格式为“SLL r1,r2,n”,表示将r2的值向左移动n位,空出的低位用0填充,存放到r1中。

其他的移位指令根据功能的不同,指定相应的操作码。

4.存取指令存取指令主要包括读、写、加载等指令,其中最基本的指令为LOAD指令,格式为“LOAD r1,addr”,表示将存储在addr地址中的数据加载到r1中。

其他的存取指令根据功能的不同,指定相应的操作码。

5.分支指令分支指令主要包括BZ(分支为零)、BC(分支为给定条件)、J(无条件跳转)等指令,其中最基本的指令为JUMP指令,格式为“JUMP addr”,表示将程序的控制跳转到addr地址处。

MIPS指令集汇总

MIPS指令集汇总以下是一些常用的MIPS指令:1.算术和逻辑操作:- add:将两个寄存器中的值相加,并将结果存储到目标寄存器中。

- sub:将第一个寄存器的值减去第二个寄存器的值,并将结果存储到目标寄存器中。

- mult:将两个寄存器中的值相乘,并将结果存储在两个特殊寄存器(HI和LO)中。

- div:将第一个寄存器的值除以第二个寄存器的值,并将结果存储在两个特殊寄存器(HI和LO)中。

- and:对两个寄存器中的值进行按位与操作,并将结果存储到目标寄存器中。

- or:对两个寄存器中的值进行按位或操作,并将结果存储到目标寄存器中。

- xor:对两个寄存器中的值进行按位异或操作,并将结果存储到目标寄存器中。

2.数据传输指令:- lw:从内存中加载一个字(4个字节)的数据到指定的寄存器中。

- sw:将指定寄存器中的数据存储到内存的指定位置中。

- lb:从内存中加载一个字节的数据到指定的寄存器中。

- sb:将指定寄存器中的数据的低8位存储到内存的指定位置中。

3.分支和跳转指令:- beq:如果两个寄存器中的值相等,则跳转到目标地址。

- bne:如果两个寄存器中的值不相等,则跳转到目标地址。

-j:无条件跳转到目标地址。

- jr:无条件跳转到一个寄存器中存储的地址。

- jal:有条件跳转到目标地址,并将返回地址保存在链接寄存器($ra)中。

4.系统调用指令:- syscall:执行一个系统调用,通过系统调用号(存储在$v0寄存器中)来定义执行的操作。

5.位移指令:- srl:对寄存器中的值进行逻辑右移。

- sll:对寄存器中的值进行逻辑左移。

- sra:对寄存器中的值进行算术右移。

除了上述指令外,还有一些其他的MIPS指令,如条件分支和加载延迟等。

此外,MIPS还支持浮点运算指令集(MIPS-FP),用于处理浮点运算。

总结起来,MIPS指令集包含了各种算术和逻辑操作、数据传输、分支和跳转、系统调用以及位移指令。

MIPS常用指令

寄存器的内容到另外一个寄存器

根据地址向量转入管态

从异常中返回到用户态

一个双精度浮点数与单精度浮点数相乘加,

结果为单精度

一个双精度浮点数与单精度浮点数相乘加, 结果为双精度

两个单精度浮点数相乘加,结果为单精度

两个定点寄存器的内容相除,也就是定点除 DDIV R1,R2,R3

不带符号的除法运算

DDIVU R1,R2,R3

一个双精度浮点数除以一个单精度浮点数, DIV.S F1,F2,F3 结果为单精度浮点数

一个双精度浮点数除以一个单精度浮点数, DIV.D F1,F2,F3

结果为双精度浮点数

两个单精度浮点数相除,结果为单精度

把一个数据从定点寄存器复制到浮点寄存器 MFC1 R1,F1

把一个数据从浮点寄存器复制到定点寄存器 MTC1 R1,F1

把一个 16 位的立即数填入到寄存器的高 16 LUI R1,#42

位,低 16 位补零

双字逻辑左移

DSLL R1,R2,#2

双字逻辑右移

DSRL R1,R2,#2

双字算术右移

DSRA R1,R2,#2

结果为双精度浮点数

两个单精度浮点数相乘,结果为单精度浮点 DMUL.PS F1,F2,F3

数

与运算,两个寄存器中的内容相与

ANDR1,R2,R3

一个寄存器中的内容与一个立即数相与

ANDIR1,R2,#3

或运算,两个寄存器中的内容相或

ORR1,R2,R3

一个寄存器中的内容与一个立即数相或

ORIR1,R2,#3

功能与 LB 指令相同,但读出的是不带符号的 LBU R1, 0(R2)

数据

功能与 LH 指令相同,但读出的是不带符号的 LHU R1, 0(R2)

mips核心指令

mips核心指令MIPS核心指令是一种常用于计算机体系结构中的指令集架构,它是一种基于RISC(精简指令集计算机)原则设计的指令集。

MIPS 核心指令集包括了许多常见的操作指令,如加载和存储指令、算术和逻辑指令、分支和跳转指令等。

下面将对MIPS核心指令集的一些重要指令进行介绍。

一、加载和存储指令1. Load Word(LW)指令:LW指令用于从内存中加载一个字(32位数据)到寄存器中。

它的语法为:LW $rt, offset($rs),其中$rt表示目标寄存器,offset表示偏移量,$rs表示基址寄存器。

这个指令非常常用,用于从内存中读取数据进行后续计算或操作。

2. Store Word(SW)指令:SW指令用于将一个字(32位数据)存储到内存中。

它的语法为:SW $rt, offset($rs),其中$rt表示源寄存器,offset表示偏移量,$rs表示基址寄存器。

SW指令常用于将计算结果存储到内存中,以便后续的读取和使用。

二、算术和逻辑指令1. Add(ADD)指令:ADD指令用于将两个寄存器中的值相加,并将结果存储到目标寄存器中。

它的语法为:ADD $rd, $rs, $rt,其中$rd表示目标寄存器,$rs和$rt表示源寄存器。

ADD指令常用于数值计算和数据处理中。

2. Subtract(SUB)指令:SUB指令用于将一个寄存器中的值减去另一个寄存器中的值,并将结果存储到目标寄存器中。

它的语法为:SUB $rd, $rs, $rt,其中$rd表示目标寄存器,$rs和$rt表示源寄存器。

SUB指令常用于进行减法运算。

3. Bitwise AND(AND)指令:AND指令用于对两个寄存器中的值进行按位与操作,并将结果存储到目标寄存器中。

它的语法为:AND $rd, $rs, $rt,其中$rd表示目标寄存器,$rs和$rt表示源寄存器。

AND指令常用于逻辑运算和掩码操作。

三、分支和跳转指令1. Branch on Equal(BEQ)指令:BEQ指令用于在两个寄存器中的值相等时进行分支跳转。

c语言 mips指令

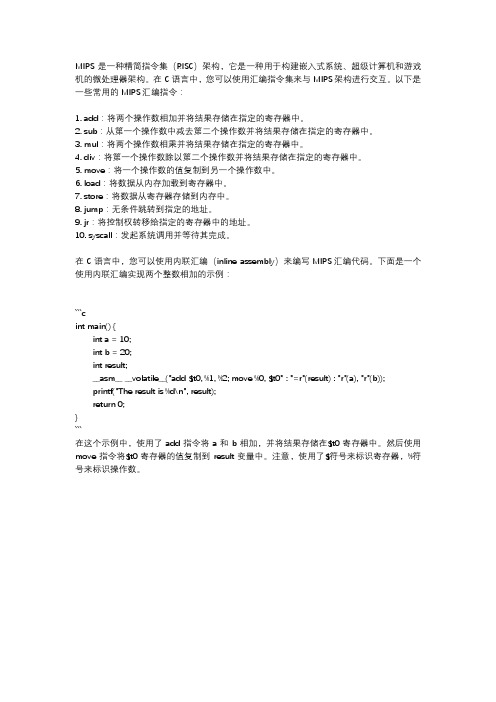

MIPS是一种精简指令集(RISC)架构,它是一种用于构建嵌入式系统、超级计算机和游戏机的微处理器架构。

在C语言中,您可以使用汇编指令集来与MIPS架构进行交互。

以下是一些常用的MIPS汇编指令:1. add:将两个操作数相加并将结果存储在指定的寄存器中。

2. sub:从第一个操作数中减去第二个操作数并将结果存储在指定的寄存器中。

3. mul:将两个操作数相乘并将结果存储在指定的寄存器中。

4. div:将第一个操作数除以第二个操作数并将结果存储在指定的寄存器中。

5. move:将一个操作数的值复制到另一个操作数中。

6. load:将数据从内存加载到寄存器中。

7. store:将数据从寄存器存储到内存中。

8. jump:无条件跳转到指定的地址。

9. jr:将控制权转移给指定的寄存器中的地址。

10. syscall:发起系统调用并等待其完成。

在C语言中,您可以使用内联汇编(inline assembly)来编写MIPS汇编代码。

下面是一个使用内联汇编实现两个整数相加的示例:```cint main() {int a = 10;int b = 20;int result;__asm__ __volatile__("add $t0, %1, %2; move %0, $t0" : "=r"(result) : "r"(a), "r"(b));printf("The result is %d\n", result);return 0;}```在这个示例中,使用了add指令将a和b相加,并将结果存储在$t0寄存器中。

然后使用move指令将$t0寄存器的值复制到result变量中。

注意,使用了$符号来标识寄存器,%符号来标识操作数。

mips 实验报告

mips 实验报告MIPS实验报告引言:计算机体系结构是计算机科学中的一个重要领域,它研究计算机硬件和软件之间的关系。

在计算机体系结构的学习过程中,我们接触到了MIPS (Microprocessor without Interlocked Pipeline Stages)指令集架构。

本实验报告将介绍我们在实验中对MIPS进行的学习和实践。

一、MIPS的背景和特点MIPS是一种经典的RISC(Reduced Instruction Set Computer)指令集架构,它于1981年由斯坦福大学的约翰·亨尼西(John Hennessy)和他的学生大卫·帕特森(David Patterson)提出。

MIPS架构的设计理念是简化指令集,提高指令执行速度,以及降低硬件复杂度。

MIPS指令集包含了一组简洁而强大的指令,使得编译器和硬件设计更容易实现。

该架构的特点包括高效的流水线执行、固定长度的指令格式、延迟槽等。

二、MIPS的实验环境和工具为了学习和实践MIPS指令集,我们使用了一款名为MARS(MIPS Assembler and Runtime Simulator)的工具。

MARS提供了一个模拟器,可以在计算机上运行MIPS指令。

它还提供了汇编器和调试器,方便我们编写和调试MIPS程序。

通过MARS,我们可以观察和分析指令的执行过程,更好地理解MIPS的工作原理。

三、MIPS的基本指令和寄存器MIPS指令集包含了一系列基本指令,如加载(Load)指令、存储(Store)指令、算术运算(Arithmetic)指令、逻辑运算(Logic)指令等。

这些指令可以完成各种计算和数据操作任务。

同时,MIPS架构还提供了32个通用寄存器,用于存储和操作数据。

这些寄存器以$0、$1、$2等命名,并且有特殊用途的寄存器如程序计数器(PC)和堆栈指针(SP)等。

四、MIPS程序设计实践通过MARS工具,我们编写了一些简单的MIPS程序,以加深对MIPS指令集和寄存器的理解。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

MIPS基本指令和寻址方式:MIPS是典型的RISC处理器,采用32位定长指令字,操作码字段也是固定长度,没有专门的寻址方式字段,由指令格式确定各操作数的寻址方式。

MIPS指令格式一般有三种格式:R-型指令格式I-型指令格式J理指令格式R_Type指指指指31 265bit 6bit OP:操作码rs:第一个源操作数寄存器rt: 第二个源操作数寄存器(单目原数据)rd: 结果寄存器shamt :移位指令的位移量func:指令的具体操作类型特点:R-型指令是RR型指令,其操作码0P字段是特定的000000”,具体操作类型由字段给定。

例如:func= 100000"时,表示加法"运算。

R[rd] —R[rs] + R[rt]I_Type 指指指指5bit 5bit 16bit 特点:I-型指令是立即数型指令双目运算:R[rt] R[rs] (OP) SignExt(imm16)Load指令:funcAddr J R[rs] + SignExt(imm16) M[Addr] J R[rt]J _Type 指令格式3126 256bit特点:J-型指令主要是无条件跳转指令, 将当前PC 的高4位拼上26位立即数,后补两个“ 0”, 作为跳转目标地址。

R 型指令:定点运算: add / addu , sub / subu , sra , mult/multu , div/divu逻辑运算:and / or / nor , sll / srl比较分支:beq / bne / slt / sltu跳转指令: jrI 型指令:定点运算: addi / addiu逻辑运算:andi / ori比较分支:slti / sltiu数据传送: lw / sw/ lhu / sh / lbu / sb / luiJ 型指令:j / jalAddr J R[rs] + SignExt(imm16) R[rt] J M[Addr]Store 指令:计算数据地址(立即数要进行符号扩展) 从存储器中取出数据,装入到寄存器中设计模块划分,教学安排1、MIPS格式指令系统设计2、指令存储器设计3、寄存器堆设计4、ALU设计---- 基本算术、逻辑单元的设计32位超前进位加法器的设计32位桶式移位寄存器的设计5、取指令部件的设计6、立即数处理单元设计7、单周期处理器设计一一R型指令的数据通路设计I型指令的数据通路设计Load/Store指令的数据通路设计分支指令/转移指令的数据通路设计综合12条指令的完整数据通路设计8、ALU控制单元设计9、主控制单元的设计10、单周期处理器总体验证11、异常和中断处理及其电路实现12、带有异常和中断处理功能的处理器的设计设计示例1指令存储器设计1指令存储器模块定义:指令存储器用于存放 CPU 运算的程序指令和数据等,采用单端口存储器设计,设计最 大为64个存储单元,每个存储单元数据宽度为32bit 。

下图为指令存储器的模块框图。

module ExtMemExtMem Adr ExtMem RD ExtMem CLK图1模块框图序号 接口信号名称方向(I/O )说明备注1 ExtMem_CLK I 存储器工作时钟,频率为50Mhz2 ExtMem_CS n I 存储器片选信号,低有效3 ExtMem_Adr [5:0] I 存储器地址线最大64个单兀4 ExtMem_WR n I 存储器写信号,低有效5 ExtMem_RD n I 存储器读信号,低有效6 ExtMem_Din [31:0] I 存储器输入数据线7 ExtMem_Dout [31:0]O存储器输出数据线8Vcc电源9Gnd地线ExtMem CS ExtMem Dout ExtMem WR ExtMem DinExtMem_CLK ExtMem_CS ExtMem_WR ExtMem_RD ExtMem_Adr ExtMem_Din图2存储器接口读时序框图reg [31:0] Memory [0: 63]; //---存储器写操作always @( posedgeExtMem )beginif (~ExtMem_CS end& ~ExtMem_WR )Memory[ExtMem_Adr]<= ExtMem_Di n;//---存储器读操作方式 1 always @( posedge ExtMem )beginExtMem_CLK ExtMem_CS ExtMem_WRExtMem_RD ExtMem_Adr ExtMem_Dout/Valid ) \/Valid\\图3存储器接口写时序框图ExtMem_CLK ExtMem_CS ExtMem_WR ExtMem_RD ExtMem_Adr ExtMem_Din ExtMem_DoutValidValid--------------- (Valid ' --------- ---------------------------------------------------- -------------------------------------------------------------- ■, Valid图4存储器接口读写时序框图2、设计电路源代码 Module ExtMem ( in putin put in put in put in put in put output ExtMem_CLK,ExtMem_CS, [5:0] ExtMem_Adr, ExtMem_WR, ExtMem_RD, [31:0] ExtMem_D in, [31:0] ExtMem_Dout )if (~ExtMem_CS & ~ExtMem_RD ) ExtMem_Dout<= Memory[ExtMem_Adr];end//--- 存储器读操作方式 2always @( * )beginif (~ExtMem_CS & ~ExtMem_RD ) ExtMem_Dout<= Memory[ExtMem_Adr];endendmodule问题讨论:// ----- 方式1 与方式2 的区别?// ----- altera 公司的FPGA 芯片,使用其内部存储器IP 必须采用方式1 设计// ----- xilinx 公司的FPGA 芯片,使用其内部存储器IP 可以采用方式1或方式2 设计3、指令存储器初始化值设计在仿真环境下,在设计电路中添加如下初始化存储器值电路:initialbegin#0 Memory[6'h0]<=32'h10; Memory[1]=32'h11; Memory[2]=32'h12;Memory[63]=32'h63;end问题讨论:在硬件设计实现方式下,如何给存储器付初值?4、设计电路仿真所设计的指令存储器模块电路,采用Active-HDL 8.1ver 仿真器工具进行了设计仿真验证,验证结果表明存储器功能以及接口时序完全正确,如下是仿真验证的波形图。

附件 1 是仿真激励源代码。

图5存储器电路读写仿真波形图5、存在问题及解决方式方法,设计讨论等XXXXXXXXXYYYYZZZZZZZZZZZ附件1:// -------------------------------------------------------- ////Desc:// -------------------------------------------------------- ////'timescale 10ps/10psmodule ExtMem_testbench ( );//--- 测试信号定义reg fpga_clk, mem_cs, mem_wr, men_rd;reg [5:0] mem_addr;reg [31:0] mem_din;wire [31:0] mem_dout;//---存储器模块实例化调用ExtMem mem_inst( .ExtMem_CLK(fpga_clk),.ExtMem_CS(mem_cs),.ExtMem_Adr(mem_addr),.ExtMem_WR(mem_wr),.ExtMem_RD(men_rd),.ExtMem_Din(mem_din), .ExtMem_Dout(mem_dout) );// ------------------------------always #50 fpga_clk<= ~fpga_clk;initialbegin#0 fpga_clk=1'h0; mem_cs=1'h1; mem_wr=1'h1; men_rd=1'h1; mem_addr=6'h00; mem_din=32'h00;end initialbegin#510 mem_cs=1'h0; mem_wr=1'h0; mem_addr=6'h01; mem_din=32'h01;#100 mem_addr=6'h02; mem_din=32'h02;#100 mem_cs=1'h1; mem_wr=1'h1;#100 mem_addr=6'h03; mem_din=32'h03;#100 mem_cs=1'h0; mem_wr=1'h0;#100 mem_cs=1'h1; mem_wr=1'h1; mem_addr=6'h04; mem_din=32'h04;#200 mem_cs=1'h0; men_rd=1'h0; mem_addr=6'h02; mem_din=32'hzz;#100 mem_addr=6'h03;#100 mem_cs=1'h1; men_rd=1'h1;#200 mem_cs=1'h0; men_rd=1'h0; mem_addr=6'h01;#200 mem_cs=1'h1; men_rd=1'h1;#100 mem_addr=6'hzz;end// --------------------------------------------------- //endmodule。