PowerCompiler_2010

VS2010与PB10开发和使用PBNI-初步使用3

PBNI初步使用三(函数功能调用-代码优化)下面讲解如何使用VS2010开发PB10.5版本PBNI组件应用实例:在VS中创建一个f_add的函数,实现2个int类型的数值进行相加。

PB调用和使用这个函数功能代码的优化。

1 优化和使用PBNIADD代码将项目管理中多余的文件进行删除,系统仅仅只是留下3个主要的文件。

Stdafx.h,PBNIAdd.cpp和PBNIAdd.h这三个文件。

如下图:stdafx,.h代码主要定义生成DLL文件的入口。

代码如下:#pragma once#ifndef STRICT#define STRICT#endif#ifndef WINVER#define WINVER 0x0400#endif#ifndef _WIN32_WINNT#define _WIN32_WINNT 0x0400#endif#define VC_EXTRALEAN // Exclude rarely-used stuff from Windows headers//Pull in support for Commctrl v6#ifdef _UNICODE#if defined _M_IX86#pragma comment(linker,"/manifestdependency:\"type='win32'name='mon-Controls' version='6.0.0.0' processorArchitecture='x86'publicKeyToken='6595b64144ccf1df' language='*'\"")#elif defined _M_IA64#pragma comment(linker,"/manifestdependency:\"type='win32'name='mon-Controls' version='6.0.0.0' processorArchitecture='ia64'publicKeyToken='6595b64144ccf1df' language='*'\"")#elif defined _M_X64#pragma comment(linker,"/manifestdependency:\"type='win32'name='mon-Controls' version='6.0.0.0' processorArchitecture='amd64' publicKeyToken='6595b64144ccf1df' language='*'\"")#else#pragma comment(linker,"/manifestdependency:\"type='win32'name='mon-Controls' version='6.0.0.0' processorArchitecture='*' publicKeyToken='6595b64144ccf1df' language='*'\"")#endif#endifPBNIApp.h代码主要声明类和函数。

PowerINSPECT常见问题

PowerINSPECT问题、解决

13)软件可以打开,但是很多图标都是灰色的, 且不能打开已有的测量文件。软件狗和授权 都没有问题。 有可能的解决方法:计算机系统的内存条松了, 重新插好内存条。

PowerINSPECT问题、解决 14)PI软件可以使用,EXCEL也可以正常使用(版本 也没有问题),报告模板变量也正确,但是在输出 报表时就是不能输出EXCEL,可以输出html格式报 告。 可能的原因:用光盘安装软件时,没有先安装一个文 件“MSXML 4.0 SP2 Parser and SDK”,就直接 安装的PI软件,这样就导致了不能启动EXCEL报表。 解决办法是:重新装一个干净的系统,最好不用克隆 方法安装,然后再装EXCEL,再装PI,这样就不会 有问题了。

PowerINSPECT问题如何解决

对于问题上述问题中的1~5)都可以的很方便 的解决。 方法是:从计算机的开始--运行-- regedit--HKEY_CURRENT_USER--Software-Delcam--Powerinspect,下面有相应的版 本序号。如果是4315版本,在关闭软件的情 况下,删掉4315这整个健值定义。同理,其 他版本同样处理

Delcam PowerINSPECT 4)在测量平面、圆时,没有测量向导图框; 5)如在测量平面、圆时,前面第一、二点没 有任何问题,在测取第三点后,不能接收测 量结果,然后跳出测量界面; 6)在实际的数模比对工作中,测量A面,但是 实际的比对确是在B面; 7)PowerINSPECT在测量一个面/点的时候在 跳出的面测量窗口内容往下滑动(包含应该 测量的点数,已经测量的点数等内容),都 下滑的无影无踪;

PowerINSPECT问题、解决

10)软件可以打开,也可以使用,但是不能对 重新打开的检测文件(用于数模对比)的数 模进行渲染。 这个是有一个和检测文件同名的odx文件没有 放置在同一目录下,把同名的pwi和odx文件 放置在同一目录下即可解决这个问题。

惠普 瘦客户机 用户指南

HP 瘦客户机©Copyright 2018 HP Development Company, L.P.Windows 是 Microsoft Corporation 在美国和/或其他国家/地区的注册商标或商标。

本文档中包含的信息如有更改,恕不另行通知。

HP 产品和服务附带的明示保修声明中阐明了此类产品和服务的全部保修服务。

本文档中的任何内容均不构成任何额外保证。

HP 对本文档中出现的技术错误、编辑错误或遗漏之处不承担任何责任。

第一版:2018 年 5 月文档部件号:L18409-AA1产品通告本用户指南介绍大多数机型的常见功能。

您的笔记本计算机上可能未提供某些功能。

并非所有功能在所有 Windows 版本中都可用。

系统可能需要升级和/或单独购买硬件、驱动程序或 BIOS 更新,以充分利用 Windows 功能。

Windows 10 会自动更新,此功能始终处于启用状态。

可能会收取 ISP 费用,在更新过程中可能还会有其他要求。

请参阅。

要获取最新版本的用户指南,请访问/support,然后按照说明查找您的产品。

然后选择用户指南。

软件条款如果安装、复制、下载或以其他方式使用此计算机上预安装的任何软件产品,即表明您同意受 HP 最终用户许可协议(EULA) 条款的约束。

如果您不接受这些许可协议条款,只需将未使用的产品(包括硬件和软件)在 14 天内完整地退回给您的经销商,并依据其退款政策申请全额退款即可。

有关任何其他信息或申请计算机的全额退款,请联系您的经销商。

关于此手册指示一种危险情况,如果不避免,可能导致设备损坏或信息丢失。

切记:表示重要但与危险无关的信息(例如,与财产损失相关的消息)。

系统会发出一个通知,提醒用户如果不完全按照所述的步骤进行操作,将可能导致数据丢失或硬/软件损坏。

此外还包含用于解释概念或完成任务的基本信息。

注:包含其他信息,以强调或补充正文的要点。

提示:提供完成任务的有用提示。

MPI+VS2010 配置及编译

MPI+VS2010 配置及编译分类:并行计算2013-04-06 16:57 1584人阅读评论(0) 收藏举报目录(?)[+]上学期学了多核计算,现在由于需要要重新配置环境,竟然忘了。

又走了很多弯路,所以还是要记录下来。

一下载mpi for windows在这一块我浪费了很多时间。

首先windows下(自己电脑的多核)和一般的工作站是不一样的。

windos为了兼容mpi,自己做了一个基于一般电脑的MPI实现,如果要安装真正意义的mpi,在intel上有。

我这里是为了在自己笔记本上学习mpi,用的市微软的HPC Pack 2008 R2 MS-MPI Redistributable Package with Service Pack 4 - 中文(简体),下载地址:。

不过如果是想在自己笔记本上用fortran版的mpi,即用fortran编译mpi,那么和这里的不一样。

这里是c 的。

fortran的以后添加。

二安装mpi我的电脑是64位的,所以安装的是mpi_x64.msi,默认安在C:\Program Files\Microsoft HPC Pack 2008 R2,三配置vs2010这里的配置有点多。

3.1配置目录,即加载Include和Lib库3.2配置运行库3.3预处理处理,这里至于为什么,我没搞懂,3.4加载依赖项四编译这是一个测试例子,在vs2010下编译生成xx.exe文件(具体看自己的命名) [cpp]view plaincopy1./*2.功能:mpi点对点通信3.时间:2012.12.134.*/5.#include<stdio.h>6.#include<string.h>7.#include"mpi.h"8.9.#define BUFLEN 51210.int main(int argc, char *argv[])11.{12.int myid,numprocs,next,namelen;13.char buffer[BUFLEN],processor_name[MPI_MAX_PROCESSOR_NAME];14. MPI_Status status;15.16.//17. MPI_Init(&argc, &argv);18. MPI_Comm_size(MPI_COMM_WORLD, &numprocs);19. MPI_Comm_rank(MPI_COMM_WORLD, &myid);20. MPI_Get_processor_name(processor_name, &namelen);21.22. printf("Process %d on %s \n", myid, processor_name);23. printf("Process %d of %d \n", myid, numprocs);24. memset(buffer, 0, BUFLEN*sizeof(char));25.if(myid == numprocs-1)26. {27. next = 0;28. }29.else30. {31. next = myid+1;32. }33.if(myid == 0)34. {35. strcpy(buffer,"hello there");36. printf("%d sending '%s' \n",myid, buffer);fflush(stdout);37. MPI_Send(buffer,strlen(buffer)+1, MPI_CHAR, next, 99, MPI_COMM_WORLD);38. printf("%d receving \n", myid);fflush(stdout);39. MPI_Recv(buffer, BUFLEN, MPI_CHAR, MPI_ANY_SOURCE, 99, MPI_COMM_WORLD, &status);40. printf("%d received '%s' \n", myid, buffer);fflush(stdout);41. }42.else43. {44. printf("%d receiving \n",myid);fflush(stdout);45. MPI_Recv(buffer, BUFLEN, MPI_CHAR, MPI_ANY_SOURCE, 99, MPI_COMM_WORLD, &status);46. printf("%d received '%s' \n", myid, buffer);fflush(stdout);47. MPI_Send(buffer,strlen(buffer)+1, MPI_CHAR, next, 99, MPI_COMM_WORLD);48. printf("%d sending '%s' \n",myid, buffer);fflush(stdout);49. }50. MPI_Finalize();51.return 0;52.}五运行因为mpi是有命令行输入的,需要mpiexec.exe来运行,具体的命令可以help 一下,自己摸索吧。

Powerpc构架系统内核和内核模块调试.

Powerpc构架系统内核和内核模块调试Powerpc构架系统内核和内核模块调试类别:嵌入式系统作者:易松华,华清远见嵌入式学院深圳中心讲师。

说明:此文档的目标系统为freescale MPC8349E-mITX,对其他采用POWERPC,MIPS,ARM的芯片的系统亦具有参考意义。

此文档中内核调试为了简化,采用目标系统中的UBOOT初始化目标板,并通过UBOOT或者BDI2000加载内核到目标板的RAM中。

1.BDI2000配置:下面是MPC8349E-mITX的BDI2000配置文件,; BDI-2000 Configuration file for the MPC8349E-mITX ; Tip: If after a reset, the BDI-2000 fails to halt at 0x100, ; you may need to power-down the board for a few seconds. [INIT] ; we use UBOOT to initialize the board [TARGET] CPUTYPE 8349 JTAGCLOCK 1 ;STARTUP RESET STARTUP RUN BREAKMODE HARD STEPMODE HWBP BOOTADDR 0x00000100 ;If you're getting "Writing to workspace failed" errors during flash operations, ;then try uncommenting this line instead. This moves the FLASH windowto ;high memory, leaving low memory available for DDR. RCW0xb060a000 0x04040000 ;Set the HRCW to boot the image at 0xFE000000 MMU XLAT ;0xc0000000 PTBASE 0xf0 ; [HOST] IP 192.168.7.90 FILE $u-boot.bin LOAD MANUAL PROMPT 8349E-mITX-GP> DUMPitx-dump.bin [Flash] CHIPTYPE AM29BX16 CHIPSIZE 0x800000 BUSWIDTH 16 ;WORKSPACE 0x1000 FORMAT BIN0xfe000000 ;flash_image.bin is an image file of an entire 8MBflash region. ;Flash this file at 0xfe0000000 to restore all of flash. ;ERASE 0xFE000000 0x10000 127 ; 127 sectors @ 64KBeach ;ERASE 0xFE7F0000 0x2000 8 ; 8 sectors @ 8KB each ;FILE $flash_image.bin ;Use these lines if you just want to flash U-Boot ERASE 0xfe000000 0x10000? 4; Erase 384KB, each sector is64KB FILE? mpc8349e/u-boot131-mitx-gp.bin [REGS] FILE $reg8349e.def 以上配置文件的【HOST】段的IP要改为主机IP,关键的字段MMU XLAT 和PTBASE 是POWERPC和MIPS经常需要设置的,关于PTBASE的具体设置,超出本文范围,详细情况请参考BDI2000的手册 2.内核修改和配置为了能够调试内核,需要在内核中的Makefile中增加如下调试选项:CFLAGS 增加C代码调试选项-g –ggdb AFLAGS 增加汇编代码调试选项:-Wa,-L -gdwarf-2 去掉CFLAGS编译选项中-fomit-frame-pointer GCC的-fomit-frame-pointer选项是优化函数栈回溯(stack backtrace)的,我们调试的时候需要提供函数回溯能力,所以我们要去掉这个选项,当然,有的系统系统不受它的影响,或者说它不起作用,为了统一,我们统一去掉它。

PowerMILL安装版安装破解说明

PowerMILL 及相关软件安装说明一.软件安装.安装PowerMILL 及相关软件:1.安装PowerMILL2010_RC1_Full(PowerMILL2010主程序)2.安装Exchange612005(图档格式转换)3.安装DuctPost1510(后处理程序)4.完全汉化PowerMILL2010软件.因为原版有些没汉化到位,还有英文.要全面中文化可将PowerMILL 11.0.10文件夹覆盖到安装目录的PowerMILL 11.0.10文件夹即可.二.破解方法此破解能运行在32位或64位的XP,Vista 和Win7系统.支持以下软件的以下版本:PowerMILL 8009,PowerMILL 9003,PowerMILL 10006,PowerMILL 2010RC1PowerSHAPE 8080,PowerSHAPE 8124,PowerSHAPE 2010SP4CopyCAD 7350,CopyCAD 2010SP1)PowerINSPECT 6020,PowerINSPECT 2010SP1(with additinal DLL patching!)Exchange 61205Ductpost 1516PostProcessor v7SP1FeatureCAM 2010SP5DentMIIL 5070Dental Suit 2010SP4Delcam for SolidWorks v16.8.0.23FlexLM 服务安装:1.如果有请删除所有旧的Delcam PAF 许可文件(它可能在你电脑中的C:\dcam\config\pass\*.paf,C:\Program Files\Common Files\Delcam\*.paf)2.复制文件夹"Flex"到你的计算机中(如将"Flex"文件夹复制到"D:\Program Files\Delcam"目录下).因为杀毒软件可能会误报为病毒,最好先关掉杀毒软件或将为杀毒软件可能会误报为病毒,最好先关掉杀毒软件或将"Flex""Flex""Flex"目录设置为"可信任程序目录设置为"可信任程序目录设置为"可信任程序””3.设置系统环境变量:变量名:DELCAM_LICENSE_FILE 变量值:1700@计算机名(如:1700@CNC)4.FlexLM服务设置步骤a.运行Flex服务目录中的"lmtools.exe"(如:D:\Program Files\Delcam\Flex\lmtools.exe)b.在"Services/License File"中选"Configuration using Services"c.转到"Config Servises"选项卡,开始创建并配置Delcam FlexLM服务器:各类CAD/CAM模具设计软件和视频教程资料1)在"Service Name"中任意输入新的配置名(如:DELCAM)2)点击"Path to the lmgrd.exe file"右边的"Browse"浏览并选取文件"D:\ProgramFiles\Delcam\Flex\lmgrd.exe"3)点击"Path to the license file"右边的"Browse"浏览并选取文件"C:\ProgramFiles\Delcam\Flex\delcam.lic"4)点击"Path to the debug log file"右边的"Browse"浏览并选取文件""C:\ProgramFiles\Delcam\Flex\delcam.log"5)勾选"Start Server at Power Up"和"Use Servise"选项.6)点击"Save Servise"保存此配置d.打开"Start/Stop/Reread"选项卡并点击"Start Server".e.关闭LMTOOLSf.必须确认"lmgrd.exe"和"delcam.exe"两个进程能在系统的任务管理器中看到.才表示配置成功.(同时按键盘的Crtl+Alt+Del三个键能打开任务管理器)5.以上是所有的操作步骤.更多软件请点击。

Power Compiler

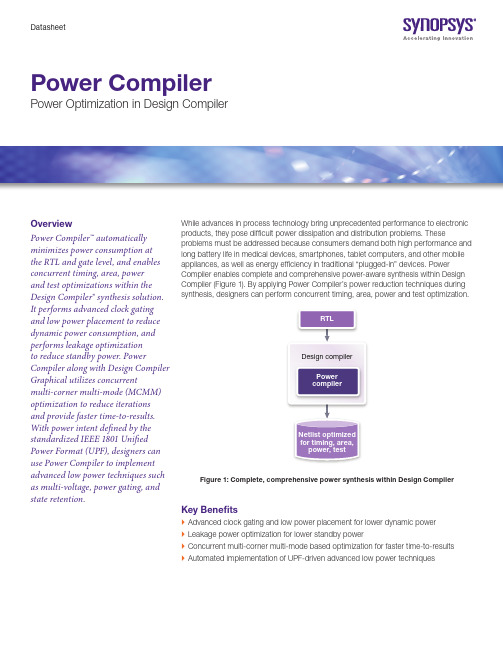

DatasheetPower CompilerPower Optimization in Design CompilerOverviewPower Compiler™ automaticallyminimizes power consumption atthe RTL and gate level, and enablesconcurrent timing, area, powerand test optimizations within theDesign Compiler® synthesis solution.It performs advanced clock gatingand low power placement to reducedynamic power consumption, andperforms leakage optimizationto reduce standby power. PowerCompiler along with Design CompilerGraphical utilizes concurrentmulti-corner multi-mode (MCMM)optimization to reduce iterationsand provide faster time-to-results.With power intent defined by thestandardized IEEE 1801 UnifiedPower Format (UPF), designers canuse Power Compiler to implementadvanced low power techniques suchas multi-voltage, power gating, andstate retention.While advances in process technology bring unprecedented performance to electronicproducts, they pose difficult power dissipation and distribution problems. Theseproblems must be addressed because consumers demand both high performance andlong battery life in medical devices, smartphones, tablet computers, and other mobileappliances, as well as energy efficiency in traditional “plugged-in” devices. PowerCompiler enables complete and comprehensive power-aware synthesis within DesignCompiler (Figure 1). By applying Power Compiler’s power reduction techniques duringsynthesis, designers can perform concurrent timing, area, power and test optimization.Figure 1: Complete, comprehensive power synthesis within Design CompilerKey Benefits``Advanced clock gating and low power placement for lower dynamic power``Leakage power optimization for lower standby power``Concurrent multi-corner multi-mode based optimization for faster time-to-results``Automated implementation of UPF-driven advanced low power techniquesRTLDesign compilerPowercompilerNetlist optimizedfor timing, area,power, testPower Compiler 2Figure 2: Power Compiler performs automatic clock gating to reducedynamic power consumption.Figure 3: Power-aware placement minimizes capacitance on high activity netsD_IN DEN CLKENCLKD_OUTQStandard non clock-gating ImplementationPower compiler gated-clock ImplementationFFLTalways @ (posedge CLK) if (EN)D_OUT = D_INRegister BankICGAdvanced Clock GatingPower Compiler reduces dynamic power consumption by gating the clocks of synchronous load-enable register banks instead of circulating the outputs back to the inputs when the load-enable conditions are invalid (Figure 2). The operations are performed automatically during the design elaboration phase without requiring any changes to the RTL source, enabling fast and easy trade-off analysis and maintaining technology-independent RTL source. Power Compiler’s clock gating can also be performed at the gate level and can complement manual clock gating. The tool supports several advanced clock gating techniques, including self-gating, multi-stage, latency-driven, activity-driven (using SAIF files) and user-instantiated clock gating.Low Power PlacementIn addition to clock gating, Power Compiler along with Design Compiler Graphical, performs power-aware placement, This capability utilizes the same technology as IC Compiler to minimize net length on signals with high switching activity, in order to minimize dynamic power consumption.Leakage Power OptimizationPower Compiler reduces leakage power using multi-voltage threshold based optimization, or by the designer’s specifying a maximum percentage of low-voltage threshold cells to be used in a design. Power Compiler measures the trade-offs between positive timing slacks, area and power, and delivers the lower power-consuming design that meets the timing constraints.Concurrent Multi-Corner Multi-Mode Based OptimizationConcurrent MCMM optimization isessential for fast turnaround time when implementing designs that can operate in many modes such as test mode, low-power active mode, stand-by mode, etc. One of the primary benefits of MCMM is the ability to achieve optimal leakage results without performing either leakageLow activityHigh activityLow activityHigh activity01/14.AP.CS3874.Synopsys, Inc. • 700 East Middlefield Road • Mountain View, CA 94043 • ©2014 Synopsys, Inc. All rights reserved. Synopsys is a trademark of Synopsys, Inc. in the United States and other countries. A list of Synopsys trademarks is available at /copyright.html . All other names mentioned herein are trademarks or registered trademarks of their respective owners.power optimization on the same corner as timing optimization or successive leakage-timing optimizations (using differentcorners for worst-case timing and worst-case leakage).MCMM optimization in Design Compiler Graphical and Power Compiler takes all of the different process corners into account to provide the best leakage results with minimal impact on performance. The ability to concurrently optimize for multiple modes and corners enables rapid design convergence through fewer design iterations. Used with UPF power intent specification, MCMM serves as the key enabling technology for performing dynamic voltage and frequency scaling (DVFS).Automated Implementationof Advanced Low Power TechniquesEarly definition of power intent in thedesign flow enables downstream tasks in the process to be automated and driven by a consistent power specification. Power intent includes the specification of multiple voltage supplies, power domains, power shutdown modes, isolation, voltage level shifting and state retention behavior. Power intent written in the IEEE 1801 Unified Power Format (UPF) is used systematically throughout the design process to describe thedesign power intent, and is captured as a companion file to the RTL or gate level design. This power intent automates the implementation of the advanced low power capabilities employed.Power Compiler takes UPF input and automatically inserts power management cells such as isolation, level-shifter, retention register, power gating and always-on cells as needed based on the power domain, strategy and state definitions. It also supports a “golden UPF” flow that preserves original power intent across the entire design flow.Netlist Formats and InterfacesPower Compiler is seamlessly integrated with the Synopsys synthesis design flow and shares the same GUI, commands, constraints and libraries as the Design Compiler and IC Compiler ® tools. It supports all popular industry standard formats and platforms.Circuit Netlist:``Verilog, SystemVerilog, VHDL Interfaces: ``SDF, PDEF, SDC Platforms:``IBM AIX (32-/64-bit)``Redhat Linux (32-/64-bit) ``Sun Solaris (32-/64-bit)SummaryPower Compiler delivers complete and comprehensive power synthesis within Design Compiler, including advanced clock gating for dynamic power savings, leakage power optimization for lower standby power and concurrent MCMM of leakage and timing corners. Power Compiler also supports automated implementation of low power methodologies using UPF.For more information on Synopsys’ Advanced Low Power Solution, visit /lowpower.。

c++ redistributable 2010

c++ redistributable 2010【实用版】目录1.C++ Redistributable 2010 简介2.C++ Redistributable 2010 的功能与特点3.C++ Redistributable 2010 的安装与使用4.C++ Redistributable 2010 的优势与不足5.总结正文C++ Redistributable 2010 是一款由微软公司开发的 C++ 编程工具集,可用于 Windows 平台的应用程序开发。

该工具集提供了一系列的库和工具,可以帮助开发人员快速、高效地编写 C++ 代码。

以下是该工具集的功能与特点:C++ Redistributable 2010 提供了多种库和工具,包括 C++ 标准库、ATL(Active Template Library)、MFC(Microsoft Foundation Class) 等。

这些库和工具可以帮助开发人员轻松地实现各种功能,例如文件操作、网络通信、图形界面等。

该工具集还提供了一种名为“C++/CX”的新的编程模型,可以使得开发人员更容易地编写跨平台的 C++ 代码。

C++/CX 提供了对 Windows 8 API 的支持,同时也支持其他操作系统和平台。

C++ Redistributable 2010 的安装非常简单,只需要下载相应的安装程序,然后按照提示进行安装即可。

安装完成后,开发人员可以使用该工具集提供的命令行工具和 IDE 插件来进行 C++ 编程。

虽然 C++ Redistributable 2010 提供了许多功能和工具,但是它也有一些不足之处。

例如,它只支持 Windows 平台,对于其他操作系统和平台的支持不够完善。

此外,该工具集的文档和帮助也比较有限,需要开发人员自己进行学习和探索。

C++ Redistributable 2010 是一款功能强大的 C++ 编程工具集,可以帮助开发人员快速、高效地编写 Windows 平台的应用程序。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Gate-level Power Optimization Clock Gating

Synopsys 10-I-061-SG-007© 2005 Synopsys, Inc. All Rights Reserved

6

Unit Objectives

After completing this unit, you should be able to

Isht Iintsw

N

Isht Isw

Cint

Gnd N

Out

Internal power (dynamic):

Ileak

Ileak

Cload

Gnd

Leakage power (static):

Vdd

In

Out

Cload

Gnd

Internal power != Short Circuit Power

Recognize power information in library Evaluate the quality of a library Calculate power manually at gate-level

7

Low Power Methodology

Modeling:

} pin(clk) { …... internal_power() { rise_power(trans_time) { values( “0.55, 0.6, 0.7”); } } .........

Unit

Templates

Internal Power Tables

12

Leakage Power In Library

Unit of C, V The “nom_voltage” used as default voltage “power_supply” defines multiple voltages used in the library Input pin capacitance is part of the driving cell’s output load “output_signal_level” specifies voltage used for computing switching power

Cell

4 toggles 40ns

Toggle rate (Tr) is Toggles / time Dynamic power equals to energy times toggle rate P(dyn) = E(toggle) * Tr Power analysis needs toggle on every node

The infrastructure for power management Library models for ASIC design Provides visibility into power consumption Required at all levels of abstraction Based on scenario simulation Reduces power consumption at all levels of abstraction

Vdd2

Default leakage

leakage_power() { power_level } leakage_power() { power_level VDD2 ; value : 6.332 ; } leakage_power() { power_level VDD1 ; when : "!A1 A2" ; value : 4.792 ; } leakage_power() { power_level VDD2 ; when : “!A1 A2" ; value : 5.176 ; } VDD1 ; value : 3.459 ;

9

Calculate Cell Power

Switch Power:

Dependent on output load and input transition Pre-processed by characterization tools Stored in library power lookup tables SDPD (state dependent path dependent) Pre-processed by characterization tools Stored in library SD (state dependent)

library (power) { ...... leakage_power_unit : 1pW; default_cell_leakage_power : k_volt_cell_leakage_power : k_temp_cell_leakage_power : k_process_cell_leakage_power ....... cell (AN2) { area : 2.0; cell_leakage_power : 0.5678; leakage_power() { when : "!A & !B" ; value : 0.0175811 ; } leakage_power() { when : "!A & B" ; value : 0.0184178 ; }

14

Toggle Rate Based Average Power Analysis

Digital circuit consumes dynamic energy E(toggle) for each toggle 4 toggles consumes energy E(dyn) = E(toggle) * 4

3

Agenda

DAY 1

1 2 3 4 5

Power Modeling Design-Compiler Overview Power Analysis

Gate-level Power Optimization Clock Gating

Synopsys 10-I-061-BSG-007

© 2005 Synopsys, Inc. All Rights Reserved

Power Compiler

Synopsys Customer Education Services

© 2010 Synopsys, Inc. All Rights Reserved Synopsys 10-I-061-BSG-007

1

Workshop Goal

Acquire basic skills to analyze and optimize for power using Synopsys Power Compiler.

4

Icons Used In This Workshop

Hint, tip or suggestion Additional information

Caution or warning

5

Agenda

DAY 1

1 2 3 4 5

Power Modeling Design-Compiler Overview Power Analysis

2

Workshop Prerequisites

Understanding of digital IC design Working knowledge of Design Compiler Knowledge of Verilog simulation Familiar with LINUX environment

11

Internal Power In Library

library (power) { ........ voltage_unit : “1V” capacitive_load_unit(1,pf); ........ power_lut_template(load_trans) { variable_1 : total_output_net_capacitance; variable_2 : input_transition_time; index_1 ( “0.1, 5.0, 6.0”); index_2 ( “0.1, 3.0, 7.0, 15.0, 20.0”); } power_lut_template(load_only) { variable_1 : total_output_net_capacitance; index_1 ( “0.0, 5.0, 10.0”); } power_lut_template(trans_time) { variable_1 : input_transition_time; index_1 ( “0.0, 3.0, 20.0”); }

values ("1.934150, 2.148130"); } } internal_power() { power_level : VDD2 ; power (power_rl) { values ("1.032871, 0.823947");

States must be identical for different rails

Analysis:

Optimization:

8

Power Model

CMOS cell power model

Vdd P In Vdd P

Switch power (dynamic):

Charging output load Short circuit; Charging internal load Stable state