NIOSII开发板原理图

NIOS II Step By Step

/bbs/showbbs.asp?bd=3&id=80&totable=1NIOS II Step By Step(1)---NIOS II自定义指令可编程软核处理器最大的特点是灵活,灵活到我们可以方便的增加指令,这在其他SOC系统中做不到的,增加用户指令可以把我们系统中用软件处理时耗费时间多的关键算法用硬逻辑电路来实现,大大提高系统的效率,更突出的一点是:我们通过下面的逐步操作会认识到,这是一个听起来高深,其实比较容易实现的功能(我们站在EDA工具这个巨人肩上,风光无限啊:),通过这一文档的介绍可以增强我们掌握NIOS II所有的技术手段的信心,这也是我把NIOS II 用户指令放在最前面的用意。

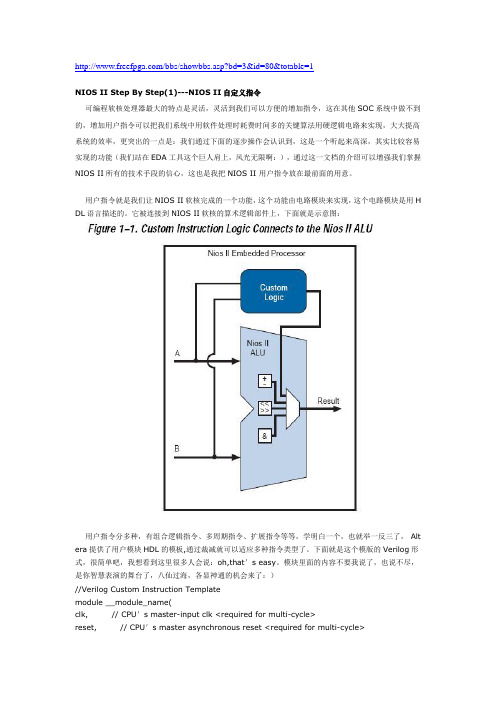

用户指令就是我们让NIOS II软核完成的一个功能,这个功能由电路模块来实现,这个电路模块是用H DL语言描述的。

它被连接到NIOS II软核的算术逻辑部件上,下面就是示意图:用户指令分多种,有组合逻辑指令、多周期指令、扩展指令等等,学明白一个,也就举一反三了, Alt era提供了用户模块HDL的模板,通过裁减就可以适应多种指令类型了。

下面就是这个模版的Verilog形式,很简单吧,我想看到这里很多人会说:oh,that's easy。

模块里面的内容不要我说了,也说不尽,是你智慧表演的舞台了,八仙过海,各显神通的机会来了:)//Verilog Custom Instruction Templatemodule __module_name(clk, // CPU's master-input clk <required for multi-cycle>reset, // CPU's master asynchronous reset <required for multi-cycle>clk_en, // Clock-qualifier <required for multi-cycle>start, // True when this instr. issues <required for multi-cycle>done, // True when instr. completes <required for variable muli-cycle> dataa, // operand A <always required>datab, // operand B <optional>n, // N-field selector <required for extended>a, // operand A selector <used for Internal register file access>b, // operand b selector <used for Internal register file access>c, // result destination selector <used for Internal register file access> readra, // register file index <used for Internal register file access>readrb, // register file index <used for Internal register file access>writerc,// register file index <used for Internal register file access>result // result <always required>);input clk;input reset;input clk_en;input start;input readra;input readrb;input writerc;input [7:0] n;input [4:0] a;input [4:0] b;input [4:0] c;input [31:0]dataa;input [31:0]datab;output[31:0]result;output done;// Port Declaration// Wire Declaration// Integer Declaration// Concurrent Assignment// Always Constructendmodule下面两张图和表可以帮助我们更深入的理解和总结:万事开头难,那我们就挑个软的捏,来做一条组合逻辑指令吧,下面就是模块示意图:,这个模块只有两个输入,A,B,都是32BIT的,输出也是32BIT的。

第1节 Nios II IDE简介

Nios II EDS(Embedded Design Suite——嵌入式开发包)提供了一个统一的开发平台,适用于所有Nios II处理器系统。

仅仅通过一台PC机、一片Altera的FPGA以及一根JTAG下载电缆,软件开发人员就能够往Nios II 处理器系统写入程序以及和Nios II处理器系统进行通讯。

Nios II处理器的JTAG 调试模块提供了使用JTAG下载线和Nios II处理器通信唯一的、统一的方法。

无论是单处理器系统中的处理器,还是复杂多处理器系统中的处理器,对其的访问都是相同的。

用户不必去自己建立访问嵌入式处理器的接口。

Nios II EDS 提供了两种不同的设计流程,包括很多生成Nios II程序的软件工具,包括需要版权的和开源软件工具如,GNU C/C++ 工具集。

Nios II EDS为基于Nios II的系统自动生成板支持包(board support package——BSP)。

Altera的BSP包括Altera硬件抽象层(hardware abstraction layer——HAL),可选的RTOS,设备驱动。

BSP提供了C/C++运行环境,使用户避免直接和硬件打交道。

Nios II EDS 的第一种开发流程是用户在集成开发环境Nios II IDE中完成所有的工作,第二种开发流程是在命令行和脚本环境中使用Nios II 软件生成工具,然后将工程导入到IDE中进行调试。

本书介绍使用Nios II IDE进行软件设计的流程,Nios II IDE基于开放式的、可扩展Eclipse IDE project工程以及Eclipse C/C++ 开发工具(CDT)工程。

Nios II集成开发环境(IDE)是Nios II系列嵌入式处理器的基本软件开发工具。

所有软件开发任务都可以Nios II IDE下完成,包括编辑、编译和调试程序。

Nios II IDE为软件开发提供四个主要的功能:工程管理器编辑器和编译器调试器闪存编程器6.1.1 工程管理器The Nios II IDE提供多个工程管理任务,加快嵌入式应用程序的开发进度。

NiosIISOPC开发PPT课件

27.12.2020

.

44

SOPC Builder界面分成三个部分,界面左边是组件 (Nios II嵌入式系统元件)选择栏,用树型结构列出了SOPC Builder的组件;右边空白处用于加入用户定制Nios II系统的组 件;下方是提示栏,用于显示SOPC Builder的提示信息和警告 错误信息。在界面的右上方,可以选择器件系列和系统工作频 率。

27.12.2020

.

66

(1)加入NIOS CPU CORE(CPU核) 在SOPC Builder的组件库中,用鼠标双击Component

Library(组件库)中的“Nios II Processor”项,弹出添加新 的Nios II(CPU核)对话框。 在对话框中提供Nios II系列微处理器的三个成员供选择: ① Nios II/e(经济型)成员,具有占用最小逻辑的优化,占用 600~700LEs(逻辑元件)。 ② Nios II/f(快速型)成员,具有高性能的优化,占用1400~ 1800LEs。 ③ Nios II/s(标准型)成员,在占用逻辑和高性能优化方面的 性能居中,占用1200~1400LEs。

用VHDL或Verilog HDL来定制外设。

Nios II的硬件开发必须得到特定的开发板的硬件支持。下

面以DE2(含DE2 70)开发板为例,介绍Nios II(9.0版本)

硬件开发的具体流程。

在DE2开发板上,支持Nios II系统的外部设备包括

SDRAM、SRAM、FLASH、LCD、七段数码管、发光二极管、

27.12.2020

加入UA. RT对话框

1100

(4) 加入BUTTON PIO DE2开发板上有4只按钮开关key3~key0,设计中需要加

NiosⅡ嵌入式处理器设计

并行计算

03

利用多个处理器核心同时处理多个数据,实现大规模数据处理。

动态调度技术

静态调度

在编译时确定指令的执行顺 序。

动态调度

在运行时根据指令的依赖关 系和资源冲突,动态调整指 令的执行顺序。

编译器优化

利用编译器对程序进行优化 ,减少冗余指令和优化指令 执行顺序。

05 NIOS II处理器应用实例

静态并行

通过编译器优化,将多个独立无依赖的指令并 行执行。

动态并行

在运行时根据指令之间的依赖关系,将无依赖 的指令并行执行。

超标量并行

通过增加硬件资源,同时执行多个指令,提高处理器的并行处理能力。

数据并行技术

单指令多数据流

01

在同一时刻对多个数据执行相同的操作,实现数据并行处理。

向量化

02

将数据分组,对每组数据执行相同的操作,提高数据处理速度。

高效能DSP算法

对于通信系统中的数字信号处理需求,如解调、调制、滤 波等,NIOS II处理器能够高效地实现各种DSP算法。

数字信号处理应用

数字信号处理应用

在数字信号处理领域,NIOS II处理器广泛应用于音频、视频、雷达、导航等信号处理 场景。它能够快速处理大量的数字信号数据,实现实时信号分析和处理。

感谢您的观看

调试与仿真工具

JTAG调试器

通过JTAG接口进行硬件调试,支持实时跟踪、断点、单步执行等 功能。

ModelSim仿真软件

用于模拟和验证硬件设计,支持多种硬件描述语言,如VHDL和 Verilog。

SOPC Builder

用于构建可定制的片上系统(SOPC),支持将多个IP核组合在一 起,并生成相应的硬件描述语言代码。

第8章 Nios II系统高级开发技术

8.2 定制基于Avalon的用户外设

9.选择SW Files选项卡打开添加文件对话框,将路径指向软件文件所在的文件夹。

8.2 定制基于Avalon的用户外设

10. 选择Component Wizard选项卡。

8.2 定制基于Avalon的用户外设

11.可以单击Preview the Wizard 按钮进行预览。

第8章 目录

8.1 定制Nios II用户指令 8.2 定制基于Avalon的用户外设

8.2 定制基于Avalon的用户外设

定制用户外设简介

一个典型元件定制的步骤如下:

1.规划元件的硬件功能。 2.如将采用微控制器来控制该元件,则规划访问该硬件的应用程序接口(API)。

3.在硬件和软件要求的基础上,定义一个恰当的Avalon接口。

最简单的也最容易使用的是通过内建(Built-in)函数和宏定义使用定制指令。

内建(Built-in)函数的格式如下: _builtin_custom_<返回类型>n<参数类型>

i表示int(整型),f表示float(浮点),p表示void*(指针)。

使用汇编指令使用定制指令时,汇编指令的格式如下: Custom N,xC,xA,xB

第8章 目录

8.1 定制Nios II用户指令 8.2 定制基于Avalon的用户外设

8.1 定制Nios II用户指令

Nios II定制指令综述

具有定制指令的NiosII硬件结构

NiosII处理器用户指令硬件模块框图

8.1 定制Nios II用户指令

Nios II定制指令综述

组合逻辑指令结构框图

定制指令设计示例

NiosIISOPC开发

Nios II/SOPC 的应用领域

01

02

03

04

通信

Nios II/SOPC在通信领域的 应用包括基带处理、调制解调

、协议栈处理等。

工业控制

Nios II/SOPC在工业控制领 域的应用包括运动控制、过程

控制、机器人控制等。

数字信号处理

Nios II/SOPC在数字信号处 理领域的应用包括音频处理、 图像处理、雷达信号处理等。

仿真测试

02

03

调试与优化

使用仿真工具对编译后的文件进 行仿真测试,验证设计的正确性 和可靠性。

在仿真测试过程中,对发现的问 题进行调试和优化,提高设计的 可靠性和性能。

在系统编程与调试

01

02

03

在系统编程

将编译后的文件下载到 Nios II处理器中,实现系 统的实际运行。

在系统调试

在系统运行过程中,使用 调试工具进行实时调试, 解决可能出现的错误和问 题。

Nios II 是一款基于 Altera FPGA 的可定制处理器,具有 高速、低功耗、可编程等优点 ,适用于数字信号处理应用。

数字信号处理算法包括滤波器 设计、频谱分析、信号识别等 ,基于 Nios II 的数字信号处 理系统可以实现这些算法的硬 件加速。

基于 Nios II 的数字信号处理 系统可以应用于音频处理、图 像识别、雷达信号处理等领域 。

应用领域

广泛应用于数字信号处理、通信、控制、图像处理等领域。

Nios II IDE 集成开发环境

概述

Nios II IDE是Altera公司 为Nios II处理器提供的集 成开发环境,支ห้องสมุดไป่ตู้C/C和 汇编语言开发。

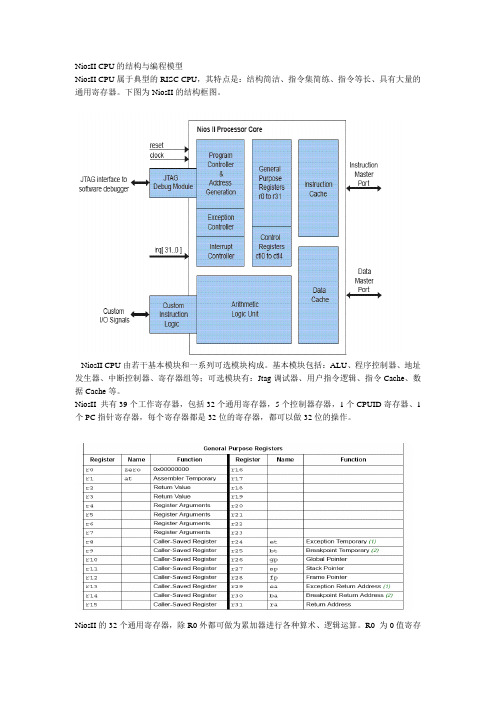

NiosII CPU的结构与编程模型

NiosII CPU的结构与编程模型NiosII CPU属于典型的RISC CPU,其特点是:结构简洁、指令集简练、指令等长、具有大量的通用寄存器。

下图为NiosII的结构框图。

NiosII CPU由若干基本模块和一系列可选模块构成。

基本模块包括:ALU、程序控制器、地址发生器、中断控制器、寄存器组等;可选模块有:Jtag调试器、用户指令逻辑、指令Cache、数据Cache等。

NiosII 共有39个工作寄存器,包括32个通用寄存器,5个控制器存器,1个CPUID寄存器、1个PC指针寄存器,每个寄存器都是32位的寄存器,都可以做32位的操作。

NiosII的32个通用寄存器,除R0外都可做为累加器进行各种算术、逻辑运算。

R0 为0值寄存器,对其进行读操作返回值是0,写操作对其没有影响,这一寄存器在指令集中有特殊的应用。

R24是中断处理程序专用寄存器,它是给中断处理程序专用的,虽然在用户程序中许访问,但不要用来保存数据,因为其中数据有可能被中断处理程序覆盖掉。

同样,R25是调试代理专用寄存器,也不要在用户程序中使用。

R29是PC指针的中断堆栈寄存器,当有中断发生时,这一寄存器用来保留一个返回地址,以便从中断处理程序返回到被中断的程序。

R30是PC指针的断点堆栈寄存器,用于系统调试。

当程序运行过程中遇到断点,这一寄存器中保留一个返回地址,以便从调试代理程序返回。

R31是PC指针的调用堆栈,用于子程序调用。

执行子程序调用指令时,这一寄存器中保留返回地址,以便从子程序返回。

R26、R27、R28在C开发系统中付予了一些特殊的应用,其中R27被作堆栈指针。

NiosII 有5个控制寄存器和一个CPUID寄存器。

Ctl0是程序状态字,目前只有BIT0、BIT1两位是有效的,高30位保留。

BIT0是全局中断控制位,用于中断的全局管理,1为允许,0为禁止。

BIT1是工作模式控制位。

当这一位为1时,系统工作于用户模式,当其为0时,系统工作于管理模式。

NIOSII设计 (DE2实验板)

※※※※※中断※※※※※百度百科上对“中断”的定义:在计算机执行期间,系统内发生任何非寻常的或非预期的急需处理事件,使得CPU暂时中断当前正在执行的程序而转去执行相应的时间处理程序。

待处理完毕后又返回原来被中断处继续执行或调度新的进程执行的过程。

翻译成白话:有客人要来你家做客,你正在洗菜做饭,你怎么知道客人已经到了呢?有两种办法,一是让客人到了之后按门铃,另一种是你不断地去门口瞧瞧人有没来到。

对应到nios系统中,CPU即“你”,硬件外设即“客人”,硬件有数据更新(“客人”到了),第一种方式称为“硬件中断”(按门铃),第二种方式“轮询”(你在厨房和大门口之间疲于奔命)。

只是作一个比喻而已,没人会傻到痴痴地坐门口等人,但是硬件系统不分傻与不傻,“轮询”也是一种可行的方式,效率低一些罢了。

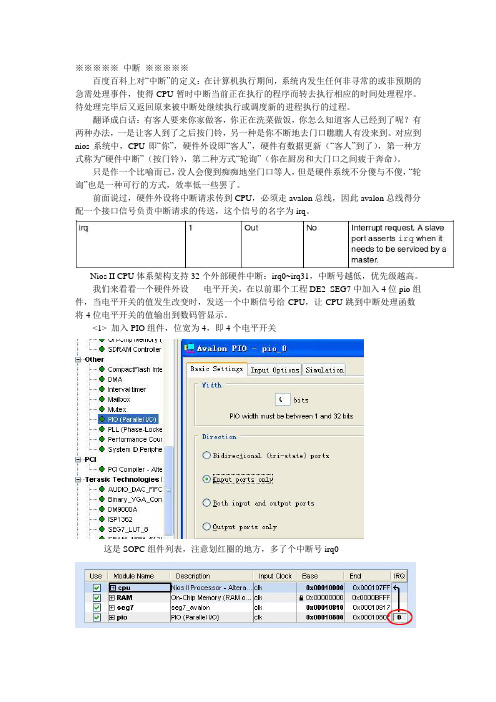

前面说过,硬件外设将中断请求传到CPU,必须走avalon总线,因此avalon总线得分配一个接口信号负责中断请求的传送,这个信号的名字为irq。

Nios II CPU体系架构支持32个外部硬件中断:irq0~irq31,中断号越低,优先级越高。

我们来看看一个硬件外设-- 电平开关,在以前那个工程DE2_SEG7中加入4位pio组件,当电平开关的值发生改变时,发送一个中断信号给CPU,让CPU跳到中断处理函数--将4位电平开关的值输出到数码管显示。

<1> 加入PIO组件,位宽为4,即4个电平开关这是SOPC组件列表,注意划红圈的地方,多了个中断号irq0<3> Generate "Nios2_system",在Quartus II里分配电平开关引脚SW[0]~SW[3],编译。

接着打开工程目录下的pio.vhd,可以看到pio控制器确实定义有avalon中断信号irq。

<4> 下面打开Nios II IDE,写软件C语言在哪里?2008-03-13 16:55按照Altera的文档,软硬件之间的过渡部分应该是这个样子:上次没把"C语言标准库"算进去,是想另开一篇文章来说,而且上次写那几行程序确实没用到C标准库里的函数,altera_avalon_seg7_×××是我们自己定义的,不算数。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

FLASH

PAGE 04 EXT_DATA

B

SCHEMATIC INDEX:

00 01 02 03 04 05 06 07 08 09 NOTES CONNECTORS,UART,LED & OTHERS CYCLONE CLOCK,PLL & RESET CYCLONE CONFIG CYCLONE IO CYCLONE POWER SYSTEM POWER SDRAM SRAM FLASH

DB9

MAX3232 PAGE 02 LEDs SWITCH EXT_IO

LOGO

说明:

1. 采用四层板设计,SDRAM的信号处理要注意等长原则,FPGA的管脚定义可以适当调整,但是SDCLK的位置不能动; 2. 蓝色边框的单元为接插件,注意与周围器件的间距;右侧为扩展区域,不能有高过8mm的器件;

ECL1+

B

CL1

CL2

CL3

B

1uF 2

2.2uF 0.1uF 0.01uF

1.5V FBL2 VCCA_PLL2 1 ECL2+ 1uF 2

CL4

CL5

CL6

2.2uF 0.1uF 0.01uF

【L】

A A

这些元件靠近芯片相应的管脚,靠近摆放,尽量没有过孔

Title Size A4 Date:

5 4 3 2

EXT_ADDR

C

EXT_DATA 3.3V EGPIO[15:0] EGPIO[15:0] 3.3V

【D】

C

RD1 4.7K

RD2 4.7K

RD3 4.7K

RD4 4.7K

3.3V CU1

B

0.1uF 1

U100 C1+ VCC C1T1I R1O T2I R2O C2+ V+ T1O R1I T2O R2I V16 2 14 13 7 8 6 15

C

U1B ALT_CF_nCONFD ALT_CF_nSTATUS ALT_CF_nCONF ALT_CF_nCE UC1 3 7 8 4

C

T1

RC5 10K JC1 1 3 5 7 9 TCK TDO TMS NC2 TDI VCC NC1 NC3 GND1 GND2

3.3V

145 146 26 33 25 36 24 37

5

4

3

2

1

REV NOTES,UNLESS OTHERWISE SPECIFIED:

1. RESISTANCE VALUES IN OHMS. 2. CAPACTITANCE VALUES IN FARADS. 3. ALL 0.1uF and 0.01uF CAPACITORS ARE DECOUPLING CAPS UNLESS OTHERWISE NOTED. THEY ARE SHOWN ON THE PAGE WITH THE ICs AND SHOULD BE PLACED NEAR.

02 e CYCLONE l CLOCK,PLL&RESET R d C y c o n e M a i n B o

Document Number 2004001 Wednesday, November 03, 2004 Sheet

1

a r d

Rev A

3

of

10

5

4

3

2

1

3.3V

D D

3.3V RC1 10K RC2 10K RC3 10K RC4 10K U1E 32 TCK TDO TMS TDI MSEL1 MSEL0 35 34 MSEL1 MSEL0 147 149 148 155 RC7 10K

GNDA_PLL1 GNDD_PLL1 EP1C12Q240C8

GNDA_PLL2 GNDD_PLL0

151 150

3.3V X1 CX1

C

3.3V X2 3 1 RX2 33 0.1uF MCLKIN CX2 4 2 VCC OUT GND NC NO POP 3 1 RX3 CLK_USER NO POP

布局参考:(具体尺寸根据实际情况而定)

C

RESET ALTERA_AS SDRAM PAGE 03 EXT_ADDR ALTERA_JTAG POWER CLOCK LT1085-3.3V ,LT1585-1.5V

SRAM

EP1C1/4 EP1C6/EP1C12 PQ240

B

SRAM

CYCLONE FPGA

EP1C12Q240C8

ALTERA_JTAG

EP1C12Q240C8 RC9 0 RC10 0

3.3V

CC1 0.1uF

Configuration device is configured use AS mode. The JTAG download mode is also available.

JE1

D

EA0 EA6 EA4 EA2 EA15 EA13 EA17 EA19

pack1: EA15-FLASH_RY_BY#

FLASH_RY_BY# FLASH_RW#

EA8 EA10 FLASH_CE# FLASH_BYTE#

1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39

JTAG下载座靠近FPGA

JC3

JC2 1 3 5 7 9 DCLK GND1 CONF_DONE VCC nCONFIG nCE DATAOUT nCS ASDI GND2 ALTERA_AS

B

2 4 6 8 10

3.3V MSEL0 INIT_DONE 1 3 ALT_CF_nCONFD 5 ALT_CF_nSTATUS7 ALT_CF_nCONF 9 ALT_CF_nCE 11 13 2 4 6 8 10 12 14 CONFIG IO MSEL1 FPGA_CF_DATA0 ALT_CF_DCLK ALT_CF_nCS ALT_CF_ASD

CONF_DONE nSTATUS nCONFIG nCE nCEO DATA0 DCLK nCSO(IO) ASDO(IO)

3.3V 4 6 TRST 8 2 10

RC6 10K

VCC1 VCC2 VCC3 GND EPCS4

DATA DCLK nCS ASDI

2 6 1 5

FPGA_CF_DATA0 ALT_CF_DCLK ALT_CF_nCS ALT_CF_ASD RC8 10K

JE3 2 4 6 8 10 12 14 16 18 20 22 24 26 28 30 EXT_IO

D

ECLKIN_P ECLKOUT_P

ECLKIN_N ECLKOUT_N EGPIO1 EGPIO3 EGPIO5 EGPIO7 EGPIO9 EGPIO11 EGPIO13 EGPIO15

ECLKIN_N ECLKOUT_N

TX RX TX_EXT RX_EXT

PB[1:0]

PB1 LEDG[3:0] 10 PU1 LEDG1 RD7 LEDG2 RD8 LEDG3 510 510 LEDG[3:0] LEDG0 RD6 510 RD5 510 DD1 2 DD2 2 DD3 2 DD4 2 GREEN 1 GREEN 1 GREEN 1 GREEN 1

RR5 100 ECR1 + 10uF 2 1

47K

RR6

0

阻容复位,作为候选的复位电路 RR4-47K; RR5-100; RR6-0 ECR1-10uF

C

4 2

VCC OUT GND NC 50.000MHz

0.1uF

【X】

CYCLONE PLLs

1.5V FBL1 VCCA_PLL1 1

【R】

C2- GND SP3232ECA DU1 2 DU2 2

CU4

0.1uF 3 2 1

GREEN UART_TX 1 GREEN UART_RX 1

J100 UART_EXT

A

【U】

A

01 CONNETORS

Title Size A4 Date:

R e d

C y c l o n e

M a i n B o a r d

D

放在显著位置

SW2 RESET

RR1 NO POP RR3 NO POP 1 2 3 4 3.3V 2 RR4 DR1 1 3.3V UR1 /MR VCC GND PFI NO POP RST /RST NC /PFO 8 7 6 5

RR2 NO POP SYS_RST SYS_RST#

D

30 31

Rev A Sheet

1

Document Number 2004001 Wednesday, November 03, 2004 2 of 10

5

4

3

2

5

4

3

2

1

3.3V U1C ECLKIN_P ECLKIN_N ECLKOUT_P ECLKOUT_N ECLKIN_P ECLKIN_N ECLKOUT_P ECLKOUT_N VCCA_PLL1 28 29 38 39 27 CLK0(LVDSCLK1p) CLK1(LVDSCLK1n) PLL1_OUTp(IO) PLL1_OUTn(IO) VCCA_PLL1 CLK2(LVDSCLK2p) CLK3(LVDSCLK2n) PLL2_OUTp(IO) PLL2_OUTn(IO) VCCA_PLL2 153 152 144 143 154 VCCA_PLL2 MCLKIN CLK_USER RX1 33 SDCLK SDCLK

CU2

0.1uF 1 6 2 7 3 8 4 9 5