基于FPGA的数字视频监控系统设计

基于FPGA的视频监控

基于FPGA的视频监控在工业系统中,很多仪器和设备都需要实时监控其运行状态,由于工业环境很多情况下并不适合人工长期现场值守,因此往往选择使用视频监控设备来将工业环境中的情况实时采集到监控室,由专人统一来监视,保证对工业环境中仪器设备运行情况的实时掌握。

目前,已有视频监控系统采用的方案主要分为4种,分别为采用ARM或X86处理器的方案、DSP数字信号处理器的方案、专用视频监控集成芯片方案和使用FPGA方案。

基于ARM或X86处理器架构的视频监控方案应用相对成熟,开发简单,使用灵活,尤其是使用ARM处理器的方案,系统结构简单,成本低廉。

但是,无论是基于ARM或X86的方案,都存在着性能瓶颈以及可升级性较差的问题。

无法实现高速的或多通道的数据采集和同步显示。

DSP数字信号处理器以其卓越的数据运算性能,在图像数据处理方面有很高的效率和灵活性。

适用于需要对图像数据进行处理变换的应用中,但是,DSP本身数据带宽有限,当需要处理的数据总量达到一定的程度后,DSP由于其串行运算的本质,其性能也会出现瓶颈。

另外,一般DSP芯片的片上外设大多固定,扩展性有限,即可升级性不强,而且,能够实现视频图像采集和处理的DSP芯片,成本都相对较高。

专用视频监控集成芯片专为视频监控应用而开发,在性能和成本上有非常大的优势,适合大规模的应用。

但是,由于是专用集成芯片,其功能单一,性能固定,因此扩展性和升级性较差,该方案主要适用于功能明确且成本敏感的应用。

采用FPGA的方案,拥有很高的数据带宽和扩展性。

另外,由于FPGA拥有强大的并行数据处理能力,在数据采集、处理、存储以及传输上都有非常高的实时性,而且,由于FPGA属于通用可编程逻辑器件,能够在不改变本身芯片硬件结构的情况下大幅度修改设计功能,因此具有非常高的扩展性和可升级特性。

从理论上,只要FPGA资源足够多,单颗FPGA芯片就能实现多通道的视频采集、存储和显示。

只是,相对于采用ARM的方案,FPGA方案成本更高一些。

基于FPGA的视频处理系统设计与实现

基于FPGA的视频处理系统设计与实现随着数字化技术与高清视频的普及,基于FPGA的视频处理系统的应用也越来越广泛。

它们可以满足人们对于视频质量、速度和响应性能的要求。

FPGA作为一种高度可编程的器件,可根据应用需求任意重构电路结构,使得视频处理系统具有高度的扩展性、灵活性和定制性。

本文将从设计目标、系统结构、视频数据流传输、数字信号处理、硬件开发与软件开发等多个方面来介绍基于FPGA的视频处理系统的设计与实现。

一、设计目标在设计基于FPGA的视频处理系统时,我们需要考虑以下几个方面:1.视频质量:在视频的采集、传输和显示过程中需要确保视频的清晰、流畅和无噪音。

2.速度:视频处理系统需要具备高速的处理能力,可以迅速对视频进行处理,以达到实时性和响应性能。

3.低功耗:由于FPGA系统是基于硬件实现的,所以需要考虑低功耗来满足电源限制和延长电池寿命。

4.设计可重用:这就需要设计出可重用的平台,方便进行软件开发和硬件设计。

二、系统结构基于FPGA的视频处理系统的系统结构如图1所示。

它主要由三个部分组成:视频输入模块、视频处理模块和视频输出模块。

1.视频输入模块视频输入模块主要负责从相机或视频文件中采集视频数据,并将其转换成数字信号传输给FPGA。

该模块包括视频采集和视频解码两个部分。

2.视频处理模块视频处理模块主要是对采集到的视频数据进行处理,包括降噪、滤波、缩放、边缘检测、图像增强等操作。

它往往是FPGA设计的重点。

3.视频输出模块视频输出模块主要把处理好的视频数据输出到显示器、硬盘或网络等外设上,并在此过程中再次进行编码技术,使传输数据量减小,加快传输速度。

该模块还需要实现垂直同步、交错、逆交错等技术来保证视频输出的正确性和质量。

图1:基于FPGA的视频处理系统结构图三、视频数据流传输视频数据流传输是视频处理系统中非常重要的一环,它利用高带宽的总线来传输大量数据。

视频数据流传输主要有以下三种方式:1.像素传输像素传输是最常用的一种方式,它将每个像素的RGB值保存在一个字节中,并采用三根数据线分别传输每个像素的R、G、B值。

视频监控系统中基于FPGA方案的视频处理

视频监控系统中基于FPGA方案的视频处理视频监控系统是火车站、机场、银行、娱乐场所、购物中心甚至家庭保安的重要组件。

随着安全风险增加,对视觉监视和记录事件的需求以多种使用模式激增。

因此,新架构必须为横跨一整套日渐繁杂的视频监控系统要求的成本效益方案提供可扩展性。

上市时间的压力、新CODEC标准、日益广泛的要求(包括先进的目标探测、运动探测、目标跟踪和目标跟踪特性),这些不过是新型视频监控架构所面临挑战中的几项。

伴随挑战而来的是对可扩展为不同性能范围的实现的需求。

对于从低端到高端以及从单机到PC扩展卡的任何视频监控系统,XilinxFPGA都是理想的解决方案。

视频监控和DVR系统数字监控系统中的数字视频录像机(DVR)正在迅速采用先进的数字视频压缩。

大多数DVR制造商从MPEG4向H.264高清晰度(HD)CODEC转移,对更高分辨率和压缩速度的需求也随之增加。

专用芯片(ASSP)对大批量应用很有用,但缺少灵活性,开发成本高,而且开发时间较长;大多数高级数字媒体处理器则只能执行H.264HD解码(而H.264HD编码比解码还要复杂得多)。

满足H.264HD性能要求的最佳解决方案是使用一个FPGA加上一个外部DSP或数字媒体处理器。

使用低成本的XilinxFPGA,可以更进一步提供运动探测、视频缩放、颜色空间转换、硬盘接口和DDR2存储器接口,还可以将两个27-MHzITU-RBT656数据流时分多路传输到一个54MHz 数据流中,同时为DSP处理器提供视频加速。

要将两个ITU-RBT656数据流多路传输到一个ITU-RBT656数据流中,仅需要一个通道视频端口来独立地传输完整的二通道视频数据。

要为只有一个ITU-RBT656视频输入端口的数字媒体处理器提供接口,这种实现方法非常有用。

图1所示就是这样一种建议架构的框图。

对于使用德州仪器公司DaVinci处理器(仅有一个ITU-RBT656视频输入端口)的DVR设计,需要一种更有效的实现方法将两个或更多ITU-RBT656数据流时分多路传输到一个VLYNQ数据流中,然后才能将其输送到DaVinci处理器。

基于FPGA技术的视频信息采集系统的设计与实现的开题报告

基于FPGA技术的视频信息采集系统的设计与实现的开题报告一、选题背景随着科技的不断发展,数字信号的处理已经成为当今社会的一个重要方向。

视频信息是其中不可或缺的一部分,它被广泛应用于监控、视频会议、互联网直播等领域。

而基于FPGA(Field Programmable Gate Array)技术的视频信息采集系统是一个非常有前景和实用价值的研究方向。

FPGA具有硬件可重构和并行处理等优点,能够高效处理大规模的数据,因此被广泛应用于视频采集和处理领域。

二、选题目的本项目旨在设计和实现一个基于FPGA技术的视频信息采集系统,能够高效地采集、传输和处理视频信号,并提供简单易用的界面。

具体实现目标如下:1. 设计一个视频信号采集板卡,能够快速采集高清视频信号,并通过高速接口传输到FPGA。

2. 设计一个视频信号处理模块,能够对采集到的视频信号进行色彩空间转换、图像增强等操作。

3. 利用高速存储器实现视频数据的暂存和传输,并设计一套简单易用的界面,在界面上实现视频的播放和保存等操作。

三、研究内容本项目主要涉及以下内容:1. FPGA基础知识:了解FPGA的基本原理、编程语言和开发软件。

2. 视频信号采集:设计和实现一个视频信号采集板卡,能够快速采集高清视频信号,并通过高速接口传输到FPGA。

3. 视频信号处理:设计一个视频信号处理模块,能够对采集到的视频信号进行色彩空间转换、图像增强等操作。

4. 高速存储器设计:利用高速存储器实现视频数据的暂存和传输。

5. 界面设计:设计一套简单易用的界面,在界面上实现视频的播放和保存等操作。

四、研究方法本项目采用以下研究方法:1. 文献查阅法:通过查阅相关的专业书籍、学术论文和网络资料,掌握FPGA技术的基本原理和应用。

2. 实验研究法:通过设计和实现一个视频信息采集系统,验证所学理论知识的正确性和实用性。

3. 数据分析法:通过对实验结果的数据分析,总结经验和发现问题,进一步完善和优化系统的性能。

基于FPGA+DSP的高清视频监控系统研究

基于FPGA+DSP的高清视频监控系统探究摘要:随着科技的不息进步和进步,高清视频监控系统在安防领域得到了广泛应用。

本文将详尽探究基于FPGA+DSP的高清视频监控系统,并从硬件设计、软件算法以及系统性能方面进行分析和探讨。

通过试验验证,本文所提出的基于FPGA+DSP的高清视频监控系统在图像质量和处理性能上具有巨大优势,能够有效应对日益复杂的安防需求。

关键词:高清视频;监控系统;FPGA;DSP第一章引言1.1 探究背景随着社会的不息进步和人们对安全的日益重视,高清视频监控系统在城市安防和企事业单位的安全管理中起到了至关重要的作用。

高清视频监控系统通过实时采集和传输高清视频图像,能够对潜在的安全隐患进行准时发现和处理,为各行业提供有效的安全保障。

1.2 探究意义目前市场上的高清视频监控系统主要基于开发板或者成熟的硬件平台,但是这些系统存在着处理速度慢、图像质量差、占用存储空间大等问题。

因此,本文旨在探究并设计一种基于FPGA+DSP的高清视频监控系统,通过硬件和软件的协作,提高系统的处理速度和图像质量,以满足复杂的安防需求。

第二章系统设计方法2.1 硬件设计本系统基于FPGA+DSP实现,接受了高性能的FPGA芯片和DSP 芯片。

FPGA用于图像数据的采集、处理和传输,DSP用于复杂算法的运行和图像质量的优化。

通过硬件设计,实现对高清视频的高速处理和传输,提高系统的实时性和稳定性。

2.2 软件算法本系统接受了图像增强算法、目标检测算法和运动跟踪算法等。

图像增强算法通过增加对比度和锐化处理,提升图像的明晰度和细节;目标检测算法通过特征提取和分类器的运用,实现对目标物体的准确检测;运动跟踪算法通过连续帧的比对和匹配,实现对目标物体的精确跟踪。

第三章系统性能评估为了评估所设计的基于FPGA+DSP的高清视频监控系统的性能,本文进行了多组试验,并从图像质量、处理速度和系统资源占用等方面进行了分析和评估。

基于FPGA的低成本网络视频监控系统设计

2 2 视频 采集 模块 .

OV9 5 6 0美 国豪 杰公 司生产 的一 款 彩色 分辨 率可 达 S XGA 级 别 ( 0万 像 素 ) 1 3 CMOS图 像传 感 器 ,它 的片 内集 成 了色 彩 信号 处理 器 。 这 种 CM0S图 像传 感 器 与色 彩信 号 处 理 器 集 成 到一 个 芯 片 内 部 的技 术

・

数 字技 术 ・

基于 F G P A的低成本网络视频监控 系统设计

徐 均 段 永 霞

( 中国人 民解放军 蚌埠 坦克 学院实 验中心 安徽 蚌埠

23 5 ) 3 0 0

【 摘 要 】 文介 绍 了一 种基 于 FP 本 GA和 视 频采 集 芯片 OV9 5 6 O嵌入 式 视频 采 集 与处理 系统 的设 计 过程 。在 系统 中 ,关 键 的 DCT运 算 算法 选取 了适合 实 际 需要 的 当前 业 界 内运 算速 度 最快 的 算 法 ,而 FP GA 上 VHDL程 序 功能 的 模 块化 和 可 复用 性 可 以提 高设 计 效率 , 同时有效的控制了成本。 【 关键词] GA 监控 视频处理 FP 【 中图分类号] TN9 ¨

降 低 了功 耗 ,而 且 减 小 了体 积 。

理 的 数据 量 较 低 层 算 法 少 ,但 算 法 的 控制 结 构 复 杂 ,适 于 用 运 算 速度 高 、寻 址 方式

灵 活 、 通 信 机 制 强 大 的 专 用 视 频 芯 片 来 实 现 。 FPGA 芯 片 与 专 用 视 频 芯 片 相 比 , 由 于 其 结 构 上 的 优 势 , 更 适 合 完 成 并 行 处

0 95 基于 C V 60 MOS 工艺 ,使 用有 源像

素传 感器 ,与传统 的 CCD传感 器相 比有 很

基于FPGA的智能安防监控系统实现

基于FPGA的智能安防监控系统实现随着科技的不断进步和社会的不断发展,人们对于安全和保护的需求越来越强烈。

而智能安防监控系统正是应对这种需求而生。

基于FPGA的智能安防监控系统,是一种集图像处理、智能分析、视频传输于一体的先进安防监控技术。

一、FPGA的特点及在智能安防监控中的应用FPGA,即现场可编程门阵列,是一种可编程的半导体器件。

它的灵活性和可重构性,使得它成为流行的数字电路设计方案之一。

FPGA由于其可重构性和高速性能,在图像处理和视频处理方面得到了广泛的应用,因此,在智能安防监控中,使用FPGA进行图像和视频信号的处理是非常重要的一步。

在智能安防监控中,FPGA可以对摄像头捕捉到的图像或视频信号进行数字信号处理。

对于图像处理,FPGA可以实现高清晰度的图像捕捉,图像增强、减噪和边缘检测等功能。

对于视频处理,FPGA可以实现视频的编解码、字幕添加、分段处理等功能。

以及对音频进行处理,如降噪降燥、回声消除等。

由于FPGA的高速性能,可以实时的处理图像和视频信号,从而大大提高了智能安防监控的效率。

二、智能分析算法及在智能安防监控的应用智能分析算法是智能安防监控的核心。

它能够将图像或视频信号进行分类、识别、计数和跟踪等,并且能够进行异常检测和预警。

智能分析算法的应用,将为智能安防监控系统的应用带来更大的便利。

目标检测和跟踪是智能监控中最基本的算法之一。

在智能安防监控中,目标检测和跟踪可以应用于人、车、物体等的区分和识别。

该算法利用人工智能技术实现对象的定位和跟踪,并且可以对目标进行实时的自动拍摄和追踪。

同时,该算法也可以检测目标是否有异常行为,如长时间停留、闯入等,从而快速响应和压制。

另外,智能识别技术,如人脸识别、车牌识别和物体识别等,在智能安防监控中也得到了广泛的应用。

利用这些智能识别技术,可以快速获取目标的信息,同时可以实现实时的数据统计和监控,更加高效地配合人工智能技术,减少人工参与和减轻监控压力。

基于FPGA的数字视频监控系统设计

【 src 】 D s n o i o m n ̄r g ss m b sd o F G s it d cd n dti .r i ss m hs a vn gs f et Abtat ei fvd o i i yt ae n P A i n oue i e l r s yt a d at e o xr g e n e r as h e a a

的另一 端 参 与 图像 传 输 过程 2 和 过 程 1 的 图像位 宽 ) )

为 8bt传 输 时 钟 为 l . MHz i. 25 。

2 )从 过 程 1 的 FF 中 输 出 的 图 像 数 据 进 入 图 像 ) IO

写 人 缓 存 模 块 W R b f r ,将 4 b t 据 拼 接 成 1个 _ uf 中 e ye数 宽 为 3 i 的数 据 , 经 过 同步 F F 2bt 再 IO送 人 S RA 中 。 D M

速发展 , 利用数字图像处理技术进行动态监测 和现场监控 都已成为现实 , 视频监控技术 已全面进入数字时代。

视 频 监 控 产 品要 求 采 用 具 备 更 高性 能 和灵 活 性 的器 件 来构 建 ,过 去单 纯 采 用 D P处 理 器 或 现成 芯 片 ( S P S A S)

的方法 已难 以满 足 系统 需 求 . F GA特有 的灵 活 性 和高 而 P

LI S n ,F Ya g U o g U n ,GUO P i y a e- u n

(c olo fr ain E gn eig e ig U iesy o eh ooy ad B s s,B rn 0 0 8 hn ) Sho f I om t n i r ,B in nvri f Tc nlg n ui s e i 10 4 ,C i n o e n j t e n g a

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

文章编号:1002—8692(2010)03—_0092—03基于FPGA的数字视频监控系统设计··实用设计·刘松,付扬,郭培源(北京工商大学信息工程学院,北京100048)【摘要】详细介绍了基于FPGA的视频监控系统设计。

该系统具有高精度、高速和高效等优点,设计灵活。

用VerilogHDL语言来实现各个模块的编写,使硬件设计更简单。

该系统通过0V9650摄像头获取图像数据.经过FPGA采集、缓存、数据变换,最终在VGA显示中显示。

【关键词】视频监控;现场可编程门阵列;VerilogHDL;视频采集【中图分类号】’rP277【文献标识码】ADesignofDi萄talVideoMonitoringSystemBasedonFPGALIUSong,FUYang,GUOPei-yuan(SchoolofInformationEngineering,BeijingUniversityofTechnologyandBusiness,Beo'inglo004s,China)【Abstract】DesignofvideomonitoringsystembasedFPGAisintroducedindetails.Thissystemhasadvantagesofextraprecision,highspeedandhishefficiency.ItcanmakethedesignofhardwaremoreconvenientviausingVerilogHDLlanguage.Inthisdesign,theimagedatacapturedby0V9650cameraiscollected,storedintothebufferandtransformedbyFPGA,andfinallydisplayedVGAmachine.【Keywords】videomonitoring;FPGA;VerilogHDL;videocollection1引言近年来,随着数字图像处理技术和数字电路技术的飞速发展.利用数字图像处理技术进行动态监测和现场监控都已成为现实,视频监控技术已全面进入数字时代。

视频监控产品要求采用具备更高性能和灵活性的器件来构建,过去单纯采用DSP处理器或现成芯片(ASSP)的方法已难以满足系统需求。

而FPGA特有的灵活性和高性能使其成为许多监控产品的理想解决方案Ill。

笔者详细地介绍了在FPGA上实现视频监控系统的设计思路。

用VerilogHDL语言来实现各个模块的编写以及各个模块之间的信号关系。

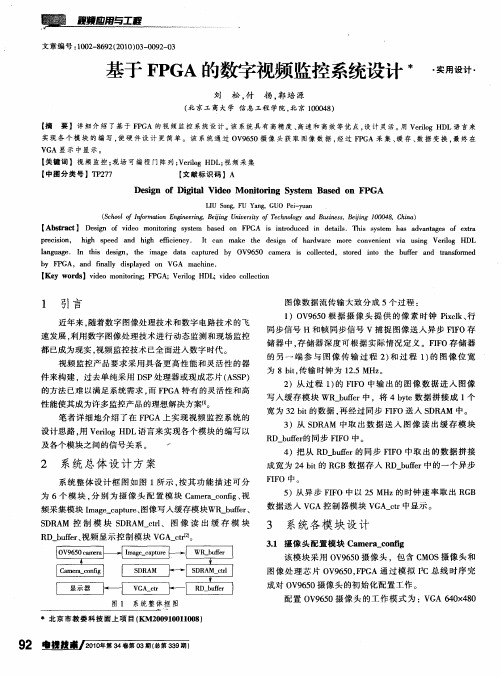

2系统总体设计方案系统整体设计框图如图1所示.按其功能描述可分为6个模块。

分别为摄像头配置模块Camera_config、视频采集模块Image_capture、图像写入缓存模块WR_buffer、SDRAM控制模块SDRAM_ctrl、图像读出缓存模块RD_buffer、视频显示控制模块VGJLcd习。

Ov9650cameraImage_capture卜lWR—buffer至三固[巫}匝亟亟显示器卜l—一VGA_ctr卜I—一IRD_buffer图1系统整体框图·北京市教委科技面上项目IKM200910011008)92垒塑熊堂∥而丽磊i忑i丽丽丽i丽图像数据流传输大致分成5个过程:1)0V9650根据摄像头提供的像素时钟Pixclk、行同步信号H和帧同步信号V捕捉图像送入异步FIFO存储器中,存储器深度可根据实际情况定义。

FIFO存储器的另一端参与图像传输过程2)和过程1)的图像位宽为8bit,传输时钟为12.5MHz。

2)从过程1)的FIFO中输出的图像数据进入图像写入缓存模块WR_buffer中,将4byte数据拼接成1个宽为32bit的数据,再经过同步FIFO送入SDRAM中。

3)从SDRAM中取出数据送人图像读出缓存模块RD-_buffer的同步FIFO中。

4)把从RD_buffer的同步FIFO中取出的数据拼接成宽为24bit的RGB数据存入RD_buffer中的一个异步FIFO中。

5)从异步FIFO中以25MHz的时钟速率取出RGB数据送入VGA控制器模块VGA_ctr中显示。

3系统各模块设计3.1摄像头配置模块Camera_config该模块采用OV9650摄像头。

包含CMOS摄像头和图像处理芯片OV9650。

FPGA通过模拟12C总线时序完成对OV9650摄像头的初始化配置工作。

配置0V9650摄像头的工作模式为:VGA640x480万方数据格式视频,以RGB数据流输出,RGB格式为RGB4:2:2,数据流输出为GlBG2RG3…,4byte数据为2个像素点,同行相邻的左右2个像素共用BR值,视频速率为15f/s(帧/秒)。

12C控制过程如图2所示。

步骤为:1)判断复位信号Reset是否有效,假如有效,置位SCL(串行时钟)、SDA(串行数据)、END(传输结束);2)复位END,通知传输开始;3)模拟12C启动信号,即在SCL为高电平期间置位SDA;4)开始传输控制数据,SCL低电平时修改SDA的值,并且每传输完1byte释放SDA线;5)模拟12C结束信号,即在SCL为高电平期间复位SDA;6)置位SDA和END,通知传输结束。

图212C控制过程3.2视频数据的采集模块Image_capturemodule经过摄像头产生的数据。

包含摄像头的像素时钟Pixelk(12.5MHz)、行同步信号H、帧同步信号V以及RGB像素数据Pixdata。

接下来需要把图像数据写入SDRAM中,由于OV9650与SDRAM工作在不同的频率下,这就出现了异步时钟处理问题,所以在SDRAM控制器与摄像头的输出端之间添加一个异步FIFO。

异步FIFO主要用来缓冲数据和隔离时钟或相位差异。

FIFO的存储介质是双口端RAM,所以读写操作可以在两端同时进行。

访问FIFO时仅需要读写线和控制线,不需要地址线131。

图3实例化的F1F0首先利用n,GA的RAM资源实例化一块双口RAM。

实例化的f'IFo如图3所示。

数据位为9位,深度为64。

由于数据的写入时钟远远小于数据的读出时钟.不用担心写满的情况,深度可以尽量小。

以节省FPGA资源。

nFo模块主要有以下端口:9位输入data[8..o】和输出q[8..01,数据的低8位存储的是图像数据,最高位判….】!!№耻塑鲍鱼卫啦!一.囵断存储的图像数据是否是图像每一帧的第一行:写时钟wrclk和读时钟信号rdclk;写请求wrreq和读请求rdreq信号;空标志位rdempty以及溢出标志位wdull。

重启后置位rdempty并且复位wrfull。

由于读时钟远远高于写时钟且只要rdempty为O,就发出一个读请求rdreq.不会出现写满的情况.所以每来一个rdclk判断读地址和写地址的位置关系.及时地置位rdempty。

图4写控制过程写控制过程如图4所示。

步骤为:1)判断是否复位,假如是复位wrreq;2)如非复位且行信号H有效,则根据场同步信号V以及行同步信号H来判断是否是图像的第一行;3)假如是图像的第一行则置位wrreq,写入pixdata,并且置位图像第一行的判断信号data罔。

假如不是第一行则复位data/目。

图5读控制过程读控制过程如图5所示。

步骤为:1)判断是否复位。

假如是则复位rdreq;2)假如非复位则判断异步FIFO是否为空且wr_buffer(图像写入缓存模块)是否为可写状态;3)假如非复位且FIFO非空且wrbuffer为可写.则置位wrreq和din_valid(图像缓存模块)写有效。

3.3图像写入缓存模块WR_buffer以上存入异步FIFO的数据流,包括图像数据q[8。

01信号以及图像数据输入有效信号din_valid,接下来要把万方数据E翟型堑型塑堡~每一幅图像数据存储的SDRAM里面供后续显示使用。

由于WR_buffer的数据需要存入SDRAM中且RD_buffer需要从SDRAM中读出数据。

而本文只使用了l块SDRAM.为了防止这两个模块同时访问存储器产生冲突,具体方法是在它们分别存入或取出20个32bit的数据后将访问权利交给对方.在SDRAM中开辟了2个等大的SDRAM(640x480x3/2)区域交替工作,使用乒乓机制交换它们的工作机制,保证了图像画面的显示流畅。

由于SDRAM中存储的是32位的数据,在数据送入SDRAM前.把4byte的pixdata数据拼接成一个32bit宽的数据.送入同步FIFO中.然后再送人SDRAM中。

同步FIFO工作原理和异步FIFO类似,只不过同步FIFO只有1个时钟输入。

设置同步FIFO的空阈值为20,即当FIFO中存有的数据超过20个时复位rdempty,通知SDRAM从兀FO中取数据[41。

i状态机制……·………………。

……-…。

·;WhenSO&&dinvalidsetd0=-q[7。

olnext一>sl}WhenSlgetdl=q【7。

o】next->s2iWllenS2setd2=q[7。

0】next->s3iWhenS3}get;d=q[7..o】+d2<<8+dl<<16+d0<<24;d_valid=lnext一>sO图6WR_buffer控制过程WR_buffer控制过程如图6所示。

步骤为:1)使用4个状态机制SO,S1,S2,S3完成把从视频数据采集模块而来的4byte的pixdata=q[7..o】拼接成1个32bit宽的数据,并送入同步FIFO中;2)判断同步FIFO的rdempty位是否为有效.无效则表示FIFO中已经存有了20个图像数据.并且开始从FIFO中读出这已经存好的20个数据写入SDRAM中;3)判断图像写入缓存SDRAM是否已经写入了一幅图像的数据,并切换图像写入缓存模块和图像读出缓存即交换它们的工作机制。

3.4SDRAM控制模块SDRAMctrlSDRAM的控制逻辑比较复杂.对时序要求也十分严格.这就要求有一个专门的控制器使用户能够很方便地操作SDRAM,在这里使用QuartusII自带的AlteraSDRAM控制模块。

SDRAM控制器设计框图如图7所示【5l。

步骤为:94堕塑鲢煎厂五面函五石晶而再而函丽1)WR_buffer往SDRAM中写入20个32bit的数据;2)从SDRAM中读出20个32bit的数据。

SDRAM控制器图7SDRAM控制器设计框图3.5图像读出缓存模块RDb·ufferRD_buffer控制过程见图8,RD--bu虢r在SDRAM的状态为写完20个32bit数据后再从SDRAM中读取20个32bit的数据送人同步Sync—FIFO_0中,)ASync_FIFO__O中取出1个32bit数据转化成2个24bit数据(之前数据格式为GlBG2RG3…,需转化成G1BRG2BR…)。