帧格式头数据检测_VerilogHDL有限状态机

状态机verilog实际工程应用

状态机verilog实际工程应用

Verilog状态机在实际工程中有着广泛的应用。

状态机是一种能够根据输入信号和当前状态自动转移的逻辑电路,它可以用来描述系统的行为和控制逻辑。

在Verilog中,状态机通常使用有限状态机(FSM)来描述,可以分为Moore状态机和Mealy状态机两种类型。

在实际工程中,Verilog状态机可以应用于各种数字系统的设计,包括但不限于通信系统、控制系统、图形处理器、计算机处理器等。

下面我将从不同的角度来介绍Verilog状态机在实际工程中的应用。

1. 控制逻辑,Verilog状态机可以用于实现控制逻辑,例如在数字系统中根据特定的输入信号来控制输出信号的状态转移,比如在通信系统中根据接收到的数据来执行特定的操作。

2. 时序逻辑,状态机可以用于描述时序逻辑,例如在时序电路中根据时钟信号来执行特定的操作,比如在处理器中根据时钟信号来执行指令的译码和执行。

3. 状态转移,Verilog状态机可以描述系统中不同状态之间的

转移关系,比如在控制系统中描述不同的控制状态和状态之间的转

移条件,从而实现系统的自动控制。

4. 状态检测,状态机可以用于检测系统的状态,例如在通信系

统中可以用状态机来检测数据的传输状态,从而实现数据的接收和

发送控制。

总的来说,Verilog状态机在实际工程中有着广泛的应用,可

以用于描述系统的控制逻辑、时序逻辑、状态转移和状态检测等方面,是数字系统设计中非常重要的一部分。

通过合理的设计和实现,Verilog状态机可以帮助工程师们实现复杂的数字系统功能,提高

系统的可靠性和性能。

有限状态机的verilog例子

有限状态机的verilog例子有限状态机(Finite State Machine, FSM)是数字电路设计中的一种基本构件,它可以用来实现各种复杂的控制逻辑。

在Verilog中,可以用模块(module)来描述一个有限状态机,使用参数(parameters)来定义状态数量和状态转移逻辑。

以下是一个简单的有限状态机的Verilog例子,该FSM有3个状态(S0, S1, S2)和两个输入(clk, rst_n)以及一个输出(next_state, out):```verilogmodule fsm(input wire clk, // 时钟信号input wire rst_n, // 低电平复位信号input wire [1:0] in, // 输入信号,这里位宽为2,可以扩展output reg next_state, // 下一状态输出output reg out // 输出信号);// 状态参数parameter S0 = 2'b00;parameter S1 = 2'b01;parameter S2 = 2'b10;// 状态寄存器reg [1:0] state;// 状态转移逻辑always @(posedge clk or negedge rst_n) beginif (!rst_n) begin// 当处于复位状态时,状态寄存器和输出都初始化为0state <= S0;out <= 1'b0;end else begin// 根据当前状态和输入信号,更新下一状态和输出case (state)S0: beginnext_state <= S1;out <= 1'b1;endS1: beginnext_state <= S2;out <= 1'b0;endS2: beginnext_state <= S0;out <= 1'b1;enddefault: beginnext_state <= S0;out <= 1'b0;endendcaseendendendmodule```在这个例子中:- `clk` 是时钟信号。

基于Verilog HDL的有限状态机的优化设计

第二个进程组合逻辑 a as l y 模块的设计和二段式 的 w 设计相似 , 但是其只进行输入判断和状态转移规律描述 , 而不进行组合逻辑输出 ; 第三个进程也设计成 同步时序 a as l y 模块 ,采用同 w

步时序逻辑寄存 F M 的输出。 S

4三种状态机的逻辑、 电路 、 仿真分析

mp _t a e — ” jgi u uc O 一 / jg u— i s em r i / p / p t v. ” O” p/ t g r m n _ S m o

)

警

图 1 频 采集 图像 0视

图 8内核启动前加载摄 像头驱 动信息

不管你在何时插入 , 以上信息之一都表明 , 出现 摄像

头驱动加载成功 。驱动加载成功后 同时会在 /e dv目录下 产生一个 v eO i o 的设备节点 。 l命令可 以查看 , 图 9 d 用 s 如

所示 。

一

检验所设计 的 F M 的完备性 ,如果所设 计 的 F M不完 S S 备, 则会进入任意状态 , 仿真时很容易发现。

33三段式(h e — l y ) - T re awa s状态机 三段式状态机的设计 即使用三个进程对状态机进行 描述。第一个 a as l y 模块使用 同步时序描述状态之间的 w 转移 ; 第二个 a as l y 模块使用组合逻辑判 断状 态转移条 w 件, 描述状态转移规律 ; 第三个 a as l y 模块采用同步时序 w

成了远程视频数据 的采集 ,为整个 网络智能家居监控 系

统的实现打下了基础 。

摄像头被驱动后 ,需要编写一个对视频流采集 的应

用程序。 系统 中采用的是 m pg s em, 本 je—t a 这是一个视频 r 流服务器 , 里面有对整个视频采集及处理发送 的过程 。 首 先要 将其移植 到 目标板 上 , 也就 是 ¥ C 4 0平 台 , 3 24 并在 目标板上运行此视频流服务器 , 命令如下 :

verilog有限状态机的设计

习

题

8

8.5 设计一个汽车尾灯控制电路。已知汽车左右两侧各 有3个尾灯,要求控制尾灯按如下规则亮灭。 (1)汽车沿直线行驶时,两侧的指示灯全灭; (2)右转弯时,左侧的指示灯全灭,右侧的指示灯按 000,100,010,001,000循环顺序点亮; (3)左转弯时,右侧的指示灯全灭,左侧的指示灯按与 右侧同样的循环顺序点亮; (4)如果在直行时刹车,两侧的指示灯全亮;如果在转 弯时刹车,转弯这一侧的指示灯按上述的循环顺序点 亮,另一侧的指示灯全亮。

always @(state) /*该过程产生输出逻辑*/ begin case(state) S3: z=1'b1; default:z=1'b0; endcase end endmodule

“101”序列检测器(单过程描述)

module fsm4_seq101(clk,clr,x,z); input clk,clr,x; output reg z; reg[1:0] state; parameter S0=2'b00,S1=2'b01,S2=2'b11,S3=2'b10; /*状态编码,采用格雷(Gray)编码方式*/ always @(posedge clk or posedge clr) Begin if(clr) state<=S0; //异步复位,s0为起始状态 else case(state) S0:begin if(x) begin state<=S1; z=1'b0;end else begin state<=S0; z=1'b0;end end S1:begin if(x) begin state<=S1; z=1'b0;end else begin state<=S2; z=1'b0;end end S2:begin if(x) begin state<=S3; z=1'b0;end else begin state<=S0; z=1'b0;end end S3:begin if(x) begin state<=S1; z=1'b1;end else begin state<=S2; z=1'b1;end end default:begin state<=S0; z=1'b0;end /*default语句*/ endcase end endmodule

FPGA Verilog HDL 设计实例系列连载--------有限状态机设计

数字系统有两大类有限状态机(Finite State Machine,FSM):Moore状态机和Mealy 状态机。

Moore状态机其最大特点是输出只由当前状态确定,与输入无关。

Moore状态机的状态图中的每一个状态都包含一个输出信号。

这是一个典型的Moore状态机的状态跳转图,x、y、z是输入,a、b、c是输出。

Mealy状态机它的输出不仅与当前状态有关系,而且与它的输入也有关系,因而在状态图中每条转移边需要包含输入和输出的信息。

状态编码数字逻辑系统状态机设计中常见的编码方式有:二进制码(Binary码)、格雷码(Gray 码)、独热码(One-hot码)以及二一十进制码(BCD码)。

格雷码的特点:相邻的两个码组之间仅有一位不同。

普通二进制码与格雷码之间可以相互转换。

二进制码转换为格雷码:从最右边一位起,一次与左边一位“异或”,作为对应格雷码该位的值,最左边的一位不变(相当于最左边是0)。

格雷码转换为二进制码:从左边第二位起,将每一位与左边一位解码后的值“异或”,作为该解码后的值(最左边的一位依然不变)。

独热码又分为独热1码和独热0码,是一种特殊的二进制编码方式。

当任何一种状态有且仅有一个1时,就是独热1码,相反任何一种状态有且仅有一个0时,就是独热0码。

状态机的描述状态机有三种描述方式:一段式状态机、两段式状态机、三段式状态机。

下面就用一个小例子来看看三种方式是如何实现的。

(各种图片,各种坑爹啊 - -!)一段式状态机当把整个状态机卸载一个always模块中,并且这个模块既包含状态转移,又含有组合逻辑输入/输出时,称为一段式状态机。

不推荐采用这种状态机,因为从代码风格方面来讲,一般都会要求把组合逻辑和时序逻辑分开;从代码维护和升级来说,组合逻辑和书序逻辑混合在一起不利于代码维护和修改,也不利于约束。

1.//一段式状态机来实现:在异步复位信号的控制下,一段式状态机进入IDLE2.//状态,q_sig4被复位,一旦sig1或者sig2有效,状态机进入WAIT状态,如果3.//sig1和sig2同时有效,那么状态机进入DONE状态,4.//如果sig4还有效,那么q_sig4置位,同时状态机进入IDLE状态。

Verilog HDL代码描述对状态机综合的研究

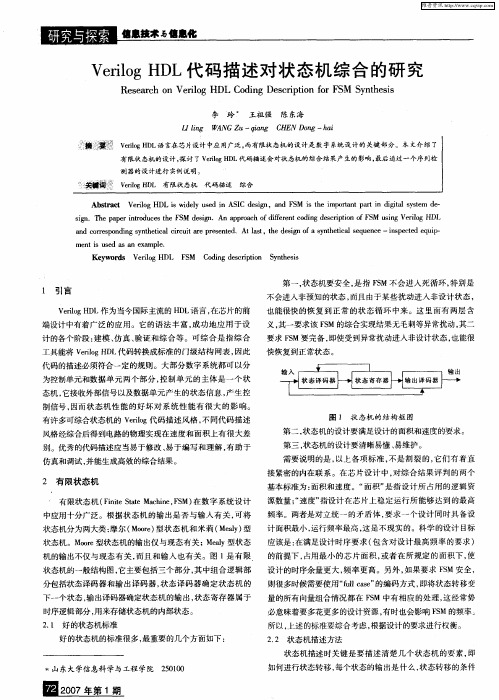

1 引 言 V ro D elg L作为当今 国际主流的 H L语 言, 芭片的前 i H D 在 =

端 设计 中有着 广 泛 的应 用 。它 的 语 法 丰 富 , 功 地 应 用 于设 成

第 一 , 态 机要 安全 , 指 F M 不 会 进 入 死 循 环 , 别 是 状 是 S 特

应该是 : 在满足设计 时序 要求( 含对设计最 高频 率的要求) 包 的前提下 , 占用最小的芯 片面积 , 或者 在所规定 的面积下 , 使

设计 的时序余量更大 , 频率更高。另外 , 如果要求 F M安全 , S

则很多时候 需要使用“u ae 的编码 方式 , fls ” lc 即将状态转 移变 量的所有向量组合情况都在 F M 中有相应 的处理 , S 这经常势

计的各个 阶段 : 建模 、 真 、 仿 验证 和综合等 。可综 合是指综 合 工具能将 V ro D e l H L代码转换成标 准的门级结构 网表 , ig 因此 代码的描述必须符合一定的规则 。大部分数字系统都可以分 为控制单元和数据单元两个 部分 , 控制单 元的主体是 一个状

态机 , 它接收外部信号 以及数据单元 产生的状态信 息, 产生控

分包括状态译码器 和输 出译码器 , 状态译码器 确定状态机 的 下一个状态 , 输出译码器确定状态机 的输 出, 状态 寄存 器属于

时序逻辑部分 , 用来存储状态机 的内部状态 。

计 面积 最 小 , 行频 率 最 高

状态机 。M r 型状态机 的输出仅与现态 有关 ;M a oe e y型状态 l 机的输 出不仅 与现态有关 , 而且和输入 也有关。图 1 是有 限 状态机 的一般结构 图, 它主要包括三个部分 , 中组合 逻辑部 其

Verilog-HDL入门基础之时序状态机的设计精选全文完整版

可编辑修改精选全文完整版时序状态机的设计入门与提高计算机及具有存储器或按照所存储信息执行一系列操作的其他数字系统统称为“时序状态机”,其电路可以通过时序逻辑进行建模。

时序状态机的性能与组合逻辑不同,因为时序状态机的输出不仅仅取决于当前的输入值,而且取决于历史的输入值。

时序状态机被广泛应用于需要指定顺序操作的应用中。

所有的时序状态机都具有如图的通用反馈结构,在这种结构中时序状态机的下一状态是由当前状态和当前输入一起形成的:时序状态机可以按是否受一个公共的时钟控制(钟控)分为同步状态机和异步状态机;根据状态数目是否有限分为有限状态机和无限状态机。

此处只讨论有限状态机。

有限状态机的(FSM)分类有限状态机有米利(Mealy)机和摩尔(Moore)机:米利(Mealy)机:米利(Mealy)机的下一状态和输出都取决于当前状态和当前输入。

摩尔(Moore)机:摩尔(Moore)机的下一状态取决于当前状态和当前输入,而输出仅仅取决于当前状态。

有限状态机常用的描述、开发方法有限状态机可以借助时序图、状态表、状态图以及ASM图进行系统的描述与设计。

•时序图可以用于说明系统中及系统与周围环境的接口中信号的有效输入与状态转移之间的关系。

•状态表与状态转移表以表格的形式表示在当前状态和输入的各种组合下状态机的下一状态和输出•状态转移图(STG)是一种有向图,图中带有标记的节点或顶点与时序状态机的状态一一对应。

当系统处于弧线起点的状态时,用有向边或弧线表示在输入信号的作用下可能发生的状态转移。

米利机STG的顶点用状态进行标记,状态转移图的有向边有下面两种标记方法:(1)用能够导致状态向指定的下一状态转移的输入信号来标记(2)在当前状态下,用输入信号的输出来进行标记摩尔机的状态转移图与米利机相类似,但它的输出是由各状态的顶点来表示的,而不是在弧线上表示•算法状态机(ASM)图是时序状态机功能的一种抽象,是模拟其行为特性的关键工具。

基于Verilog HDL的有限状态机设计与描述

不会 进 入 死 循 环 , 使 由于 某 些 扰 动 进 入 非 法 状 态 , 能 很 快 即 也

的恢 复 到 正 常 的 状 态 循 环 中来 。

能 力 , 系统 在 系 统 级 或 寄 存 器 传 输 级 进 行 描 述 。 对

限状 态 机 已经 成 为关 键 。 传 统 的 有 限 状 态 机 的 描 述 方 式 有 状 态 转 移 图 , 态 转 移 状

图 1 有 限状 态机 结 构

() 限状 态 机 要 安 全 , 定 性 高 。这 就 要求 有 限 状 态 机 1有 稳

列 表 两 种 。随着 E A 技 术 的发 展 , 们 开 始 用 硬 件 描 述 语 言 D 人

sye n ei gHDL d srpin f S r to u e , s bl , ra a it, s e da dae fh s ls ed srb d Fn l , tls dV rl a o ecit s F M fei rd c d t it o o i n a i y e d bl i y p e rao tees e e c e . ial n y t r a i y

维普资讯

第 2 卷 第 4 9 期

VO . 9 12 N O. 4

计 算机 工 程 与设 计

Co mp t rE g n e n n sg u e n i e r g a d De in i

20 年 2 08 月

F b.2 0 e 0 8

文章编号 :0 072 20 ) 40 5 —3 10 —04(0 8 0 —9 80

De in a dd s rp in o n t tt c i eb s d o e i gHDL sg n e c t f i saema h n a e nv r o i o i f e l

使用Verilog进行硬件描述

使用Verilog进行硬件描述硬件描述语言(Hardware Description Language,简称HDL)是专门用于描述数字电路的语言,其中Verilog是一种常用的HDL。

本文将介绍如何使用Verilog进行硬件描述。

一、Verilog简介Verilog是一种硬件描述语言,用于描述和设计数字电路。

它具有丰富的语法和功能,可以灵活地描述各种类型的电路。

Verilog分为Verilog HDL和Verilog-A两种,本文主要介绍Verilog HDL。

二、Verilog的基本语法1. 模块声明Verilog中,通过使用`module`关键字进行模块声明。

模块由输入(Input)、输出(Output)和内部信号(Wire)组成。

例如:```module adder(input a, input b, output sum);// 模块的具体实现endmodule```2. 信号赋值Verilog中,使用`assign`关键字进行信号赋值。

例如:```assign sum = a + b;```3. 运算符Verilog支持各种运算符,包括算术运算符(+、-、*、/)、比较运算符(>、<、==、!=)和逻辑运算符(&&、||、!)。

例如:```assign c = a & b;```4. 时钟信号在Verilog中,时钟信号通常使用`always`关键字进行描述。

例如:```always @(posedge clk)begin// 在时钟上升沿执行的操作end```三、Verilog的应用1. 组合逻辑电路Verilog可以用于描述各种组合逻辑电路,如加法器、多路选择器等。

例如,下面的代码描述了一个4位全加器:```module full_adder(input a, input b, input c_in, output sum, output c_out);assign sum = a ^ b ^ c_in;assign c_out = (a & b) | (b & c_in) | (a & c_in);endmodule```2. 时序逻辑电路Verilog还可以描述时序逻辑电路,如触发器、时钟分频器等。

verilog 状态机写法

verilog 状态机写法Verilog是一种硬件描述语言,常用于设计和开发数字电路和系统。

在Verilog中,状态机是一种常用的建模方法,用于描述系统的状态和状态转移。

Verilog的状态机可以使用不同的写法来实现,通常有两种主要的方法:行为级描述和结构级描述。

行为级描述是一种以状态转移的逻辑和状态转移的条件为基础的写法。

在行为级描述中,我们需要定义状态变量和状态转移条件,然后使用if-else语句来实现状态转移逻辑。

以下是一个简单的例子,使用行为级描述写法实现一个简单的二进制计数器状态机:```verilogmodule binary_counter(input clk,input reset,output reg [3:0] count);reg [3:0] next_count;always @(posedge clk or posedge reset) beginif (reset) begincount <= 4'b0000;end else begincase (count)4'b0000: next_count = 4'b0001;4'b0001: next_count = 4'b0010;4'b0010: next_count = 4'b0011;4'b0011: next_count = 4'b0100;4'b0100: next_count = 4'b0101;4'b0101: next_count = 4'b0110;4'b0110: next_count = 4'b0111;4'b0111: next_count = 4'b1000;4'b1000: next_count = 4'b1001;4'b1001: next_count = 4'b0000;default: next_count = 4'b0000;endcasecount <= next_count;endendendmodule```在上面的例子中,我们定义了一个4位的计数器变量`count`,并在always块中定义了状态转移逻辑。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

题目1:串行通讯中,经常要检测数据包的开始标志,例如:USB 数据包的起

始数据是8‘b00101010设计一个电路,能够检测串行数据流中的特殊数据串,并在数据串有效时,给出相应的指示信号;

(1)RTL Code

/*信号定义与说明

Clk:同步时钟

rstb: 异步复位信号,低电平复位

up_down: 加/减计数方向控制信号,1为加计数

Din:串行数据输入

pat_det: 检测结果输出

*/

`timescale 1ns/1ns

module serialdata(din,clk,rstb,pat_det);

input clk,rstb;

input din;

output pat_det;

parameter S0='d0,S1='d1,S2='d2,S3='d3,S4='d4,S5='d5,S6='d6,IDLE='d7;

reg[2:0] state;

assign pat_det=(state= =S6&&din= =0)?1:0;

always@(posedge clk or negedge rstb)

begin

if(!rstb) state<=IDLE;

else

begin

case(state)

IDLE:

begin

if(din==0) state<=S0;

else state<=IDLE;

end

S0:

begin

if(din==0) state<=S1;

else state<=IDLE;

end

S1:

begin

if(din==1) state<=S2;

else state<=S1;

end

S2:

begin

if(din==0) state<=S3;

else state<=IDLE;

end

S3:

begin

if(din==1) state<=S4;

else state<=S1;

end

S4:

begin

if(din==0) state<=S5;

else state<=IDLE;

end

S5:

begin

if(din==1) state<=S6;

else state<=S1;

end

S6: state<=IDLE;

default: state<=IDLE;

endcase

end

end

endmodule

(2)Test File

`timescale 1ns/1ns

`include "serialdata.v"

module tb_serialdata;

reg clk,rstb;

wire din;

wire pat_det;

reg[31:0] data;

assign din=data[31];

serialdata t1(din,clk,rstb,pat_det);

initial begin

clk=1'b0;

rstb=1'b0;

data=32'b1001_0010_1010_1100_1010_1000_1010_1010;

#10 rstb=1'b1;

#640 $stop;

end

always@(posedge clk)

begin

data <={data[30:0],data[31]};

end

always #5 clk=~clk;

endmodule

(3)波形与说明

图示标注地方每个上升沿取得数据din,当检测到00101010之后输出pat_det 置为高电平。

整个32位串行输入数据1001_0010_1010_1100_1010_1000_1010_1010,总共640个时间单位stop,即32位输入数据跑两遍,共输出6个高电平脉冲,符合设计!

题目2:设计一个串行数据检测器,输入数据与时钟同步。

要求是:输入连续5

个或5 个以上的1 时输出为1,其他输入情况下输出为0

(1)RTL Code

/*信号定义与说明

clk: 同步输入时钟

nreset: 复位信号,低电平有效

din: 串行数据输入

out:检测结果输出

*/

`timescale 1ns/1ns

module serialfive1(out,din,clk,nreset);

input din;

input clk,nreset;

output out;

parameter M0='d0,M1='d1,M2='d2,M3='d3,M4='d4,IDLE='d5;

reg[2:0] state;

assign out=(state==M4&&din==1)?1:0;

always @(posedge clk)

begin

if(!nreset) state<=IDLE;

else

case(state)

IDLE:

begin

if(din==1) state <= M0;

else state <= IDLE;

end

M0:

begin

if(din==1) state <= M1;

else state <= IDLE;

end

M1:

begin

if(din==1) state <= M2;

else state <= IDLE;

end

M2:

begin

if(din==1) state <= M3;

else state <= IDLE;

end

M3:

begin

if(din==1) state <= M4;

else state <= IDLE;

end

M4:

begin

if(din==1) state <= M4;

else state <= IDLE;

end

default: state <= IDLE;

endcase

end

endmodule

(2)Test File

`include "serialfive1.v"

`timescale 1ns/1ns

module tb_serialfive1;

reg clk,nreset;

wire din,out;

reg[15:0] data;

assign din=data[15];

serialfive1 t1(out,din,clk,nreset);

initial

begin

clk = 1'b0;

nreset = 1'b0;

data = 'b0111_1110_0101_1111;

#8 nreset = 1'b1;

#320 $stop;

end

always #5 clk=~clk;

always @(posedge clk)

data = {data[14:0],data[15]};

endmodule

(3)波形与说明

如图所示,输入16位串行数据0111_1110_0101_1111。

在320个时间单位跑两遍,一共输出4个高电平脉冲输出,其中一个是连续6个1,所以其维持2个clk,如图示,满足设计要求!。