EDA考试程序

EDA常用程序

08 上EDA 复习纲要考试题分两个大题,编程题和设计题,如下面例子所示,叙述的部分需要写到试卷上,还有需要画出框图,所以需要带上铅笔和直尺!编程题一、用CASE/WHEN_ELSE/WITH_SELECT 语句设计一个一位四选一数据选择器,实体名为MUX4,要求画出设计的框图(手工),并简单叙述各端口的作用(手工);写出VDHL程序并生成符号文件(计算机)。

例:用CASE语句设计的四选一数据选择器,(其他语句也要掌握):其中DIN[3..0]为数据输入端口,SEL[1..0]为数据选择端口,由SEL 的二进制数据来决定那一个数据被选通,YOUT 为数据输出端口。

LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;--************************************ENTITY MUX4 ISPORT(DIN :IN STD_LOGIC_VECTOR(3 DOWNTO 0);SEL :IN STD_LOGIC_VECTOR(1 DOWNTO 0);YOUT:OUT STD_LOGIC);END MUX4;ARCHITECTURE CASE_M4ARCH OF MUX4 ISBEGINPROCESS(DIN,SEL)BEGINCASE SEL ISWHEN"00"=>YOUT<=DIN(0);WHEN"01"=>YOUT<=DIN(1);WHEN"10"=>YOUT<=DIN(2);WHEN"11"=>YOUT<=DIN(3);WHEN OTHERS=>NULL;END CASE;END PROCESS;END CASE_M4ARCH;二、用FOR_GENERATE语句调用D触发器(设D触发器已经存在,名字为DFF1,端口:d,clk:in std_logic;q:out std_logic)设计一个四位串入并出移位寄存器,实体名为SREG4,要求画出设计的框图(手工),并简单叙述各端口的作用(手工);写出程序并生成符号文件(计算机)。

EDA考试要点

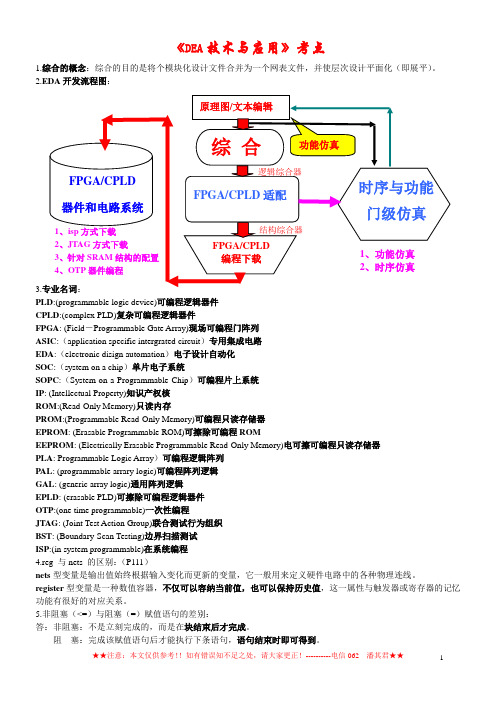

《DEA 技术与应用》考点1.综合的概念:综合的目的是将个模块化设计文件合并为一个网表文件,并使层次设计平面化(即展平)。

2.EDA 开发流程图:3.专业名词:PLD :(programmable logic device)可编程逻辑器件CPLD :(complex PLD)复杂可编程逻辑器件FPGA : (Field -Programmable Gate Array)现场可编程门阵列ASIC :(application specific intergrated circuit )专用集成电路EDA :(electronic disign automation )电子设计自动化SOC :(system on a chip )单片电子系统SOPC :(System-on-a-Programmable-Chip )可编程片上系统IP : (Intellectual Property)知识产权核ROM :(Read-Only Memory)只读内存PROM :(Programmable Read-Only Memory)可编程只读存储器EPROM : (Erasable Programmable ROM)可擦除可编程ROMEEPROM : (Electrically Erasable Programmable Read-Only Memory)电可擦可编程只读存储器PLA : Programmable Logic Array )可编程逻辑阵列PAL : (programmable arrary logic)可编程阵列逻辑GAL : (generic array logic)通用阵列逻辑EPLD : (erasable PLD)可擦除可编程逻辑器件OTP :(one time programmable)一次性编程JTAG : (Joint Test Action Group)联合测试行为组织BST : (Boundary-Scan Testing)边界扫描测试ISP :(in system programmable)在系统编程4.reg 与nets 的区别:(P111)nets 型变量是输出值始终根据输入变化而更新的变量,它一般用来定义硬件电路中的各种物理连线。

eda考试程序

全加器设计:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL; ENTITY add1_v ISPORT(A : IN STD_LOGIC;B : IN STD_LOGIC;Cin : IN STD_LOGIC;Co : OUT STD_LOGIC;S : OUT STD_LOGIC); END add1_v;and2_vARCHITECTURE structure OF add1_v ISCOMPONENT PORT(a : IN STD_LOGIC;b : IN STD_LOGIC;y : OUT STD_LOGIC);END COMPONENT; COMPONENT or2_vPORT(a : IN STD_LOGIC;b : IN STD_LOGIC;y : OUT STD_LOGIC);END COMPONENT; COMPONENT xor2_vPORT(a : IN STD_LOGIC;b : IN STD_LOGIC;y : OUT STD_LOGIC);END COMPONENT; SIGNAL tmp1,tmp2,tmp3 : STD_LOGIC;FOR U1,U2 : xor2_v USE ENTITY work.xor2_v( xor2_arc);FOR U3,U4 : and2_v USE ENTITY work.and2_v( and2_arc);FOR U5 : or2_v USE ENTITY work.or2_v( or2_arc);BEGINU1 : xor2_v PORTMAP(A,B,tmp1);U2 : xor2_v PORTMAP(tmp1,Cin,S);U3 : and2_v PORTMAP(tmp1,Cin,tmp2);U4 : and2_v PORTMAP(A,B,tmp3);U5 : or2_v PORTMAP(tmp2,tmp3,Co);END structure;全加器行为描述方式:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY add1_v ISPORT(A : IN STD_LOGIC;B : IN STD_LOGIC;Cin : IN STD_LOGIC;Co : OUT STD_LOGIC;S : OUT STD_LOGIC);END add1_v;ARCHITECTURE structure OF add1_vISBEGINS <= A XOR B XOR Cin;Co <= (A XOR B) AND Cin OR(A AND B);END structure;行为描述全加器:ARCHITECTURE behav OF full_adderISBEGINPROCESS (x, y, c_in)V ARIABLE n: INTEGER;CONSTANT sum_vector:STD_LOGIC_VECTOR (0 TO 3) :=“0101”;CONSTANT carry_vector:STD_LOGIC_VECTOR (0 TO 3) :=“0011”;BEGINn := 0;IF x = ‟1‟ THENn := n+1;END IF;IF y = ‟1‟ THENn:=n+1;END IF;IF c_in = ‟1‟ THENn:=n+1;END IF;sum <= sum_vector (n) AFTER2*tpd;c_out <= carry_vector (n)AFTER 3*tpd;END PROCESS;数据流描述:LIBRARY IEEE;USEIEEE.STD_LOGIC_1164.ALL;ENTITY full_adder ISGENERIC(tpd : TIME := 10ns);PORT(x,y,c_in : INSTD_LOGIC;Sum, c_out : OUTSTD_LOGIC);END full_adder;ARCHITECTURE dataflow OFfull_adder ISBEGINs <= x XOR y AFTER tpd;sum <= s XOR c_in AFTERtpd;c_out <= (x AND y) OR( s ANDc_in) AFTER 2* tpd;END dataflow;半加器设计:ARCHITECTURE behavioral OFhalf_adder ISBEGINPROSESS (in1, in2)BEGINsum <= in1 XOR in2 AFTERtpd;carry <= in1 AND in2 AFTERtpd;END PROCESS;END behavioral;警告系统:LIBRARY ieee;USE ieee.std_logic_1164.all;ENTITY alarm ISPORT(smoke,door,water:INstd_logic;en,alarm_en :IN std_logic;fire_alarm,burg_alarm,water_alarm:OU T std_logic);END alarm;ARCHITECTURE alarm_arc OF alarm ISBEGINPROCESS(smoke,door,water,en,alarm_e n)BEGINIF ((smoke= …1‟) AND (en= …0‟)) THENfire_alarm <= …1‟;ELSEfire_alarm <= …0‟;END IF;IF ((door= …1‟) AND ((en= …0‟) AND (alarm_en= …0‟))) THENburg_alarm <= …1‟;ELSEburg_alarm <= …0‟;END IF;IF ((water= …1‟) AND (en= …0‟)) THENwater_alarm <= …1‟;ELSEwater_alarm <= …0‟;END IF;END PROCESS;END alarm_arc四选一数据选择器LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY mux4 ISPORT(d0 :INSTD_LOGIC_VECTOR (7 DOWNTO1);d1 :INSTD_LOGIC_VECTOR (7 DOWNTO1);d2 :INSTD_LOGIC_VECTOR (7 DOWNTO1);d3 :INSTD_LOGIC_VECTOR (7 DOWNTO1);s0 :INSTD_LOGIC;s1 :INSTD_LOGIC;y :OUTSTD_LOGIC_VECTOR (7 DOWNTO1) );END mux4 ;:ARCHITECTURE behave OFmux4 ISBEGINlable:PROCESS(d0,d1,d2,d3,s0,s1)V ARIABLE tmp:INTEGER;BEGINtmp := 0;IF(s0=…1‟)THENtmp := tmp+1;END IF;IF(s1=…1‟)THENtmp := tmp+2;END IF;CASE tmp ISWHEN 0 => y <=d0;WHEN 1 => y <=d1;WHEN 2 => y <=d2;WHEN 3 => y <=d3;WHEN OTHERS=> NULL;END CASE;END PROCESS;END behave;3数最大值比较器:;LIBRARY IEEE;USE IEEE. STD_LOGIC_1164.ALL;USE IEEE. STD_LOGIC_UNSIGNED.ALL;ENTITY max ISPORT(in1:IN STD_LOGIC_VECTOR (7 DOWNTO 0);in2:IN STD_LOGIC_VECTOR (7 DOWNTO 0);in3:INSTD_LOGIC_VECTOR (7 DOWNTO0);q:OUTSTD_LOGIC_VECTOR (7 DOWNTO0) );END max ;ARCHITECTURE rtl OF max ISPROCEDURE maximum(a,b:IN STD_LOGIC_VECTOR;c:OUT STD_LOGIC_VECTOR)ISV ARIABLE temp:STD_LOGIC_VECTOR(a‟RANGE);BEGINIF(a > b)THENtemp := a;ELSEtemp := b;END IF;c := temp;END maximum;BEGINPROCESS(in1,in2,tmp1)V ARIABLE tmp1,tmp2:STD_LOGIC_VECTOR (7 DOWNTO 0) ;BEGINmaximum(in1,in2,tmp1);maximum(tmp1,in3,tmp2);q <= tmp2;END PROCESS;END rtl;四位移位寄存器:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY shift_reg ISPORT(di:IN STD_LOGIC;cp:IN STD_LOGIC;do:OUTSTD_LOGIC);END shift_reg;ARCHITECTURE structure OFshift_reg ISCOMPONENT dffPORT(d:INSTD_LOGIC;clk:INSTD_LOGIC;q:OUTSTD_LOGIC);END COMPONENT;SIGNAL q:STD_LOGIC_VECTOR(4 DOWNTO0);BEGINdff1:dff PORT MAP (d1,cp,q(1));dff2:dff PORT MAP (q(1),cp,q(2));dff3:dff PORT MAP (q(2),cp,q(3));dff4:dff PORT MAP (q(3),cp,do);END structure;用VHDL 语言设计同步60 进制计数器library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;library altera;use altera.maxplus2.all;library lpm;use lpm.lpm_components.all;entity count60 isport(clk,clr,en:in std_logic;cy:out std_logic;qh,ql:out std_logic_vector(3 downto 0));end count60;architecture behavior of count60 is signal qh_tmp,ql_tmp:std_logic_vector(3 downto 0);beginqh<=qh_tmp;ql<=ql_tmp;cy<='1'when(ql_tmp="1001"andqh_tmp="0101")else '0';--²¢ÐÐÓï¾äÃèÊö½øλprocess(clr,clk,en)beginif clr='0'thenqh_tmp<=(others=>'0');--µÈ¼ÛÓëqh_tmp<="0000";ql_tmp<=(others=>'0');elsif (clk'event and clk='1')thenif en='1'thenif (ql_tmp=9)thenql_tmp<="0000";if(qh_tmp=5)thenqh_tmp<="0000";elseqh_tmp<=qh_tmp+1;end if;elseql_tmp<=ql_tmp+1;end if;end if;--END IF (EN)end if;--END IF(clr)end process;end behavior;状态机:LIBRARY IEEE;USEIEEE.std_logic_1164.ALL;USEIEEE.std_logic_unsigned.ALL; --operator '-' IS overwrited IN the packageentity timer ISport ( data_in: INstd_logic_vector( 7 DOWNTO 0 );reset, CLK, start:IN std_logic;ring : OUTstd_logic);END timer;architecture behav OF timerISBEGINPROCESS( reset, clk )V ARIABLEcounter: std_logic_vector( 7DOWNTO 0 );V ARIABLE state: integer RANGE 0 TO 3;BEGINIF reset = '0' THENring <= '0';state := 0;ELSIF clk'event AND clk = '1' THENCASE state ISWHEN 0 =>ring <= '0';counter := "00000000";IF start = '1' THENstate := 1;ELSEstate := 0;END IF;WHEN 1 =>counter := data_in; IF start = '1' THEN state := 1; ELSEstate := 2; END IF;WHEN 2 =>IF counter < 3 THENcounter := "00001000"state := 3;ELSEcounter := counter - 1;state := 2;END IF;WHEN 3 =>ring <= '1';IF counter = 1 THENstate := 0;ELSECountter := counter - 1;state := 3;END IF;END CASE;END IF;END PROCESS;END behav;四--七library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;--************************************entity yima47 isport(in47:in std_logic_vector(3 downto 0);seg:out std_logic_vector(6 downto 0));end yima47;--************************************************ architecture a of yima47 isbeginseg<="1000000"when in47=0 else"1111001"when in47=1 else"0100100"when in47=2 else"0110000"when in47=3 else"0011001"when in47=4 else"0010010"when in47=5 else"0000010"when in47=6 else"1111000"when in47=7 else"0000000"when in47=8 else"0010000";--=>seg<="0010000";end a;。

电子EDA实操考试方案-李全胜(1)

2015-2016第一学期上机实操(期中)考试方案适用年级:14级适用专业:电气自动化课程题目:DXP考生须知:考生必须在D:盘,以“姓名+学号”为名建立一个文件夹,并在该文件夹中以“姓名+学号”为名建立设计数据库文件,将所有答题放入设计数据库里。

《DXP》课程实用性强,每周都在机房上机。

因此,通过考核学生的上机绘图功能,可以很好的检验学生对Protel DXP绘图软件的掌握程度。

本课程期末考试采取上机实操考核方式,具体方案如下:每班都分组随堂考试,教师根据上机课时间自己掌握时间,为防止泄题,任课教师考试时随机对学习过的内容进行抽取,按照难以程度在打分时进行调整。

开考后,登记每人的机器编号,姓名,学号,考试时间到,学生立刻离开机房室,由任课老师对每位学生的考试情况进行打分。

每组的考试时间为100分钟,为防止题目泄露,每组题目均不相同,但难易相当,随堂考试,一周内考完。

绘制的图形最终打印出来由任课教师手写签名并打分之后连同电子版统一交给系里,没有签名的成绩无效。

实操考试占总成绩的50%,另外50%为平时成绩,包括上机上课点名、作业等。

根据提供的图纸(如图1、图2)教师给每位学生指定出题目,在Protel DXP软件中绘制原理图,具体要求如下:图1 单片机应用电路图2 数模转换电路1、在D盘新建考生文件夹,命名为班级+考生姓名。

例如:109101张三。

(5分)2、在Protel DXP中新建项目文件,命名为班级+考生姓名,例如:109101张三.PrjPCB。

所有原理图文件、PCB文件等均应保存在该项目文件下。

(5分)3、原理图尺寸、选项要求。

(5分)4、取消默认标题栏显示,根据下列参数,自行设计标题栏,放置于图纸右下角,并填入相关数据。

(姓名、班级、制图时间、图纸名称、图纸尺寸、成绩)(5分)5、正确选择与放置元件,修改元件属性和参数。

(10分)6、原理图设计要求:原理图布局居中;元件符号使用、标注正确;无重复标注、无元件摆放重叠;线路绘制正确;接点无遗漏。

EDA考试必考知识点

考试题型:简答题,程序语句解释,程序填空,编程EDA就是以计算机为工作平台,以EDA软件工具为开发环境,以PLD器件或者ASIC专用集成电路为目标器件设计实现电路系统的一种技术。

现代EDA技术的特征:1,、采用硬件描述语言进行设计2、逻辑综合与优化3、开放性和标准化4.、更完备的库。

数字系统设计技术:1、Topdown即自顶向下的设计。

这种设计首先从系统设计下手,在顶层进行功能方框图的划分和结构设计。

须经过“设计—验证—修改设计再验证”的过程,不断反复,直到结果能够实现所要求的功能,并在速度、功耗、价格和可靠性方面实现较为合理的平衡。

2、Bottomup设计,即自底向上的设计,由设计者调用设计库中的元件(如各种门电路、加法器、计数器等) ,设计组合出满足自己需要的系统。

不仅效率低、成本高而且易出错。

IP:原来的含义是指知识产权、著作权,在IC设计领域指实现某种功能的设计。

IP核(IP模块):指功能完整,性能指标可靠,已验证的、可重用的电路功能模块。

IP复用:软IP--用VHDL等硬件描述语言描述的功能块,但是并不涉及用什么具体电路元件实现这些功能。

固IP完成了综合的功能块。

硬IP供设计的最终阶段产品:掩膜。

基于IP复用的开发帮助设计者节省时间,缩短开发周期,避免重复劳动。

可编程逻辑阵列PLA,可编程与阵列或阵列,输出电路固定。

可编程阵列逻辑PAL,可编程与阵列,或阵列输出电路固定。

FPGA是一种半定制的器件,器件内已做好各种逻辑资源,用户只需对器件内的资源编程连接就可实现所需要的功能。

ASIC指用全定制的方法来实现设计的方式,它在最底层,即物理版图级实现设计,因此也称为掩膜ASCI。

CPLD即复杂可编程逻辑器件,是从EPLD改进而来的。

逻辑综合:RTL级描述转换到逻辑门级(包括触发器)。

版图综合或结构综合:从逻辑门表示转换到版图表示,或转换到PLD器件的配置网表表示。

综合器是能够自动实现上述转换的软件工具,是能将原理图或HDL语言描述的电路功能转化为具体电路结构网表的工具。

EDA考试必考知识点

EDA考试必考知识点咱先来说说 EDA 这玩意儿哈,这在考试里可重要得很呢!就像你去参加一场刺激的冒险,EDA 知识就是你手中的关键地图。

首先,EDA 的基本概念那是必考的。

啥是 EDA 呢?简单来说,就是电子设计自动化,它能帮工程师们更高效地设计电路和系统。

比如说,有一次我去一个电子厂参观,看到工程师们坐在电脑前,用 EDA软件就像变魔术一样,把复杂的电路设计得井井有条。

那场面,真让人惊叹!然后就是 EDA 工具的使用。

像那些常见的 EDA 工具,比如Cadence、Altium Designer 等等,你得熟悉它们的操作界面、功能模块。

我记得有个学生,在考试前拼命练习工具的使用,结果考试的时候碰到一个相似的题目,轻松就拿下了高分。

再说说硬件描述语言,像 VHDL 和 Verilog 这俩“大佬”。

你得搞清楚它们的语法规则、数据类型、控制结构。

想象一下,你要用这些语言来给电路“说话”,告诉它该怎么做。

这就好比你指挥一个机器人,得把指令说得明明白白。

还有数字电路设计,这也是重点中的重点。

什么组合逻辑电路、时序逻辑电路,都得弄得清清楚楚。

我曾经遇到过一个实际的案例,一个电路出现故障,就是因为时序逻辑没设计好,导致整个系统都乱套了。

另外,系统级设计也是必考的一块儿。

从顶层到底层,怎么把一个大的系统分解成一个个小模块,再把它们整合起来,这可需要不少功夫。

在 EDA 考试中,仿真和验证也是不能忽视的。

你设计好的电路到底行不行,得通过仿真来验证一下。

就像你做好了一道菜,得尝尝味道对不对。

最后,可别忘了综合和布局布线。

这就像是给你的电路找个合适的“家”,让它能舒舒服服地工作。

总之,EDA 考试的必考知识点就像一个个宝藏,你得用心去挖掘、去掌握。

只要你认真学习,多做练习,相信在考试中一定能取得好成绩,顺利开启你的电子设计之旅!加油吧!。

《EDA技术及电子电路PCB设计》实操考核题

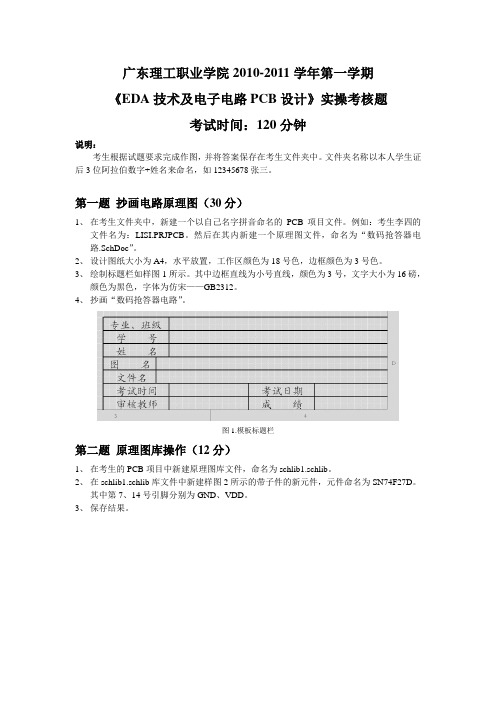

广东理工职业学院2010-2011学年第一学期《EDA技术及电子电路PCB设计》实操考核题考试时间:120分钟说明:考生根据试题要求完成作图,并将答案保存在考生文件夹中。

文件夹名称以本人学生证后3位阿拉伯数字+姓名来命名,如12345678张三。

第一题抄画电路原理图(30分)1、在考生文件夹中,新建一个以自己名字拼音命名的PCB项目文件。

例如:考生李四的文件名为:LISI.PRJPCB。

然后在其内新建一个原理图文件,命名为“数码抢答器电路.SchDoc”。

2、设计图纸大小为A4,水平放置,工作区颜色为18号色,边框颜色为3号色。

3、绘制标题栏如样图1所示。

其中边框直线为小号直线,颜色为3号,文字大小为16磅,颜色为黑色,字体为仿宋——GB2312。

4、抄画“数码抢答器电路”。

图1.模板标题栏第二题原理图库操作(12分)1、在考生的PCB项目中新建原理图库文件,命名为schlib1.schlib。

2、在schlib1.schlib库文件中新建样图2所示的带子件的新元件,元件命名为SN74F27D。

其中第7、14号引脚分别为GND、VDD。

3、保存结果。

第三题 PCB库操作(13分)在考生的设计文件中新建PCBLIB1.PcbLib文件,根据图3参数设计要求创建SN74F27D 元件封装,命名为DIP14。

单位:inches (millimeters)。

第四题制图(45分)1、选择合适的电路板尺寸制作电路板边,要求一定要选择国家标准。

2、在数码抢答器电路.PcbDoc中制作电路板,要求根据电路给出的电流分配关系与电压大小,选择合适的导线宽度和线距。

3、要求选择合适的管脚封装,如果和标准库中的不一致或没有时,要进行修改或新建。

4、保存结果。

图3.DIP14图4.数码抢答器电路。

EDA实验考试程序

1,设计一个带计数使能、同步复位、带进位输出的增1六位二进制计数器,计数结果由共阴极七段数码管显示。

library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity counter isport(clk,clk1,en,clr:in std_logic;ledout:out std_logic_vector(6 downto 0);scanout:out std_logic_vector(1 downto 0);co:out std_logic);end counter;architecture a of counter issignal cnt:std_logic_vector(7 downto 0);signal led:std_logic_vector(6 downto 0);signal scan:std_logic:='0';signal hex:std_logic_vector(3 downto 0);beginprocess(clk)beginif(clk'event and clk='1')thenif en='1'thenif clr='1'thencnt<=(others=>'0');elseif cnt="00111111"thencnt<="00000000";co<='1';elsecnt<=cnt+'1';co<='0';end if;end if;end if;end if;end process;process(clk1)beginif clk1'event and clk1='1'then scan<=not scan;end if;end process;ledout<= not led;scanout<="10" when scan='0' else "01";hex<=cnt(7 downto 4) when scan='1'else cnt(3 downto 0); with hex selectled<="1111001"when"0001","0100100"when"0010","0110000"when"0011","0011001"when"0100","0010010"when"0101","0000010"when"0110","1111000"when"0111","0000000"when"1000","0010000"when"1001","0001000"when"1010","0000011"when"1011","1000110"when"1100","0100001"when"1101","0000110"when"1110","0001110"when"1111","1000000"when others;end a;2、设计一个带计数使能、异步复位、带进位输出的增1二十进制计数器,计数结果由共阴极七段数码管显示。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

---'1' Counter---library ieee;use ieee.std_logic_1164.all;entity sj9 isport(din:in std_logic_vector(7 downto 0);counter:out integer range 0 to 8); end sj9;architecture bhv of sj9 isbeginprocess(din)variable temp:integer range 0 to 8;begintemp:=0;for i in 0 to 7 loopif din(i)='1' thentemp:=temp+1;end if;end loop;counter<=temp;end process;end bhv;6分频器library ieee;use ieee.std_logic_1164.all;entity f_divider isport(clk:in std_logic;output:buffer std_logic);end f_divider;architecture bhv of f_divider isbeginprocess(clk)variable count:integer range 0 to 5; variable op:std_logic;beginif clk'event and clk='1' thencount:=count+1;if count=3 thenoutput<=not output;count:=0;end if;end if;end process;end bhv; led译码器library ieee;use ieee.std_logic_1164.all;entity LED_encoder isport(a:in std_logic_vector(3 downto 0);dataout:out std_logic_vector(6 downto 0));end LED_encoder;architecture bhv of LEd_encoder isbegindataout<="0111111" when a="0000" else"0000110" when a="0001" else"1011011" when a="0010" else"1001111" when a="0011" else"1100110" when a="0100" else"1101101" when a="0101" else"1111101" when a="0110" else"0000111" when a="0111" else"1111111" when a="1000" else"1101111" when a="1001" else"1110111" when a="1010" else"1111100" when a="1011" else"0111001" when a="1100" else"1011110" when a="1101" else"1111001" when a="1110" else"1110001";end bhv;--------ROM--------16*8--------library ieee;use ieee.std_logic_1164.all;entity sj15rom isport(addr:integer range 0 to 15;dout:out integer range 0 to 255);end sj15rom;architecture bhv of sj15rom istype mem_type is array(0 to 15)of integer range 0 to 255;constantmemory:mem_type:=(15,34,85,122,49,65,47,9 4,212,3,55,67,81,29,44,37);begindout<=memory(addr);end bhv;------RAM-----------16*8------library ieee;use ieee.std_logic_1164.all;entity sj15ram isgeneric (m:integer:=8;n:integer:=16);port(wr_ena,clk:in std_logic;addr:in integer range 0 to n-1;din:in std_logic_vector(m-1 downto 0);dout:out std_logic_vector(m-1 downto 0)); end sj15ram;architecture bhv of sj15ram istype vector_array is array(0 to n-1)of std_logic_vector(m-1 downto 0);signal memory :vector_array;beginprocess(clk,wr_ena)beginif wr_ena='1'thenif clk'event and clk='1' thenmemory(addr)<=din;end if;end if;end process;dout<=memory(addr);end bhv;STOP_WATCH代码:COUNTER:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity counter isport(clk,rst:in std_logic;outp1:out std_logic_vector(3 downto 0));end counter;architecture bhv of counter isbeginprocess(clk,rst)variable temp:std_logic_vector(3 downto 0); beginif rst='1' then temp:="0000";elsif clk'event and clk='1' thenif temp="1010" thentemp:="0000";elsetemp:=temp+1;end if;end if;outp1<=temp;end process;end bhv;REGIST:library ieee;use ieee.std_logic_1164.all;entity regist isport(inp2:in std_logic_vector(3 downto 0);store:in std_logic;outp2:out std_logic_vector(3 downto 0));end regist;architecture bhv of regist isbeginprocess(store)beginif store='1' thenoutp2<=inp2;end if;end process;end bhv;STOP_WA TCH:library ieee;use ieee.std_logic_1164.all;entity stop_watch isport(clk,stop:in std_logic;reg:out std_logic_vector(3 downto 0)); end stop_watch;architecture bhv of stop_watch is component counter isport(clk,rst:in std_logic;outp1:out std_logic_vector(3 downto 0));end component counter;component regist isport(inp2:in std_logic_vector(3 downto 0);store:in std_logic;outp2:out std_logic_vector(3 downto 0));end component regist;signal m:std_logic_vector(3 downto 0); beginu1:counter port map(clk,stop,m);u2:regist port map(m,stop,reg);end bhv;比较器library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;entity comparer isport(a,b:in unsigned (7 downto 0);sel:in bit;x1,x2,x3:out bit);end comparer;architecture bhv of comparer isbeginprocess(a,b,sel)variable a_temp,b_temp:signed(7 downto 0); begina_temp:=conv_signed(a,8);b_temp:=conv_signed(b,8);case sel iswhen '0'=>if a>b thenx1<='1';x2<='0';x3<='0';elsif a=b thenx2<='1';x1<='0';x3<='0';elsex3<='1';x2<='0';x1<='0';end if;when '1'=>if a_temp>b_temp thenx1<='1';x2<='0';x3<='0';elsif a_temp=b_temp thenx2<='1';x1<='0';x3<='0';elsex3<='1';x2<='0';x1<='0';end if;when others=>null;end case;end process;end bhv;编码器library ieee;use ieee.std_logic_1164.all;entity encoder isport(a:in std_logic_vector(7 downto 0);b:out std_logic_vector(2 downto 0)); end encoder;architecture bhv of encoder isbeginb<="000" when a="00000001" else"001" when a="00000010" else"010" when a="00000100" else"011" when a="00001000" else"100" when a="00010000" else"101" when a="00100000" else"110" when a="01000000" else"111" when a="10000000" else"ZZZ";end bhv;并串转换器library ieee;use ieee.std_logic_1164.all;entity sj14 isport(clk,load:in std_logic;din:in std_logic_vector(7 downto 0);dout:out std_logic);end sj14;architecture bhv of sj14 isbeginprocess(clk)variable temp:std_logic_vector(7 downto 0); beginif clk'event and clk='1' thenif load='1' thentemp:=din;elsedout<=temp(7);temp:=temp(6 downto 0)&'0';end if;end if;end process;end bhv;存储控制器library ieee;use ieee.std_logic_1164.all;entity sj19 isport(clk,ready,lw_r,blast:in std_logic;mread,mwrite:out std_logic);end sj19;architecture bhv of sj19 istype state is (idle,decision,r_ead,w_rite); signal p_s,n_s:state;beginprocess(clk)beginif clk'event and clk='1' thenp_s<=n_s;end if;end process;process(ready,lw_r,blast,p_s)begincase p_s iswhen idle=>mwrite<='0';mread<='0';if ready='1' thenn_s<=decision;elsen_s<=idle;end if;whendecision=>mwrite<='0';mread<='0';if lw_r='0' thenn_s<=r_ead;elsen_s<=w_rite;end if;when r_ead=>mwrite<='0';mread<='1';if blast='1' thenn_s<=idle;elsen_s<=r_ead;end if;whenw_rite=>mwrite<='1';mread<='0';if blast='1' thenn_s<=idle;elsen_s<=w_rite;end if;end case;end process;end bhv;二百进制计数器library ieee;use ieee.std_logic_1164.all;entity counter isport(clk,rst,ena:in std_logic;d1,d2:out integer range 0 to 15;d3:out integer range 0 to 3);end counter;architecture bhv of counter isbeginprocess(clk,rst,ena)variable temp1:integer range 0 to 10; variable temp2:integer range 0 to 10; variable temp3:integer range 0 to 2;beginif rst='1' thentemp1:=0;temp2:=0;temp3:=0;elsif clk'event and clk='1' thenif ena='1' thentemp1:=temp1+1;if temp1=10 thentemp1:=0;temp2:=temp2+1;if temp2=10 thentemp2:=0;temp3:=temp3+1;if temp3=2 thentemp3:=0;end if;end if;end if;end if;end if;d1<=temp1;d2<=temp2;d3<=temp3;end process;end bhv;二进制_格雷码转换器library ieee;use ieee.std_logic_1164.all;entity shift isgeneric (n:integer :=4);port (inp:in std_logic_vector(n-1 downto 0);outp: out std_logic_vector(n-1 downto 0));end shift;architecture bhv of shift isbeging1:for i in 0 to n-2 generateoutp(i)<=not inp(i) when inp(i+1)='1' else inp(i);end generate;outp(n-1)<=inp(n-1);end bhv;空调控制器library ieee;use ieee.std_logic_1164.all;entity air_controller isport(temp_high,temp_low,clk:in std_logic;hot,cold:out std_logic);end air_controller; architecture bhv of air_controller is type state is (normal,high1,low1); signal n_s,p_s : state;beginprocess(clk)beginif clk'event and clk='1' thenp_s<=n_s;end if;end process;process(temp_high,temp_low,p_s) begincase p_s iswhen high1 => cold<='1';hot<='0';if temp_low='1' thenn_s<=low1;elsif temp_high='1' thenn_s<=high1;elsen_s<=normal;end if;when low1 => cold<='0';hot<='1';if temp_high='1' thenn_s<=high1;elsif temp_low='1' thenn_s<=low1;elsen_s<=normal;end if;when normal => cold<='0';hot<='0';if temp_high='1' thenn_s<=high1;elsif temp_low='1' thenn_s<=low1;elsen_s<=normal;end if;end case;end process;end bhv;密度编码器library ieee;use ieee.std_logic_1164.all;entity encoder isport(din:in std_logic_vector(7 downto 1);dout:out std_logic_vector(7 downto 0)); end encoder;architecture bhv of encoder isbeginprocess(din)variable count :integer range 0 to 7;begincount:=0;for i in 7 downto 1 loopcase din(i) iswhen '1'=>count:=count+1;when others=>next;end case;end loop;case count iswhen 0=> dout<="00000001";when 1=> dout<="00000010";when 2=> dout<="00000100";when 3=> dout<="00001000";when 4=> dout<="00010000";when 5=> dout<="00100000";when 6=> dout<="01000000";when 7=> dout<="10000000";end case;end process;end bhv;奇偶校验器library ieee;use ieee.std_logic_1164.all;entity xiti6_8 isport(datain:in std_logic_vector(7 downto 0);dataout:out std_logic);end xiti6_8;architecture bhv of xiti6_8 isbeginprocess(datain)variable temp:std_logic;begintemp:='0';for i in 0 to 7 looptemp:=temp xor datain(i);end loop;dataout<=temp;end process;end bhv;三态缓冲电路library ieee;use ieee.std_logic_1164.all;entity tri_state isport(ena:in std_logic;input:in std_logic_vector(7 downto 0);output:out std_logic_vector(7 downto 0));end tri_state;architecture bhv of tri_state isbeginoutput<=input when ena='0' else"ZZZZZZZZ";end bhv;数据选择器library ieee;use ieee.std_logic_1164.all;entity mux isport(a,b,c,d,sel1,sel2:in std_logic;y:out std_logic);end mux;architecture bhv of mux issignal sel:std_logic_vector(1 downto 0); beginsel<=sel1 & sel2;with sel selecty<=a when "00",b when "01",c when "10",d when others;end bhv;信号发生器-进程library ieee;use ieee.std_logic_1164.all;entity xhfsq isport(clk:in std_logic;dataout:out std_logic_vector(7 downto 0));end xhfsq;architecture bhv of xhfsq istype mem_type is array (0 to 63) of std_logic_vector(7 downto 0);constant memory : mem_type:=("11111111"等数据);beginprocess(clk)variable count:integer range 0 to 63;beginif clk'event and clk='1' thendataout<=memory(count);count:=count+1;end if;end process;end bhv;信号发生器-状态机library ieee;use ieee.std_logic_1164.all;entity signal_gen isport(clk:in std_logic;out1,out2:out std_logic);end signal_gen;architecture bhv of signal_gen istype state is(s1,s2,s3,s4);signal p_s1,n_s1:state;signal p_s2,n_s2:state;signal temp1,temp2:std_logic;beginprocess(clk)beginif clk'event and clk='1' thenp_s1<=n_s1;end if;end process;process(clk) beginif clk'event and clk='0' thenp_s2<=n_s2;end if;end process;process(p_s1)begincase p_s1 iswhen s1 => out1<='0';temp1<='0';n_s1<=s2;when s2 => out1<='1';temp1<='0';n_s1<=s3;when s3 => out1<='0';temp1<='1';n_s1<=s4;when s4 => out1<='0';temp1<='0';n_s1<=s1;end case;end process;process(p_s2)begincase p_s2 iswhen s1 => temp2<='0';n_s2<=s2;when s2 => temp2<='1';n_s2<=s3;when s3 => temp2<='0';n_s2<=s4;when s4 => temp2<='0';n_s2<=s1;end case;end process;out2<=temp1 xor temp2;end bhv;序列检测器library ieee;use ieee.std_logic_1164.all; entity str_detector isport (datain,rst,clk:in std_logic;dataout:out std_logic); end str_detector;architecture bhv of str_detector is type state is(s0,s1,s2,s3,s4,s5,s6); signal n_s,p_s :state;beginprocess(rst,clk)beginif rst='1' thenp_s<=s0;elsif clk'event and clk='1' thenp_s<=n_s;end if;end process;process(datain,p_s)begincase p_s iswhen s0 =>dataout<='0';if datain='1' thenn_s<=s1;elsen_s<=s0;end if;when s1=>dataout<='0';if datain='1' thenn_s<=s2;elsen_s<=s0;end if;when s2=>dataout<='0';if datain='0' thenn_s<=s3;elsen_s<=s2;end if;when s3=>dataout<='0';if datain='0' thenn_s<=s4;elsen_s<=s1;end if;when s4=>dataout<='0';if datain='1' thenn_s<=s5;elsen_s<=s0;end if;when s5=>dataout<='0';if datain<='0' thenn_s<=s6;elsen_s<=s2;end if;when s6=>dataout<='1';if datain='0' thenn_s<=s0;elsen_s<=s1;end if;end case;end process;end bhv;library ieee;use ieee.std_logic_1164.all;entity sj13 isgeneric(n:integer:=4);port(d,clk,rst:in std_logic;q:out std_logic);end sj13;architecture bhv of sj13 issignal m:std_logic_vector(n-1 downto 0); beginprocess(clk,rst)beginif rst='1' thenm<=(others=>'0');elsif clk'event and clk='1' thenm<=d&m(n-1 downto 1);end if;end process;q<=m(0);end bhv;优先级编码器library ieee;use ieee.std_logic_1164.all;entity mysup isport(a:in std_logic_vector(6 downto 0);b:out std_logic_vector(2 downto 0)); end mysup;architecture bhv of mysup isbeginb<="111" when a(6)='1' else"110" when a(5)='1' else"101" when a(4)='1' else"100" when a(3)='1' else"011" when a(2)='1' else"010" when a(1)='1' else"001" when a(0)='1' else"000" ;end bhv;。