中科大DSP课件6

合集下载

dsp课件

DSP是一种通过数字方式对信号进行处理的学科,它涉及到信号的采集、存储、 变换、滤波、估值、压缩等处理过程,最终的目的是为了满足人们对信号处理的 需求。

DSP的特点

DSP具有高效性

由于DSP采用数字信号处理器 进行信号处理,因此其处理效 率高,能够实现高速实时信号

处理。

DSP具有高精度

数字信号处理器可以实现对信 号的高精度处理,避免了模拟 信号处理中可能出现的误差和 失真。

快速傅里叶变换(FFT)

01

FFT是一种高效计算离散傅里叶变换(DFT)及其逆变换的算法

。

数字滤波器设计

02

数字滤波器是一种用于信号处理的算法,可以实现对信号的滤

波、去噪等功能。

数字信号处理(DSP)算法

03

DSP算法包括多种数字信号处理方法,如频域分析、时域分析

、功率谱分析等。

CHAPTER 04

DSP课件

目 录

• DSP概述 • DSP硬件平台 • DSP软件编程 • DSP在信号处理中的应用 • DSP的优化与扩展 • DSP的发展趋势与未来展望

CHAPTER 01

DSP概述

DSP的定义

数字信号处理(DSP)是一门涉及信号处理、算法设计、系统实现等领域的学科 。它主要研究如何利用数字信号处理器(DSP)对数字信号进行采集、变换、滤 波、估值、压缩等处理,以满足人们在不同领域的需求。

DSP扩展板

内存扩展板

用于扩展DSP的内存容量,提高数据处理能力。

数字IO扩展板

用于扩展DSP的数字输入输出接口,实现与外部设备的通信。

音频视频接口扩展板

用于扩展DSP的音频视频接口,实现音频视频数据的采集和输出。

DSP与其他设备的连接

DSP的特点

DSP具有高效性

由于DSP采用数字信号处理器 进行信号处理,因此其处理效 率高,能够实现高速实时信号

处理。

DSP具有高精度

数字信号处理器可以实现对信 号的高精度处理,避免了模拟 信号处理中可能出现的误差和 失真。

快速傅里叶变换(FFT)

01

FFT是一种高效计算离散傅里叶变换(DFT)及其逆变换的算法

。

数字滤波器设计

02

数字滤波器是一种用于信号处理的算法,可以实现对信号的滤

波、去噪等功能。

数字信号处理(DSP)算法

03

DSP算法包括多种数字信号处理方法,如频域分析、时域分析

、功率谱分析等。

CHAPTER 04

DSP课件

目 录

• DSP概述 • DSP硬件平台 • DSP软件编程 • DSP在信号处理中的应用 • DSP的优化与扩展 • DSP的发展趋势与未来展望

CHAPTER 01

DSP概述

DSP的定义

数字信号处理(DSP)是一门涉及信号处理、算法设计、系统实现等领域的学科 。它主要研究如何利用数字信号处理器(DSP)对数字信号进行采集、变换、滤 波、估值、压缩等处理,以满足人们在不同领域的需求。

DSP扩展板

内存扩展板

用于扩展DSP的内存容量,提高数据处理能力。

数字IO扩展板

用于扩展DSP的数字输入输出接口,实现与外部设备的通信。

音频视频接口扩展板

用于扩展DSP的音频视频接口,实现音频视频数据的采集和输出。

DSP与其他设备的连接

DSP第六章6.3

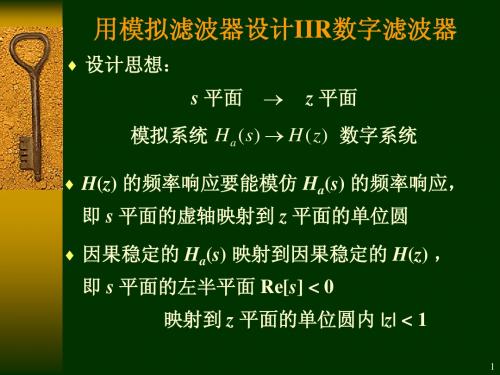

用模拟滤波器设计IIR数字滤波器 数字滤波器 用模拟滤波器设计

♦ 设计思想: 设计思想:

s 平面

→

z 平面

模拟系统 H a ( s ) → H ( z ) 数字系统

♦ H(z) 的频率响应要能模仿 Ha(s) 的频率响应, 的频率响应,

即 s 平面的虚轴映射到 z 平面的单位圆

♦ 因果稳定的 Ha(s) 映射到因果稳定的 H(z) ,

7

3、模拟滤波器的数字化方法 、

H a ( s ) → ha (t ) → ha (nT ) → h(n) → H ( z )

Ak H a (s) = ∑ k =1 s − sk ha (t ) = L [ H a ( s )] = ∑ Ak e u (t )

−1 N

N

sk t

k =1

h(n) = ha (nT ) = ∑ Ak e

∑

4

k

以改变程序中的T值 观察 的大小与频谱混叠失真的关 以改变程序中的 值,观察T的大小与频谱混叠失真的关 系。

17

%例6.3.2 用脉冲响应不变法设计数字滤波器程序: 用脉冲响应不变法设计数字滤波器程序 T=1; ; wp=0.2*pi/T; ws=0.35*pi/T; rp=1; rs=10; 的模拟滤波器指标 %T=1 s的模拟滤波器指标 的模拟滤波器指标 [N, wc]=buttord(wp, ws, rp, rs, 's'); ] %计算相应的模拟滤波器阶数N和3 dB截止频率 截止频率wc 计算相应的模拟滤波器阶数 和 截止频率 [B, A]=butter(N, wc, 's'); ] %计算相应的模拟滤波器系统函数 计算相应的模拟滤波器系统函数 [Bz, Az]=impinvar(B, A); ] %用脉冲响应不变法将模拟滤波器转换成数字滤波器 省略绘图部分。 省略绘图部分。 %T=1s

♦ 设计思想: 设计思想:

s 平面

→

z 平面

模拟系统 H a ( s ) → H ( z ) 数字系统

♦ H(z) 的频率响应要能模仿 Ha(s) 的频率响应, 的频率响应,

即 s 平面的虚轴映射到 z 平面的单位圆

♦ 因果稳定的 Ha(s) 映射到因果稳定的 H(z) ,

7

3、模拟滤波器的数字化方法 、

H a ( s ) → ha (t ) → ha (nT ) → h(n) → H ( z )

Ak H a (s) = ∑ k =1 s − sk ha (t ) = L [ H a ( s )] = ∑ Ak e u (t )

−1 N

N

sk t

k =1

h(n) = ha (nT ) = ∑ Ak e

∑

4

k

以改变程序中的T值 观察 的大小与频谱混叠失真的关 以改变程序中的 值,观察T的大小与频谱混叠失真的关 系。

17

%例6.3.2 用脉冲响应不变法设计数字滤波器程序: 用脉冲响应不变法设计数字滤波器程序 T=1; ; wp=0.2*pi/T; ws=0.35*pi/T; rp=1; rs=10; 的模拟滤波器指标 %T=1 s的模拟滤波器指标 的模拟滤波器指标 [N, wc]=buttord(wp, ws, rp, rs, 's'); ] %计算相应的模拟滤波器阶数N和3 dB截止频率 截止频率wc 计算相应的模拟滤波器阶数 和 截止频率 [B, A]=butter(N, wc, 's'); ] %计算相应的模拟滤波器系统函数 计算相应的模拟滤波器系统函数 [Bz, Az]=impinvar(B, A); ] %用脉冲响应不变法将模拟滤波器转换成数字滤波器 省略绘图部分。 省略绘图部分。 %T=1s

DSP第06讲

地址生成方式:重复操作

以RPTZ为例,说明单指令重复操作: 语法:RPTZ dst, #lk 说明:dst 清零且执行下一条指令 k+1 次 , 其中 常数 k 存放在循环计数器 RC 中。 举例 : RPTZ A, 1023; 重复执行下一条指令 1024 次

STL

A, *AR2+

地址生成方式:重复操作

地址生成方式:中断

'C54x 既支持软件中断 , 也支持硬件中断 : (1) 由程序指令 (INTR、TRAP或 RESET) 要求 的软件中断。 (2) 由外围设备信号要求的硬件中断。这种硬件 中断有两种形式 : ①受外部中断口信号触发的外部硬件中断。 ②受片内外围电路信号触发的内部硬件中断。

地址生成方式:中断

地址生成方式:重复操作

注意事项: 利用块重复操作进行循环,是一种零开 销循环。但由于只有一套重复寄存器, 因此块重复操作不能嵌套。 块重复操作可以响应中断。

地址生成方式:硬件复位

5.硬件复位 复位(RS)是一个不可屏蔽的外部中断, 它可以 在任何时候使‘C54x进入一已知状态。 正常操作是上电后RS引脚应至少保持5个时钟 周期的低电平,以确保数据、地址和控制线的 正确配置。 复位后(RS变高电平),处理器从FF80h处取指 , 并开始执行程序。

地址生成方式:分支转移

条件分支转移操作与无条件分支转移操作类似,但仅当 用户规定的一个或多个条件得到满足时才执行。如果 条件满足,就用分支转移指令的第2个字(分支转移地 址)加载PC,并从这个地址继续执行程序。

地址生成方式:分支转移

条件操作中的“条件”

地址生成方式:分支转移

BC[D]的语法为:BC[D] pmad,cond[,cond,[cond]] 其功能是,如果满足给定的条件 ,pmad 值赋给 PC 实现条件转移。若为延迟方式 , 此时紧跟该指令的 两条单字指令或一条双字指令先被取出执行 , 且不 会影响被测试的条件。若条件不 满足 ,PC 加 2, 条 件满足时程序跳到 pmad 地址处。 程序举例:

DSP第四章6概论

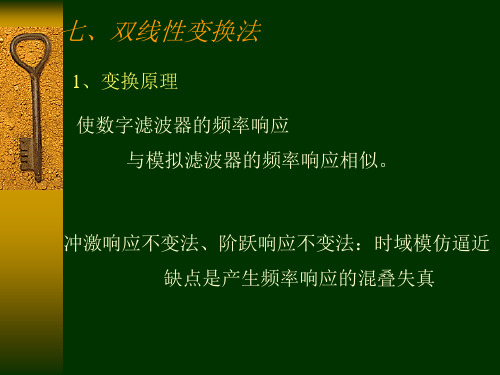

七、双线性变换法

1、变换原理 使数字滤波器的频率响应

与模拟滤波器的频率响应相似。

冲激响应不变法、阶跃响应不变法:时域模仿逼近 缺点是产生频率响应的混叠失真

:[,]

1

:

T

,

T

tg 1T 2

z es1T

tg 1T 2

sin 1T 2

cos 1T 2

j 1T

j 1T

e 2 e 2

2 j j 1T

c tg 1T 2

s

c

1 1

z z

1 1

z cs cs

2、变换常数c的选择

1)低频处有较确切的对应关系: 1

1

c

tg

1T 2

c

1T 2

c 2 T

2)某一特定频率严格相对应: c c

c

c tg

1cT 2

c tg c

2

c

cctg

Байду номын сангаас

c

2

特定频率处频率响应严格相等,可以较准确地 控制截止频率位置

4、优缺点

优点:避免了频率响应的混迭现象

c tg

2 s 平面与 z 平面为单值变换

0 0 0 0

缺点:除了零频率附近, 与 之间严重非线性

1)线性相位模拟滤波器 非线性相位数字滤波器

2)要求模拟滤波器的幅频响应为分段常数型,不 然会产生畸变

分段常数型模拟滤波器 经变换后仍为分段常数 型数字滤波器,但临界 频率点产生畸变

j 1T

e 2 e 2

2

j 1T

j 1T

s1T

s1T

s

j

e2

j 1T

e 2

j 1T

1、变换原理 使数字滤波器的频率响应

与模拟滤波器的频率响应相似。

冲激响应不变法、阶跃响应不变法:时域模仿逼近 缺点是产生频率响应的混叠失真

:[,]

1

:

T

,

T

tg 1T 2

z es1T

tg 1T 2

sin 1T 2

cos 1T 2

j 1T

j 1T

e 2 e 2

2 j j 1T

c tg 1T 2

s

c

1 1

z z

1 1

z cs cs

2、变换常数c的选择

1)低频处有较确切的对应关系: 1

1

c

tg

1T 2

c

1T 2

c 2 T

2)某一特定频率严格相对应: c c

c

c tg

1cT 2

c tg c

2

c

cctg

Байду номын сангаас

c

2

特定频率处频率响应严格相等,可以较准确地 控制截止频率位置

4、优缺点

优点:避免了频率响应的混迭现象

c tg

2 s 平面与 z 平面为单值变换

0 0 0 0

缺点:除了零频率附近, 与 之间严重非线性

1)线性相位模拟滤波器 非线性相位数字滤波器

2)要求模拟滤波器的幅频响应为分段常数型,不 然会产生畸变

分段常数型模拟滤波器 经变换后仍为分段常数 型数字滤波器,但临界 频率点产生畸变

j 1T

e 2 e 2

2

j 1T

j 1T

s1T

s1T

s

j

e2

j 1T

e 2

j 1T

dsp课件

代码调试

在代码实现完成后,进行代码调试,确保程序的正确性和稳定性。

调试与测试结果分析总结

调试过程

在代码调试完成后,进行系统调试,确保各个模块之间的协调和正 常运行。

测试结果分析

对测试结果进行分析,包括性能测试、功能测试等,找出可能存在 的问题和不足。

总结

根据调试和测试结果,对项目进行总结,包括经验教训、改进方向等 ,为后续的项目提供参考和借鉴。

DSP课件

目录

• DSP概述 • DSP硬件结构与工作原理 • DSP软件编程与开发环境 • 典型应用案例分析 • DSP发展趋势与挑战 • 实践项目设计与实现

01 DSP概述

定义与发展

定义

数字信号处理(Digital Signal Processing,简称DSP)是一门涉及多个学科 的交叉学科,主要研究将模拟信号转换为数字信号,并对数字信号进行各种处 理。

通信信号处理应用

总结词

通信信号处理是数字信号处理的另一个重要应用领域,涉及信号的调制、传输和解调等环节。

详细描述

在通信信号处理中,数字信号处理技术可以用于信号的调制、编码、解调和解码等环节,同时还可以 进行信号特征提取、分类和识别等任务。具体的应用包括移动通信、卫星通信、数字电视和雷达信号 处理等。

未来DSP将进一步提高处理速度和效率,满足更 多复杂应用的需求。

更低的功耗

通过不断优化技术,降低DSP的功耗,延长设备 的使用寿命。

更广泛的应用领域

DSP将在更多领域得到应用,如智能家居、自动 驾驶、医疗保健等。

06 实践项目设计与 实现

项目需求分析与设计思路

明确项目目标

01

在开始实践项目之前,需要明确项目的目标,包括要实现的功

在代码实现完成后,进行代码调试,确保程序的正确性和稳定性。

调试与测试结果分析总结

调试过程

在代码调试完成后,进行系统调试,确保各个模块之间的协调和正 常运行。

测试结果分析

对测试结果进行分析,包括性能测试、功能测试等,找出可能存在 的问题和不足。

总结

根据调试和测试结果,对项目进行总结,包括经验教训、改进方向等 ,为后续的项目提供参考和借鉴。

DSP课件

目录

• DSP概述 • DSP硬件结构与工作原理 • DSP软件编程与开发环境 • 典型应用案例分析 • DSP发展趋势与挑战 • 实践项目设计与实现

01 DSP概述

定义与发展

定义

数字信号处理(Digital Signal Processing,简称DSP)是一门涉及多个学科 的交叉学科,主要研究将模拟信号转换为数字信号,并对数字信号进行各种处 理。

通信信号处理应用

总结词

通信信号处理是数字信号处理的另一个重要应用领域,涉及信号的调制、传输和解调等环节。

详细描述

在通信信号处理中,数字信号处理技术可以用于信号的调制、编码、解调和解码等环节,同时还可以 进行信号特征提取、分类和识别等任务。具体的应用包括移动通信、卫星通信、数字电视和雷达信号 处理等。

未来DSP将进一步提高处理速度和效率,满足更 多复杂应用的需求。

更低的功耗

通过不断优化技术,降低DSP的功耗,延长设备 的使用寿命。

更广泛的应用领域

DSP将在更多领域得到应用,如智能家居、自动 驾驶、医疗保健等。

06 实践项目设计与 实现

项目需求分析与设计思路

明确项目目标

01

在开始实践项目之前,需要明确项目的目标,包括要实现的功

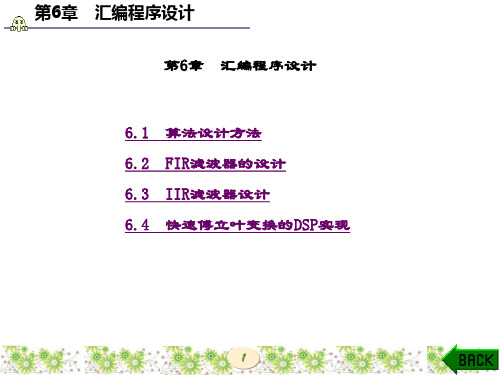

精品课件-DSP技术及应用-第6章

图 6.1 sin函数一个周期的采样值(N=16)

4

第6章 汇编程序设计

表的偏移地址的计算方法是, 将x=[0~2π)弧度变换到0~N -1之间的整数index。

x' N x 2

index=floor(x′)

(6.2)

则y=sin(x)

y=sin_table(index)

(6.3)

查表法速度快, 但表中两点之间的值需用靠近它们的值

32

第6章 汇编程序设计 第1次运算: src=src+h(0)×x(n), 运算后指针未超边界,

ARy→h+1, ARx→x+1; 第2次运算: src=src+h(1)×x(n-1), 运算后指针未超边

界, ARy→h+2, ARx→ x+2; … 第N次运算: src=src+h(N-1)×x[n-(N-1)], 运算后指

9

第6章 汇编程序设计

(6.5)

10

第6章 汇编程序设计 式(6.5)具有迭代性。 若系数用Q15格式表示, 从最里面的

括号开始计算, 均为乘加(减)运算, 可用C54x的汇编专用指令 快速实现。 余弦等其他函数也可用类似的方法处理。

正弦函数也可用迭代公式(6.6)计算, 但不推荐使用, 因 为它容易产生累加误差。

在程序存储器中定义滤波系数h向量, 首地址设为pmad。 在数据存储器定义一个缓冲区用于存放x序列值, 最新的数据存 放在缓冲区顶部, 最“老”的数据放在底部, 将辅助寄存器指 针ARx初始化并指向底部, 如图6.4所示。

22

第6章 汇编程序设计

图 6.4 线性缓冲区法的数据存储

23

第6章 汇编程序设计 设源累加器src初始化为0, pmad指针每计算一次就自动加1,

4

第6章 汇编程序设计

表的偏移地址的计算方法是, 将x=[0~2π)弧度变换到0~N -1之间的整数index。

x' N x 2

index=floor(x′)

(6.2)

则y=sin(x)

y=sin_table(index)

(6.3)

查表法速度快, 但表中两点之间的值需用靠近它们的值

32

第6章 汇编程序设计 第1次运算: src=src+h(0)×x(n), 运算后指针未超边界,

ARy→h+1, ARx→x+1; 第2次运算: src=src+h(1)×x(n-1), 运算后指针未超边

界, ARy→h+2, ARx→ x+2; … 第N次运算: src=src+h(N-1)×x[n-(N-1)], 运算后指

9

第6章 汇编程序设计

(6.5)

10

第6章 汇编程序设计 式(6.5)具有迭代性。 若系数用Q15格式表示, 从最里面的

括号开始计算, 均为乘加(减)运算, 可用C54x的汇编专用指令 快速实现。 余弦等其他函数也可用类似的方法处理。

正弦函数也可用迭代公式(6.6)计算, 但不推荐使用, 因 为它容易产生累加误差。

在程序存储器中定义滤波系数h向量, 首地址设为pmad。 在数据存储器定义一个缓冲区用于存放x序列值, 最新的数据存 放在缓冲区顶部, 最“老”的数据放在底部, 将辅助寄存器指 针ARx初始化并指向底部, 如图6.4所示。

22

第6章 汇编程序设计

图 6.4 线性缓冲区法的数据存储

23

第6章 汇编程序设计 设源累加器src初始化为0, pmad指针每计算一次就自动加1,

中科大操作系统原理与实现课件6_Process_synchronization1

.

.

.

.

.

.

another solution using counting value II

while (true) { /* produce an item and put in nextProduced */ while (count == BUFFER SIZE) ; // do nothing buffer [in] = nextProduced; in = (in + 1) % BUFFER SIZE; count++; }

.

.

.

.

.

.

Bounded-Buffer – Shared-Memory Solution III

Remove() Method

while (true) { while (in == out) ; // do nothing – nothing to consume // remove an item from the buffer item = buffer[out]; out = (out + 1) % BUFFER SIZE; return item; }

操作系统原理与设计

第6章 Processe Synchronization1(进程同步1)

陈香兰

中国科学技术大学计算机学院

2009年10月28日

.

.

.

.

.

.

提纲

Background The Critical-Section Problem Peterson’s Solution Synchronization Hardware TestAndSet Instruction Swap Instruction Semaphores 小结和作业

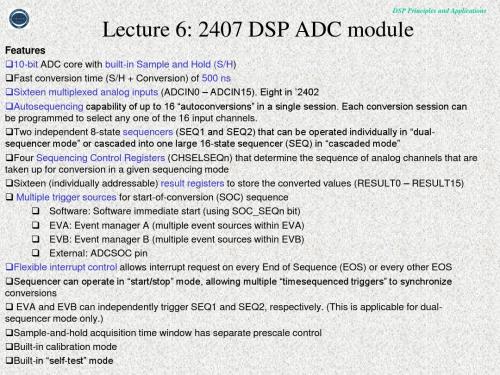

DSP课件 DSP Lecture6

DSP Principles and Applications

Lecture 6: 2407 DSP ADC module

Features 10-bit ADC core with built-in Sample and Hold (S/H) Fast conversion time (S/H + Conversion) of 500 ns Sixteen multiplexed analog inputs (ADCIN0 – ADCIN15). Eight in ’2402 Autosequencing capability of up to 16 ―autoconversions‖ in a single session. Each conversion session can be programmed to select any one of the 16 input channels. Two independent 8-state sequencers (SEQ1 and SEQ2) that can be operated individually in ―dualsequencer mode‖ or cascaded into one large 16-state sequencer (SEQ) in ―cascaded mode‖ Four Sequencing Control Registers (CHSELSEQn) that determine the sequence of analog channels that are taken up for conversion in a given sequencing mode Sixteen (individually addressable) result registers to store the converted values (RESULT0 – RESULT15) Multiple trigger sources for start-of-conversion (SOC) sequence Software: Software immediate start (using SOC_SEQn bit) EVA: Event manager A (multiple event sources within EVA) EVB: Event manager B (multiple event sources within EVB) External: ADCSOC pin Flexible interrupt control allows interrupt request on every End of Sequence (EOS) or every other EOS Sequencer can operate in ―start/stop‖ mode, allowing multiple ―timesequenced triggers‖ to synchronize conversions EVA and EVB can independently trigger SEQ1 and SEQ2, respectively. (This is applicable for dualsequencer mode only.) Sample-and-hold acquisition time window has separate prescale control Built-in calibration mode Built-in ―self-test‖ mode

Lecture 6: 2407 DSP ADC module

Features 10-bit ADC core with built-in Sample and Hold (S/H) Fast conversion time (S/H + Conversion) of 500 ns Sixteen multiplexed analog inputs (ADCIN0 – ADCIN15). Eight in ’2402 Autosequencing capability of up to 16 ―autoconversions‖ in a single session. Each conversion session can be programmed to select any one of the 16 input channels. Two independent 8-state sequencers (SEQ1 and SEQ2) that can be operated individually in ―dualsequencer mode‖ or cascaded into one large 16-state sequencer (SEQ) in ―cascaded mode‖ Four Sequencing Control Registers (CHSELSEQn) that determine the sequence of analog channels that are taken up for conversion in a given sequencing mode Sixteen (individually addressable) result registers to store the converted values (RESULT0 – RESULT15) Multiple trigger sources for start-of-conversion (SOC) sequence Software: Software immediate start (using SOC_SEQn bit) EVA: Event manager A (multiple event sources within EVA) EVB: Event manager B (multiple event sources within EVB) External: ADCSOC pin Flexible interrupt control allows interrupt request on every End of Sequence (EOS) or every other EOS Sequencer can operate in ―start/stop‖ mode, allowing multiple ―timesequenced triggers‖ to synchronize conversions EVA and EVB can independently trigger SEQ1 and SEQ2, respectively. (This is applicable for dualsequencer mode only.) Sample-and-hold acquisition time window has separate prescale control Built-in calibration mode Built-in ―self-test‖ mode

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

中国科学技术大学

10

wei@

6.1

线性相位下FIR滤波器的频率特性

⑷ h(n) 奇对称,N 偶数

H (ω )

6.1

线性相位下FIR滤波器的频率特性

Impulse Response 30 10 20 Type-4 Amplitude Response

1 H (ω ) = ∑ d (n )sin ω n − 2 n =0

w(n)

0.1 0 -0.1

0.5

w(n) 0 20 40 60 n Actual Impulse Response

0 -0.2

0.5

0

20 40 60 n Actual Impulse Response

0

0

20 40 60 n Magnitude Response in dB

-0.4

0

0

20 40 60 n Magnitude Response in dB

N 奇数 h (n ) 镜像反对称 N 偶数

中国科学技术大学 4 wei@

(偶对称) 群延迟均为 τ =

中国科学技术大学

(奇对称)

wei@

6.1

线性相位下FIR滤波器的频率特性

6.1

线性相位下FIR滤波器的频率特性

Impulse Response 10 5 h(n) Hr 0 -5 0 5 n a(n) coefficients 10 20 10 0 -10 -20 Type-1 Amplitude Response

( )

ω ≤ ωc

其他

N 的 FIR, ① 把hd(n)移动α = N − 1 个采样点(设N为奇数)

hd ( n ) =

1 2π

∫ω e

−

c

ωc

dω =

sin ωc n π n

ˆ (n ) ⋅ W (n ) ② 截取N个点,得到 h (n ) = h d R

1

Hamming窗,低通

中国科学技术大学 25 wei@ 中国科学技术大学

Blackman窗,带通

26 wei@

6.2

傅立叶级数法设计FIR滤波器(窗函数法)

Ideal Impulse Response 1 0.6 hd(n) w(n) 0.4 0.2 0 -0.2 0 20 30 40 n Actual Impulse Response 10 0 0 10 20 30 40 n Magnitude Response in dB Kaiser Window

N 2

0

π

2π

ω

5 h(n) Hr 0 5 n d(n) coefficients 10 Imaginary Part 5 d(n) 0 -5 0 5 n 10 1 0.5 0 -0.5 -1 -1 0 Real Part 1 11 10 10 0 -10 0 -5

0

0.5 frequency in pi units

0.5

6.3

频率抽样设计方法

0.6 h(n) 0.4 0.2 0 -0.2 0 10 20 n 30 40 Decibels

23

wei@

6.2

傅立叶级数法设计FIR滤波器(窗函数法)

Ideal Impulse Response 0.3 0.2 hd(n) 1 Hamming W indow

6.2

傅立叶级数法设计FIR滤波器(窗函数法)

Ideal Impulse Response 0.4 0.2 hd(n) 1 Blackman Window

θ

18

θ

− 2π N 2π N

wei@

6.2

傅立叶级数法设计FIR滤波器(窗函数法)

6.2

傅立叶级数法设计FIR滤波器(窗函数法)

① 因为截短,产生过渡带,宽度为窗函数的 主瓣宽度。对矩形窗, ∆ω = 4π

N

θ

H (ω ) H (0 )

肩峰值

② 增加N,可使过渡带变得陡峭,但对一个 固定的窗函数不能改变肩峰值大小。 Gibbs效应。

0 ≤ n ≤ N −1 1 矩形窗 WR (n ) = 其他, 0 sin ω c (n − α ) , n = 0, ..., N −1 即 h(n ) = π (n − α )

中国科学技术大学 16 wei@

ˆ (n ) = h (n − α ) = sin ω c (n − α ) h d d π (n − α )

0.3 0.2 Decibels

0

0.4 Decibels 0 20 40 n 60 0.2

0

h(n)

0.1 0 -0.1

50

h(n)

60

0 -0.2

0

20 n

40

60

0

0.2 0.3 frequency in pi units

1

-0.4

0

0.2 0.35 0.65 0.8 frequency in pi units

6.1

线性相位下FIR滤波器的频率特性

Impulse Response 40 10 Type-2 Amplitude Response

⑵ h(n) 偶对称,N 偶数

H (ω )

1 H (ω ) = ∑ b(n ) cos ω n − 2 n =0

N 2

ω

π

2π

5 h(n) 0 -5 0 5 10 n b(n) coefficients Hr

0

N −1 n = 1, 2, ... , 2

0.5 frequency in pi units

1

10

1 0.5 0 -0.5 -1 0 5 n 10 -1 0 Real Part 1 10

H(ω)关于 0, π, 2π奇对称 必有H(0)=H(π)=H( 2π)=0,带通

中国科学技术大学 9 wei@

6.2

傅立叶级数法设计FIR滤波器(窗函数法)

二、窗函数的选择 过渡带的宽度:与窗函数的主瓣宽度有关 肩峰值大小:与窗函数的旁瓣大小有关

0 -1 0 frequency in pi units M = 51 1

0 -1 0 frequency in pi units M = 101 1

Integrated Amplitude Response

6 FIR数字滤波器设计

6.1

线性相位下FIR滤波器的频率特性

中国科学技术大学

1

wei@

中国科学技术大学

2

wei@

6.1

线性相位下FIR滤波器的频率特性

6.1

线性相位下FIR滤波器的频率特性

在线性相位条件下, h(n ) = ± h( N − 1 − n )

20

0

-20

0

0.5 frequency in pi units

1

10

1 Imaginary Part 0.5 0 -0.5 -1 0 5 n 10 -1 0 Real Part 1 11

N b(n ) = 2h − n 2

N n = 1, 2, ... , 2

5 b(n) 0 -5

1

N N 2, ... , d (n ) = 2h − n n = 1, 2 2 H(ω)关于π偶对称,

必有H(0)=H( 2π)=0,高通

中国科学技术大学 11 wei@

中国科学技术大学

12

wei@

6.2

傅立叶级数法设计FIR滤波器(窗函数法)

常用窗函数 主瓣 矩形 4π/N 三角 8π/N Hanning 8π/N Hamming 8π/N Blackman 12π/N

中国科学技术大学

旁瓣 -13dB -25 -32 -42 -57

24

最小阻带衰减 -21dB -25 -44 -53 -74

wei@

中国科学技术大学

2

−∞ < n < ∞

hd(n)为无限时宽

中国科学技术大学 15 wei@

6.2

傅立叶级数法设计FIR滤波器(窗函数法)

6.2

傅立叶级数法设计FIR滤波器(窗函数法)

hd (n )

n

h(n)的频率响应,频域卷积

H e jω =

( )

1 2π

π ˆ (e θ )W [e (ω θ ) ] dθ ∫πH

⑶ h(n) 奇对称,N 奇数

H (ω )

H (ω ) = ∑ c(n )sin ω n

n =0

h(n)

N −1 2

0

π

2π

ω

0 -5 0 5 n c(n) coefficients 10

5 c(n) 0 -5

Imaginary Part

N −1 c (n ) = 2h − n 2

1

Integrated Amplitude Response

1

选择窗函数的原则: ① 主瓣窄,使过渡带陡峭 ② 旁瓣低,减小肩峰和余振

0 -1 0 frequency in pi units 1

0 -1 0 frequency in pi units 1

中国科学技术大学

21

wei@

− jω n

故, H(ejω)对Hd(ejω)的逼近程度随截取长度而增加

中国科学技术大学 13 wei@ 中国科学技术大学 14 wei@

6.2

傅立叶级数法设计FIR滤波器(窗函数法)

6.2

傅立叶级数法设计FIR滤波器(窗函数法)

理想低通的逼近

1 H d e jω = 0

一、基本设计方法 基于频域特性的解析表达与窗函数 给定Hd(ejω)导出hd(n)

6.2 傅立叶级数法设计FIR滤波器(窗函数法)