On Permutation Operations in Cipher Design

艾顿 bypass 隔离自动转换交换器说明书

Unmatched performance and reliabilityBypass isolation ATS Eaton’s bypass isolation automatic transfer switch (ATS) is designed to provide unmatched performance, reliability and versatility for critical standby power applications. Supervisory intelligence is provided by an ATC-900 or ATC-300+ controller, delivering operational simplicity and field adaptability coupled with diagnostic and troubleshooting capabilities. The bypass isolation ATS design is ideal for those applications where the ability to perform maintenance is required without interrupting power to life safety and other critical loads.Product configuration• Automatic operation—ATS and bypass switch• Open and closed transition• 100–1200 A rating• Two-, three- or four-pole• NEMA T 1, 3R• Up to 600 Vac, three- orfour-wire, 60 Hz or 50/60 Hz• Drawout ATS and fixedbypass switch, facilitatingconcurrent maintenance• Service entranceFeatures and benefitsProven performanceand reliability• Automatic and non-automaticoperation modes are availableto provide multiple methods oftransferring the load betweenpower sources• Manual operation allowsunloaded transfer betweenpower sources for allproduct configurations• UL T 1008 Listed short-circuitand short-time (select catalognumbers only) withstandclosing current ratingsmaximize system reliabilitySimplified installationand integration• Factory-configured powersource and load terminalsfor top/bottom cable ingress• Removable enclosure panelsprovide front and rear accessto cable terminal connections• Seismic certified to OSHPD,CBC, IBC and UBCEnhanced safety• Two-door, compartmentalizedconstruction provides steelbarriers, protecting workers• Integral safety interlocksautomatically open the maincontacts prior to the ATSbeing isolated for test orremoved for serviceImproved serviceability• Two-door design eliminatesthe need to scheduleshutdowns for routine test,inspection or maintenanceof the ATS• Drawout design allows theATS to be disconnectedfrom the electrical bus andisolated in cell for regulartesting as prescribed bycode (NFPA T 70, 99, 110)• Testing of the isolated ATScan be performed whilethe bypass switch is in theautomatic or non-automaticmode of operationDesign featuresDual automatic technology Eaton’s bypass isolationtransfer switch design includes an automatic bypass switch and an ATS housed within a single assembly.Regardless of which power switch is actively distributing power, redundant automatic operation provides for a rapid load transfer and restoration of power to life safety and critical loads, eliminating the need for active supervision by qualified personnel.Segmented construction The ATS and automatic bypass switch are housed in separate compartments, with robust steel walls, that isolate the power switches from each other to facilitate ease of maintenance and worker safety. Eachcompartment includes a door with padlockable handle. This design prevents the possibility of inadvertent contact andunnecessary exposure to power cable terminations and energized electrical control components.Drawout ATS and fixed-mounted bypassService personnel can rack-out and isolate the ATS (with compartment door closed) from the electrical bus for routine test or exercise. A Kirk T -key interlock prevents access to the racking mechanism until the load connection has been transitioned to the automatic bypass switch.Opening the compartment door allows the ATS to be completely drawn out of the cell for inspection or maintenance.Safety interlocks prevent rack-out or rack-in of the ATS from the electrical bus with the main contacts closed. The automatic bypass switch is fixed mounted to the electrical bus and stands ready to initiate an automatic load transfer when the ATS is undergoing maintenance.Multi-tap control power transformerSystem voltage can be fieldconfigured via a multi-tap control power transformer (CPT) with quick-disconnect plugs.T ransition to bypass mode When maintenance or testing of the ATS needs to be performed, qualified personnel can easily and quickly transition the load connection between the ATS and automatic bypass switch using door-mounted operator controls fitted with indication lights. The transition occurs in a make-before-break fashion, ensuring continuous power flow to loads.Multiple operation modes Operation is possible in the following modes:• Automatic • Non-automatic •Manual AIn automatic mode, the transfer switch is self-acting, and atransfer is automatically initiated by the intelligent logic controller.In non-automatic mode(optional), a transfer is initiated by the operator using a door-mounted selector switch.In manual mode, a transfer is initiated by the operator using controls mounted directly on the automatic bypass switch or ATS.Alternatively, a transfer can be initiated remotely via an HMi remote annunciator controller.A Manual operation (unloaded) is provided forall product configurations.for top and bottom cable terminationFixed-mounted automatic Drawout ATS can be isolated for test within compartment orand automatic bypassswitch compartments600–1200 A rating (480 V), NEMA 1 enclosure100–400 A rating (480 V), NEMA 1 enclosureFixed-mounted automatic Drawout ATS can within compartmentor completely removedRemoveable optionpanels allow front access for top and bottom cableterminationDrawout ATS removed for bench level inspection/Automatic bypass switch stands ready to transfer load2EATON Bypass isolation automatic transfer switchesStandard enclosure dimensions and weightsDimensions and weights shown are approximate and subject to change. Reference product outline drawings for the latest information.NEMA 1 enclosure NEMA 3R enclosureNEMA 12/4X enclosureTransferswitch rating Device Dimensions in inches (mm)Normal,emergency, loadNeutral A Weight ABCA Neutral connection size listed is for product configuration with a solid neutral. For product configurations with a switched neutral (four-pole), reference the size listed in theEmergency/Load Connection column.B Three-pole product configuration.C Four-pole product configuration.3EATON Bypass isolation automatic transfer switchesEaton is a registered trademark.All other trademarks are property of their respective owners.Eaton1000 Eaton Boulevard Cleveland, OH 44122United States © 2022 EatonAll Rights Reserved Printed in USAPublication No. PA01602019E / Z25954March 2022Product selectionCatalog numbering systemote: N Some catalog number combinations may not be available. For additional information, please contact your local Eaton sales representative.Bypass isolation ATS schematic diagramUL 1008 withstand and closing current ratings (kA)Ampere Device Up to 480 VUp to 600 V Short-circuit (specific circuit Short-circuit (specific circuit SpecificFollow us on social media to get the latest product and support information.。

aet_精品文档

aetAET: Exploring the Advanced Encryption Technique in Computer SecurityIntroductionIn today's digital world, where sensitive data is constantly being transmitted and stored, ensuring its security is of utmost importance. Cryptography plays a vital role in safeguarding information, and one of the most widely used encryption techniques is the Advanced Encryption Technique (AET). AET is a robust encryption algorithm that secures data by transforming it into an unreadable format. In this document, we will explore the technical aspects of AET and its significance in computer security.1. A Brief Overview of Encryption Techniques1.1 Historical Development of EncryptionEncryption techniques have a long history stretching back thousands of years, with the earliest known examples beingthe use of substitution ciphers by the ancient Greeks and Romans. Over time, encryption methods have become more sophisticated to counter evolving threats.1.2 Basics of EncryptionEncryption involves converting plaintext into ciphertext, which can only be deciphered with the correct key or algorithm. It uses various mathematical operations to scramble the data, making it unintelligible to unauthorized individuals.2. Understanding the Advanced Encryption Technique (AET)2.1 AET BackgroundAET, also known as the Advanced Encryption Standard (AES), is an encryption algorithm adopted by the U.S. government in 2001. It replaced its predecessor, the Data Encryption Standard (DES), and is now considered the gold standard for securing information.2.2 AET FeaturesAET possesses several key features that contribute to its robustness:2.2.1 Symmetric Key AlgorithmAET employs a symmetric key algorithm, meaning the same key is used for both encryption and decryption. This ensures efficiency and simplicity in the encryption process.2.2.2 Block Cipher Operation ModeAET operates as a block cipher, encrypting data in fixed-size blocks. The most common block size used is 128 bits. Larger files are divided into these blocks, which are then individually encrypted.2.2.3 Key Sizes and VariantsAET supports three key sizes: 128 bits, 192 bits, and 256 bits. The larger the key size, the stronger the encryption. Additionally, AET has three variants based on the key size, namely AES-128, AES-192, and AES-256.2.2.4 Substitution-Permutation Network (SPN)AET utilizes a symmetric key permutation network, which combines substitution and permutation operations. This ensures a high level of confusion and diffusion, preventing adversaries from obtaining valuable information.3. AET Mode of Operation3.1 Electronic Codebook (ECB) ModeIn ECB mode, each block of plaintext is encrypted independently with the same key. While simple, this mode is vulnerable to certain attacks because identical plaintext blocks produce identical ciphertext blocks.3.2 Cipher Block Chaining (CBC) ModeCBC mode XORs each plaintext block with the previous ciphertext block before encryption. This introduces randomness and eliminates the vulnerability found in ECB mode. Initialization Vector (IV) is used to ensure the initialblock has no predictable relationship with the subsequent ones.3.3 Counter (CTR) ModeCTR mode transforms a block cipher into a stream cipher. It generates a unique counter value for each block, creating an encryption keystream. The keystream is then XORed with the plaintext to produce the ciphertext.4. Security and Applications of AET4.1 Security of AETAET has gained widespread acceptance due to its robust security. It has undergone extensive academic scrutiny and cryptographic analysis, standing up against various attacks. However, it is crucial to properly implement and use AET to avoid potential vulnerabilities.4.2 Applications of AETAET is extensively employed in various applications, including:- Secure communication systems- File and disk encryption- Virtual Private Networks (VPNs)- Wireless communication protocols- The Internet of Things (IoT) security5. ConclusionAET, with its strong security features and widespread industry adoption, has become an integral part of computer security. It provides a reliable encryption technique for safeguarding sensitive data from unauthorized access and tampering. As technology continues to advance, AET's significance in ensuring information security will remain invaluable. Organizations and individuals must understand and implement AET correctly to maximize its benefits and protect their valuable data.。

第2讲古典密码

要求唯一解的充要条件是gcd( a,26)=1它称之为乘数密 码算法。该算法描述为:

设P=C=Z/(26), K={a ∈Z/(26) |gcd(a,26)=1},

对k=a ∈K,

定义 ek(x)=ax (mod 26)和dk(y)=a-1(y)(mod 26) x,y ∈Z/(26)

例子: a=9,

• 依然保留了字符频率某些统计信息 • 重码分析法:间距是密钥长度整数倍的相同子串有相

同密文,反过来,密文中两个相同的子串对应的密文 相同的可能性很大。

abc def ghi jkl m

000102 030405 060708 091011 12

nop qrs tuv wxy z

131415 161718 192021 222324 25

(1)若q|(a-b),则a≡b mod q (2)(a mod q)=(b mod q)意味a≡b mod q (3) a≡b mod q等价于b≡a mod q (4)若a≡b mod q且b≡c mod q ,则a≡c mod q

• 模算术(Modular Arithmatic) 在mod q的q个剩余类集{0,1,2,…,q-1}

(5 17)K=(15 16) (8 3)K=(2 5) (0 24)K=(10 20)

⎜⎜⎝⎛125 156⎟⎟⎠⎞ = ⎜⎜⎝⎛85 137⎟⎟⎠⎞K

X −1

=⎟⎠⎞−1

=

⎜⎜⎝⎛

9 2

115⎟⎟⎠⎞

因此,

K

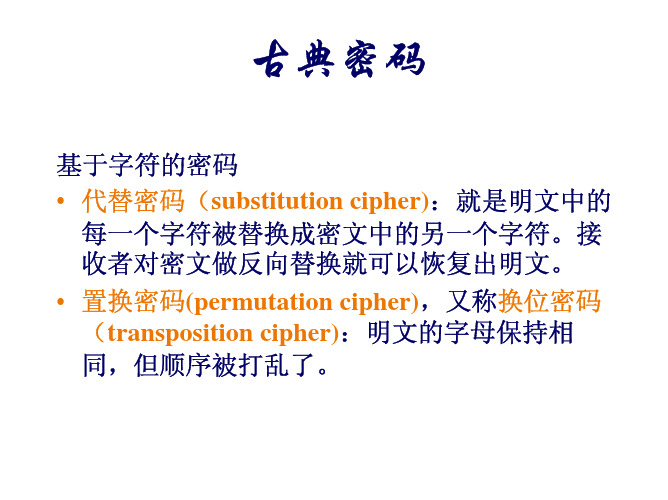

古典密码

基于字符的密码 • 代替密码(substitution cipher):就是明文中的

每一个字符被替换成密文中的另一个字符。接 收者对密文做反向替换就可以恢复出明文。 • 置换密码(permutation cipher),又称换位密码 (transposition cipher):明文的字母保持相 同,但顺序被打乱了。

aes128原理

aes128原理AES128, which stands for Advanced Encryption Standard with a 128-bit key, is a widely-used encryption algorithm to protect sensitive information. It has become the de facto standard for encryption and is used in various applications, including securing data at rest and in transit. AES128 operates on 128-bit block sizes and uses a 128-bit key and is considered secure for most practical applications.AES128 works through a series of mathematical operations, including substitution, permutation, and linear transformation, to transform plaintext into ciphertext. This process ensures that even if an unauthorized party were to intercept the encrypted data, they would not be able to decipher the original message without the correct key. This level of security provided by AES128 makes it an essential component of modern cybersecurity protocols.The strength of AES128 lies in its ability to resist known cryptanalytic attacks when implemented correctly. The algorithm has been thoroughly vetted by cryptographers and has withstood rigorous scrutiny for many years. Furthermore, AES128 has been adopted byvarious government and industry standards organizations, further validating its security and reliability.From a practical standpoint, AES128 is also relatively efficient in terms of computational resources compared to higher bit key lengths such as AES256. This makes it a popular choice for resource-constrained environments where performance is a critical factor. Additionally, AES128 is resistant to attacks like brute force and is resilient against quantum computing threats, making it a reliable choice for long-term security.However, it's essential to note that while AES128 is secure for most use cases, its strength is contingent on the proper management of keys and the overall implementation of the encryption scheme. Weaknesses in key generation, storage, or distribution can undermine the security provided by AES128. Therefore, it's crucial to follow best practices for key management and encryption implementation to maximize the effectiveness of AES128.In conclusion, AES128 is a robust and versatile encryption algorithm that has become an integral part of modern cybersecurity. Its strongsecurity guarantees, efficiency, and widespread adoption make it a compelling choice for safeguarding sensitive information in various applications. As technology continues to evolve, AES128 remains a cornerstone for ensuring data confidentiality and integrity in an increasingly interconnected digital world. AES128的原理与应用是现代信息安全领域的重要组成部分。

可逆操作皇后(FAROQ)密码的对称密码快速算法(IJCNIS-V9-N4-4)

Prof. Abdul Monem S. Rahma

Computer Science Department, University of Technology-Baghdad, Iraq E-mail: Monem.rahma@

Assist. Prof Abdul Mohssen J. Abdul Hossen

I. J. Computer Network and Information Security, 2017, 4, 29-36

PublishΒιβλιοθήκη d Online April 2017 in MECS (/) DOI: 10.5815/ijcnis.2017.04.04

Computer Science Department, University of Technology-Baghdad, Iraq E-mail: Abdulmoohsen53@ Abstract—In this paper, we have proposed a new iterated symmetric cipher, which is designed with Substitution and Permutation Network (SPN) structure and depends on strong mathematical built. It uses a compact algorithm for encryption and decryption processes, which consists of four main stages that roughly similar in its work to the Advance Encryption Standard (AES) stages. Starting by the SubByte operation, ReversibleShiftrows operation, ReversibleMixcolumns operation, and Round key addition. The proposed operations in this cipher have implemented in a straightforward manner relatively in both Encryption/Decryption by an elegant way. These four stages designed to reduce the hardware requirements and to produces high efficiency, which keeps the encryption and decryption process at the same speed in the hardware devices and eliminates the difference of execution times as well as creates a balance in forward and backward operations. The proposed cipher interested with modern design by adopted new algebraic operations and clear mathematical notations to ensure a high level of security. The proposed cipher did not build suddenly or arbitrarily but it acts as a sequence of developments and represents as a long process of design for long time, since several proposed ciphers have been published recently by us that paved the way to its new design, so the designed cipher inherited a good properties from a proven famous algorithms’ features to produce high resistance against al l known attacks and to submit a high performance on many platforms and in a wide range of hardware and software applications. Index Terms—Block Cipher, Symmetric Cipher, Advance Encryption Standard (AES), Substitution and Permutation Network (SPN), Feistel Structure (FS). aspects and encourage on flexible style and intractable manner with robust structure by selection effective factors of cryptographic primitives for the algorithm built [1]. The National Institute of Standards and Technology (NIST) invited the cryptographers, cryptanalysts academic researchers and data security specialists all over the world to apply their own algorithms in order to select one to be a good alternative for the Data Encryption Standard (DES) and triple-DES, because the DES cipher suffered from many problems, represented by short key that not withstand the advance technology through nonresistance against brute force attacks, and the Triple-DES suffered from slowness with three ciphering key [2]. Many ciphers were originally submitted by designers from several countries. Fifteen algorithms were selected as initial selection, then after deep study and hard analysis processes reduced to the best five algorithms as a finalist candidate in the second selection [3]. The five algorithms were MARS, RC6, RIJNDAEL, SERPENT and TWOFISH which are considered non-superior at all. On October 2nd 2000, NIST announced that the Rijndael algorithm is the best one that has got the higher voting scores. The Rijndael cipher appears to be a very good in both hardware and software implementation through a wide range of platforms [4]. Our proposed model called FAROQ cipher similar in its work to the Rijndael cipher from several aspects and can be pictured as a byteoriented structure that iterated for a number of stable rounds. So the first stage is a Subbyte operation that designed by applying another irreducible equation and a new affine transformation that was chosen from the best selection of what we have gotten. They have been given acceptable results in randomness and non-linearity. The second stage is a ReversibleShiftRow that is based on the same rotate operations in forward and backward operations. The third stage is a ReversibleMixcolumn operation is also based on adoption new linear equation with Maximum Distance Separable (MDS) notation that has self-inverse, which uses a single 4*4 MDS matrix over GF(28)[5]. The ReversibleMixcolumns considers a

密码技术期末复习(牛比版)讲解

密码技术期末复习(⽜⽐版)讲解密码技术期末复习(⽜⽐版)⼀、填空:1、Cryptology include the two fields:密码编码学和密码分析学,根据每次处理数据的多少可以把密码算法分为流密码和分组密码其代表算法有:维基尼亚(RC4)和DES算法。

轮转机密钥空间有:26(n 次⽅)。

2、Monoalphabetic Cipher has a total of keys:26!;playfair cipher has 25!keys。

3、IDEA算法的密钥长度为128 bits,RC4算法的密钥长度为8-2048 bits,AES4算法的密钥长度分别为128,192,256。

4、In EDS cipher data block is 64 bit and the input key is 56 bit product 48 sub-key。

5、In Security services,X.800 defines it in 5 major categories:数据机密性,认证,访问控制,数据完整性,⾮否认机制。

6、Consider three aspects of information security:安全攻击、安全机制、安全服务。

7、Security Mechanisms:基于密码技术机制,常规机制。

8、密钥分发中⼼的认证协议(KDC):该协议的缺点是不能防范重放攻击。

9、Type of encryption operations used:置换,代换。

⼆、名词解释:碰撞攻击(Collision):⼀般是对Hash函数⽽⾔,即不同的数据,得到了相同Hash值,就称之为⼀次碰撞。

⽤数学语⾔表⽰,即对函数f(x),找到了x1,x2,且x1不等于x2,有f(x1)=f(x2)。

既然是把任意长度的字符串变成固定长度的字符串,所以,必有⼀个输出串对应⽆穷多个输⼊串,碰撞是必然存在的。

blowfish

blowfishBlowfish: A Powerful Symmetric Block Cipher AlgorithmIntroduction:Blowfish is a symmetric block cipher algorithm designed by Bruce Schneier in 1993. It gained widespread recognition due to its simplicity, security, and efficiency. Blowfish operates on 64-bit blocks and supports key sizes ranging from 32 bits to 448 bits. It has been widely used in various applications such as secure communication protocols, file encryption, and password storage.Structure and Operation:Blowfish employs a Feistel network structure, which is a widely used design in block ciphers. It consists of 16 rounds, each round applying a modified version of the cipher's key to the right half of the data block. The left and right halves are then swapped, and the process is repeated. This iteration process increases Blowfish's security and cryptographic strength.Key Generation:Blowfish uses a key expansion algorithm to generate a series of subkeys before encryption or decryption can take place. The key expansion process involves applying the user's supplied key multiple times using a combination of modular arithmetic operations and the cipher's internal structure. The subkeys generated during this process are then used in each round of encryption or decryption.Feistel Network:The Feistel network structure used in Blowfish is one of the key features contributing to its success. This structure allows for efficient and secure encryption and decryption by dividing the input block into two halves and applying a series of transformation rounds on each half. Blowfish's Feistel network utilizes a combination of substitution and permutation operations, known as the F-function, to provide confusion and diffusion properties.Security:Blowfish is considered a secure algorithm and has stood the test of time against various cryptographic attacks. However, due to advances in technology and computing power, certain vulnerabilities have been identified. One vulnerability is related to weak keys, which refer to a specific set of keys that make Blowfish encryption less secure. To mitigate thisvulnerability, proper key management and the usage of sufficient key sizes are recommended.Applications:Blowfish has found wide application in various domains due to its desirable properties and simplicity. It is commonly used in Virtual Private Networks (VPNs), Secure Shell (SSH) protocols, and secure file transfer protocols (SFTP) to secure data transmission. Furthermore, it has been incorporated into popular cryptographic libraries and frameworks, making it easily accessible for developers looking to implement encryption and decryption functionality.Comparison with AES:Although Blowfish gained significant popularity in the past, it has been largely surpassed by the Advanced Encryption Standard (AES). AES provides a higher level of security and efficiency compared to Blowfish. Nonetheless, Blowfish continues to be used in legacy systems due to its simplicity and compatibility.Conclusion:Blowfish has been a pioneering symmetric block cipher algorithm that has stood the test of time. It offers a goodbalance between security and efficiency, making it suitable for various cryptographic applications. However, with the advent of newer and more secure algorithms, like AES, it is important to assess the specific security requirements and select the most appropriate encryption algorithm for each use case.。

华为S6720-HI系列路由交换机说明书

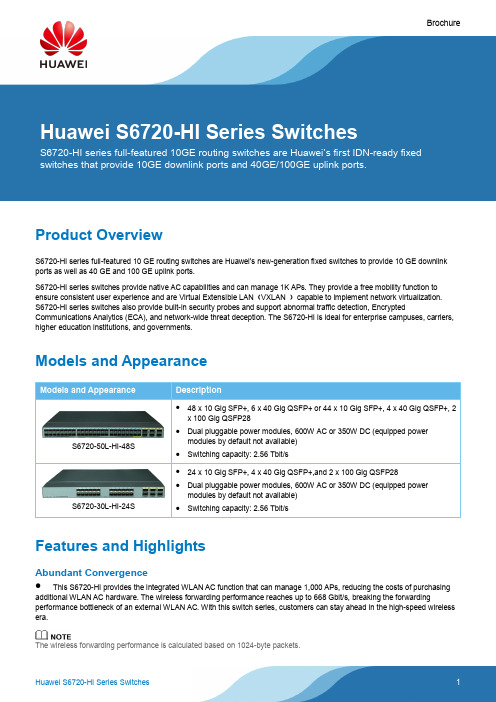

BrochureProduct OverviewS6720-HI series full-featured 10 GE routing switches are Huawei's new-generation fixed switches to provide 10 GE downlink ports as well as 40 GE and 100 GE uplink ports.S6720-HI series switches provide native AC capabilities and can manage 1K APs. They provide a free mobility function to ensure consistent user experience and are Virtual Extensible LAN(VXLAN )capable to implement network virtualization.S6720-HI series switches also provide built-in security probes and support abnormal traffic detection, Encrypted Communications Analytics (ECA), and network-wide threat deception. The S6720-HI is ideal for enterprise campuses, carriers, higher education institutions, and governments.Models and AppearanceModels and AppearanceDescriptionS6720-50L-HI-48S ●48 x 10 Gig SFP+, 6 x 40 Gig QSFP+ or 44 x 10 Gig SFP+, 4 x 40 Gig QSFP+, 2x 100 Gig QSFP28●Dual pluggable power modules, 600W AC or 350W DC (equipped powermodules by default not available)●Switching capacity: 2.56 Tbit/sS6720-30L-HI-24S ●24 x 10 Gig SFP+, 4 x 40 Gig QSFP+,and 2 x 100 Gig QSFP28●Dual pluggable power modules, 600W AC or 350W DC (equipped powermodules by default not available)●Switching capacity: 2.56 Tbit/sFeatures and HighlightsAbundant Convergence●This S6720-HI provides the integrated WLAN AC function that can manage 1,000 APs, reducing the costs of purchasing additional WLAN AC hardware. The wireless forwarding performance reaches up to 668 Gbit/s, breaking the forwarding performance bottleneck of an external WLAN AC. With this switch series, customers can stay ahead in the high-speed wireless era.The wireless forwarding performance is calculated based on 1024-byte packets.●The S6720-HI supports SVF and functions as a parent switch. With this virtualization technology, a physical network with the "Small-sized core and aggregation switches + Access switches + APs" structure can be virtualized into a "super switch", greatly simplifying network management.●The S6720-HI provides excellent QoS capabilities and supports queue scheduling and congestion control algorithms. Additionally, it adopts innovative priority queuing and multi-level scheduling mechanisms to implement fine-grained scheduling of data flows, meeting service quality requirements of different user terminals and services.Providing Granular Network Management●The S6720-HI uses the Packet Conservation Algorithm for Internet (iPCA) technology that alters the traditional method of using simulated traffic for fault location. iPCA technology can monitor network quality for any service flow anywhere, anytime, without extra costs. It can detect temporary service interruptions in a very short time and can identify faulty ports accurately. This cutting-edge fault detection technology turns "extensive management" to "granular management."●The S6720-HI supports Two-Way Active Measurement Protocol (TWAMP) to accurately check any IP link and obtain the entire network's IP performance. This protocol eliminates the need of using a dedicated probe or a proprietary protocol. Flexible Ethernet Networking●In addition to traditional Spanning Tree Protocol (STP), Rapid Spanning Tree Protocol (RSTP), and Multiple Spanning Tree Protocol (MSTP), the S6720-HI supports Huawei-developed Smart Ethernet Protection (SEP) technology and the latest Ethernet Ring Protection Switching (ERPS) standard. SEP is a ring protection protocol specific to the Ethernet link layer, and applies to various ring network topologies, such as open ring topology, closed ring topology, and cascading ring topology. This protocol is reliable, easy to maintain, and implements fast service switching within 50 milliseconds. ERPS is defined in ITU-T G.8032. It implements millisecond-level protection switching based on traditional Ethernet MAC and bridging functions.●The S6720-HI supports Smart Link and Virtual Router Redundancy Protocol (VRRP), which implement backup of uplinks. One S6720-HI switch can connect to multiple aggregation switches through multiple links, significantly improving reliability of access devices.Intelligent Stack (iStack)●The S6720-HI supports the iStack function that combines multiple switches into a logical switch. Member switches in a stack implement redundancy backup to improve device reliability and use inter-device link aggregation to improve link reliability. iStack provides high network scalability. You can increase a stack's ports, bandwidth, and processing capability by simply adding member switches. iStack also simplifies device configuration and management. After a stack is set up, multiple physical switches can be virtualized into one logical device. You can log in to any member switch in the stack to manage all the member switches in it.Cloud-based Management●The Huawei cloud management platform allows users to configure, monitor, and inspect switches on the cloud, reducing on-site deployment and O&M manpower costs and decreasing network OPEX. Huawei switches support both cloud management and on-premise management modes. These two management modes can be flexibly switched as required to achieve smooth evolution while maximizing return on investment (ROI).VXLAN●VXLAN is used to construct a Unified Virtual Fabric (UVF). As such, multiple service networks or tenant networks can be deployed on the same physical network, and service and tenant networks are isolated from each other. This capability truly achieves 'one network for multiple purposes'. The resulting benefits include enabling data transmission of different services or customers, reducing the network construction costs, and improving network resource utilization.●The S6720-HI series switches are VXLAN-capable and allow centralized and distributed VXLAN gateway deployment modes. These switches also support the BGP EVPN protocol for dynamically establishing VXLAN tunnels and can be configured using NETCONF/YANG.Clock Synchronization●The S6720-HI supports the IEEE 1588v2 protocol, which implements low-cost, high-precision, and high-reliability time and clock synchronization. This feature can meet strict requirements of power and transportation industry customers on time and clock synchronization.OPS●Open Programmability System (OPS) is an open programmable system based on the Python language. IT administrators can program the O&M functions of a switch through Python scripts to quickly innovate functions and implement intelligent O&M. Big Data Powered Collaborative Security●Agile switches use NetStream to collect campus network data and then report such data to the Huawei Cybersecurity Intelligence System (CIS). The purposes of doing so are to detect network security threats, display the security posture across the entire network, and enable automated or manual response to security threats. The CIS delivers the security policies to the Agile Controller. The Agile Controller then delivers such policies to agile switches that will handle security events accordingly. All these ensure campus network security.●The S6720-HI supports Encrypted Communication Analytics (ECA). It uses built-in ECA probes to extract characteristics of encrypted streams based on NetStream sampling and Service Awareness (SA), generates metadata, and reports the metadata to Huawei Cybersecurity Intelligence System (CIS). The CIS uses the AI algorithm to train the traffic model and compare characteristics of extracted encrypted traffic to identify malicious traffic. The CIS displays detection results on the GUI, provides threat handling suggestions, and automatically isolates threats with the Agile Controller to ensure campus network security.●The S6720-HI supports deception. It functions as a sensor to detect threats such as IP address scanning and port scanning on a network and lures threat traffic to the honeypot for further checks. The honeypot performs in-depth interaction with the initiator of the threat traffic, records various application-layer attack methods of the initiator, and reports security logs to the CIS. The CIS analyzes security logs. If the CIS determines that the suspicious traffic is an attack, it generates an alarm and provides handling suggestions. After the administrator confirms the alarm, the CIS delivers a policy to the Agile Controller. The Agile Controller delivers the policy to the switch for security event processing, ensuring campus network security. Intelligent O&M●The S6720-HI provides telemetry technology to collect device data in real time and send the data to Huawei campus network analyzer CampusInsight. The CampusInsight analyzes network data based on the intelligent fault identification algorithm, accurately displays the real-time network status, effectively demarcates and locates faults in a timely manner, and identifies network problems that affect user experience, accurately guaranteeing user experience.●The S6720-HI supports a variety of intelligent O&M features for audio and video services, including the enhanced Media Delivery Index (eMDI). With this eDMI function, the S6720-HI can function as a monitored node to periodically conduct statistics and report audio and video service indicators to the CampusInsight platform. In this way, the CampusInsight platform can quickly demarcate audio and video service quality faults based on the results of multiple monitored nodes.Intelligent Upgrade●Switches support the intelligent upgrade feature. Specifically, switches obtain the version upgrade path and download the newest version for upgrade from the Huawei Online Upgrade Platform (HOUP). The entire upgrade process is highly automated and achieves one-click upgrade. In addition, preloading the version is supported, which greatly shortens the upgrade time and service interruption time.●The intelligent upgrade feature greatly simplifies device upgrade operations and makes it possible for the customer to upgrade the version independently. This greatly reduces the customer's maintenance costs. In addition, the upgrade policies on the HOUP platform standardize the upgrade operations, which greatly reduces the risk of upgrade failures. Product SpecificationsFixed ports 48 x 10 Gig SFP+, 6 x 40 Gig QSFP+ or 44 x 10Gig SFP+, 4 x 40 Gig QSFP+, 2 x 100 Gig QSFP2824 x 10 Gig SFP+, 4 x 40 Gig QSFP+, 2 x100 Gig QSFP28MAC 256000(Max) MAC address entriesIEEE 802.1d standards complianceMAC address learning and agingStatic, dynamic, and blackhole MAC address entries Packet filtering based on source MAC addressesVLAN 4K VLANsGuest VLANs and voice VLANsGVRPMUX VLANVLAN assignment based on MAC addresses, protocols, IP subnets, policies, and ports VLAN mappingIP routing Static routes, RIP v1/2, RIPng, OSPF, OSPFv3, IS-IS, IS-ISv6, BGP, BGP4+, ECMP, routing policyInteroperability VLAN-Based Spanning Tree (VBST), working with PVST, PVST+, and RPVST Link-type Negotiation Protocol (LNP), similar to DTPVLAN Central Management Protocol (VCMP), similar to VTPWireless service AP access control, AP domain management, and AP configuration template management Radio management, unified static configuration, and dynamic centralized management WLAN basic services, QoS, security, and user managementCAPWAP, tag/terminal location, and spectrum analysisEthernet loop protection RRPP ring topology and RRPP multi-instanceSmart Link tree topology and Smart Link multi-instance, providing millisecond-level protection switchoverSEPERPS (G.8032)BFD for OSPF, BFD for IS-IS, BFD for VRRP, and BFD for PIMSTP (IEEE 802.1d), RSTP (IEEE 802.1w), and MSTP (IEEE 802.1s)BPDU protection, root protection, and loop protectionMPLS MPLS L3VPNMPLS L2VPN (VPWS/VPLS) MPLS-TEMPLS QoSIPv6 features Neighbor Discover (ND)PMTUIPv6 Ping, IPv6 Tracert, IPv6 TelnetACLs based on source IPv6 addresses, destination IPv6 addresses, Layer 4 ports, or protocol typesMulticast Listener Discovery snooping (MLDv1/v2)IPv6 addresses configured for sub-interfaces, VRRP6, DHCPv6, and L3VPNMulticast IGMP v1/v2/v3 snooping and IGMP fast leaveMulticast forwarding in a VLAN and multicast replication between VLANs Multicast load balancing among member ports of a trunkControllable multicastPort-based multicast traffic statisticsIGMP v1/v2/v3, PIM-SM, PIM-DM, and PIM-SSMMSDPMulticast VPNQoS/ACL Rate limiting in the inbound and outbound directions of a portPacket redirectionPort-based traffic policing and two-rate three-color CARHQoSEight queues on each portDRR, SP, and DRR+SP queue scheduling algorithmsWREDRe-marking of the 802.1p and DSCP fields of packetsPacket filtering at Layer 2 to Layer 4, filtering out invalid frames based on the source MAC address, destination MAC address, source IP address, destination IP address, TCP/UDP source/destination port number, protocol type, and VLAN IDQueue-based rate limiting and shaping on portsSecurity Hierarchical user management and password protectionDoS attack defense, ARP attack defense, and ICMP attack defenseBinding of the IP address, MAC address, port number, and VLAN IDPort isolation, port security, and sticky MACMAC Forced Forwarding (MFF)Blackhole MAC address entriesLimit on the number of learned MAC addressesIEEE 802.1X authentication and limit on the number of users on a portAAA authentication, RADIUS authentication, and HWTACACS authenticationNACSSH V2.0HTTPSCPU protectionBlacklist and whitelistAttack source tracing and punishment for IPv6 packets such as ND, DHCPv6, and MLD packets IPSec for management packet encryptionReliability LACPE-TrunkEthernet OAM (IEEE 802.3ah and IEEE 802.1ag)ITU-Y.1731DLDPLLDPBFD for BGP, BFD for IS-IS, BFD for OSPF, BFD for static routesVXLAN VXLAN functions, VXLAN L2 and L3 gateways, BGP EVPN VXLAN configuration using NETCONF/YANGSVF Acting as the parent node to vertically virtualize downlink switches and APs as one device for managementTwo-layer client architectureASs can be independently configured. Services not supported by templates can be configured on the parent node.Third-party devices allowed between SVF parent and clientsiPCA Marking service packets to obtain the packet loss ratio and number of lost packets in real time Measurement of the number of lost packets and packet loss ratio on networks and devicesManagement and maintenance Cloud-based managementVirtual cable testSNMP v1/v2c/v3RMONWeb-based NMSSystem logs and alarms of different severities GVRPMUX VLAN802.3az Energy Efficient Ethernet (EEE) NetStreamDying gasp upon power-offDimensions (W x D xH)442 mm x 420 mm x 43.6 mm 442 mm x 420 mm x 43.6 mm Height 1 U 1 UInput voltage AC:●Rated AC voltage: 100V to 240V AC; 50/60 Hz ●Max. AC voltage: 90V to 264V AC; 47–63 Hz DC:●Rated DC power: –48V to 60V DC●Max. DC voltage: –38.4V to 72V DCMaximum powerconsumption279W 232WPower consumption(30% traffic load)194W 138WOperating temperature ●0–1800 m altitude: 0°C to 45°C●1800–5000 m altitude: The operating temperature reduces by 1°C every time the altitudeincreases by 220 m.Relative humidity 5% to 95% (non-condensing)Heat dissipation Heat dissipation with fan, intelligent fan speed adjustmentNetworking and ApplicationsHuawei S6720-HI is the first fixed agile switch with 10GE downlink and 40GE/100GE uplink ports. It supports in-depth wired and wireless convergence and unified management on devices, users, and services. The S6720-HI can be used as the core device in an enterprise branch network or a small- or middle-sized campus network, or as the aggregation device in a large-sized campus network. The switch helps achieve a manageable and highly reliable enterprise campus network with scalable services.Ordering InformationThe following table lists ordering information of the S6720-HI series switches.Model Product DescriptionS6720-50L-HI-48S S6720-50L-HI-48S (48 x 10 Gig SFP+, 6 x 40 Gig QSFP+ or 44 x 10 Gig SFP+, 4 x 40 Gig QSFP+, 2 x 100 Gig QSFP28; without power module)S6720-30L-HI-24S S6720-30L-HI-24S (24 x 10 Gig SFP+, 4 x 40 Gig QSFP+, 2 x 100 Gig QSFP28; without power module)PAC-600WA-B 600W AC power modulePDC-350WA-B 350W DC power moduleMore InformationFor more information about Huawei Campus Switches, visit or contact us in the following ways:●Global service hotline: /en/service-hotline●Logging in to the Huawei Enterprise technical support website: /enterprise/●Sending an email to the customer service mailbox: ********************Copyright © Huawei Technologies Co., Ltd. 2019. All rights reserved.No part of this document may be reproduced or transmitted in any form or by any means without prior writtenconsent of Huawei Technologies Co., Ltd.Trademarks and Permissionsand other Huawei trademarks are trademarks of Huawei Technologies Co., Ltd.All other trademarks and trade names mentioned in this document are the property of their respective holders.NoticeThe purchased products, services and features are stipulated by the contract made between Huawei and thecustomer. All or part of the products, services and features described in this document may not be within thepurchase scope or the usage scope. Unless otherwise specified in the contract, all statements, information, andrecommendations in this document are provided "AS IS" without warranties, guarantees or representations ofany kind, either express or implied.The information in this document is subject to change without notice. Every effort has been made in thepreparation of this document to ensure accuracy of the contents, but all statements, information, andrecommendations in this document do not constitute a warranty of any kind, express or implied. Huawei Technologies Co., Ltd. Address:Huawei Industrial Base Bantian, Longgang Shenzhen 518129 People's Republic of China Website:。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

On Permutation Operations in Cipher Design∗Ruby B.Lee,Z.J.Shi and Y.L.YinPrinceton University Department of Electrical Engineering B-218,Engineering QuadranglePrinceton,NJ08544,U.S.A. Email:{rblee,zshi,yyin}@Ronald L.RivestM.I.T.CSAIL545Technology SquareCambridge,MA02139,U.S.A.Email:rivest@M.J.B.RobshawInformation Security GroupRoyal HollowayUniversity of LondonEgham,Surrey,TW200EX,U.K.Email:m.robshaw@AbstractNew and emerging applications can change the mix of operations commonly used within computer architectures. It is sometimes surprising when instruction-set architecture (ISA)innovations intended for one purpose are used for other(initially unintended)purposes.This paper consid-ers recent proposals for the processor support of families of bit-level permutations.From a processor architecture point of view,the ability to support very fast bit-level per-mutations may be viewed as a further validation of the ba-sic word-orientation of processors,and their ability to sup-port next-generation secure multimedia processing.How-ever,bitwise permutations are also fundamental operations in many cryptographic primitives and we discuss the suit-ability of these new operations for cryptographic purposes.1.IntroductionTo support new user requirements such as digital mul-timedia processing and secure information processing,the basic operations supported within new generation proces-sors might evolve.For a general-purpose microprocessor,it is desirable that any added instructions have multiple uses, rather than being specific to only one algorithm or to one application.Since secure communications and networking have become critical features of many applications,it would seem to be advantageous for the architectural and crypto-graphic communities to explore the following questions. Are there instruction-set architecture(ISA)innovations that may occur in a widespread way that might also be used ben-eficially in the design of cryptographic algorithms?Alter-natively,are there desirable instructions,perhaps motivated by the design of cryptographic algorithms,that might also be useful for other emerging applications?To begin explor-ing these questions,this paper examines recently-proposed ∗This work was supported in part by NSF CCR-0105677.bit permutation operations from the perspective of cipher design and cryptanalysis.In addition to studying the cryp-tographic properties of such permutation operations in iso-lation,we consider their role in the design of new ciphers.The contributions of this paper are as follows.We exam-ine the cryptographic properties of bit-level permutations in the construction of new ciphers or in strengthening ex-isting ciphers.In particular,we study the cryptographic properties of the group operation GRP[13,23],as well as OMFLIP[13,27]which were recently identified for possi-ble inclusion in future processor architectures.We consider the properties of GRP and OMFLIP and consider how their inclusion within a cryptographic design might change the properties of the scheme.As a detailed example,we con-sider the implications of incorporating the GRP operation into a block cipher and discuss some of the issues that arise. Provided care is taken,it may be possible for the support of new operations to lead to new designs offering higher performance and reduced energy consumption;something which would be particularly important for constrained envi-ronments like hand-held devices.In Section2,we motivate the study of permutation operations from both an architec-tural and cryptographic viewpoint.In Section3,we pro-vide our design goals and detailed definitions of bit permu-tation operations.We also give results on the implementa-tion complexity of GRP.In Section5,we analyze the cryp-tographic properties of GRP and,as an example,in Sec-tion6.2we explore how one might use GRP in a variant of the block cipher RC5[20].Section7concludes the paper.2.Motivation for new permutation operationsBit-level permutation operations are very important from both an architectural and cryptographic point of view.Architecturally,the ability to support very fast bit-level permutations may be the next step in the evolution of word-oriented processors to support new multimedia and secure information processing workloads.Bit level computationis used in Huffman encoding and decoding,for example, and general-purpose processors are optimized for word-oriented computation.Hence,their instruction set architec-ture(ISA)provides limited support for the manipulation of data items smaller than a word.Currently,only simple bit-level operations like logical operations and shifts are im-plemented in microprocessors.For multimedia processing, processor architectures have already incorporated the con-cept of subword parallelism[11,12]where subwords are typically8-bit pixels or16-bit audio samples.A subword-parallel instruction performs the same operation on multi-ple pieces of data(subwords)packed in one or more reg-isters[11].Subword-parallel arithmetic operations can ef-ficiently exploit the data parallelism in processing images, video,graphics and audio.Subword-parallel instructions—first introduced to accelerate multimedia in PA-RISC mi-croprocessors[11,12]—have now been added to all mi-croprocessors[6,8,11,12,18,19].These ISA additions have swept the microprocessor industry in a matter offive years,demonstrating that new architectural features will be added to processors if they provide significant performance or other advantages at a very low cost.Subword permuta-tion operations are often necessary to rearrange subwords into proper positions in registers so that subsequent oper-ations can be applied to all subwords in parallel.As we decrease the size of the subword,we increase the difficulty of achieving all possible permutations since the number of items to be permuted increases significantly.Nevertheless, recent work[13,23,26,27]has examined architectural so-lutions that can achieve any arbitrary permutation of both single-bit and multi-bit subwords packed in a register.Cryptographically,bit-level operations are useful in the design of many algorithms,particularly block ciphers, stream ciphers,and hash functions.The design of the block cipher DES[16]is an important landmark in this regard. The security of many of these algorithms relies on what Shannon termed confusion and diffusion[22]which are typ-ically attained by a judicious combination of simple opera-tions.Bit-level permutations naturally provide certain ef-fects which are not easily obtained through word-level op-erations.However,bit-level permutations tend to be slow on current programmable processors,since they have to be emulated using other instructions.While all processors im-plement add,subtract,logical,memory load and shift oper-ations,the only bit-level permutations that might be rou-tinely supported in microprocessors are bitwise rotations which form a very small subset of all possible bit-level permutations.Some processors supportfixed bitwise ro-tations where the amount of rotation is specified at compile time;even fewer processors support data-dependent rota-tions(DDR)where the rotation amount is only available at execution time.DES[16]uses bit-level permutations which are very fast in special-purpose hardware,but inherently slow in software.While the fewfixed permutations in DES can be sped up using table lookup techniques in software, it is not feasible to do this for all possible data-dependent permutations.In[27]the use of OMFLIP to speed up the performance offixed permutations within DES is explored.More recent proposals for hash functions and encryp-tion functions—including the new AES[17]—have demon-strated a move away from bit-level operations and toward a mix of word-oriented operations such as arithmetic and log-ical operations,as well as some form of table lookup accom-plished with memory load instructions.Much of this,how-ever,might be due to the currently poor support for bit-level permutations;currently no processors implement more gen-eral purpose bit-wise permutation instructions.Neverthe-less,the role of bit-wise permutations remains fundamental and it is interesting to consider whether increased support for bit-level permutation operations might not encourage their use in new cipher designs.Finally,another interesting application of bit-level per-mutations is in the obfuscation of data[3]within tamper-resistant chips.The use of keyed bit-level permutations can provide a mechanism to enhance the resistance of such hardware deployments to so-called“probing attacks”.It would be interesting to consider the applications of the tech-niques we discuss in this paper to this particular problem.3.Design goals for new permutation operationsA permutation operation for our architectural and cryp-tographic needs should ideally satisfy the following goals:•Goal1:Be general-purpose andflexible.The new per-mutation operation should be general-purpose,rather than specific to a given algorithm.For example,the permutation operation might have uses in applications as diverse as multimedia applications,sorting applica-tions,and cryptography.•Goal2:Be easy to implement.The new permuta-tion operation should be easy to implement in a va-riety of processors,from high-performance micropro-cessors down to the simplest processors suitable for small information appliances and even smart cards.Since many of these processors have simple architec-tures,the new operation should ideally require no more than two source registers,and write to one destination register upon completion of execution.Ideally,the la-tency through the functional unit should allow the op-eration to execute in a single cycle.On the other hand, if the direct hardware support for the operation is not available,other instructions should be able to emulate the operation efficiently.•Goal3:Have good cryptographic properties.The new permutation operation should have good cryptographicproperties,and be resistant to common cryptanalytic attacks as well as not opening new weaknesses.To help judge how successful such new operations might be,we will use the data-dependent rotation(DDR)as ameans for comparison.This operation has been used in the block cipher RC5[20]and it has been widely studied from a cryptographic perspective.Like all the permutations con-sidered in this paper,the action of DDR is notfixed.Instead, the bits of a control register are used to specify the permu-tation to be applied to the bits in the data register.One po-tential weakness of DDR is that only the lower lg(w)bits of the w-bit control register are used to effect the permutation,where lg(w)is the logarithm to the base two of w.For con-venience,lg(w)is used to denote log2(w)in this paper.The potential weakness of DDR has been used to mount certaintheoretical attacks on RC5and so it seems that new permu-tation operations with more control bits might potentiallybe cryptographically useful.4.Permutation Operations:GRP and OMFLIPThe general form of a permutation operation will bewritten as Z=X•Y where the bits(or subwords)of X are permuted according to the value of bits(or sub-words)of Y.The data-dependent rotation(DDR)typi-cally denoted as Z=X<<<Y takes two operands X and Y,generating a result Z where all are w-bit words. The word X is rotated left by the amount specified in the lower lg(w)bits of Y.Several new permutation instruc-tions such as PPERM[13],GRP[13,23],CROSS[13], OMFLIP[13,27],and BFLY[26]have been proposed for arbitrary bit-level permutations.However,we will restrict our attention to GRP and OMFLIP in this paper.4.1.Definition of GRPThe GRP operation will be written as Z=X Y where the bits in X are divided into two groups depending on whether the corresponding bit in Y is0or1.The two groups of bits are then placed next to each other in Z.The bits with a control bit of0are placed at the left end;the bits with a control bit of1at the right end.Fig.1shows an example of an8-bit GRP operation.Since the control bits of x0,x2,x5, x6are0,these four bits are placed at the left end in Z.The bits x1,x3,x4,x7are placed at the right since their control bit has the value1.If the GRP operation is used in a cryptographic algo-rithm,the inverse operation,UNGRP for ungroup,may be needed for decryption.Here we give programmatic definitions of GRP and UNGRP.Let X=x w−1...x0, Y=y w−1...y0,and Z=X Y=z w−1...z0be w-bit words.XYZ b c f h a d e ga b c d e f g h10011010z©©r rr r r jr rr r r jAdd$$$$$$$$WFigure1.An8-bit GRP operation GRPj=0;for(i=0;i<w;i=i+1)if(y i=1){z j=x i;j=j+1;}for(i=0;i<w;i=i+1)if(y i=0){z j=x i;j=j+1;}UNGRPj=0;for(i=0;i<w;i=i+1)if(y i=1){z i=x j;j=j+1;}for(i=0;i<w;i=i+1)if(y i=0){z i=x j;j=j+1;}4.2.Definition of OMFLIPThe OMFLIP operation will be written as Z=X (·,·)Y. It is based on concatenating an omega stage with a flip stage which we will now describe.In an omega or a flip stage,w input bits are divided into w/2pairs.The two bits in a pair are mapped to two output positions,the destina-tion order being determined by a single control bit.Conse-quently w/2control bits are needed for w/2data pairs in an omega or a flip stage.At the input of an omega stage,bits i and(i+w/2), 0≤i<w/2,form a pair and they are mapped to the two bit positions2i and(2i+1).At the input of a flip stage, bits2i and(2i+1),0≤i<w/2,form a pair which is mapped to positions i and i+w/2.Clearly,a flip stage can be viewed as the inverse of an omega stage.The OMFLIP operation Z=X (a0,a1)Y uses two stages in an omega-flip network to permute the data bits X with Y specifying the control bits for the two stages.The subscript(a 0,a 1)represents a two-bit encoding (with omega being represented by 0and flip by 1)that specifies which stages are used;they could be (omega ,omega ),(flip ,flip ),(omega ,flip ),or (flip ,omega ).Fig.2shows an 16-bit omega-flip network that has two omega stages and two flip stages.It can be used to perform 16-bit OMFLIP operations.A 16-bit OMFLIP operation can use any two stages in the network to permute bits and pass through the other two.Actually,each stage in such a network has pass-through paths,which allow bits to go through a stage with-out any position changes.But the pass-through paths are not shown in the figure for illustrating better the paths that are essential to an omega or a flip stage.The programmatic definition of OMFLIP is given be-low.Let X =x w −1...x 0,Y =y w −1...y 0,and Z =X (a 0,a 1)Y =z w −1...z 0be w -bit words.OMFLIP (a 0,a 1)j =0;for (i =0;i <2;i =i +1)if (a i =0){for (j =0;j <w 2;j =j +1)z 2j =x j ;z 2j +1=x j +w 2;if (y j +iw 2=1)swap(z 2j ,z 2j +1);}else {for (j =0;j <w 2;j =j +1)z j =x 2j +1;z j +w/2=x 2j +1;if (y j +iw 2=1)swap(z j ,z j +w 2);}4.3.Basic properties of GRP and OMFLIPGRP can be used to simulate any bit permutation of a w -bit word with at most lg(w )steps [23].It can also be used for multi-bit subword permutations and is useful for multi-media processing.It can achieve any one of m !permuta-tions of m subwords in at most lg(m )instructions,where m is the number of subwords.Here m =w/k ,where w is the number of bits in a word,and k is the number of bits in a multi-bit subword.In addition,GRP is very useful for accelerating sorting algorithms,and can achieve a speedup of 10or more when sorting a small set of integers [24].OMFLIP has similar properties to GRP in terms of per-forming permutations of bits or multi-bit subwords that are stored in one word (or register).It can perform an arbi-trary permutation of w bits with at most lg(w )steps and an arbitrary permutation of m multi-bit subwords with at most lg(m )steps.Any one of the w !permutations can beOUTPUTomegaflipflipomegaFigure 2.A 16-bit omega-flip networkachieved by simulating a full omega-flip network,whichconsists of lg(w )omega stages followed by lg(w )flip stages.Since an OMFLIP instruction performs the opera-tion of two of these stages,a sequence of lg(w )OMFLIP instructions can achieve any arbitrary w -bit permutations.Both GRP and OMFLIP are general-purpose permuta-tion primitives useful in multimedia and security applica-tions;hence,they satisfy Goal 1.4.4.Implementation of GRP and OMFLIPBoth GRP and OMFLIP are easy to add to a typical pro-cessor since each requires reading only two source registers and writing one result register.This fits typical processor datapaths,instruction formats,and pipeline organizations.Other implementation issues like execution latency and size of the functional unit required are discussed below.A hardware implementation of GRP given in [25]sug-gests that it takes slightly longer than a typical ALU (Arith-metic Logical Unit)latency.Since the latter is often used to determine the cycle time of a processor,this means that a GRP operation will execute in one or two cycles,depend-ing on the aggressiveness of the processor cycle time in the design with respect to the latency of the ALU.When imple-mented in a processor,the GRP functional unit may also be used to perform some other operations such as DDR.In a processor design where a GRP operation takes two cycles to complete,the GRP functional unit can easily be pipelined,if desired,so that a new GRP instruction can start every cycle.While the functional unit implementing a GRP oper-ation is more complicated than an ALU,it is simpler than that needed for a MULTIPLY operation.On some proces-sors such as Itanium [5],the multiplications of large inte-gers are intended to be performed withfloating-point units, byfirst transferring the operands tofloating-point registers, performing the multiplication,and transfer the result back. Hence,the cost of the MULTIPLY operation becomes even higher when it is mixed with other operations that are per-formed with integer units.Furthermore,a GRP operation takes only1-2cycles of execution latency compared to the 3-7cycles needed by a MULTIPLY operation.A hardware implementation of an OMFLIP instruction is much simpler than for GRP,and also simpler than for an ALU.An OMFLIP instruction will have a latency no longer than a typical ALU,and hence it can execute in a single cycle.Since the number of stages in an OMFLIP functional unit isfixed no matter how big w is,the size and latency advantages of the OMFLIP functional unit over the GRP functional unit increases as the number of bits,w,to be permuted increases.OMFLIP definitely satisfies Goal2in terms of ease of implementation.GRP’s implementation complexity is higher,but it has a latency much smaller than that of a MULTIPLY operation,with a smaller functional unit size. Indeed,GRP may be a simpler alternative than MULTIPLY for cryptography purposes.Hence,Goal2is reasonably well satisfied for both GRP and OMFLIP.In the next sec-tion,we show that GRP has better cryptographic properties than OMFLIP.5.Cryptographic properties of permutationsWe now discuss the cryptographic properties of permuta-tion operations in the context of cipher design and analysis, and the satisfaction of Goal3.Wefirst give a brief overview of cryptographic algorithms and the role of bitwise permu-tations as a contribution to their security.It is typical to classify cryptographic algorithms accord-ing to the way they use key information[15].Public key al-gorithms use two keys;one is kept secret and the other—as the name implies—is made public.Such algorithms are not our concern here.Other algorithms require that the two par-ticipants in a cryptographic exchange share the same secret key.Encryption is provided by block ciphers and stream ciphers and authentication based on secret key techniques can be provided by message authentication codes.Finally, a class of algorithms known as hash functions are entirely keyless.While public key algorithms are based on difficult prob-lems in number theory and have a rich mathematical struc-ture,secret-key algorithms and hash functions tend to be more ad hoc in design.The process to establish the new AES[17]was notable for the wealth of new design and analysis techniques that were discussed at great length.The fields of stream ciphers,message authentication codes,and hash functions have not had comparable exposure,though many of the same design principles can often be applied in one way or another.Indeed,the basic ideas of confusion and diffusion[22] that are so prominent in block cipher designs also appear elsewhere.Confusion might be viewed as a process by which small amounts of complex interaction are introduced locally,while diffusion can be viewed as the process by which this complexity is spread from being solely a local phenomenon.By alternating primitive functions that pro-vide confusion and diffusion,the hope is that thefinal algo-rithm will exhibit globally complex,and cryptographically strong,behavior.The common way to provide the diffusive elements of this process is to use a bitwise permutation,and the success of a cipher design can depend in a fundamental way on the properties of the permutation that is used.5.1.GRP and OMFLIP as cryptographic primitivesThere are many different ways of using a bitwise per-mutation in a cipher design.Frequently the permutation is fixed,as is the case in DES[16],and so it is straightforward to account for the behavior of the permutation in analysis. However,some recent designs have introduced the possi-bility of using a permutation that is variable and depends on the value of the data being encrypted.We have already mentioned one good example of this,the data-dependent rotation DDR.The operations we consider here,GRP and OMFLIP,might be viewed as being complementary to the DDR operation.With this in mind,we consider the role of these permutations in relation to some specific attacks on block ciphers.More particularly,we will consider their effect on two important kinds of block cipher attacks;dif-ferential cryptanalysis[1]and linear cryptanalysis[14]. 5.1.1Differential and linear cryptanalysisFor differential cryptanalysis,the basic idea is that two plaintexts are chosen with a certain difference between them;the difference is typically measured by exclusive-or but for some ciphers an alternative measure can be more useful.These two plaintexts are enciphered to give two ci-phertexts,and it is hoped that the difference between the outputs has a specific value with a better-than-average prob-ability.Depending on the cipher and the analysis,the be-havior of such differences and their evolution can be useful in deriving certain bits of the key.For linear cryptanaly-sis,the basic idea is tofind relations among certain bits of plaintext,ciphertext,and the key that hold with a probabil-ity p=1/2(i.e.,there is a bias of|p−1/2|>0).Such a relation is called a linear approximation.As in differential cryptanalysis,we seek to exploit such non-ideal behavior and it may be possible to identify linear approximations that reveal information about the key.An important feature that determines the possible suc-cess of differential and linear cryptanalysis is the speed with which the complexity of a difference or linear approxima-tion increases as we try and keep track of such close re-lations during the encryption process.For a good block cipher,the differences between related texts and the rela-tion between bits of the same text should both become very complicated very quickly so that by the time the encryption process is concluded any statistical variations are smoothed out and there is no unusual behavior left for the cryptan-alyst to exploit.The process by which this is achieved is often loosely referred to as the avalanche of change and the spread of change and the spread of effect and influence is often influenced by the role of permutations within the ci-pher design.5.1.2Differential and linear propertiesHere we consider the differential and linear properties of GRP,OMFLIP and DDR.There are many differential char-acteristics and linear approximations for a given permuta-tion operation,each holding with different associated prob-abilities.The most useful ones are typically those that are both simple and which hold with relatively large probabili-ties.The properties on DDR are mostly results that can be found in[4,9],while the properties for GRP and OMFLIP are new results.The results in this paper are necessarily preliminary results and concentrate on some of the simplest forms of cryptanalysis.In Section5.3we take account of some more advanced considerations.For differential cryptanalysis,we need to consider a pair of inputs and their corresponding output.Specifically,for i=1,2,let Z i=X i•Y i.We define the differences in the input and output to be∆X=X1⊕X2,and∆Y=Y1⊕Y2,and∆Z=Z1⊕Z2.A differential character-istic of the permutation operation Z=X•Y is a triplet (∆X,∆Y)→∆Z,together with the probability p that the given triplet holds when the inputs are chosen at random. We let e s denote the w-bit word which is zero except for a single one in bit position s.In our preliminary investiga-tion,we will restrict our attention to single-bit differences and approximations.The following differential characteristics of a permuta-tion operation are often useful(we use∆to denote a gen-eral difference which may be zero).The aim is to keep track of any changes induced during encryption and to keep the evolution of differences as simple as possible.(A)(e s,0)→e t(B)(0,e t)→∆(C)(e s,e t)→∆Since Z is a permutation of the bits in X,we know that type (A)characteristics exist and their probabilities are easy toTable 1.The propagation of differencesacross DDR,GRP,and OMFLIP.Type(A)Type(B)Type(C)(e s,0)→e t(0,e t)→∆(e s,e t)→∆p=1wH WT(∆)=0E(H WT(∆))=1 DDR∀s,t lg(w)≤t lg(w)≤tE(H WT(∆))=w2E(H WT(∆))=w20≤t≤lg(w)−10≤t≤lg(w)−1 p≤E(H WT(∆))=w4E(H WT(∆))=w4 GRP(12+12w)∀s,t∀s,t∀s,tOMFLIP p≤14H WT(∆)≤2H WT(∆)≤3∀s,t∀s,t∀s,tcompute.The more interesting characteristics are type(B) and type(C)which depend on the input difference in the control bits Y.For these,we will compare the diffusion effect by computing the expected Hamming weight of the output difference∆Z.The three types of characteristics of different permutation operations and their associated prob-abilities or Hamming weights are shown in Table1.There, E(H WT(∆)denotes the expected value of H WT(∆),the Hamming weight of∆,when inputs are chosen at random.In linear cryptanalysis,we aim to exploit a linear relation among certain bits of the inputs and outputs.Specifically, ifΓand X are two binary vectors of length w,then their inner product,denoted byΓ·X,is the parity of the bits in X specified by the non-zero entries inΓ.A linear ap-proximation of the permutation Z=X•Y is therefore a triplet(ΓX,ΓY,ΓZ)together with the probability p that the equation(ΓX·X)⊕(ΓY·Y)=(ΓZ·Z)holds on random in-puts.The bias b of the linear approximation is defined to be |p−1/2|.For example,(ΓX,ΓY,ΓZ)=(2w−1,0,2w−1) is a linear approximation that holds with probability p=1 for any permutation operation,since the parity of all the bits in Z is always equal to the parity of all the bits in X;this approximation has a bias b=1/2.We will consider re-stricted forms to the linear approximations,depending on whether any control bits Y are involved in the approxima-tion.When Y is not involved,the simplest approximation takes the form of(e s,0,e t).This will be denoted type(L) and intuitively,the bias of such a linear approximation mea-sures how uniformly the permutation moves the bits around (e.g.whether there is a bit position that tends to befixed). When Y is involved,the simplest approximation,denoted with type(M),takes the form of(e s,e u,e t).The bias of these approximations measures if the destination position of a bit in X highly depends on a single bit in Y.Ideally, the destination position of a bit in X depends on many bits in Y,and these bits are equally important to determining the position.The maximum bias for these approximations are listed in Table2.。