6.1基本运算电路

电子技术06第6章电力电子器件及基本电力变换电路课件

V1,4导通,u0=Ud

u G1,4 u G2,3

t

VD2,3导通,u0= -Ud

t

V2,3导通,u0= -Ud

uo io

t3

t4

t 5

VD1,4导通,u0= Ud

t1

t2

t

控制信号 开V1,4,关V2,3 开V2,3,关V1,4 开V1,4,关V2,3

器件导通情况 VD1,4 V1,4 VD2,3 V2,3 VD1,4

数量关系

Uo

ton ton toff

E

ton T

E

E

Io

Uo

EM R

Ton / T

续流二极管

不希望电流断续

负载 上的 反电 动势

电流连续

动态演示

电流断续

6.3.2 升压斩波电路 (Boost Chopper)

1) 升压斩波电路的基本原理

电路结构

工作原理 假设L和C值很大

V通态,E向L充电,I1恒定,C向R供电,Uo恒定。 V断态,E和L同时向C充电,并向负载提供能量

6.1 常用电力电子器件

按照器件被控制信号所控制的程度,可做如下分类

半控型器件(Thyristor)通过控制信号可控制通,不能控制关 全控型器件(IGBT,MOSFET) 通过控制信号既可控制通又可控制

关又称自关断器件 不可控器件 (Power Diode) 不能用控制信号来控制其通断, 不需要

驱动电路

注入区

C

ID RN V-J1+ IC

C

-+

+

-IDRon

G

E

b)

c)

场控器件,原理与电力MOSFET基本相同,通断由栅射极电压uGE决定。

6.1角度调制原理6.2调频电路6.3角度调制的解调6.4自动频

设调制信号电压(单音频信号)为

ω(t)=ωc+Δω(t)=ωc+kfuΩ(t) (6―1)

式中, kf 为与调频电路有关的比例常数,单位为

rad/(s·V);Δω(t)=kfuΩ(t),称为角频率偏移,简称角频 移。 Δω(t) 的最大值叫角频偏, Δωm=kf|uΩ(t)|max ,它表

示瞬时角频率偏离中心频率ωc的最大值。

第6章 信号变换二:角度调制与解调

6.1 角度调制原理

6.2 调频电路 6.3 角度调制的解调 6.4 自动频率控制 6.5 实训一:49.67MHz窄带调频

发射器的制作

6.6 实训二:49.67MHz窄带调频 接收器的制作

6.1 角度调制原理

6.1.1 调频信号数学表达式 设载波信号电压为 uc(t)=Ucmcos(ωct+φ0) 式中,ωct+φ0为载波的瞬时相位;ωc为载波信号的 角频率;φ0为载波初相角(一般地,可以令φ0=0)。

对式(6―1)积分可得调频波的瞬时相位φf(t)

f (t ) (t )dt ct k f u (t )dt ct f (t )

0 0

t

t

(6―2)

f (t ) k f u (t )dt

0

t

表示调频波的相移,它反映调频信号的瞬时相位

按调制信号的时间积分的规律变化。 调频信号的数学表达式

1 .0 l= 0 0 .6 l= 1 l= 2 l= 3

l= 4

Jl (mf )

0 .2 0

- 0 .4 0 2 4 mf / rad 6 8 10

图6.3 第一贝塞尔函数曲线

在贝塞尔函数理论中,可得下述关系:

6.1时序电路的基本概念(2012)

01 / 1

S4

S7

10 / 1

s1 s2 s3 s4 s5 s6 s7

S1 / 0

S5 / 1

/

S2 / 1

S2 / 1

S3 / 1 S3 / 1

S1 / 0

S4 / 1 S4 / 1

/ / /

S6 / 1 S6 / 1

S1 / 0

S5 / 1

/

/

S7 / 1 S7 / 1

第六章 时序电路的分析与设计

6.1 时序逻辑电路概述

6.1.1 时序电路的特点 举例:铁路与公路的交叉路口,控制信号与放行栏杆的时序关系。

X1

铁路

西

公路

A B

X2

东

1 放下 AB为两栏杆: Z 0 升起

X1X 2

两传感器发出的信号 取值为1:有火车经过 取值为0:没火车经过

1

X1

公路

A

2、按输出信号的特点分 • Mealy 模型:

Z

Z F ( X ,Q )

X

1

J

Q1

Q

J

Q0

K

K

Q

CP

• Moore 模型:

Z

D

Q1

D

Q2

Z F (Q )

CP

CP1

CP 2

3

• Mealy 模型:

Z

X

状态转移图

1

J

Q1 Q

J

Q0

K

K

Q

X /Z

Q1Q0

CP

Z F ( X ,Q )

状态转移表:

X1X 2

状态

S1 S2 S3 S4

1

6.1-6.5组合逻辑电路

A B C Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7

0 0 0 0 1 2.由状态表写出 逻辑式 1 Y0 ABC Y1 ABC 1 Y2 ABC Y3 ABC 1

输入 Ai Bi 0 0 0 1 1 0 1 1

输出 Si Ci 0 0 1 0 1 0 0 1

输入 Ai Bi

输出 Si Ci

由状态表可写出本位和与进位 的逻辑函数式。 根据Si=1,按正逻辑写:

0

0 1 1

0

1 0 1

0

1 1 0

0

0 0 1

Si Ai Bi Ai Bi A B

Si ( Ai Bi Ai Bi )C i 1 ( Ai Bi Ai Bi )Ci 1

Ci Ai Bi ( Ai Bi )Ci 1

于是可写出

S0 ( A0 B0 A0 B0 )C 1 ( A0 B0 A0 B0 )C1

C0 A0 B0 ( A0 B0 )C1

Y9等十进制数的10个信号编成二进制代码。已知Y9

的优先级别最高,Y8次之,依次类推。当有几个信号 同时出现在输入端时,要求只对级别最高的编码。 解: 列优先编码表

输

入

输 出

Y0 Y1 Y2 Y3 Y4

Y5 Y6 Y7 Y8 Y9 D

C

B

A

1

0

0

0

0

0 0 1

0

0 0 0

0

0 0 0

0

0 0 0

0

Ci Ai Bi Ci 1 Ai Bi Ci 1 Ai Bi C i 1 Ai Bi Ci 1 ( Ai Bi Ai Bi )Ci 1 Ai Bi (C i 1 Ci 1 ) ( Ai Bi )Ci 1 Ai Bi

2023年大学_EDA技术与VHDL第二版(潘松著)课后习题答案下载

2023年EDA技术与VHDL第二版(潘松著)课后习题答案下载EDA技术与VHDL第二版(潘松著)课后答案下载第1章 EDA技术概述1.1 EDA技术及其发展1.1.1 EDA技术的发展1.1.2 EDA技术的涵义1.1.3 EDA技术的基本特征1.2 EDA技术的主要内容及主要的EDA厂商1.2.1 EDA技术的主要内容1.2.2 主要EDA厂商概述1.3 EDA技术实现目标1.3.1 超大规模可编程逻辑器件1.3.2 半定制或全定制ASIC1.3.3 混合ASIC1.4 EDA技术应用1.4.1 EDA技术应用形式1.4.2 EDA技术应用场合1.5 EDA技术的发展趋势1.5.1 可编程器件的发展趋势1.5.2 软件开发工具的发展趋势1.5.3 输入方式的发展趋势__小结思考题和习题第2章大规模可编程逻辑器件2.1 可编程逻辑器件概述2.1.1 PLD的'发展进程2.1.2 PLD的种类及分类方法2.2 简单可编程逻辑器件2.2.1 PLD电路的表示方法及有关符号 2.2.2 PROM基本结构2.2.3 PLA基本结构2.2.4 PAL基本结构2.2.5 GAL基本结构2.3 复杂可编程逻辑器件2.3.1 CPLD基本结构2.3.2 Altera公司器件2.4 现场可编程逻辑器件2.4.1 FPGA整体结构2.4.2 Xilinx公司FPGA器件2.5 在系统可编程逻辑器件2.5.1 ispLSl/pLSl的结构2.5.2 Lattice公司ispLSI系列器件 2.6 FPGA和CPLD的开发应用2.6.1 CPLD和FPGA的编程与配置2.6.2 FPGA和CPLD的性能比较2.6.3 FPGA和CPLD的应用选择__小结思考题和习题第3章 EDA设计流程与开发3.1 EDA设计流程3.1.1 设计输入3.1.2 综合3.1.3 适配3.1.4 时序仿真与功能仿真3.1.5 编程下载3.1.6 硬件测试3.2 ASIC及其设计流程3.2.1 ASIC设计方法3.2.2 一般的ASIC设计流程3.3 可编程逻辑器件的开发环境 3.4 硬件描述语言3.5 IP核__小结思考题和习题第4章硬件描述语言VHDL4.1 VHDL概述4.1.1 VHDL的发展历程4.1.2 VHDL的特点4.2 VHDL程序基本结构4.2.1 实体4.2.2 结构体4.2.3 库4.2.4 程序包4.2.5 配置4.3 VHDL基本要素4.3.1 文字规则4.3.2 数据对象4.3.3 数据类型4.3.4 运算操作符4.3.5 VHDL结构体描述方式 4.4 VHDL顺序语句4.4.1 赋值语句4.4.2 IF语句4.4.3 等待和断言语句4.4.4 cASE语句4.4.5 LOOP语句4.4.6 RETIARN语句4.4.7 过程调用语句4.4.8 REPORT语句4.5 VHDL并行语句4.5.1 进程语句4.5.2 块语句4.5.3 并行信号代人语句4.5.4 并行过程调用语句4.5.5 并行断言语句4.5.6 参数传递语句4.5.7 元件例化语句__小结思考题和习题第5章 QuartusⅡ软件及其应用5.1 基本设计流程5.1.1 建立工作库文件夹和编辑设计文件 5.1.2 创建工程5.1.3 编译前设计5.1.4 全程编译5.1.5 时序仿真5.1.6 应用RTL电路图观察器5.2 引脚设置和下载5.2.1 引脚锁定5.2.2 配置文件下载5.2.3 AS模式编程配置器件5.2.4 JTAG间接模式编程配置器件5.2.5 USBBlaster编程配置器件使用方法 __小结思考题和习题第6章 VHDL应用实例6.1 组合逻辑电路设计6.1.1 基本门电路设计6.1.2 译码器设计6.1.3 数据选择器设计6.1.4 三态门设计6.1.5 编码器设计6.1.6 数值比较器设计6.2 时序逻辑电路设计6.2.1 时钟信号和复位信号6.2.2 触发器设计6.2.3 寄存器和移位寄存器设计6.2.4 计数器设计6.2.5 存储器设计6.3 综合实例——数字秒表的设计__小结思考题和习题第7章状态机设计7.1 一般有限状态机7.1.1 数据类型定义语句7.1.2 为什么要使用状态机 7.1.3 一般有限状态机的设计 7.2 Moore型有限状态机设计 7.2.1 多进程有限状态机7.2.2 单进程有限状态机7.3 Mealy型有限状态机7.4 状态编码7.4.1 状态位直接输出型编码 7.4.2 顺序编码7.4.3 一位热码编码7.5 状态机处理__小结思考题和习题第8章 EDlA实验开发系统8.1 GW48型实验开发系统原理与应用8.1.1 系统性能及使用注意事项8.1.2 GW48系统主板结构与使用方法8.2 实验电路结构图8.2.1 实验电路信号资源符号图说明8.2.2 各实验电路结构图特点与适用范围简述8.3 GW48CK/GK/EK/PK2系统信号名与芯片引脚对照表 __小结思考题和习题第9章 EnA技术实验实验一:全加器的设计实验二:4位加减法器的设计实验三:基本D触发器的设计实验四:同步清零计数器的设计实验五:基本移位寄存器的设计串人/串出移位寄存器实验六:同步预置数串行输出移位寄存器的设计实验七:半整数分频器的设计实验八:音乐发生器的设计实验九:交通灯控制器的设计实验十:数字时钟的设计EDA技术与VHDL第二版(潘松著):内容简介《EDA技术与VHDL》主要内容有Altera公司可编程器件及器件的选用、QuartusⅡ开发工具的使用;VHDL硬件描述语言及丰富的数字电路和电子数字系统EDA设计实例。

数字电路基础

2021/2/4

2

这里的0和1不是十进制数中的数字,而是逻辑0和逻辑1。

产生和处理这类数字信号的电路称为数字电路或逻辑电路。数字电 路的任务是对数字信号进行运算(算术运算和逻辑运算)、计数、存贮、 传递和控制。

2.脉冲信号

t

t

所谓脉冲,是指脉动、短促和不连续的意思。

在数字电子技术中,把作用时间很短的、突变的电压或 电流称为脉冲。 数字信号实质上是一种脉冲信号。

解: ( 10 ) 2 1 1 2 5 1 1 2 3 1 1 2 2 1 1 2 1 1 2 0 ( 4 ) 1 (5 F )1D 65 12 6 1 1 5 1 6 1 1 3 0 6 ( 15 )10 33

(2)十进制数转换成二、十六进制数 十进制数转换成二进制数或十六 进制数,要分整数和小数两部分分别进行转换,这里只介绍整数部分的转 换。通常采取除2或除16取余法,直到商为0止。读数方向由下而上。

1·0=0;1·1=1

Y=A+B 0+0=0;0+1=1;

1+0=1;1+1=1

Y= A

0 1 10

2021/2/4

21

能实现与、或、非三种基本逻辑运算关系的单元电路分别叫做与门、 或门、非门(也称反相器),其对应的逻辑符号如图6.2.2所示。

2021/2/4

22

2.复合逻辑运算

与、或、非是三种最基本的逻辑关系,任何其他的复杂逻辑关系都可 由这三种基本逻辑关系组合而成。

2021/2/4

11

例6.1.5 将十进制数(58)10 分别

转换成二进制数和十六进制数。

先将(58)10转换成二进制数,

采取“除2取余法”,过程如下

三个基本门电路代数式,图符号及真值表

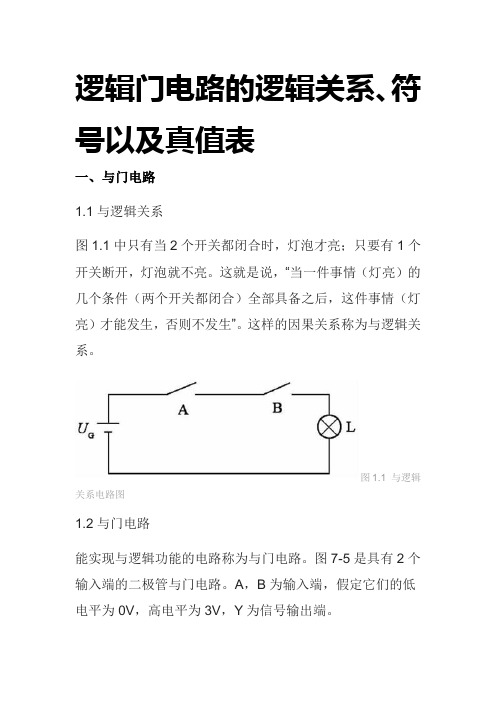

逻辑门电路的逻辑关系、符号以及真值表一、与门电路1.1与逻辑关系图1.1中只有当2个开关都闭合时,灯泡才亮;只要有1个开关断开,灯泡就不亮。

这就是说,“当一件事情(灯亮)的几个条件(两个开关都闭合)全部具备之后,这件事情(灯亮)才能发生,否则不发生”。

这样的因果关系称为与逻辑关系。

图1.1 与逻辑关系电路图1.2与门电路能实现与逻辑功能的电路称为与门电路。

图7-5是具有2个输入端的二极管与门电路。

A,B为输入端,假定它们的低电平为0V,高电平为3V,Y为信号输出端。

图1.2与门电路(1) 当A,B都处于低电平0V时,二极管VD1,VD2同时导通,Y=0V,输出低电平。

(忽略二极管的正向压降,下同)。

(2) 当A=0V,B=3V时,VD1优先导通,Y被箝位在0V,VD2反偏而截止。

(3) 当A=3V,B=0V时,VD2优先导通,Y被箝位在0V,VD1反偏而截止。

(4) 当A,B都处在高电平3V时,VD1与VD2均截止,Y 端输出高电平(即3V)。

与逻辑关系的逻辑函数表达式为Y=A*B。

表1.1是与门真值表,从真值表可以看出,与门电路的逻辑功能是“有0出0,全1出1”。

与门的逻辑符号如图1.3所示。

表1.1 与门真值表图1.3与门的逻辑符二、或门电路2.1或逻辑关系图2.1中电路由2个开关和灯泡组成。

由图可知,在决定一件事情的各种条件中,至少具备一个条件,这件事情就会发生,这种因果关系称为或逻辑关系。

图2.1 或逻辑关系电路图2.2或门电路能实现或逻辑关系的电路称为或门电路。

图2.2所示为具有2个输入端的二极管或门电路。

图2.2 或门电路真值表见表2.1,从真值表可以看出,或门的逻辑功能为“有1出1,全0出0”。

或门的逻辑符号如图2.3所示。

表2.1 或门真值表图2.3 或门逻辑符号三、非门电路(反相器)3.1非逻辑关系如图3.1开关与灯泡并联,当开关断开时,灯亮;开关闭合时,灯不亮。

这就是说,“事情(灯亮)和条件(开关)总是呈相反状态”,这种关系称为非逻辑关系。

EDA技术及应用—基于FPGA的电子系统设计:基于Verilog hdl的数字电路设计

10100

1111

15

10101

8421BC 余三码 D码

0000

0011

0001

0100

0010

0101

0011

0110

0100

0111

0101

1000

0110

1001

0111

1010

1000

1011

1001

1100

-

-

-

-

-

-

-

-

-

-

-

-

4位格雷码

0000 0001 0011 0010 0110 0111 0101 0100 1100 1101 1111 1110 1010 1011 1001 1000

4'b0011:a_to_g=7'b1111001; //显示3

4'b0100:a_to_g=7'b0110011; //显示4

4'b0101:a_to_g=7'b1011011; //显示5

4'b0110:a_to_g=7'b1011111; //显示6

4'b0111:a_to_g=7'b1110000; //显示7

4: y= {d[2:0],d[3]}; // rol

5: y= {d[3],d[3:1]}; // asr

6: y= {d[1:0],d[3:2]}; // ror2

7: y= d;

// noshift

default: y = d;

图6-2 基本门电路仿真结果

综合结果如图6-3所示。

图6-3 基本门电路综合结果

2、 三态逻辑电路

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1

t

(U

0.1m s

I

)dt

uO

(0.1ms)

5

(

t

0.1ms)

5

uo

(0.3

ms)

[

5 0.1ms

(0.3ms

0.1ms)ຫໍສະໝຸດ 5]V5V

正峰值未达运放的正饱和电压10V,所以仍正常线性积分.

例6.1.3 积分电路及输入波形如下,运放最大输出电压为10V, t =0 时电容电压为零,试画出输出电压波形。

二、变跨导模拟乘法器的基本工作原理

用压控电流源代 替了差分放大电 路中的恒流源。

二、变跨导模拟乘法器的基本工作原理

当 uY >> uBE3 时,iC3≈uY/RE

V1、V2管的跨导

gm

I E1 UT

iC3 2U T

uY

2REU T

uO

β

RC rbe

uX

gm RCuX

KuX uY

K RC

当rbIeC1、rbI'uCe Y2较有小限/时制g,m:必须为正且应较2R大EU。T

6.1.2 加减运算电路

一、求和运算电路

1. 反相求和运算电路

平衡电阻

R3 =R1 // R2 // RF

电路特点: 输入信号均加至运放反相端

分析:

根据“虚短”“虚断”,可得

un up 0

if i1 + i2

故得

uo ui1 ui2 RF R1 R2

uo

RF

(

ui1 R1

ui2 R2

)

优点:调节方便。

特点:1. 信号加至反相端,反相放大或缩小电压信号。

2. un up 0,运放输入端虚地。 uic 0 ,故对 KCMR 的要求低。这两点也是所有反相运算电路的特点。

3. 输入电阻较小。输出电阻趋于零,因此带负载能力强,

带负载前后的运算关系不变。

二、同相比例运算电路

平衡电阻 R2 = R1 // R F

R2 KR1

uI1 uI 2

注意:要求 uI2>0 ,以使电路构成 深度负反馈。

四、模拟乘法器构成的运算电路 续

3. 平方根运算

iF

iI

注意:要求 uI<0 电路构成深度负反馈,

由运放输入端虚短、虚断得

uO KuO2 uI

故 uO

uI K

6.1 复习要点

主要要求:

理解基本运算电路的组成和特点,掌握基本运算 电路的分析方法。

分析:

利用叠加定理解题:

令ui2 = 0 , 得

令ui1 = 0 , 得

uo2

(1

RF R1

)uP

(1

RF R1

)

RF R1 RF

ui 2

uo1

RF R1

ui1

二、减法运算电路

电路特点:两个输入信号分别加至 运放反相和同相输入端

分析:

利用叠加定理解题:

令ui2 = 0 , 得

令ui1 = 0 , 得

2. 同相求和运算电路

电路特点:信号均加至同相输入端

分析:

平衡电阻

R2 // R3 =R1 // RF

根据同相端“虚断”,可得

uP

R3 R2 R3

ui1

R2 R2 R3

ui2

则

uo

(1

RF R1

)uP

(1

RF )( R3 R1 R2 R3

ui1

R2 R2 R3

ui2 )

uo (1

MC1496 内部结构及外部连接

uO KuXuY

K RC RYU T

四、模拟乘法器构成的运算电路

1. 平方运算 2. 除法运算

iF iI

实现乘法、平方、除法、开平方等运算

uO KuI2

当 uI2>0 时,电路构成深度负反馈, 由运放输入端虚短、虚断得

uI1 uO'

而uO'

R1

R2

KuOuI2 故uO

5V

解续:在 0.3~0.5ms 时间段内

uo(t)

1

t

U

0.3 m s

Idt

uO(0.3ms)

5 (t

0.3ms) 5

5

uo (0.5ms) 0.1ms (0.5ms 0.3ms) 5 5 V

由周期性,可画出输出电压波形如图所示。

例6.1.3 积分电路及输入波形如下,运放最大输出电压为10V, t =0 时电容电压为零,试画出输出电压波形。

uo

R(F

ui1 R1

ui2 ) R2

(1

RF ) R4 R1 // R2 R3 R4

ui3

与题意相比较得

R1

RF 4

25k

R2

RF 5

20k

(1 RF ) R4 8 R1 // R2 R3 R4

得 R4 4R3

又根据输入直流电阻相等的要求,得

R3 // R4 R1 // R2 // RF 10k

uo

(1

RF R1

)uP

Auf

1

RF R1

Ri

Ro 0

特点:

1. 信号加至运放同相端,同相放大电压信号, 放大倍数大于等于1。

2. 输入电阻很大。 3. 共模输入信号较大,对 KCMR 要求高。

二、同相比例运算电路 续

特例:电压跟随器, Auf 1

Auf

1

RF R1

Auf 1 常用作缓冲器

解: 根据题意,可采用积分运算电路,如图所示。

图中RF用以防止对低频信号增益过大。

要求RF远大于CF的容抗,也远大于R1 , 通常可取RF=10 R1

由图得Ri= R1 , 故R1= 10k

1

由图得 uo (t ) R1CF uI d t

1 与目标运算时相比较得 R1CF 103 故得 CF 0.1 F

1

t 0

UIdt

uO (0)

5

t

uo

(0.1ms)

5V 0.1ms

0.1ms

5

V

负峰值未达运放的负饱和电压-10V,所以能正常线性积分.

例6.1.3 积分电路及输入波形如下,运放最大输出电压为10V, t =0 时电容电压为零,试画出输出电压波形。

5V

解续:在 0.1~0.3ms 时间段内

uo(t)

6.1 基本运算电路

6.1.1 比例运算电路 6.1.2 加减运算电路 6.1.3 微分与积分运算电路 6.1.4 对数与指数运算电路 6.1.5 模拟乘法器在运算电路中的应用

6.1.1 比例运算电路

一、反相比例运算电路

Auf

uo ui

RF R1

Ri = R1

平衡电阻

Ro 0

R2 = R1 // R F

解续:在 0.3~0.5ms 时间段内

uo(t)

1

t

U

0.3 m s

Idt

uO(0.3ms)

5 (t

0.3ms) 5

5

uo (0.5ms) 0.1ms (0.5ms 0.3ms) 5 5 V

由周期性,可画出输出电压波形如图所示。

例 试设计一个运算电路,实现 uo 103 uI d t 且要求 Ri为 10k 。

RF R1

)(

R2

//

R3

)(

ui1 R2

ui2 ) R3

R2 // R3 R1 // RF

RF

(

ui1 R2

ui2 ) R3

调节不便

二、减法运算电路

电阻平衡

电路特点:信号分别加至 反相端和同相端。

分析:

利用叠加定理解题:

令ui2 = 0 ,

得

uo1

RF R1

ui1

二、减法运算电路

电路特点:两个输入信号分别加至 运放反相和同相输入端

重点:

基本运算电路的分析方法

作业:P348~ 6.1b c 6.3a 6.14

自学: 6.1.6 运算电路仿真 知识拓展

2. 分析运算电路的关键是抓住集成运放输入端“虚短”和 “虚断” 的特点,进行电路分析,从而求得运算关系。这 也是 分析运放构成的其它线性应用电路的基本方法,读 者应 通过多练习,熟练掌握这种方法。

3. 理想运放输出电阻为零,故运放带负载后运算关系不变。

6.1.5 模拟乘法器在运算电路中的应用

一、模拟乘法器的作用与基本特性

uo2

(1

RF R1

)uP

(1

RF R1

)

RF R1 RF

ui 2

uo1

RF R1

ui1

故

uo

uo1+uo2

RF R1

ui1+(1

RF R1

)

RF R1 RF

ui 2

当满足 R1 = R1, RF = RF 时, uo

RF R

( ui 2

ui1 )

例 试设计一个运算电路,实现 uo= ui2ui2 , 规定 RF 取 100k 。

三、单片集成模拟乘法器

改进思路:

采用双差分对模拟乘法 器(又称双平衡模拟乘法器) 构成四象限乘法器;利用负 反馈等扩展输入信号的动态 范围。

调节静态偏置电 流 I0/2

引入负反馈扩展 uY 的动态范围。

MC1496 内部结构及外部连接

MC1496 简介

I0 2

RY

uY

I0 2

RY

uX < UT ( 26 mV)

1

1t

分析: uo (t) R1CF

uI

dt