《ARM嵌入式系统结构与编程》第二章课后答案

最新《ARM嵌入式系统结构与编程》第二章课后答案

第2章ARM技术与ARM体系结构121.简述ARM处理器内核调试结构原理3答:ARM处理器一般都带有嵌入式追踪宏单元ETM(Embedded Trace Macro),4它是ARM公司自己推出的调试工具。

ARM处理器都支持基于JTAG(Joint TestAction Group 联合测试行动小组)的调试方法。

它利用芯片内部的Embedded ICE 56来控制ARM内核操作,可完成单步调试和断点调试等操作。

当CPU处理单步执7行完毕或到达断点处时,就可以在宿主机端查看处理器现场数据,但是它不能8在CPU运行过程中对实时数据进行仿真。

910ETM解决了上述问题,能够在CPU运行过程中实时扫描处理器的现场信息,并11数据送往TAP(Test Access Port)控制器。

上图中分为三条扫描链(图中的粗12实线),分别用来监视ARM核,ETM,嵌入式ICE的状态。

13141.分析ARM7TDMI-S各字母所代表的含义。

15答:ARM7 T D M I – S 中16ARM是Advanced RISC Machines的缩写177是系列号;T:支持高密度16位的Thumb指令集;1819D:支持JTAG片上调试;20M:支持用于长乘法操作(64位结果)ARM指令,包含快速乘法器;;21I:带有嵌入式追踪宏单元ETM,用来设置断点和观察点的调试硬件;22S:可综合版本,意味着处理器内核是以源代码形式提供的。

这种源代码形式23又可以编译成一种易于EDA工具使用的形式。

24252.ARM处理器的工作模式有哪几种,其中哪些为特权模式,哪些为异26常模式,并指出处理器在什么情况下进入相应的模式。

27答:ARM技术的设计者将ARM处理器在应用中可能产生的状态进行了分类,并28针对同一类型的异常状态设定了一个固定的入口点,当异常产生时,程序会自29动跳转到对应异常入口处进行异常服务。

301.用户模式:非特权模式,也就是正常程序执行的模式,大部分任31务在这种模式下执行。

ARM嵌入式系统结构与编程习题标准答案

《ARM嵌入式系统结构与编程》习题答案第一章绪论1.国内嵌入式系统行业对“嵌入式系统”的定义是什么?如何理解?答:国内嵌入式行业一个普遍认同的定义是:以应用为中心,以计算机技术为基础,软硬件可裁剪,适应应用系统对功能,可靠性,成本,体积,功耗严格要求的专业计算机系统。

从这个定义可以看出嵌入式系统是与应用紧密结合的,它具有很强的专用性,必须结合实际系统需求进行合理的剪裁利用。

因此有人把嵌入式系统比作是一个针对特定的应用而“量身定做”的专业计算机系统。

2.嵌入式系统是从何时产生的,简述其发展历程。

答:从20世纪70年代单片机的出现到目前各式各样的嵌入式微处理器,微控制器的大规模应用,嵌入式系统已经有了30多年的发展历史。

嵌入式系统的出现最初是基于单片机的。

Intel公司1971年开发出第一片具有4位总线结构的微处理器4004,可以说是嵌入式系统的萌芽阶段。

80年代初的8051是单片机历史上值得纪念的一页。

20世纪80年代早期,出现了商业级的“实时操作系统内核”,在实时内核下编写应用软件可以使新产品的沿着更快,更节省资金。

20世纪90年代实时内核发展为实时多任务操作系统。

步入21世纪以来,嵌入式系统得到了极大的发展。

在硬件上,MCU的性能得到了极大的提升,特别是ARM技术的出现与完善,为嵌入式操作系统提供了功能强大的硬件载体,将嵌入式系统推向了一个崭新的阶段。

3.当前最常用的源码开放的嵌入式操作系统有哪些,请举出两例,并分析其特点。

答:主要有嵌入式Linux和嵌入式实时操作内核uC/OS-II嵌入式Linux操作系统是针对嵌入式微控制器的特点而量身定做的一种Linux操作系统,包括常用的嵌入式通信协议和常用驱动,支持多种文件系统。

主要有以下特点:源码开放,易于移植,内核小,功能强大,运行稳定,效率高等。

uC/OS是源码工卡的实时嵌入式系统内核,主要有以下特点:源码公开,可移植性强,可固化,可剪裁,占先式,多任务,可确定性,提供系统服务等。

ARM嵌入式系统基础教程第二版课后习题答案

第1xx 嵌入式系统概述(1)举出3个本书中未提到的嵌入式系统的例子。

答:键盘、鼠标、扫描仪。

(2)什么叫嵌入式系统?答:嵌入到对象体系中的专用计算机应用系统。

(3)什么叫嵌入式处理器?嵌入式处理器分为哪几类?答:嵌入式处理器是为完成特殊的应用而设计的特殊目的的处理器。

分为3类:1.注重尺寸、能耗和价格;2.关注性能;3.关注全部4个需求——性能、尺寸、能耗和价格。

(4)什么是嵌入式操作系统?为何要使用嵌入式操作系统?答:嵌入式操作系统是操作系统的一种类型,是在传统操作系统的基础上加入符合嵌入式系统要求的元素发展而来的。

原因:1.提高了系统的可靠性;2.提高了开发效率,缩短了开发周期。

3.充分发挥了32位CPU的多任务潜力。

第2章ARM7体系结构1.基础知识(1)ARM7TDMI中的T、D、M、I的含义是什么?答:T:高密度16位Thumb指令集扩展;D:支持片上调试;M:64位乘法指令;I:Embedded ICE硬件仿真功能模块。

(2)ARM7TDMI采用几级流水线?使用何种存储器编址方式?答:3级;冯·诺依曼结构。

(3)ARM处理器模式和ARM处理器状态有何区别?答:ARM处理器模式体现在不同寄存器的使用上;ARM处理器状态体现在不同指令的使用上。

(4)分别列举ARM的处理器模式和状态?答:ARM的处理器模式:用户模式、系统模式、管理模式、中止模式、未定义模式、中断模式、快速模式;ARM的处理器状态:ARM状态、Thumb状态。

(5)PC和LR分别使用哪个寄存器?答:PC:R15;LR:4。

(6)R13寄存器的通用功能是什么?答:堆栈指针SP。

(7)CPSR寄存器中哪些位用来定义处理器状态?答:位31~28:N、Z、C、V,条件代码标志位;27~8:保留位;7~0:I、F、T、M4~0,控制标志位。

(8)描述一下如何禁止IRQ和FIQ的中断。

答:当控制位I置位时,IRQ中断被禁止,否则允许IRQ中断使能;当控制位F置位时,FIQ中断被禁止,否则允许FIQ中断使能。

《ARM嵌入式系统结构与编程》习题答案 邱铁编著

《ARM嵌入式系统结构与编程》邱铁编著. 清华大学出版社.年月第版 年月第二次印刷20093120108 《ARM嵌入式系统结构与编程》第1~4章思考与练习题答案 此答案仅供教师教学用 第1章绪论思考与练习题答案 1. 国内嵌入式系统行业对“嵌入式系统”的定义是什么 如何理解答 见教材1.1节。

2. 嵌入式系统是从何时产生的 简述其发展历程。

答 见教材1.1节。

3. 当前最常见的源码开放的嵌入式操作系统有哪些 请举出两例 并分析其特点。

答 见教材1.2.1节的嵌入式Linux和嵌入式实时操作内核μC /OS-II。

4. 举例说明嵌入式设备在工控设备中的应用。

答 见教材1.3节的“工业控制领域”。

5. 未来嵌入式技术的发展趋势有哪些 答 见教材1.4节的嵌入式技术的发展趋势。

第2章 ARM技术与ARM体系结构思考与练习题答案 1 简述ARM处理器内核调试结构原理。

答 对教材1.2节的图2-1进行描述。

2 分析ARM7TDMI-S各字母所代表的含义。

答 参考教材2 1 2 ARM核版本命名规则说明。

课后答案网《ARM嵌入式系统结构与编程》邱铁编著. 清华大学出版社. 年月第版 年月第二次印刷200931201083 ARM处理器的工作模式有哪几种 其中哪些为特权模式 哪些为异常模式并指出处理器在什么情况下进入相应的模式。

答 ARM处理器共有7种工作模式用户模式 非特权模式 也就是正常程序执行的模式 大部分任务在这种模式下执行。

在用户模式下 如果没异常发生 不允许应用程序自行改变处理器的工作模式 如果有异常发生 处理器会自动切换工作模式FIQ模式 也称为快速中断模式 支持高速数据传输和通道处理 当一个高优先级(fast)中断产生时将会进入这种模式。

IRQ模式 也称为普通中断模式 :当一个低优先级中断产生时将会进入这种模式。

在这模式下按中断的处理器方式又分为向量中断和非向量中断两种。

通常的中断处理都在IRQ模式下进行。

ARM嵌入式系统结构与编程课后复习题答案

《ARM嵌入式系统结构与编程》课后思考与练习题参考答案第一章绪论思考与练习题答案:1、答:见教材P2的1.1节容。

2、答:见教材P1的1.1节容。

3、答:见教材P4的1.2.1节的嵌入式Linux和嵌入式实时操作系统核µC/OS-Ⅱ。

4、答:见教材P6的1.3节的“工业控制领域”。

5、答:见教材P8的1.4节的嵌入式技术的发展趋势。

第二章ARM技术与ARM体系结构思考与练习题答案:1、答:对教材P15的2.2节的图2-1进行描述。

2、答:参考教材P12的2.1.2节ARM核版本命名规则说明。

3、答:见教材P18的2.3节的ARM处理器共有7种工作模式。

4、答:PSR具体的格式为:P21的图2-7,描述“标志域”和“控制域”各位的功能。

C、Z、N、V进行置位和清零见P22的容。

5、答:ARM在异常时会进行以下操作:P24最上面的(1)(2)(3)(4)。

ARM在异常返回时:(1)从SPSR_<mode>恢复CPSR;(2)从LR_<mode>恢复PC。

6、答:见教材P25的“数据存储格式”中的“小端存储格式”和“大端存储格式”。

7、答:在ARM三级流水线下:见教材P27的“三级流水线运行情况分析”的(1)带有存储器访问指令的流水线。

8、答:ARM9在指令操作上采用的5级流水线:(1)取指令:从指令Cache中读取指令。

(2)译码:对指令进行译码,识别出是对哪个寄存器进行操作,并从通用寄存器中读取操作数。

(3)执行:进行ALU运算和移位操作,如果是对存储器操作的指令,则在ALU中计算出要访问的存储器地址。

(4)存储器访问:如果是对存储器访问的指令,用来实现数据缓冲功能(通过数据Cache);如果不是对存储器访问的指令,本级流水线为一个空的时钟周期。

(5)寄存器回写:将指令运算或操作结果写回到目标寄存器中。

9、答:见教材P29的“5级流水线互锁分析”的容。

第三章ARM指令集寻址方式思考与练习题答案:1、答:见教材P32的3.1节中“2.指令条件码”的容。

嵌入式系统开发 第二章 课后作业答案

第二章ARM7体系结构1、基础知识(1)、ARM7TDMI中的T、D、M、I的含义是什么?答:带T 后缀的:高密度 16 位的Thumb指令机扩展带D 后缀的:支持片上调试带M 后缀的:64 位乘法指令带I 后缀的:有EmbededICE 硬件仿真功能(2)、ARM7TDMI采用几级流水线?使用何种存储器编址方式?答:三级流水线(取指译码执行);使用了冯·诺依曼(Von Neumann )结构,指令和数据共用一条32 位总线。

(8)、描述一下如何禁止IRQ和FIQ的中断。

答:当控制位I置位时,IRQ中断被禁止,否则允许IRQ中断使能;当控制位F置位时,FIQ中断被禁止,否则允许FIQ中断使能。

2.存储器格式答:无论是大端格式还是小端格式,R2的值与R1一致;地址0x4000单元的字节:大端:0x12、小端:0x78。

3.处理器异常请描述一下ARM7TDMI产生异常的条件是什么?各种异常会使处理器进入哪种模式?进入异常时内核有何操作?各种异常的返回指令又是什么?答:产生异常的条件:只要正常的程序被暂时终止,处理器就进入异常模式进入异常时,内核自动做:PC→LR、CPSR→相应异常模式下的SPSR、设置CPSR为相应的异常模式、相应异常处理程序的中断入口向量地址→PC。

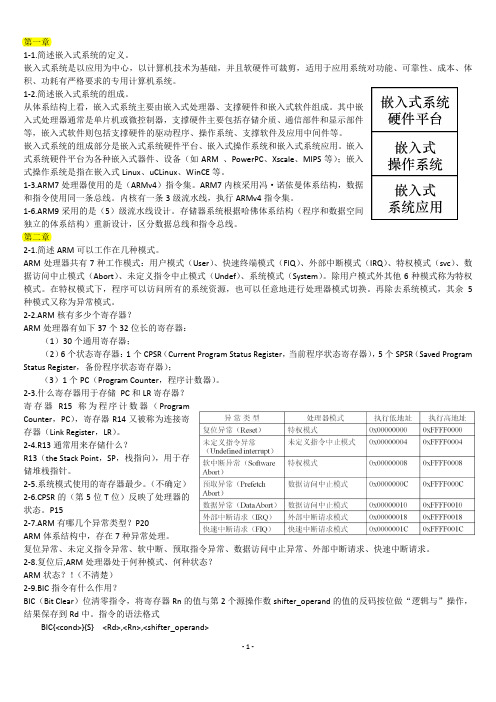

异常返回指令;【异常】【模式】【返回指令】复位管理无未定义指令未定义 MOVS PC,R14_svc软件中断管理 MOVS PC,R14_und预取指中止中止 SUBS PC,R14_abt,#4数据中止中止 SUBS PC,R14_abt,#8IRQ 中断 SUBS PC,R14_irq,#4FIQ 快速中断 SUBS PC,R14_fiq,#4。

《ARM嵌入式系统结构与编程》第二章课后答案复习进程

第2章ARM技术与ARM体系结构1.简述ARM处理器内核调试结构原理答:ARM处理器一般都带有嵌入式追踪宏单元ETM(Embedded Trace Macro),它是ARM 公司自己推出的调试工具。

ARM处理器都支持基于JTAG(Joint Test Action Group 联合测试行动小组)的调试方法。

它利用芯片内部的Embedded ICE来控制ARM内核操作,可完成单步调试和断点调试等操作。

当CPU处理单步执行完毕或到达断点处时,就可以在宿主机端查看处理器现场数据,但是它不能在CPU运行过程中对实时数据进行仿真。

ETM解决了上述问题,能够在CPU运行过程中实时扫描处理器的现场信息,并数据送往TAP(Test Access Port)控制器。

上图中分为三条扫描链(图中的粗实线),分别用来监视ARM核,ETM,嵌入式ICE的状态。

1.分析ARM7TDMI-S各字母所代表的含义。

答:ARM7 T D M I – S 中ARM是Advanced RISC Machines的缩写7是系列号;T:支持高密度16位的Thumb指令集;D:支持JTAG片上调试;M:支持用于长乘法操作(64位结果)ARM指令,包含快速乘法器;;I:带有嵌入式追踪宏单元ETM,用来设置断点和观察点的调试硬件;S:可综合版本,意味着处理器内核是以源代码形式提供的。

这种源代码形式又可以编译成一种易于EDA工具使用的形式。

2.ARM处理器的工作模式有哪几种,其中哪些为特权模式,哪些为异常模式,并指出处理器在什么情况下进入相应的模式。

答:ARM技术的设计者将ARM处理器在应用中可能产生的状态进行了分类,并针对同一类型的异常状态设定了一个固定的入口点,当异常产生时,程序会自动跳转到对应异常入口处进行异常服务。

⏹1.用户模式:非特权模式,也就是正常程序执行的模式,大部分任务在这种模式下执行。

在用户模式下,如果没异常发生,不允许应用程序自行改变处理器的工作模式,如果有异常发生,处理器不会自动切换工作模式⏹2.FIQ模式:也称为快速中断模式,支持高速数据传输和通道处理,当一个高优先级(fast)中断产生时将会进入这种模式。

嵌入式系统课后习题-部分答案(PDF)

第一章1-1.简述嵌入式系统的定义。

嵌入式系统是以应用为中心,以计算机技术为基础,并且软硬件可裁剪,适用于应用系统对功能、可靠性、成本、体积、功耗有严格要求的专用计算机系统。

1-2.简述嵌入式系统的组成。

从体系结构上看,嵌入式系统主要由嵌入式处理器、支撑硬件和嵌入式软件组成。

其中嵌入式处理器通常是单片机或微控制器,支撑硬件主要包括存储介质、通信部件和显示部件等,嵌入式软件则包括支撑硬件的驱动程序、操作系统、支撑软件及应用中间件等。

嵌入式系统的组成部分是嵌入式系统硬件平台、嵌入式操作系统和嵌入式系统应用。

嵌入式系统硬件平台为各种嵌入式器件、设备(如ARM 、PowerPC、Xscale、MIPS等);嵌入式操作系统是指在嵌入式Linux、uCLinux、WinCE等。

1-3.ARM7处理器使用的是(ARMv4)指令集。

ARM7内核采用冯·诺依曼体系结构,数据和指令使用同一条总线。

内核有一条3级流水线,执行ARMv4指令集。

1-6.ARM9采用的是(5)级流水线设计。

存储器系统根据哈佛体系结构(程序和数据空间独立的体系结构)重新设计,区分数据总线和指令总线。

第二章2-1.简述ARM可以工作在几种模式。

ARM处理器共有7种工作模式:用户模式(User)、快速终端模式(FIQ)、外部中断模式(IRQ)、特权模式(svc)、数据访问中止模式(Abort)、未定义指令中止模式(Undef)、系统模式(System)。

除用户模式外其他6种模式称为特权模式。

在特权模式下,程序可以访问所有的系统资源,也可以任意地进行处理器模式切换。

再除去系统模式,其余5种模式又称为异常模式。

2-2.ARM核有多少个寄存器?ARM处理器有如下37个32位长的寄存器:(1)30个通用寄存器;(2)6个状态寄存器:1个CPSR(Current Program Status Register,当前程序状态寄存器),5个SPSR(Saved Program Status Register,备份程序状态寄存器);(3)1个PC(Program Counter,程序计数器)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第2章ARM技术与ARM体系结构

1.简述ARM处理器内核调试结构原理

答:ARM处理器一般都带有嵌入式追踪宏单元ETM(Embedded Trace Macro),它是ARM 公司自己推出的调试工具。

ARM处理器都支持基于JTAG(Joint Test Action Group 联合测试行动小组)的调试方法。

它利用芯片内部的Embedded ICE来控制ARM内核操作,可完成单步调试和断点调试等操作。

当CPU处理单步执行完毕或到达断点处时,就可以在宿主机端查看处理器现场数据,但是它不能在CPU运行过程中对实时数据进行仿真。

ETM解决了上述问题,能够在CPU运行过程中实时扫描处理器的现场信息,并数据送往TAP(Test Access Port)控制器。

上图中分为三条扫描链(图中的粗实线),分别用来监视ARM 核,ETM,嵌入式ICE的状态。

1.分析ARM7TDMI-S各字母所代表的含义。

答:ARM7 T D M I – S 中

ARM是Advanced RISC Machines的缩写

7是系列号;

T:支持高密度16位的Thumb指令集;

D:支持JTAG片上调试;

M:支持用于长乘法操作(64位结果)ARM指令,包含快速乘法器;;

I:带有嵌入式追踪宏单元ETM,用来设置断点和观察点的调试硬件;

S:可综合版本,意味着处理器内核是以源代码形式提供的。

这种源代码形式又可以编译成一种易于EDA工具使用的形式。

2.ARM处理器的工作模式有哪几种,其中哪些为特权模式,哪些为异常模式,并指出处

理器在什么情况下进入相应的模式。

答:ARM技术的设计者将ARM处理器在应用中可能产生的状态进行了分类,并针对同一类型的异常状态设定了一个固定的入口点,当异常产生时,程序会自动跳转到对应异常入口处进行异常服务。

⏹1.用户模式:非特权模式,也就是正常程序执行的模式,大部分任务在这种模式下

执行。

在用户模式下,如果没异常发生,不允许应用程序自行改变处理器的工作模式,如果有异常发生,处理器不会自动切换工作模式

⏹2.FIQ模式:也称为快速中断模式,支持高速数据传输和通道处理,当一个高优先

级(fast)中断产生时将会进入这种模式。

⏹3.IRQ模式:也称为普通中断模式,:当一个低优先级(normal)中断产生时将会进入

这种模式。

在这模式下按中断的处理器方式又分为向量中断和非向量中断两种。

通常的中断处理都在IRQ模式下进行。

⏹4.SVC模式:称之为管理模式,它是一种操作系统保护模式。

当复位或软中断指令

执行时处理器将进入这种模式。

⏹5.中止模式:当存取异常时将会进入这种模式,用来处理存储器故障、实现虚拟存

储或存储保护。

⏹6.未定义指令异常模式:当执行未定义指令时会进入这种模式,主要是用来处理未

定义的指令陷阱,支持硬件协处理器的软件仿真,因为未定义指令多发生在对协处理器的操作上。

⏹7.系统模式:使用和User模式相同寄存器组的特权模式,用来运行特权级的操作

系统任务。

⏹在这7种工作模式中,除了用户模式以外,其他6种处理器模式可以称为特权模式,

在这些模式下,程序可以访问所有的系统资源,也可以任意地进行处理器模式的切换。

⏹在这6种特权模式中,除了系统模式外的其他5种特权模式又称为异常模式,每种

异常都对应有自己的异常处理入口点。

3.分析程序状态寄存器(PSR)各位的功能描述,并说明C,Z,N,V在什么情况下进行置位

和清零。

答:

⏹条件位:

⏹N = 1-结果为负, 0-结果为正或0

⏹Z = 1-结果为0, 0-结果不为0

⏹ C =1-进位,0-借位

⏹V =1-结果溢出,0结果没溢出

⏹Q 位:

⏹仅ARM 5TE/J架构支持

⏹指示增强型DSP指令是否溢出

⏹中断禁止位:

⏹I = 1: 禁止IRQ.

⏹ F = 1: 禁止FIQ.

⏹T Bit

⏹仅ARM xT架构支持

⏹T = 0: 处理器处于ARM 状态

⏹T = 1: 处理器处于Thumb 状态

⏹Mode位(处理器模式位):

⏹0b10000User

⏹0b10001FIQ

⏹0b10010IRQ

⏹0b10011Supervisor

⏹0b10111Abort

⏹0b11011Undefined

⏹0b11111System

4.简述ARM处理器异常处理和程序返回的过程。

答:只要正常的程序流被暂时中止,处理器就进入异常模式。

例如响应一个来自外设的中断。

在处理异常之前,ARM7TDMI内核保存当前的处理器状态,这样当处理程序结束时可以恢复执行原来的程序。

如果同时发生两个或更多异常,那么将按照固定的顺序来处理异常。

在异常发生后,ARM7TDMI内核会作以下工作:

1.在适当的LR中保存下一条指令的地址

2.将CPSR复制到适当的SPSR中;

3. 将CPSR模式位强制设置为与异常类型相对应的值;

4.强制PC从相关的异常向量处取指。

ARM7TDMI内核在中断异常时置位中断禁止标志,这样可以防止不受控制的异常嵌套。

注:异常总是在ARM状态中进行处理。

当处理器处于Thumb状态时发生了异常,在异常向量地址装入PC时,会自动切换到ARM状态。

当异常结束时,异常处理程序必须:

1.将LR中的值减去偏移量后存入PC,偏移量根据异常的类型而有所不同;

2.将SPSR的值复制回CPSR;

3.清零在入口置位的中断禁止标志。

注:恢复CPSR的动作会将T、F和I位自动恢复为异常发生前的值。

5.ARM处理器字数据的存储格式有哪两种?并指出这两种格式的区别。

答:ARM7TDMI处理器可以将存储器中的字以下列格式存储

▪大端格式(Big-endian)

▪小端格式(Little-endian)

▪小端存储器系统:

在小端格式中,高位数字存放在高位字节中。

因此存储器系统字节0连接到数据线7~0。

▪大端存储器系统:

在大端格式中,高位数字存放在低位字节中。

因此存储器系统字节0连接到数据线31~24。

6.分析带有存储器访问指令(LDR)的流水线运行情况,并用图示说明流水线的运行机制。

答:存储器访问指令LDR 流水线举例

取指的存储器访问和执行的数据路径占用都是不可同时共享的资源,对于多周期指令来说,如果指令复杂以至于不能在单个时钟周期内完成执行阶段,就会产生流水线阻塞。

对存储器的访问指令LDR是非单周期指令

LDR指令的执行,访问存储器,回写寄存器(占用了3个周期)。

造成了MOV指令的执行被阻断。

7.简述ARM9的5级流水线每一级所完成的功能和实现的操作。

答:ARM920在指令操作上采用5级流水线.

取指:从指令Cache中读取指令。

译码:对指令进行译码,识别出是对哪个寄存器进行操作并从通用寄存器中读取操作数。

执行:进行ALU运算和移位操作,如果是对存储器操作的指令,则在ALU中计算出要访问的存储器地址。

存储器访问:如果是对存储器访问的指令,用来实现数据缓冲功能(通过数据Cache)。

寄存器回写:将指令运算或操作结果写回到目标寄存器中。

8.什么叫流水线互锁?应如何来解决,举例说明。

答:互锁:当前指令的执行需要前面指令的执行结果,但前面的指令没有执行完毕,引起流水线的等待。

互锁发生时,硬件会停止指令的执行,直到数据准备好。

上边程序中ORR指令执行时需要使用LDR指令加载后的R4寄存器,因此造成了ORR指令的等待。

编译器以及汇编程序员可以通过重新设计代码的顺序或者其他办法来减少互锁的数量。