A 50 Mbits iterative Turbo-decoder

跳频系统中Turbo码译码器的FPGA实现

跳频系统中Turbo码译码器的FPGA实现罗常青;安建平;沈业兵【期刊名称】《北京理工大学学报》【年(卷),期】2007(27)1【摘要】给出了跳频系统中Turbo码译码器的FPGA(field programmable gate array)实现方案.译码器采用了Max-Log-Map译码算法和模块化的设计方法,可以对不同帧长的Turbo码进行译码.在Xilinx公司的FPGA芯片xc3s2000-4fg676上实现了帧长可变的Turbo译码器.在帧长为1 024 bit、迭代5次条件下,该译码器时延为0.812 ms,数据吞吐量为1.261 Mbit/s.分别在高斯白噪声和部分频带噪声干扰两种信道环境中测试该Turbo码译码器的误码率性能,在部分频带噪声干扰中使用了AGC(自动增益控制),结果表明,AGC有效提高了译码器在部分频带噪声干扰下的性能.【总页数】5页(P63-67)【关键词】跳频系统;Turbo译码器;FPGA;部分频带噪声干扰【作者】罗常青;安建平;沈业兵【作者单位】北京理工大学信息科学技术学院电子工程系【正文语种】中文【中图分类】TN914【相关文献】1.一种改进Turbo码译码器的FPGA设计与实现 [J], 赵旦峰;罗清华;焉晓贞2.基于FPGA的Turbo码译码器设计与实现 [J], 薛礼妮;刘展威3.一种低存储容量Turbo码译码器结构设计及FPGA实现 [J], Zeng Jie;Zhan Ming;Luo Xiaohong;Yang Chao;Deng Yi;Wang Meng4.基于FPGA的高速TURBO码编译码器硬件实现方法 [J], 时述有; 吉彦军5.WCDMA系统中Turbo码译码器的FPGA实现——高效实现Log-MAP算法的硬件结构 [J], 姜军;白春龙;张平;胡健栋因版权原因,仅展示原文概要,查看原文内容请购买。

Freescale 双极性LDMOS宽带集成功率放大器数据表说明书

MW7IC008NT1MW7IC008NT11RF LDMOS Wideband Integrated Power AmplifierThe MW7IC008N wideband integrated circuit is designed with on--chip matching that makes it usable from 20to 1000MHz.This multi--stage structure is rated for 24to 32volt operation and covers most narrow bandwidth communication application formats.Driver Applications∙Typical CW Performance:V DD =28Volts,I DQ1=25mA,I DQ2=75mAFrequency G ps (dB)PAE (%)100MHz @11W CW 23.555400MHz @9W CW 22.541900MHz @6.5W CW23.534∙Capable of Handling 10:1VSWR,@32Vdc,900MHz,P out =6.5Watts CW (3dB Input Overdrive from Rated P out )∙Stable into a 5:1VSWR.All Spurs Below --60dBc @1mW to 8Watts CW P out @900MHz∙Typical P out @1dB Compression Point ≃11Watts CW @100MHz,9Watts CW @400MHz,6.5Watts CW @900MHz Features∙Broadband,Single Matching Network from 20to 1000MHz∙Integrated Quiescent Current Temperature Compensation with Enable/Disable Function (1)∙Integrated ESD Protection∙In Tape and Reel.T1Suffix =1,000Units,16mm Tape Width,13--inch Reel.Figure 2.Pin Connections123456789101112181716151413242322212019NC V T T S 1V G L S 2N CR F i n S 2R F o u t S 1/V D S 1N C N CN C N CRF outS2/V DS2NC V G S 2V T T S 2NC NC NC NCN C V GS1RF inS1NC NC V GLS11.Refer to AN1977,Quiescent Current Thermal Tracking Circuit in the RF Integrated Circuit Family and to AN1987,Quiescent Current Control for the RF Integrated Circuit Device Family .Go to /rf.Select Documentation/Application Notes --AN1977or AN1987.Document Number:MW7IC008NRev.3,12/2013Freescale Semiconductor Technical Data100--1000MHz,8W PEAK,28V RF LDMOS WIDEBANDINTEGRATED POWER AMPLIFIERMW7IC008NT12RF Device DataFreescale Semiconductor,Inc.MW7IC008NT1Table 1.Maximum RatingsRatingSymbol Value Unit Drain--Source Voltage V DSS --0.5,+65Vdc Gate--Source Voltage V GS --6.0,+12Vdc Operating VoltageV DD 32,+0Vdc Storage Temperature Range T stg --65to +150︒C Operating Junction Temperature T J 150︒C 100MHz CW Operation @T A =25︒C (3)400MHz CW Operation @T A =25︒C (3)900MHz CW Operation @T A =25︒C (3)CW1165W W W Input Power100MHz 400MHz 900MHzP in 272338dBmTable 2.Thermal CharacteristicsCharacteristicSymbol Value (1,2)Unit Thermal Resistance,Junction to Case (CW Signal @100MHz)(Case Temperature 82︒C,P out =11W CW)Stage 1,28Vdc,I DQ1=25mA Stage 2,28Vdc,I DQ2=75mA (CW Signal @400MHz)(Case Temperature 87︒C,P out =9W CW)Stage 1,28Vdc,I DQ1=25mA Stage 2,28Vdc,I DQ2=75mA (CW Signal @900MHz)(Case Temperature 86︒C,P out =6.5W CW)Stage 1,28Vdc,I DQ1=25mA Stage 2,28Vdc,I DQ2=75mAR θJC5.34.94.42.73.53.2︒C/WTable 3.ESD Protection CharacteristicsTest MethodologyClass Human Body Model (per JESD22--A114)1B Machine Model (per EIA/JESD22--A115)A Charge Device Model (per JESD22--C101)IIITable 4.Moisture Sensitivity LevelTest MethodologyRating Package Peak TemperatureUnit Per JESD22--A113,IPC/JEDEC J--STD--0203260︒C1.MTTF calculator available at /rf.Select Software &Tools/Development Tools/Calculators to access MTTF calculators by product.2.Refer to AN1955,Thermal Measurement Methodology of RF Power Amplifiers.Go to /rf.Select Documentation/Application Notes --AN1955.3.CW Ratings at the individual frequencies are limited by a 100--year MTTF requirement.See MTTF calculator (referenced in Note 1).MW7IC008NT13RF Device DataFreescale Semiconductor,Inc.Table 5.Electrical Characteristics (T A =25︒C unless otherwise noted)CharacteristicSymbolMinTypMaxUnitStage 1—Off CharacteristicsZero Gate Voltage Drain Leakage Current (V DS =65Vdc,V GS =0Vdc)I DSS ——10μAdc Zero Gate Voltage Drain Leakage Current (V DS =28Vdc,V GS =0Vdc)I DSS ——1μAdc Gate--Source Leakage Current (V GS =1.5Vdc,V DS =0Vdc)I GSS——10μAdcStage 1—On Characteristics Gate Threshold Voltage(V DS =10Vdc,I D =5.3μAdc)V GS(th) 1.32 2.8Vdc Gate Quiescent Voltage(V DD =28Vdc,I D =25mAdc,Measured in Functional Test)V GS(Q)22.83.5VdcStage 2—Off CharacteristicsZero Gate Voltage Drain Leakage Current (V DS =65Vdc,V GS =0Vdc)I DSS ——10μAdc Zero Gate Voltage Drain Leakage Current (V DS =28Vdc,V GS =0Vdc)I DSS ——1μAdc Gate--Source Leakage Current (V GS =1.5Vdc,V DS =0Vdc)I GSS——10μAdcStage 2—On Characteristics Gate Threshold Voltage(V DS =10Vdc,I D =23μAdc)V GS(th) 1.32 2.8Vdc Gate Quiescent Voltage(V DD =28Vdc,I D =75mAdc,Measured in Functional Test)V GS(Q)2 2.7 3.5Vdc Drain--Source On--Voltage(V GS =10Vdc,I D =3.6Adc)V DS(on)0.10.31VdcFunctional Tests (1)(In Freescale Test Fixture,50ohm system)V DD =28Vdc,I DQ1=25mA,I DQ2=75mA,P out =6.5W CW,f =900MHzPower GainG ps 21.523.531.5dB Power Added Efficiency PAE 3034—%Input Return LossIRL—--15--11dB Typical Broadband Performance (In Freescale Test Fixture,50ohm system)V DD =28Vdc,I DQ1=25mA,I DQ2=75mAFrequency G ps (dB)PAE (%)IRL (dB)100MHz @11W CW 23.555--20400MHz @9W CW 22.541--17900MHz @6.5W CW23.534--151.Part internally matched both on input and output.(continued)4RF Device DataFreescale Semiconductor,Inc.MW7IC008NT1Table 5.Electrical Characteristics (T A =25︒C unless otherwise noted)(continued)Characteristic Symbol Min Typ Max Unit Typical Performances (In Freescale Test Fixture,50ohm system)V DD =28Vdc,I DQ1=25mA,I DQ2=75mA,100--1000MHz BandwidthCharacteristicSymbol Min Typ Max Unit IMD Symmetry @6.8W PEP ,P out where IMD Third Order Intermodulation 30dBc (1)(Delta IMD Third Order Intermodulation between Upper and Lower Sidebands >2dB)IMD sym—0.1—MHzVBW Resonance Point (1)(IMD Third Order Intermodulation Inflection Point)VBW res —0.1—MHz Gain Flatness in 500--1000MHz Bandwidth @P out =6W Avg.G F — 1.35—dB Gain Variation over Temperature (--30︒C to +85︒C)∆G —0.024—dB/︒C Output Power Variation over Temperature (--30︒C to +85︒C)∆P1dB—0.005—dB/︒CTypical CW Performances —100MHz (In Freescale Test Fixture,50ohm system)V DD =28Vdc,I DQ1=25mA,I DQ2=75mA,P out =11W CW,f =100MHz Power GainG ps —23.5—dB Power Added Efficiency PAE —55—%Input Return LossIRL —--20—dB P out @1dB Compression Point,CWP1dB—11—WTypical CW Performances —400MHz (In Freescale Test Fixture,50ohm system)V DD =28Vdc,I DQ1=25mA,I DQ2=75mA,P out =9W CW,f =400MHz Power GainG ps—22.5—dB Power Added Efficiency PAE —41—%Input Return LossIRL —--17—dB P out @1dB Compression Point,CWP1dB—9—WTypical CW Performances —900MHz (In Freescale Test Fixture,50ohm system)V DD =28Vdc,I DQ1=25mA,I DQ2=75mA,P out =6.5W CW,f =900MHz Power GainG ps —23.5—dB Power Added Efficiency PAE —34—%Input Return LossIRL —--15—dB P out @1dB Compression Point,CWP1dB—6.5—W1.Not recommended for wide instantaneous bandwidth modulated signals.MW7IC008NT15RF Device DataFreescale Semiconductor,Inc.Figure 3.MW7IC008NT1Test Circuit Component LayoutTable 6.MW7IC008NT1Test Circuit Component Designations and ValuesPartDescriptionPart NumberManufacturer C10.01μF Chip Capacitor GRM3195C1E103JA01Murata C2,C150.1μF Chip Capacitors GRM219F51H104ZA01Murata C3,C1610μF Chip Capacitors GRM55DR61H106KA88L Murata C4,C5,C7,C8,C10,C11,C12,C140.01μF Chip Capacitors C0805C103K5RAC Kemet C6,C171μF,35V Tantalum Capacitors TAJA105K035R AVX C9 2.2pF Chip Capacitor ATC600S2R2CT250XT ATC C13 3.3pF Chip CapacitorATC600S3R3BT250XT ATC L1,L7150nH Ceramic Chip Inductors LL2012--FHLR15J Toko L2,L6180nH Ceramic Chip Inductors LL2012--FHLR18J Toko L3 1.6nH Inductor 0603HC--1N6XJLW Coilcraft L4,L5 5.1nH Inductors0603HP--5N1XJLW Coilcraft R1,R12510Ω,1/10W Chip Resistors RR1220P--511--B--T5Susumu R2,R3,R491Ω,1/8W Chip Resistors CRCW080591R0FKEA Vishay R5*,R9*0Ω,2.5A Chip Resistors CRCW08050000Z0EA Vishay R610K Ω,1/8W Chip Resistor CRCW080510K0JNEA Vishay R7,R1112K Ω,1/8W Chip Resistors CRCW080512K0JNEA Vishay R843Ω,1/8W Chip Resistor CRCW080543R0FKEA Vishay R1015K Ω,1/8W Chip Resistor CRCW080515K0JNEA Vishay PCB0.020",εr =3.66RO4350BRogers*Add for temperature compensation6RF Device DataFreescale Semiconductor,Inc.MW7IC008NT1TYPICAL CHARACTERISTICSG p s ,P O W E R G A I N (d B )1000100f,FREQUENCY (MHz)Figure 4.Broadband Performance @P in =14.6dBm CW600400300--307060504030--5--10--15I R L ,I N P U T R E T U R N L O S S (d B )4121086P A E ,P O W E R A D D E D E F F I C I EN C Y (%)500200800700--20--2514P o u t ,O U T P U T P O W E R (W A T T S )900Figure 5.Intermodulation Distortion Productsversus Two--Tone SpacingTWO--TONE SPACING (MHz)10--20--401200I M D ,I N T E R M O D U L A T I O N D I S T O R T I O N (d Bc )--60--30--50--10P out ,OUTPUT POWER (WATTS)CWFigure 6.Power Gain and Power AddedEfficiency versus Output Power18109080706050P A E ,P O W E R A D D E D E F F I C I E N C Y (%)G p s ,P O W E R G A I N (d B )2625402423222120193020100MW7IC008NT17RF Device DataFreescale Semiconductor,Inc.TYPICAL CHARACTERISTICSFigure 7.Broadband Frequency Responsef,FREQUENCY (MHz)200G A I N (d B )4006008001000120014001600-36I R L (d B )8RF Device DataFreescale Semiconductor,Inc.MW7IC008NT1V DD =28Vdc,I DQ1=25mA,I DQ2=75mAP out =11W @100MHz,9W @400MHz,6.5W @900MHz f MHz Z in ΩZ load Ω10049.78+j1.0747.87--j9.8515048.96+j1.4449.12--j5.4420048.00+j1.5449.09--j2.6625046.67+j1.3648.63--j0.7930045.30+j0.9147.73+j0.4935043.93+j0.1146.60+j1.2240042.53--j0.8645.63+j1.4345041.38--j2.1644.97+j1.1350040.30--j3.7145.04+j0.7055039.38--j5.4445.23+j0.7760038.43--j7.1144.80+j1.2965037.94--j8.7144.32+j1.4870037.49--j10.5243.57+j1.5175037.31--j12.4243.19+j1.3280037.00--j14.0342.61+j0.7785036.74--j15.6442.25+j0.3990036.57--j17.0941.90+j0.0395036.37--j18.5941.67--j0.41100036.12--j20.0641.77--j1.10105035.58--j21.4341.82--j1.60110035.00--j22.7941.90--j2.01115034.53--j24.3942.26--j2.43120033.53--j25.9742.51--j2.80125032.67--j27.8442.74--j2.99130031.61--j29.8943.10--j3.11135030.61--j32.3443.52--j3.19140029.55--j34.8143.86--j3.13145028.23--j37.6144.03--j3.03150027.34--j40.5944.33--j2.67Z in=Device input impedance as measured from gate to ground.Z load =Test circuit impedance as measured from drain to ground.Figure 8.Series Equivalent Input and Load ImpedanceZinZloadOutput Matching NetworkMW7IC008NT19RF Device DataFreescale Semiconductor,Inc.PACKAGEDIMENSIONS10RF Device Data Freescale Semiconductor,Inc.MW7IC008NT1MW7IC008NT111RF Device Data Freescale Semiconductor,Inc.12RF Device Data Freescale Semiconductor,Inc.MW7IC008NT1PRODUCT DOCUMENTATION AND SOFTWARERefer to the following documents and software to aid your design process.Application Notes∙AN1955:Thermal Measurement Methodology of RF Power Amplifiers∙AN1977Quiescent Current Thermal Tracking Circuit in the RF Integrated Circuit Family∙AN1987Quiescent Current Control for the RF Integrated Circuit Device FamilyEngineering Bulletins∙EB212:Using Data Sheet Impedances for RF LDMOS DevicesSoftware∙Electromigration MTTF Calculator∙RF High Power Model∙.s2p FileFor Software,do a Part Number search at ,and select the “Part Number”link.Go to the Software &Tools tab on the part’s Product Summary page to download the respective tool.REVISION HISTORYThe following table summarizes revisions to this document.RevisionDate Description 0Aug.2009∙Initial Release of Data Sheet 1Sept.2009∙Modified Fig.3,Test Circuit Component Layout and Table 6,Test Circuit Component Designations andValues to include temperature compensation options,p.5∙Fig.3,Test Circuit Component Layout,corrected V DD1to V GG1,p.5∙Table 6,Test Circuit Component Designations and Values,C6,C17:updated description from “1μF Tantalum Capacitors”to “1μF,35V Tantalum Capacitors”;L1,L7,L2,L6:corrected manufacturer fromCoilcraft to Toko;L3:corrected part number from “0603HC--1N6XJLC”to “0603HC--1N6XJLW”;L4,L5:corrected part number from “100B100JT500XT”to “0603HP--5N1XJLW”;R1,R12:updated descriptionfrom “510ΩChip Resistors”to “510Ω,1/10W Chip Resistors”,p.52Mar.2011∙Updated frequency in overview paragraph from “100to 1000MHz”to “20to 1000MHz”to reflect lower20MHz capability and narrow bandwidth modulation,p.1∙Updated IMD sym Typical value from 180MHz to 0.1MHz and VBW res Typical value from 210MHz to0.1MHz;modified Footnote 1to reflect limited device capability regarding wide video bandwidth,TypicalPerformance table,p.42.1Mar.2012∙Table 3,ESD Protection Characteristics,removed the word “Minimum”after the ESD class rating.ESDratings are characterized during new product development but are not 100%tested during production.ESDratings provided in the data sheet are intended to be used as a guideline when handling ESD sensitivedevices,p.23Dec.2013∙Table 6,Test Circuit Component Designations and Values:updated PCB description to reflect mostcurrent board specifications from Rogers,p.5∙Replaced Case Outline 98ASA10760D,Rev.O with Rev.A,pp.9--11.Mechanical outline drawing modified to reflect the correct lead end features.Format of the mechanical outline was also updated to thecurrent Freescale format for Freescale mechanical outlines.MW7IC008NT113Informationin this document is provided solely to enable system and software implementers to use Freescale products.There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document.Freescale reserves the right to make changes without further notice to any products herein.Freescale makes no warranty,representation,or guarantee regarding the suitability of its products for any particular purpose,nor does Freescale assume any liability arising out of the application or use of any product or circuit,and specifically disclaims any and all liability,including without limitation consequential or incidental damages.“Typical”parameters that may be provided in Freescale data sheets and/or specifications can and do vary in different applications,and actual performance may vary over time.All operating parameters,including “typicals,”must be validated for each customer application by customer’s technical experts.Freescale does not convey any license under its patent rights nor the rights of others.Freescale sells products pursuant to standard terms and conditions of sale,which can be found at the following address:/SalesTermsandConditions.Freescale and the Freescale logo are trademarks of Freescale Semiconductor,Inc.,Reg.U.S.Pat.&Tm.Off.All other product or service names are the property of their respective owners.E 2009,2011--2013Freescale Semiconductor,Inc.How to Reach Us:Home Page: Web Support:/supportMW7IC008NT1。

Turbo码及其在无线通信中的应用

Turbo码及其在无线通信中的应用1.引言未来的无线通信系统必须能为用户提供高速率、高质量、实时的多媒体业务,然而无线信道,特别是移动无线信道是典型的随机时变信道,其在时间域、频率域以及空间角域均存在着随机性的扩散,这些扩散将造成接收信号在相对应的频率域、时间域以及空间域产生严重的衰落现象,衰落将严重地恶化无线通信系统的传输可靠性和降低频谱效率。

为了实现高效、可靠的无线数据传输,两种手段是必要的:利用各种分集对抗衰落,利用信道编码实现差错控制。

频率分集、时间分集、空间分集是主要的分集手段,充分利用这些分集方法将衰落信道尽可能地改造为近似AWGN信道,然后利用信道编码进行检错和纠错。

一般的信道编译码方案,难以在无线通信中以较低的信噪比达到数据业务的服务质量(QoS)(例如一般要求误比特率 BER≤10-6),即使在以前的无线移动通信系统中通常采用的RS码与卷积码串行级联的信道编码方案,与香农(C.E. Shannon)界有较大的差距,直到1993年Claude Berrou, Alain Glavieux 和 Punya Thitimajshima发表他们的著名文章[1],他们发明的Turbo码的性能与香农界的差距仅为0.5dB。

他们发明的Turbo码的创新之处在于:用两个递归系统卷积成员码并行级联编码,这两个系统递归卷积成员码之间用一个伪随机交织器相连接,并且采用软入软出(SISO,Soft-In-Soft-Out)的迭代译码算法。

从此,Turbo 码就成为编码界的一个研究热点。

S. Ten Brink在[2]得到的Turbo码的性能与香农界的差距仅为0.1dB。

2.Turbo码的分类和迭代译码原理现在广义的Turbo码是指采用级联或乘积编码方法并利用迭代译码方法的编译码方案。

迭代译码的基本思想是将一个的复杂的长的译码步骤分解为多个相对简单的迭代译码步骤而且在迭代译码步骤之间信息概率的转移或者是软信息的传递确保几乎没有信息损失。

衰落信道硬判决解调下的Turbo码译码方法

衰落信道硬判决解调下的Turbo码译码方法王昊博;陈为刚;吴月敏【期刊名称】《信息技术》【年(卷),期】2013(000)006【摘要】In practical application,some demodulators could only provide hard-decision values,which are not compatible with the coding scheme using soft-in soft-out decoder,such as Turbo decoders.For fading channels,a decoding method was proposed which modifies the hard-decision values and improves the decoding performance.By compensating the decoding initial information with different reliable levels,the method proposed improves the accuracy of hard-decision values from channels.The simulation results show that,the improved method could improve the performance of Turbo decoding effectively with quite low complexity.%实际应用中某些通信系统的解调器只能输出硬判决信息,无法较好地匹配Turbo码采用的软输入软输出译码算法.针对衰落信道,提出了一种对硬判决信息进行修正,改善Turbo码译码性能的方法.该方法通过对译码初始化信息根据不同的可靠性进行补偿,可改善来自信道的硬判决接收值的准确性.仿真结果表明,改进方法可有效提高Turbo码译码的性能,复杂度也较低.【总页数】4页(P29-32)【作者】王昊博;陈为刚;吴月敏【作者单位】天津大学电子信息工程学院,天津300072;天津大学电子信息工程学院,天津300072;天津大学电子信息工程学院,天津300072【正文语种】中文【中图分类】TN911.22【相关文献】1.莱斯衰落信道下Turbo码的译码算法研究 [J], 饶清华2.衰落信道下卷积码的软判决译码 [J], 隋爱芬;杨义先;袁东风;李作为3.分组相关快衰落信道下Turbo码译码算法研究 [J], 姚如贵;王永生;徐娟4.分组Turbo码软判决自适应Chase译码算法的研究 [J], 张薇;刘星成;赵连强5.分组相关快衰落信道下自适应Turbo码译码算法研究 [J], 姚如贵;王永生;徐娟因版权原因,仅展示原文概要,查看原文内容请购买。

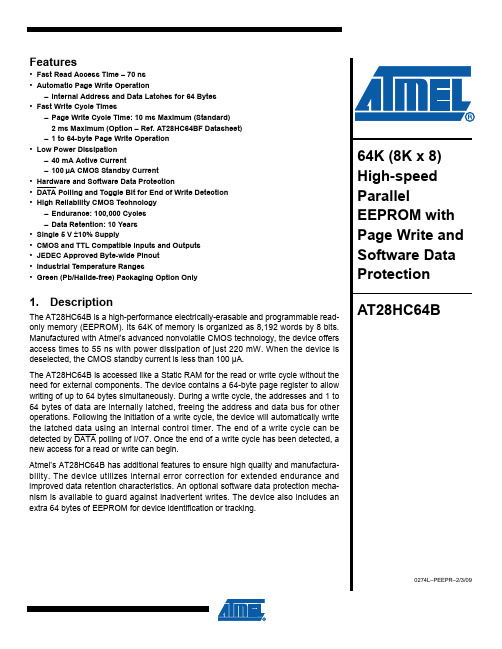

AT28HC64B高性能电擦可编程只读存储器(EEPROM)说明书

Features Array•Fast Read Access Time – 70 ns•Automatic Page Write Operation–Internal Address and Data Latches for 64 Bytes•Fast Write Cycle Times–Page Write Cycle Time: 10 ms Maximum (Standard)2 ms Maximum (Option – Ref. AT28HC64BF Datasheet)–1 to 64-byte Page Write Operation•Low Power Dissipation–40 mA Active Current–100µA CMOS Standby Current•Hardware and Software Data Protection•DATA Polling and Toggle Bit for End of Write Detection•High Reliability CMOS Technology–Endurance: 100,000 Cycles–Data Retention: 10 Years•Single 5 V ±10% Supply•CMOS and TTL Compatible Inputs and Outputs•JEDEC Approved Byte-wide Pinout•Industrial Temperature Ranges•Green (Pb/Halide-free) Packaging Option Only1.DescriptionThe AT28HC64B is a high-performance electrically-erasable and programmable read-only memory (EEPROM). Its 64K of memory is organized as 8,192 words by 8 bits. Manufactured with Atmel’s advanced nonvolatile CMOS technology, the device offers access times to 55 ns with power dissipation of just 220 mW. When the device is deselected, the CMOS standby current is less than 100µA.The AT28HC64B is accessed like a Static RAM for the read or write cycle without the need for external components. The device contains a 64-byte page register to allow writing of up to 64 bytes simultaneously. During a write cycle, the addresses and 1 to 64 bytes of data are internally latched, freeing the address and data bus for other operations. Following the initiation of a write cycle, the device will automatically write the latched data using an internal control timer. The end of a write cycle can be detected by DATA polling of I/O7. Once the end of a write cycle has been detected, a new access for a read or write can begin.Atmel’s AT28HC64B has additional features to ensure high quality and manufactura-bility. The device utilizes internal error correction for extended endurance and improved data retention characteristics. An optional software data protection mecha-nism is available to guard against inadvertent writes. The device also includes anextra 64 bytes of EEPROM for device identification or tracking.20274L–PEEPR–2/3/09AT28HC64B2.Pin Configurations2.128-lead SOIC Top ViewPin Name Function A0 - A12Addresses CE Chip Enable OE Output Enable WE Write Enable I/O0 - I/O7Data Inputs/Outputs NC No Connect DCDon’t Connect2.232-lead PLCC Top ViewNote:PLCC package pins 1 and 17 are Don’t Connect.2.328-lead TSOP Top View30274L–PEEPR–2/3/09AT28HC64B3.Block Diagram4.Device Operation4.1ReadThe AT28HC64B is accessed like a Static RAM. When CE and OE are low and WE is high, the data stored at the memory location determined by the address pins is asserted on the out-puts. The outputs are put in the high-impedance state when either CE or OE is high. This dual line control gives designers flexibility in preventing bus contention in their systems.4.2Byte WriteA low pulse on the WE or CE input with CE or WE low (respectively) and OE high initiates a write cycle. The address is latched on the falling edge of CE or WE, whichever occurs last. The data is latched by the first rising edge of CE or WE. Once a byte write has been started, it will automatically time itself to completion. Once a programming operation has been initiated and for the duration of t WC , a read operation will effectively be a polling operation.4.3Page WriteThe page write operation of the AT28HC64B allows 1 to 64 bytes of data to be written into the device during a single internal programming period. A page write operation is initiated in the same manner as a byte write; after the first byte is written, it can then be followed by 1 to 63 additional bytes. Each successive byte must be loaded within 150 µs (t BLC ) of the previous byte. If the t BLC limit is exceeded, the AT28HC64B will cease accepting data and commence the internal programming operation. All bytes during a page write operation must reside on the same page as defined by the state of the A6 to A12 inputs. For each WE high-to-low transition during the page write operation, A6 to A12 must be the same.The A0 to A5 inputs specify which bytes within the page are to be written. The bytes may be loaded in any order and may be altered within the same load period. Only bytes which are specified for writing will be written; unnecessary cycling of other bytes within the page does not occur.4.4DATA PollingThe AT28HC64B features DATA Polling to indicate the end of a write cycle. During a byte or page write cycle, an attempted read of the last byte written will result in the complement of the written data to be presented on I/O7. Once the write cycle has been completed, true data is valid on all outputs, and the next write cycle may begin. DATA Polling may begin at any time during the write cycle.40274L–PEEPR–2/3/09AT28HC64B4.5Toggle BitIn addition to DATA Polling, the AT28HC64B provides another method for determining the end of a write cycle. During the write operation, successive attempts to read data from the device will result in I/O6 toggling between one and zero. Once the write has completed, I/O6 will stop toggling, and valid data will be read. Toggle bit reading may begin at any time during the write cycle.4.6Data ProtectionIf precautions are not taken, inadvertent writes may occur during transitions of the host system power supply. Atmel ® has incorporated both hardware and software features that will protect the memory against inadvertent writes.4.6.1Hardware ProtectionHardware features protect against inadvertent writes to the AT28HC64B in the following ways: (a) V CC sense – if V CC is below 3.8 V (typical), the write function is inhibited; (b) V CC power-on delay – once V CC has reached 3.8 V, the device will automatically time out 5 ms (typical) before allowing a write; (c) write inhibit – holding any one of OE low, CE high or WE high inhib-its write cycles; and (d) noise filter – pulses of less than 15 ns (typical) on the WE or CE inputs will not initiate a write cycle.4.6.2Software Data ProtectionA software-controlled data protection feature has been implemented on the AT28HC64B. When enabled, the software data protection (SDP), will prevent inadvertent writes. The SDP feature may be enabled or disabled by the user; the AT28HC64B is shipped from Atmel with SDP disabled.SDP is enabled by the user issuing a series of three write commands in which three specific bytes of data are written to three specific addresses (refer to the “Software Data Protection Algorithm” diagram on page 10). After writing the 3-byte command sequence and waiting t WC , the entire AT28HC64B will be protected against inadvertent writes. It should be noted that even after SDP is enabled, the user may still perform a byte or page write to the AT28HC64B. This is done by preceding the data to be written by the same 3-byte command sequence used to enable SDP.Once set, SDP remains active unless the disable command sequence is issued. Power transi-tions do not disable SDP, and SDP protects the AT28HC64B during power-up and power-down conditions. All command sequences must conform to the page write timing specifica-tions. The data in the enable and disable command sequences is not actually written into the device; their addresses may still be written with user data in either a byte or page write operation.After setting SDP, any attempt to write to the device without the 3-byte command sequence will start the internal write timers. No data will be written to the device, however. For the dura-tion of t WC , read operations will effectively be polling operations.4.7Device IdentificationAn extra 64 bytes of EEPROM memory are available to the user for device identification. By raising A9 to 12 V ±0.5 V and using address locations 1FC0H to 1FFFH, the additional bytes may be written to or read from in the same manner as the regular memory array.50274L–PEEPR–2/3/09AT28HC64BNotes:1.X can be VIL or VIH.2.See “AC Write Waveforms” on page 8.3.VH = 12.0 V ±0.5 V.Note:1.I SB1 and I SB2 for the 55 ns part is 40 mA maximum.5.DC and AC Operating RangeAT28HC64B-70AT28HC64B-90AT28HC64B-120Operating Temperature (Case)-40°C - 85°C -40°C - 85°C -40°C - 85°C V CC Power Supply5 V ±10%5 V ±10%5 V ±10%6.Operating ModesMode CE OE WE I/O Read V IL V IL V IH D OUT Write (2)V IL V IH V IL D IN Standby/Write Inhibit V IH X (1)X High ZWrite Inhibit X X V IH Write Inhibit X V IL X Output Disable X V IH XHigh ZChip Erase V ILV H (3)V IL High Z7.Absolute Maximum Ratings*Temperature Under Bias................................-55°C to +125°C *NOTICE:Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent dam-age to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliabilityStorage Temperature.....................................-65°C to +150°C All Input Voltages(including NC Pins)with Respect to Ground.................................-0.6 V to +6.25 V All Output Voltageswith Respect to Ground...........................-0.6 V to V CC + 0.6 V Voltage on OE and A9with Respect to Ground..................................-0.6 V to +13.5V8.DC CharacteristicsSymbol Parameter ConditionMinMax Units I LI Input Load Current V IN = 0 V to V CC + 1 V 10µA I LO Output Leakage Current V I/O = 0 V to V CC10µA I SB1V CC Standby Current CMOS CE = V CC - 0.3 V to V CC + 1 V 100(1)µA I SB2V CC Standby Current TTL CE = 2.0 V to V CC + 1 V 2(1)mA I CC V CC Active Current f = 5 MHz; I OUT = 0 mA40mA V IL Input Low Voltage 0.8V V IH Input High Voltage 2.0V V OL Output Low Voltage I OL = 2.1 mA 0.40V V OH Output High VoltageI OH = -400 µA2.4V60274L–PEEPR–2/3/09AT28HC64B10.AC Read Waveforms (1)(2)(3)(4)Notes:1.CE may be delayed up to t ACC - t CE after the address transition without impact on t ACC .2.OE may be delayed up to t CE - t OE after the falling edge of CE without impact on t CE or by t ACC - t OE after an address changewithout impact on t ACC .3.t DF is specified from OE or CE whichever occurs first (C L = 5 pF).4.This parameter is characterized and is not 100% tested.9.AC Read CharacteristicsSymbol ParameterAT28HC64B-70AT28HC64B-90AT28HC64B-120Units MinMax MinMax MinMax t ACC Address to Output Delay 7090120ns t CE (1)CE to Output Delay 7090120ns t OE (2)OE to Output Delay 035040050ns t DF (3)(4)OE to Output Float 035040050ns t OHOutput Hold00ns70274L–PEEPR–2/3/09AT28HC64B11.Input Test Waveforms and Measurement Level12.Output Test LoadNote:1.This parameter is characterized and is not 100% tested.R F 13.Pin Capacitancef = 1 MHz, T = 25°C (1)Symbol Typ Max Units Conditions C IN 46pF V IN = 0 V C OUT 812pFV OUT = 0 V815.AC Write Waveforms15.1WE Controlled15.2CE Controlled14.AC Write CharacteristicsSymbol ParameterMin MaxUnits t AS , t OES Address, OE Setup Time 0ns t AH Address Hold Time 50ns t CS Chip Select Setup Time 0ns t CH Chip Select Hold Time 0ns t WP Write Pulse Width (WE or CE)100ns t DS Data Setup Time 50ns t DH , t OEHData, OE Hold Timens90274L–PEEPR–2/3/09AT28HC64B17.Page Mode Write Waveforms (1)(2)Notes: 1.A6 through A12 must specify the same page address during each high to low transition of WE (or CE).2.OE must be high only when WE and CE are both low.18.Chip Erase Waveformst S = t H = 5 µs (min.)t W = 10 ms (min.)V H = 12.0 V ±0.5 V16.Page Mode CharacteristicsSymbol Parameter MinMax Units t WC Write Cycle Time10ms t WC Write Cycle Time (Use AT28HC64BF))2ms t AS Address Setup Time 0ns t AH Address Hold Time 50ns t DS Data Setup Time 50ns t DH Data Hold Time 0ns t WP Write Pulse Width 100ns t BLC Byte Load Cycle Time 150µs t WPHWrite Pulse Width High50ns100274L–PEEPR–2/3/09AT28HC64B19.Software Data Protection EnableAlgorithm (1)Notes:1.Data Format: I/O7 - I/O0 (Hex);Address Format: A12 - A0 (Hex).2.Write Protect state will be activated at end of writeeven if no other data is loaded.3.Write Protect state will be deactivated at end of writeperiod even if no other data is loaded.4.1 to 64 bytes of data are loaded.20.Software Data Protection DisableAlgorithm (1)Notes:1.Data Format: I/O7 - I/O0 (Hex);Address Format: A12 - A0 (Hex).2.Write Protect state will be activated at end of writeeven if no other data is loaded.3.Write Protect state will be deactivated at end of writeperiod even if no other data is loaded.4. 1 to 64 bytes of data are loaded.21.Software Protected Write Cycle Waveforms (1)(2)Notes:1.A6 through A12 must specify the same page address during each high to low transition of WE (or CE) after the softwarecode has been entered.2.OE must be high only when WE and CE are both low.11AT28HC64BNote:1.These parameters are characterized and not 100% tested. See “AC Read Characteristics” on page 6.23.Data Polling WaveformsNotes:1.These parameters are characterized and not 100% tested.2.See “AC Read Characteristics” on page 6.25.Toggle Bit Waveforms (1)(2)(3)Notes: 1.Toggling either OE or CE or both OE and CE will operate toggle bit.2.Beginning and ending state of I/O6 will vary.3.Any address location may be used, but the address should not vary.22.Data Polling Characteristics (1)Symbol Parameter Min TypMaxUnits t DH Data Hold Time 0ns t OEH OE Hold Time 0ns t OE OE to Output Delay (1)ns t WR Write Recovery Timens24.Toggle Bit Characteristics (1)Symbol Parameter Min TypMaxUnits t DH Data Hold Time 10ns t OEH OE Hold Time 10ns t OE OE to Output Delay (2)ns t OEHP OE High Pulse 150ns t WR Write Recovery Timens12AT28HC64B26.Normalized I CCGraphs13AT28HC64B27.Ordering Information27.1Green Package Option (Pb/Halide-free)t ACC (ns)I CC (mA)Ordering Code Package Operation RangeActive Standby 70400.1AT28HC64B-70TU 28T Industrial (-40°C to 85°C)AT28HC64B-70JU 32J AT28HC64B-70SU 28S 90400.1AT28HC64B-90JU 32J AT28HC64B-90SU 28S AT28HC64B-90TU 28T 120400.1AT28HC64B-12JU 32J AT28HC64B-12SU28SPackage Type32J 32-lead, Plastic J-leaded Chip Carrier (PLCC)28S 28-lead, 0.300" Wide, Plastic Gull Wing Small Outline (SOIC)28T28-lead, Plastic Thin Small Outline Package (TSOP)27.2Die ProductsContact Atmel Sales for die sales options.28.Packaging Information 28.132J – PLCC14AT28HC64BAT28HC64B 28.228S – SOIC1528.328T – TSOP16AT28HC64BHeadquarters InternationalAtmel Corporation 2325 Orchard Parkway San Jose, CA 95131 USATel: 1(408) 441-0311 Fax: 1(408) 487-2600Atmel AsiaUnit 1-5 & 16, 19/FBEA Tower, Millennium City 5418 Kwun Tong RoadKwun Tong, KowloonHong KongTel: (852) 2245-6100Fax: (852) 2722-1369Atmel EuropeLe Krebs8, Rue Jean-Pierre TimbaudBP 30978054 Saint-Quentin-en-Yvelines CedexFranceTel: (33) 1-30-60-70-00Fax: (33) 1-30-60-71-11Atmel Japan9F, Tonetsu Shinkawa Bldg.1-24-8 ShinkawaChuo-ku, Tokyo 104-0033JapanTel: (81) 3-3523-3551Fax: (81) 3-3523-7581Product ContactWeb SiteTechnical Support******************Sales Contact/contactsLiterature Requests/literatureDisclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL’S TERMS AND CONDI-TIONS OF SALE LOCATED ON ATMEL’S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDEN-TAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel’s products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.© 2009 Atmel Corporation. All rights reserved. Atmel®, logo and combinations thereof, and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.。

Moxa ICS-G7850A系列48G+210GbE层3全光纤模块管理交换机产品介绍说明书

ICS-G7850A Series48G+210GbE Layer 3full Gigabit modular managed EthernetswitchesFeatures and Benefits•Up to 48Gigabit Ethernet ports plus 210G Ethernet ports •Up to 50optical fiber connections (SFP slots)•Up to 48PoE+ports with external power supply (with IM-G7000A-4PoEmodule)•Fanless,-10to 60°C operating temperature range•Modular design for maximum flexibility and hassle-free future expansion •Hot-swappable interface and power modules for continuous operation •Turbo Ring and Turbo Chain (recovery time <20ms @250switches)1,andSTP/RSTP/MSTP for network redundancy•Isolated redundant power inputs with universal 110/220VAC power supplyrange•Supports MXstudio for easy,visualized industrial network management •V-ON™ensures millisecond-level multicast data and video network recoveryCertificationsIntroductionProcess automation and transportation automation applications combine data,voice,and video,and consequently require high performance and high reliability.The ICS-G7850A Series full Gigabit backbone switches’modular design makes network planning easy,and allows greater flexibility by letting you install up to 48Gigabit Ethernet ports plus 210Gigabit Ethernet ports.The fanless switches support the Turbo Ring,Turbo Chain,and RSTP/STP redundancy technologies,and come with an isolated redundant power supply to increase system reliability and the availability of your network backbone.Additional Features and Benefits•Layer 3switching functionality to move data and information across networks (ICS-G7800A Series)•Advanced PoE management functions:PoE output setting,PD failure check,PoE scheduling,and PoE diagnostics (with IM-G7000A-4PoE module)•Command line interface (CLI)for quickly configuring major managed functions•Supports advanced VLAN capability with Q-in-Q tagging•DHCP Option 82for IP address assignment with different policies •Supports EtherNet/IP and Modbus TCP protocols for device management and monitoring•Compatible with PROFINET protocol for transparent data transmission•Digital inputs for integrating sensors and alarms with IP networks •Redundant,dual AC power inputs•IGMP snooping and GMRP for filtering multicast traffic•IEEE 802.1Q VLAN and GVRP protocol to ease network planning •QoS (IEEE 802.1p/1Q and TOS/DiffServ)to increase determinism •Port Trunking for optimum bandwidth utilization•TACACS+,SNMPv3,IEEE 802.1X,HTTPS,and SSH to enhance network security•Access control lists (ACL)increase the flexibility and security of network management•SNMPv1/v2c/v3for different levels of network management •RMON for proactive and efficient network monitoring•Bandwidth management to prevent unpredictable network status •Lock port function for blocking unauthorized access based on MAC address•Port mirroring for online debugging•Automatic warning by exception through email and relay output1.If the port link speed is 1Gigabit or higher,the recovery time is <50ms.SpecificationsInput/Output InterfaceAlarm Contact Channels Relay output with current carrying capacity of2A@30VDCDigital Inputs+13to+30V for state1-30to+1V for state0Max.input current:8mAEthernet Interface10GbE SFP+Slots2Slot Combination12slots for4-port interface modules(10/100/1000BaseT(X),or PoE+10/100/1000BaseT(X),or100/1000BaseSFP slots)2Standards IEEE802.1D-2004for Spanning Tree ProtocolIEEE802.1p for Class of ServiceIEEE802.1Q for VLAN TaggingIEEE802.1s for Multiple Spanning Tree ProtocolIEEE802.1w for Rapid Spanning Tree ProtocolIEEE802.1X for authenticationIEEE802.3for10BaseTIEEE802.3ab for1000BaseT(X)IEEE802.3ad for Port Trunk with LACPIEEE802.3u for100BaseT(X)and100BaseFXIEEE802.3x for flow controlIEEE802.3z for1000BaseSX/LX/LHX/ZXIEEE802.3af/at for PoE/PoE+outputIEEE802.3ae for10Gigabit EthernetEthernet Software FeaturesManagement ARPBack Pressure Flow ControlBOOTPDDMDHCP Option66/67/82DHCP Server/ClientFlow controlIPv4LLDPPort MirrorRARPRMONSCPSMTPSNMP InformSNMPv1/v2c/v3SyslogTelnetTFTPFilter802.1QBPDU FilterBPDU GuardGMRPGVRPIGMP v1/v2/v3QinQ VLANMulticast Routing DVMRPPIM-DMPIM-SMPIM-SSMRedundancy Protocols Link AggregationMRPMSTPRSTPTurbo Chain2.See the IM-G7000A datasheet for Gigabit Ethernet module product information.Turbo Ring v1/v2V-ONRouting Redundancy VRRPSecurity Access control listBroadcast storm protectionHTTPS/SSLMAB authenticationSticky MACNTP authenticationPort LockRADIUSSSHTACACS+Time Management NTP Server/ClientSNTPUnicast Routing OSPFRIPV1/V2Static RouteIndustrial Protocols EtherNet/IPModbus TCPMIB Bridge MIBEthernet-like MIBMIB-IIP-BRIDGE MIBQ-BRIDGE MIBRMON MIB Groups1,2,3,9RSTP MIBSwitch PropertiesDRAM128MBFlash16MBIGMP Groups4096Jumbo Frame Size9.6KBMAC Table Size16KMax.No.of VLANs256Packet Buffer Size12MbitsVLAN ID Range VID1to4094Priority Queues8USB InterfaceStorage Port USB Type ASerial InterfaceConsole Port USB-serial console(Type B connector) Power ParametersInput Voltage110to220VACRedundant dual inputsOperating Voltage85to264VACInput Current 1.1/0.72A@110/220VACNote:These are the input current ratings for the device with the maximum number ofmodules installed.Power Consumption(Max.)109.68/117.8W@110/220VACNote:These are the power consumption ratings for the device with the maximumnumber of modules installed.Total PoE Power Budget Installed with IM-G7000A-4PoE Module:Maximum1,440W@48VDCOverload Current Protection SupportedReverse Polarity Protection SupportedPhysical CharacteristicsIP Rating IP30Dimensions440x176x523.8mm(17.32x6.93x20.62in)Weight12900g(28.5lb)Installation Rack mountingEnvironmental LimitsOperating Temperature-10to60°C(14to140°F)Storage Temperature(package included)-40to85°C(-40to185°F)Ambient Relative Humidity5to95%(non-condensing)Standards and CertificationsEMC EN55032/24Safety EN60950-1UL60950-1UL61010-2-201EMI CISPR32,FCC Part15B Class AEMS IEC61000-4-2ESD:Contact:6kV;Air:8kVIEC61000-4-3RS:80MHz to1GHz:20V/mIEC61000-4-4EFT:Power:4kV;Signal:4kVIEC61000-4-5Surge:Power:2kV;Signal:2kVIEC61000-4-6CS:10VIEC61000-4-8PFMFRailway EN50121-4Freefall IEC60068-2-32Shock IEC60068-2-27Vibration IEC60068-2-6MTBFTime282,329hrsStandards Telcordia(Bellcore),GBWarrantyWarranty Period5yearsDetails See /warrantyPackage ContentsDevice1x ICS-G7850A Series switchCable1x USB type A male to USB type B maleInstallation Kit2x rack-mounting ear6x cap,plastic,for SFP slotPower Supply1x power cord,EU type1x power cord,US typeDocumentation1x quick installation guide1x warranty cardNote48V external power supply,SFP modules and/or modules from the IM-G7000A ModuleSeries need to be purchased separately for use with this product.DimensionsOrdering InformationModel Name Layer10GbE SFP+Slots 100/1000Base SFPSlots10/100/1000BaseT(X)PortsRJ45ConnectorOperating Temp.ICS-G7850A-2XG-HV-HV32Up to48Up to48-10to60°C Accessories(sold separately)IM-G7000A Module SeriesIM-G7000A-4GSFP Gigabit Ethernet interface module with4100/1000BaseSFP slots,-10to60°C operating temperature IM-G7000A-4GTX Gigabit Ethernet interface module with410/100/1000BaseT(X)ports,-10to60°C operatingtemperatureIM-G7000A-4PoE Gigabit Ethernet PoE+interface module with410/100/1000BaseT(X)ports,-10to60°C operatingtemperaturePower SuppliesPWR-G7000A-AC Power supply module(85to264VAC)for ICS-G7748A/G7750A/G7752A/G7848A/G7850A/G7852ASeries,-10to60°C operating temperatureSFP ModulesSFP-1FELLC-T SFP module with1100Base single-mode with LC connector for80km transmission,-40to85°Coperating temperatureSFP-1FEMLC-T SFP module with1100Base multi-mode,LC connector for2/4km transmission,-40to85°C operatingtemperatureSFP-1FESLC-T SFP module with1100Base single-mode with LC connector for40km transmission,-40to85°Coperating temperatureSFP-1G10ALC WDM-type(BiDi)SFP module with11000BaseSFP port with LC connector for10km transmission;TX1310nm,RX1550nm,0to60°C operating temperatureSFP-1G10ALC-T WDM-type(BiDi)SFP module with11000BaseSFP port with LC connector for10km transmission;TX1310nm,RX1550nm,-40to85°C operating temperatureSFP-1G10BLC WDM-type(BiDi)SFP module with11000BaseSFP port with LC connector for10km transmission;TX1550nm,RX1310nm,0to60°C operating temperatureSFP-1G10BLC-T WDM-type(BiDi)SFP module with11000BaseSFP port with LC connector for10km transmission;TX1550nm,RX1310nm,-40to85°C operating temperatureSFP-1G20ALC WDM-type(BiDi)SFP module with11000BaseSFP port with LC connector for20km transmission;TX1310nm,RX1550nm,0to60°C operating temperatureSFP-1G20ALC-T WDM-type(BiDi)SFP module with11000BaseSFP port with LC connector for20km transmission;TX1310nm,RX1550nm,-40to85°C operating temperatureSFP-1G20BLC WDM-type(BiDi)SFP module with11000BaseSFP port with LC connector for20km transmission;TX1550nm,RX1310nm,0to60°C operating temperatureSFP-1G20BLC-T WDM-type(BiDi)SFP module with11000BaseSFP port with LC connector for20km transmission;TX1550nm,RX1310nm,-40to85°C operating temperatureSFP-1G40ALC WDM-type(BiDi)SFP module with11000BaseSFP port with LC connector for40km transmission;TX1310nm,RX1550nm,0to60°C operating temperatureSFP-1G40ALC-T WDM-type(BiDi)SFP module with11000BaseSFP port with LC connector for40km transmission;TX1310nm,RX1550nm,-40to85°C operating temperatureSFP-1G40BLC WDM-type(BiDi)SFP module with11000BaseSFP port with LC connector for40km transmission;TX1550nm,RX1310nm,0to60°C operating temperatureSFP-1G40BLC-T WDM-type(BiDi)SFP module with11000BaseSFP port with LC connector for40km transmission;TX1550nm,RX1310nm,-40to85°C operating temperatureSFP-1GEZXLC SFP module with11000BaseEZX port with LC connector for110km transmission,0to60°C operatingtemperatureSFP-1GEZXLC-120SFP module with11000BaseEZX port with LC connector for120km transmission,0to60°C operatingtemperatureSFP-1GLHLC SFP module with11000BaseLH port with LC connector for30km transmission,0to60°C operatingtemperatureSFP-1GLHLC-T SFP module with11000BaseLH port with LC connector for30km transmission,-40to85°C operatingtemperatureSFP-1GLHXLC SFP module with11000BaseLHX port with LC connector for40km transmission,0to60°C operatingtemperatureSFP-1GLHXLC-T SFP module with11000BaseLHX port with LC connector for40km transmission,-40to85°Coperating temperatureSFP-1GLSXLC SFP module with11000BaseLSX port with LC connector for1km/2km transmission,0to60°Coperating temperatureSFP-1GLSXLC-T SFP module with11000BaseLSX port with LC connector for1km/2km transmission,-40to85°Coperating temperatureSFP-1GLXLC SFP module with11000BaseLX port with LC connector for10km transmission,0to60°C operatingtemperatureSFP-1GLXLC-T SFP module with11000BaseLX port with LC connector for10km transmission,-40to85°C operatingtemperatureSFP-1GSXLC SFP module with11000BaseSX port with LC connector for300m/550m transmission,0to60°Coperating temperatureSFP-1GSXLC-T SFP module with11000BaseSX port with LC connector for300m/550m transmission,-40to85°Coperating temperatureSFP-1GZXLC SFP module with11000BaseZX port with LC connector for80km transmission,0to60°C operatingtemperatureSFP-1GZXLC-T SFP module with11000BaseZX port with LC connector for80km transmission,-40to85°C operatingtemperatureSFP-1GTXRJ45-T SFP module with11000BaseT port with RJ45connector for100m transmission,-40to75°C operatingtemperatureSFP-10GERLC-T SFP+module with110GBase-ER port,LC connector for40km transmission,-40to85°C operatingtemperatureSFP-10GLRLC-T SFP+module with110GBase-LR port,LC connector for10km transmission,-40to85°C operatingtemperatureSFP-10GSRLC-T SFP+module with110GBase-SR port,LC connector for33m/82m/300m/400m transmission,-40to85°C operating temperatureSFP-10GZRLC-T SFP+module with110GBase-ZR port,LC connector for80km transmission,-40to85°C operatingtemperaturePower CordsPWC-C7UK-2B-183Power cord with United Kingdom(UK)plug,2.5A/250V,1.83mPWC-C7EU-2B-183Power cord with Continental Europe(EU)plug,2.5A/250V,1.83mPWC-C7US-2B-183Power cord with United States(US)plug,10A/125V,1.83mPWC-C13US-3B-183Power cord with United States(US)plug,1.83mPWC-C7AU-2B-183Power cord with Australian(AU)plug,2.5A/250V,1.83mPWC-C13UK-3B-183Power cord with United Kingdom(UK)plug,1.83mPWC-C13CN-3B-183Power cord with three-prong China(CN)plug,1.83mPWC-C13AU-3B-183Power cord with Australian(AU)plug,1.83mPWC-C13EU-3B-183Power cord with Continental Europe(EU)plug,1.83mSoftwareMXview-50Industrial network management software with a license for50nodes(by IP address)MXview-100Industrial network management software with a license for100nodes(by IP address)MXview-250Industrial network management software with a license for250nodes(by IP address)MXview-500Industrial network management software with a license for500nodes(by IP address)MXview-1000Industrial network management software with a license for1000nodes(by IP address)MXview-2000Industrial network management software with a license for2000nodes(by IP address)MXview Upgrade-50License expansion of MXview industrial network management software by50nodes(by IP address) Storage KitsABC-02-USB Configuration backup and restoration tool,firmware upgrade,and log file storage tool for managedEthernet switches and routers,0to60°C operating temperatureABC-02-USB-T Configuration backup and restoration tool,firmware upgrade,and log file storage tool for managedEthernet switches and routers,-40to75°C operating temperature©Moxa Inc.All rights reserved.Updated Jun28,2023.This document and any portion thereof may not be reproduced or used in any manner whatsoever without the express written permission of Moxa Inc.Product specifications subject to change without notice.Visit our website for the most up-to-date product information.。

ISD2560语音芯片的引脚及功能介绍

ISD2560语音芯片的引脚及功能介绍ISD2560是ISD系列单片语音录放集成电路的一种。

这是一种永久记忆型语音录放电路,录音时间为60s,可重复录放10万次。

该芯片采用多电平直接模拟量存储专利技术,每个采样值可直接存储在片内单个EEPROM单元中,因此能够非常真实、自然地再现语音、音乐、音调和效果声,从而避免了一般固体录音电路因量化和压缩造成的量化噪声和“金属声”。

该器件的采样频率为8.0kHz,同一系列的产品采样频率越低录放时间越长但通频带和音质会有所降低。

此外,ISD2560还省去了A/D和D/A转换器。

其集成度较高,内部包括前置放大器、内部时钟、定时器、采样时钟、滤波器、自动增益控制、逻辑控制、模拟收发器、解码器和480k字节的EEPROM。

ISD2560内部EEPROM存储单元均匀分为600行,有600个地址单元,每个地址单元指向其中一行,每一个地址单元的地址分辨率为100ms。

此外,ISD2560还具备微控制器所需的控制接口。

通过操纵地址和控制线可完成不同的任务,以实现复杂的信息处理功能,如信息的组合、连接、设定固定的信息段和信息管理等。

ISD2560可不分段,也可按最小段长为单位来任意组合分段。

1ISD2560的引脚功能ISD2560具有28脚SOIC和28脚PDIP两种封装形式。

图1所示是其引脚排列。

各引脚的主要功能如下:电源(VCCA,VCCD):为了最大限度的减小噪声,芯片内部的模拟和数字电路使用不同的电源总线,并且分别引到外封装上。

模拟和数字电源端最好分别走线,并应尽可能在靠近供电端处相连,而去耦电容则应尽量靠近芯片。

地线(VSSA,VSSD):由于芯片内部使用不同的模拟和数字地线,因此,这两脚最好通过低阻抗通路连接到地。

节电控制(PD):该端拉高可使芯片停止工作而进入节电状态。

当芯片发生溢出即OVF端输出低电平后,应将本端短暂变高以复位芯片;另外,PD端在模式6下还有特殊的用途。

一种超高速太赫兹测试信号产生器的设计

一种超高速太赫兹测试信号产生器的设计宋瑞良;刘一波【摘要】太赫兹通信系统具有极高的数据率特性,对测试环境提出巨大挑战.本研究实现一种伪随机二进制序列(pseudo-random bit sequence,PRBS)发生器,能够支持正交相移编码(quadrature phase shift keying,QPSK)调制模式,实现在QPSK 调制模式下高达40 Gbit/s码率的数据率输出,为太赫兹频带的通信系统应用测试环境提供必要条件.该PRBS发生器采用交叉存取的拓扑结构和高速数据选择器,延迟单元采用电流模式逻辑电路结构以保证高频工作情况下具有良好性能.电路采用标准40 nm互补金属氧化物半导体(complementary metal-oxide-semiconductor,CMOS)工艺,版图面积为0.25×0.15 mm2.PRBS产生器在电源电压为1.0V下功耗为37.5 mW.该技术可解决太赫兹高速数据测试的瓶颈问题.【期刊名称】《深圳大学学报(理工版)》【年(卷),期】2019(036)002【总页数】6页(P176-181)【关键词】太赫兹;电流模式逻辑门;伪随机二进制序列产生器;正交相移编码;互补金属氧化物半导体;触发器;高速电流型逻辑电路【作者】宋瑞良;刘一波【作者单位】中国电子科技集团公司第五十四研究所,河北石家庄050081;天津大学电气自动化与信息工程学院,天津300072【正文语种】中文【中图分类】TN47;TN492通信产业的迅猛发展对无线传输系统的数据率需求与日俱增.太赫兹频段 (100 GHz~10 THz)通信系统因其所具备的极宽频带特性,逐渐成为研究热点.然而,该频段通信系统高数据率的特征仍处在芯片测试环节,对测试环境的搭建提出巨大挑战.由于键合线寄生的电感在高频信号传输过程中无法忽略,印制电路板(printed circuit board,PCB)与绑定的焊盘也具有很大的寄生电容,在高数据率通信系统的测试环境中,频率高于10 GHz的信号通过键合线灌入系统难以实现良好的阻抗匹配.此外,在片外也很难通过仪器产生如此高的数据率,且能满足测试要求的伪随机序列信号.因此,一种较低成本的测试方案,即利用片上伪随机二进制序列(pseudo-random bit sequence,PRBS)发生器,产生具有足够高数据率,并能满足测试调制需求的输入信号,为太赫兹频段下的高数据率通信系统测试提供必要条件.因为SiGe BiCMOS、InP等III-V族工艺具有优越的频率特性,数据率高达100 Gbit/s的伪随机二进制序列发生器已见报道[1-4].然而,由于缺乏足够高数据率的片上伪随机二进制序列发生器,采用互补金属氧化物半导体(complementary metal-oxide-semiconductor, CMOS)工艺实现的太赫兹频段高数据率通信系统测试,需要复杂的测试方案和昂贵的测试设备[5-6].图1 传统的伪随机二进制序列产生器核心电路框图Fig.1 Block diagram of the conventional pseudo-random bit sequence generator core传统基于CMOS工艺的伪随机二进制序列发生器通常由数字电路设计完成,由组合逻辑门及多重D触发器等组成,整个电路包含数百个晶体管,通过计算机辅助设计完成布局和布线工作,常见的电路结构如图1.这样的设计方法和拓扑结构难以获得足够高的频率性能.主要原因有:① 构成系统的D触发器等延时单元等子模块主要为数字电路结构,传统的数字电路结构和设计方法难以胜任极高数据率的工作场景;② 由于数字电路的规模较大,通常采用计算机辅助设计完成器件布局和自动布线工作,数字电路单元常采用工艺库中提供的标准数字单元,这种设计方式会引入大量寄生电容和寄生电感,其影响会随工作频率的提高而逐渐增加,无法忽略甚至限制电路性能.本研究在拓扑结构设计上采用交叉存取的拓扑结构和高速数据选择器,在延迟单元设计上采用电流模式逻辑门结构替代传统D触发器结构.为减小寄生效应,采用射频集成电路的设计思想,根据电路特征进行布局布线,提升电路整体的高频性能.本研究采用40 nm CMOS工艺,实现一种高数据率的PRBS产生器.产生器单路能够产生数据率为20 Gbit/s的伪随机信号,且具有差分正交信号输出,能够满足正交相移编码 (quadrature phase shift keying,QPSK)通信系统的测试需求.在QPSK模式下,输出数据率可达40 Gbit/s以上.1 电路设计1.1 系统架构本研究实现的伪随机二进制序列产生器系统框图如图2.系统主要由伪随机二进制序列核心电路、时钟分配及驱动电路,和数据选择器构成.伪随机二进制序列核心电路产生所需的伪随机二进制序列.时钟分配及驱动电路将输入时钟进行处理,为核心电路提供所需的数字时钟.由于本研究实现的伪随机二进制序列产生器用于通信系统测试,在片上产生的伪随机二进制序列将作为被测系统的输入级,数据选择器通过控制SEL_I/SEL_Q,被测系统的输入信号从片上产生的伪随机二进制序列及外灌数据中选择,使被测电路能够在测试模式(片上产生的伪随机二进制序列)和使用模式(外灌所需要的数据)之间切换.图2 伪随机二进制序列产生器系统框图Fig.2 Block diagram of the proposed PRBS generator1.2 伪随机二进制序列产生器核心电路伪随机二进制序列产生器核心电路采用的电路框图如图3.电路分为两个支路,每个支路由7个锁存器单元和1个异或门组成.因为锁存器单元工作在高频状态下,传统的D触发器难以获得良好性能,故采用电流模式逻辑单元完成锁存工作.2个支路的输出通过数据选择器连接在一起.如果所有锁存器的初始状态都为“0”,那么整个伪随机二进制序列将被锁死,因此电路中也设置了启动开关防止出现锁死的状态.系统架构中有两个伪随机二进制序列产生器,I路与Q路的启动开关应设置在不同位置.传统伪随机二级制序列电路(图1)的输出数据频率与延时单元的工作频率和时钟频率相同.本研究采用交叉存取拓扑结构,可将延时单元的工作频率、时钟频率减为所需输出数据频率的一半,即伪随机二进制序列产生器在单路输出模式下,可实现的数据率是时钟频率的2倍.因为移向器环路仅需工作在输出速度一半的频率下,这一结构适用于高数据率输出场景,降低了高速缓存器、时钟输出驱动及时钟分配电路的设计难度.图3 伪随机二进制序列核心电路框图Fig.3 Block diagram of the proposed PRBS core1.3 电流驱动模式逻辑单元传统D触发器等基于数字电路的锁存器无法胜任如此高的工作频率,对于延时单元,本研究选择电流驱动模式逻辑单元.基本的锁存器电路结构如图4.前半个时钟周期,CKP为高电平、CLN为低电平时,输出端的信号与输入信号反向.后半个时钟周期,CLK为低电平、CLN为高电平时,输出电平与输入电平无关,交叉耦合管构成的负阻结构(M3和M4)将输出电平保持在CKP为高电平时的输出电平,由此,电路构成了一个锁存器延时单元.这种锁存器结构简单,仅由6个晶体管和2个电阻构成,在很高工作频率下,可通过合理布局和布线,减小寄生,从而具备更高的工作频率.锁存器的时间常数为τ=R×(Cds+Cgs+Cload)(1)图4 锁存器电路原理图Fig.4 Schematic of the current mode logic latch其中, R为图4中R1和R2的负载电阻和互联线的寄生电阻; Cds和Cgs是电路中晶体管的寄生电容; Cload是负载电容,通常由下一级负载晶体管的栅电容及互联线的寄生电容承担.由式(1)可见,减小负载电阻与晶体管尺寸都能提高工作频率.然而,如果电阻和晶体管尺寸减小,会影响电路的直流工作状态,电路对负载的驱动能力也会变差,负载电容的充放电时间增加,也会影响整个电路的工作频率.因此在设计过程中,应该通过迭代,综合考虑最高工作频率、驱动能力及直流功耗等多方面因素,选择最合适的参数.1.4 时钟分配电路由图3可知,伪随机二进制序列核心电路需要差分时钟.时钟分配电路需将片外单端输入时钟转换为差分时钟,且具有足够的驱动能力,能够驱动多级锁存器和数据选择器等电路.由于采用交叉存取的拓扑结构,降低了所需的时钟频率,进而降低了时钟分配电路的设计难度.然而,对数字电路来说,10 GHz依然是很高的工作频率,依然无法直接采用数字标准单元和自动化布局布线完成设计.本研究采用的时钟分配电路如图5.片外提供的时钟信号需在片外或片上完成阻抗匹配(阻抗匹配网络图中未画出),而后经过电容隔直(隔直电容也可用于阻抗匹配),偏置在合适的直流电压(VDD/2)后,经过缓冲器增强驱动能力,再分给两路完成单转差操作.为使得到的差分信号时钟延对齐,无反相器的一路需要加缓冲器进行延时.通过仿真迭代与调整,设置合适的反相器与时钟延时缓冲器尺寸,使差分时钟保持较为理想的差分状态.差分时钟在输出前需要通过多级缓冲器,以提高时钟的驱动能力.图5 时钟分配电路结构Fig.5 Block diagram of the clock distribution circuit 1.5 高速数据选择器由于二进制序列产生器核心电路采用并行交叉拓扑结构,延时单元及时钟分配电路的工作频率均为输出频率的一半,然而数据选择器的工作频率与输出频率相同.高速数据选择器也可采用电流模式逻辑实现[7],原理如图6.在前半个时钟周期,CKP为高电平、CKN为低电平时,IN1端口输入的信号从OUT端输出.后半个时钟周期,CKN为低电平、CKN为高电平时,IN2端口输入的信号从OUT端输出.图6 2∶1数据选择器电路原理图Fig.6 Schematic of the 2∶1 MUX1.6 高频电路版图设计考虑随着频率的升高,由互联线带来的寄生效应逐渐成为限制电路性能的主要原因,由数字标准单元、EDA (electronics design automation) 工具自动布局布线的设计方式难以实现高频性能,因此,本研究实现的电路版图采用射频集成电路的设计思想,充分考虑器件及互联线带来的寄生效应,提高电路的高频性能.由于器件自身寄生电容的影响,随着器件尺寸的增加,器件的本征延时会增加,影响器件的工作速度.然而,小尺寸器件难以提供足够的驱动能力,下一级电路寄生电容的充放电速度也会因此增加,同样影响电路的工作速度.因此,在器件尺寸的选择上,应综合考虑器件的本征延时和驱动能力,逐级选择合适尺寸,以实现在工作频率上的最优化设计.在晶体管布局的考虑中,要使管子距离尽可能小,版图布局尽可能对称,减少互联线不必要的拐弯,并且尽量缩短互联线长度.电路单元之间的互连采用高层互联线,降低互联线对衬底的寄生电容.对于高频信号关键路径长距离走线,采用顶层金属(top metal)实现,并在信号线周围做好良好的接地隔离.2 仿真结果本研究实现的伪随机二进制序列产生器电路版图如图7,电路采用Tsmc 40 nm CMOS标准工艺实现,版图面积为0.25 × 0.15 mm2.图7 伪随机二进制序列产生器电路版图Fig.7 Layout of the proposed PRBS generator电路及版图设计采用Cadence工具完成,由Calibre工具进行规则检查与后仿验证.由于实际应用中电源和地通过键合线提供,仿真过程中电源和地分别串入3.0 nH和0.5 nH的电感以模拟键合线的效果.电路需要的电源电压为1.0 V.在实际测试中,输入时钟采用外灌方式,由常见的信号源提供幅度为500 mV的正弦波信号即可,时钟信号通过探针给入,给入芯片后通过阻抗匹配、隔直后片内提供偏置,到达时钟分配电路,最终形成电路所需要的时钟.因此在实际仿真中,时钟分配电路的输入信号由阻抗50 Ω的正弦波信号提供,信号幅度为500 mV.对整体电路使用Calibre PEX工具提取后仿参数,进行瞬态仿真.当时钟频率为10 GHz时,I路瞬态波形如图8.可见,启动电路在发生器自锁的情况下能够发挥作用,使发生器离开锁定状态正常工作.单路输出数据率20 Gbit/s,QPSK模式下输出数据率为40 Gbit/s,其眼图如图9.电路整体的图8 QPSK调制中I路20 Gbit/s的输出波形Fig.8 20 Gbit/s output waveform of I path in QPSK mode图9 伪随机二进制序列产生器在QPSK调制模式下的眼图Fig.9 Eye diagram of the PRBS generator in QPSK mode直流功耗为37.5 mW.由仿真结果可知,该伪随机二进制序列产生器可满足QPSK调制的通讯系统片上测试要求,且最高能达到40 Gbit/s的总数据率输出.伪随机二进制序列产生器的性能概要及文献对比如表1.可见,本研究实现的伪随机二进制序列产生器,能够提供高数据率信号,且消耗更小的面积与功耗.表1 本文伪随机二进制序列产生器性能概要与其他文献对比Table 1 Comparison of the proposed generator and the state-of-the-art methods文献工艺模位长度最大数据率/(Gbit·s-1)面积/mm2功耗/W本研究(仿真)40 nm CMOS27-120 (单路)0.25 × 0.150.375文献[8]AlGaAs/GaAs HBT27-1213.20 ×3.201.100文献[9]0.13 μm CMOS27-1200.70 × 1.100.840文献[10]45 nm CMOS29-110——结语本研究采用标准40 nm CMOS工艺,实现一种(27-1)模的伪随机二进制序列发生器.该发生器采用交叉存取的拓扑结构,基本延迟单元和数据选择器均采用电流模式逻辑电路结构.单路电路能够产生20 Gbit/s数据率的伪随机二进制码输出,并具有差分正交信号输出,能够满足正交相移编码的通信系统测试需求.在正交相移编码模式下,输出数据率可达40 Gbit/s以上.仿真结果与性能比较表明,本研究实现的伪随机二进制序列产生器能够提供高数据率信号,且面积与功耗更小,对太赫兹高速信号测试奠定技术基础.参考文献:【相关文献】[1] KNAPP H, WURZER M, PERNDL W, et al. 100-Gb/s 27-1 and 54-Gb/s 211-1 PRBS generators in SiGe bipolar technology[J]. IEEE Journal of Solid-State Circuits, 2005, 40(10): 2118-2125.[2] DICKSON T O, LASKIN E, KHALID L, et al. An 80-Gb/s 231-1 pseudorandom binary sequence generator in SiGe BiCMOS technology[J]. IEEE Journal of Solid-State Circuits, 2005, 40(12): 2735-2745.[3] KJELLBERG T, HALLIN J, SWAHN T. 104 Gb/s 2″-1 and 110Gb/s 2-1 PRBS generator inInP HBT technology[C]// International Conference on Solid-State Circuits. San Francisco, USA: IEEE, 2006: 2160.[4] DICKSON T, LASKIN E, KHALID L, et al. A 72 Gb/s 2/sup 31/-1 PRBS generator in SiGe BiCMOS technology[C]// International Conference Solid-state Circuits. San Francisco, USA: IEEE, 2005: 219.[5] THYAGARAJAN S V, KANG S, NIKNEJAD A M. A 240 GHz fully integrated wideband QPSK receiver in 65 nm CMOS[J]. IEEE Journal of Solid-State Circuits, 2015, 50(10): 1-13.[6] SINGH U, LI Lijun, GREEN M M. A 34 Gb/s distributed 2∶1 MUX and CMU using 0.18 μm CMOS[J]. IEEE Journal of Solid-State Circuits, 2006, 41(9): 2067.[7] KANDA K, YAMAZAKI D, YAMAMOTO T, et al. 40 Gb/s 4∶1 MUX/1∶4 DEMUX in 90nm standard CMOS[C]// International Conference on Solid-State Circuits. San Francisco, USA: IEEE, 2005: 152.[8] CHEN M G, NOTTHOFF J K. A 3.3-V 21-Gb/s PRBS generator in AlGaAs/GaAs HBT technology[J]. IEEE Journal of Solid-State Circuits, 2000, 35(9): 1266-1270.[9] KIM J K, KIM J, JEONG D K. A 20-Gb/s full-rate 27-1 PRBS generator integrated with 20-GHz PLL in 0.13-μm CMOS[C]// International Conference on Solid-State Circuits. Fukuoka, Japan: IEEE, 2008: 221-224.[10] DEFERM N, REYNAERT P. A 120 GHz fully integrated 10 Gb/s short-range star-QAM wireless transmitter with on-chip bondwire antenna in 45 nm low power CMOS[J]. IEEE Journal of Solid-State Circuits, 2014, 49(7): 1606-1616.。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

F. Viglione, G. Masera, G. Piccinini, M. Ruo Roch, M. Zamboni Dipartimento di Elettronica - Politecnico di Torino - Torino, ITALY Abstract

2. The SISO algorithm

In the case of concatenated codes, the decoding is split into a number of subproblems equal to the number of the constituent codes. In order to exploit entirely the properties of turbo codes, single decoders must exchange soft information. This soft quantity is the sequence of the distribution of probability, conditioned by the received signal and by the knowledge of the code [7]. A solution to the decoding problem is a modification of the traditional Viterbi’s algorithm into the soft output Viterbi algorithm (SOVA) , which generates the needed soft information: this algorithm is a suboptimal solution. A different approach to the problem is represented by the a posteriori probability (APP) algorithms: the SISO (Soft Input Soft Output) algorithm [8] and

u

Encoder

c

where sS , sE , u and c depend on e. The decoder must evaluate expressions like:

"

a = log

π(c) π(c;O) SISO

π(u;O) π(u)

∑ expfaig

i

L

:

(7)

This type of relation could be approximated with the maximum of ai ; better performances are obtained with a

Very low bit error rate has become an important constraint in high performance communication systems that operate at very low signal to noise ratios: due to their impressive coding gains, turbo codes have been proposed for several applications, although they suffer a large decoding delay. This paper presents the design of a turbo decoder with high performances in terms of throughput implemented using TSPC (True Single Phase Clocking) logic family. In order to achieve the best compromise between cost (in terms of area) and throughput, several architectural solutions have been analyzed. The whole system and in particular its core, the SISO module, has been verified through VHDL simulations. HSPICE simulations show that the system can operate with a 1 GHz clock and thus it can reach a throughput of 50 Mbit/s. among single encoders: an interleaver is a memory in which data are read and written in different orders. There are two principal schemes of connection: parallel concatenated convolutional codes (PCCC, the “original” turbo codes) and serially concatenated convolutional codes (SCCC). PCCC has been used in several cases, while SCCC has been used fewer. However, SCCC have been shown to yield performance comparable, and in some cases superior, to turbo codes [5]. The decoder consists in a network of single decoders correspondent to the encoder network. Each single decoder is a soft decoder providing an index of reliability (soft information) of the decoded bits (hard information). The whole soft decoder operates in an iterative way and the decoding process is stopped when the wished level of reliability is reached. Better correction performance are obtained as the iteration number is increased; however a large number of iterations has a negative effect on both decoding speed and latency (it is a fact that the latency of turbo codes is considered unacceptable in some telephony applications). In this paper we present the VLSI design of a fast SCCC decoder with short decoding delay and high throughput. Several architectures have been analyzed in order to choose the best solution for the decoder; the selected architecture has been implemented making use of TSPC [6] logic library operating at 1 GHz.

1. Introduction

Several applications need high coding gains and performances closed to theoretical Shannon’s limit in terms of bit error rate. High gains and performances can be achieved using block codes or convolutional codes with long constraint length: the use of these codes often results in very time consuming decoding algorithms. Concatenated codes have the advantage of dividing the encoding/decoding process in several, simpler steps: inside this family of codes, the most important ones are the convolutional concatenated codes, also called “Turbo codes” [1], which have been proved as the most powerful solution for high coding gain applications. Recently, turbo codes have been proposed for satellite and deep-space communications [2], such as in the ESA’s mission Rosetta. Other applications of turbo codes are in wireless communications, such as the third generation of mobile communications (UMTS) and in standard protocols for disk drivers [3]. A concatenated encoder is composed of two or more recursive and systematic convolutional encoders connected in an encoding network [4]. Interleaving blocks are placed