NOISE-TOLERANT DYNAMIC CIRCUIT DESIGN Abstract Noise in deep submicron technology combine

诺蒂菲尔 智能 可寻址设备的监视模块(FMM-1(A), FMM-101(A) 说明书

FMM-1(A), FMM-101(A),FZM-1(A) & FDM-1(A)Monitor Modules with FlashScan®DN-6720:EGeneralFour different monitor modules are available for Notifier’sintelligent control panels for a variety of applications. Monitormodules sup ervise a circuit of dry-contact inp ut devices,such as conventional heat detectors and p ull stations, ormonitor and p ower a circuit of two-wire smoke detectors(FZM-1(A)).FMM-1(A) is a standard-sized module (typically mounts to a4" [10.16 cm] square box) that sup ervises either a Style D(Class A) or Style B (Class B) circuit of dry-contact inp utdevices.FMM-101(A) is a miniature monitor module a mere 1.3"(3.302 cm) H x 2.75" (6.985 cm) W x 0.65" (1.651 cm) D thatsup ervises a Style B (Class B) circuit of dry-contact inp utdevices. Its comp act design allows the FMM-101(A) to bemounted in a single-gang box behind the device it monitors.FZM-1(A) is a standard-sized module that monitors andsupervises compatible two-wire, 24 volt, smoke detectors ona Style D (Class A) or Style B (Class B) circuit.FDM-1(A) is a standard-sized dual monitor module that mon-itors and supervises two independent two-wire Style B (Class B) dry-contact initiating device circuits (IDCs) at two separate, consecutive addresses in intelligent, two-wire systems. FlashScan® (U.S. Patent 5,539,389) is a communication protocol developed by NOTIFIER that greatly increases the speed of communication between analog intelligent devices. Intelligent devices communicate in a grouped fashion. If one of the devices within the group has new information, the panel CPU stops the group poll and concentrates on single p oints. The net effect is resp onse sp eed greater than five times that of other communication protocols.FMM-1(A) Monitor Module•Built-in typ e identification automatically identifies this device as a monitor module to the control panel.•Powered directly by two-wire SLC loop. No additional power required.•High noise (EMF/RFI) immunity.•SEMS screws with clamping plates for ease of wiring.•Direct-dial entry of address: 01 – 159 on FlashScan loops;01 – 99 on CLIP loops.•LED flashes green during normal operation (programma-ble option) and latches on steady red to indicate alarm. The FMM-1(A) Monitor Module is intended for use in intelli-gent, two-wire systems, where the individual address of each module is selected using the built-in rotary switches. It pro-vides either a two-wire or four-wire fault-tolerant Initiating Device Circuit (IDC) for normally-open-contact fire alarm and supervisory devices. The module has a panel-controlled LED indicator. The FMM-1(A) can be used to replace MMX-1(A) modules in existing systems.FMM-1(A) A PPLICATIONSUse to monitor a zone of four-wire smoke detectors, manual fire alarm pull stations, waterflow devices, or other normally-open dry-contact alarm activation devices. May also be used to monitor normally-op en sup ervisory devices with sp ecial supervisory indication at the control panel. Monitored circuit may be wired as an NFPA Style B (Class B) or Style D (Class A) Initiating Device Circuit. A 47K Ohm End-of-Line Resistor (p rovided) terminates the Style B circuit. No resistor is required for supervision of the Style D circuit.FMM-1(A) O PERATIONEach FMM-1(A) uses one of the available module addresses on an SLC loop. It responds to regular polls from the control panel and reports its type and the status (open/normal/short) of its Initiating Device Circuit (IDC). A flashing LED indicates that the module is in communication with the control panel. The LED latches steady on alarm (subject to current limita-tions on the loop).FMM-1(A) S PECIFICATIONSNominal operating voltage: 15 to 32 VDC.Maximum current draw: 5.0 mA (LED on).Average operating current: 375 μA (LED flashing), 1 com-munication every 5 seconds, 47k EOL.Maximum IDC wiring resistance: 1500 Ohms.Maximum IDC Voltage: 11 Volts.EOL resistance: 47K Ohms.Temperature range: 32°F to 120°F (0°C to 49°C). Humidity range: 10% to 93% noncondensing. Dimensions: 4.5" (11.43 cm) high x 4" (10.16 cm) wide x1.25" (3.175 cm) deep. Mounts to a 4" (10.16 cm) square x2.125" (5.398 cm) deep box.FMM-1(A) (Type H)6999cov.jpgFMM-101(A) Mini Monitor Module•Built-in typ e identification automatically identifies this device as a monitor module to the panel.•Powered directly by two-wire SLC loop. No additional power required.•High noise (EMF/RFI) immunity.•Tinned, stripped leads for ease of wiring.•Direct-dial entry of address: 01 – 159 on FlashScan loops;01 – 99 on CLIP loops.The FMM-101(A) Mini Monitor Module can be installed in a single-gang junction directly behind the monitored unit. Its small size and light weight allow it to be installed without rigid mounting. The FMM-101(A) is intended for use in intelligent, two-wire systems where the individual address of each mod-ule is selected using rotary switches. It provides a two-wire initiating device circuit for normally-op en-contact fire alarm and security devices. The FMM-101(A) can be used to replace MMX-101(A) modules in existing systems.FMM-101(A) A PPLICATIONSUse to monitor a single device or a zone of four-wire smoke detectors, manual fire alarm pull stations, waterflow devices, or other normally-op en dry-contact devices. May also be used to monitor normally-open supervisory devices with spe-cial supervisory indication at the control panel. Monitored cir-cuit/device is wired as an NFPA Style B (Class B) Initiating Device Circuit. A 47K Ohm End-of-Line Resistor (provided) terminates the circuit.FMM-101(A) O PERATIONEach FMM-101(A) uses one of the available module addresses on an SLC loop. It responds to regular polls from the control panel and reports its type and the status (open/ normal/short) of its Initiating Device Circuit (IDC).FMM-101(A) S PECIFICATIONSNominal operating voltage: 15 to 32 VDC.Average opera t ing curren t: 350 μA, 1 communication every 5 seconds, 47k EOL; 600 μA Max. (Communicating, IDC Shorted).Maximum IDC wiring resistance: 1500 Ohms.Maximum IDC Voltage: 11 Volts.Maximum IDC Current: 450 μA.EOL resistance: 47K Ohms.Temperature range: 32°F to 120°F (0°C to 49°C). Humidity range: 10% to 93% noncondensing. Dimensions: 1.3" (3.302 cm) high x 2.75" (6.985 cm) wide x 0.65" (1.651 cm) deep.Wire length: 6" (15.24 cm) minimum.FZM-1(A) Interface Module•Supports compatible two-wire smoke detectors.•Supervises IDC wiring and connection of external power source.•High noise (EMF/RFI) immunity.•SEMS screws with clamping plates for ease of wiring.•Direct-dial entry entry of address: 01 – 159 on FlashScan loops, 01 – 99 on CLIP loops.•LED flashes during normal op eration; this is a p rogram-mable option.•LED latches steady to indicate alarm on command from control panel.The FZM-1(A) Interface Module is intended for use in intelli-gent, addressable systems, where the individual address of each module is selected using built-in rotary switches. This module allows intelligent panels to interface and monitor two-wire conventional smoke detectors. It transmits the status (normal, op en, or alarm) of one full zone of conventional detectors back to the control p anel. All two-wire detectors being monitored must be UL comp atible with the module. The FZM-1(A) can be used to replace MMX-2(A) modules in existing systems.FZM-1(A) A PPLICATIONSUse the FZM-1(A) to monitor a zone of two-wire smoke detectors. The monitored circuit may be wired as an NFPA Style B (Class B) or Style D (Class A) Initiating Device Cir-cuit. A 3.9 K Ohm End-of-Line Resistor (provided) terminates the end of the Style B or D (class B or A) circuit (maximum IDC loop resistance is 25 Ohms). Install ELR across termi-nals 8 and 9 for Style D application.FZM-1(A) O PERATIONEach FZM-1(A) uses one of the available module addresses on an SLC loop. It responds to regular polls from the control panel and reports its type and the status (open/normal/short) of its Initiating Device Circuit (IDC). A flashing LED indicates that the module is in communication with the control panel. The LED latches steady on alarm (subject to current limita-tions on the loop).FZM-1(A) S PECIFICATIONSNominal operating voltage: 15 to 32 VDC.Maximum current draw: 5.1 mA (LED on).Maximum IDC wiring resistance: 25 Ohms.Average operating current: 270 μA, 1 communication and 1 LED flash every 5 seconds, 3.9k eol.EOL resistance: 3.9K Ohms.Ex ernal supply vol age (be ween Terminals T10 and T11):•DC voltage: 24 volts power limited.•Ripple voltage: 0.1 Vrms maximum.•Current: 90 mA per module maximum.Temperature range:32°F to 120°F (0°C to 49°C).Humidity range: 10% to 93% noncondensing. Dimensions: 4.5" (11.43 cm) high x 4" (10.16 cm) wide x1.25" (3.175 cm) deep. Mounts to a 4" (10.16 cm) square x2.125" (5.398 cm) deep box.FDM-1(A) Dual Monitor ModuleThe FDM-1(A) Dual Monitor Module is intended for use in intelli-gent, two-wire systems. It p rovides two indep endent two-wire initiating device circuits (IDCs) at two sep arate, consecutive addresses. It is capable of monitoring normally open contact fire alarm and supervisory devices; or either normally open or nor-mally closed security devices. The module has a single panel-controlled LED.NOTE: The FDM-1(A) provides two Style B (Class B) IDC circuits ONLY. Style D (Class A) IDC circuits are NOT supported in any application.FDM-1(A) S PECIFICATIONSNormal operating voltage range: 15 to 32 VDC. Maximum current draw: 6.4 mA (LED on).Average operating current: 750 μA (LED flashing). Maximum IDC wiring resistance: 1,500 Ohms.Maximum IDC Voltage: 11 Volts.Maximum IDC Current: 240 μAEOL resistance: 47K Ohms.Temperature range: 32° to 120°F (0° to 49°C).Humidity range: 10% to 93% (non-condensing). Dimensions: 4.5" (11.43 cm) high x 4" (10.16 cm) wide x1.25" (3.175 cm) deep. Mounts to a 4" (10.16 cm) square x2.125" (5.398 cm) deep box.FDM-1(A) A UTOMATIC A DDRESSINGThe FDM-1(A) automatically assigns itself to two address-able points, starting with the original address. For example, if the FDM-1(A) is set to address “26”, then it will automatically assign itself to addresses “26” and “27”.NOTE: “Ones” addresses on the FDM-1(A) are 0, 2, 4, 6, or 8 only. Terminals 6 and 7 use the first address, and terminals 8 and 9 use the second address.InstallationFMM-1(A), FZM-1(A), and FDM-1(A) modules mount directly to a standard 4" (10.16 cm) square, 2.125" (5.398 cm) deep, electrical box. They may also be mounted to the SMB500 surface-mount box. Mounting hardware and installation instructions are provided with each module. All wiring must conform to ap p licable local codes, ordinances, and regula-tions. These modules are intended for p ower-limited wiring only.The FMM-101(A) module is intended to be wired and mounted without rigid connections inside a standard electri-cal box. All wiring must conform to ap p licable local codes, ordinances, and regulations.Agency Listings and ApprovalsIn some cases, certain modules may not be listed by certain approval agencies, or listing may be in process. Consult fac-tory for latest listing status.•UL: S635.•ULC: S635.•FM Approved.•CSFM: 7300-0028:0219, 7165-0028:0224,7165-0028:0243.•MEA: 457-99-E.•U.S. Coast Guard: 161.002/50/0 (NFS2-640, NFS2-320, NFS2-3030).•Lloyd’s Regis t er: 11/600013 (NFS2-640, NFS2-320, NFS2-3030).•Fire Dept. of New York: COA #6121 (NFS2-640, NFS-320), COA# 6114 (NFS2-3030).Product Line InformationNOTE: “A” suffix indicates ULC-listed model.FMM-1(A): Monitor module.FMM-101(A): Monitor module, miniature.FZM-1(A): Monitor module, two-wire detectors.FDM-1(A): Monitor module, dual, two indep endent Class B circuits.SMB500: Optional surface-mount backbox.NOTE: See installation instructions and refer to the SLC Wiring Manual, PN 51253.!CAUTION:Avoid duplicating addresses on the system.FlashScan® and NOTIFIER® are registered trademarks and FireWatch™ isa trademark of Honeywell International Inc.©2015 by Honeywell International Inc. All rights reserved. Unauthorized useof this document is strictly prohibited.This document is not intended to be used for installation purposes. Array We try to keep our product information up-to-date and accurate.We cannot cover all specific applications or anticipate all requirements.All specifications are subject to change without notice.For more information, contact Notifier. Phone: (203) 484-7161, FAX: (203) 484-7118.。

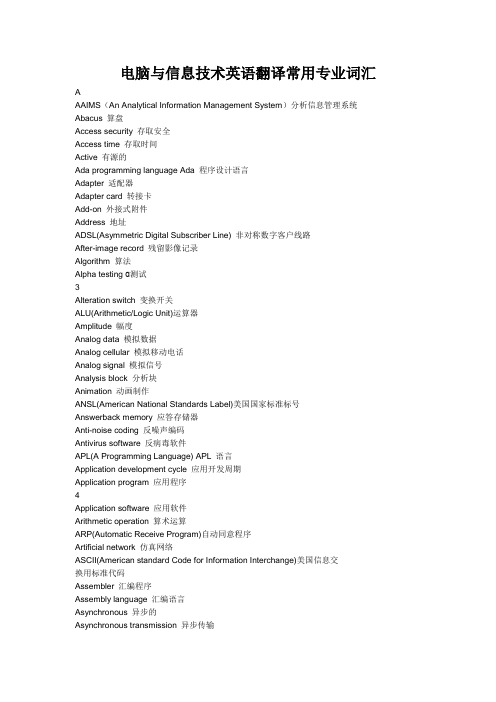

电脑与信息技术语翻译常用专业词汇

这里汇聚了计算机和网络技术领域的大部分英语词汇和详细解说,如果要查询相关词汇,你可以点此word文档工具栏的“编辑”,找到“查找”,然后点开输入你要查询的词汇就可以查询了。

AAAIMS(An Analytical Information Management System)分析信息管理系统Abacus 算盘Access security 存取安全Access time 存取时间Active 有源的Ada programming language Ada 程序设计语言Adapter 适配器Adapter card 转接卡Add-on 外接式附件Address 地址ADSL(Asymmetric Digital Subscriber Line) 非对称数字客户线路After-image record 残留影像记录Algorithm 算法Alpha testing ɑ测试3Alteration switch 变换开关ALU(Arithmetic/Logic Unit)运算器Amplitude 幅度Analog data 模拟数据Analog cellular 模拟移动电话Analog signal 模拟信号Analysis block 分析块Animation 动画制作ANSL(American National Standards Label)美国国家标准标号Answerback memory 应答存储器Anti-noise coding 反噪声编码Antivirus software 反病毒软件APL(A Programming Language) APL 语言Application development cycle 应用开发周期Application program 应用程序4Application software 应用软件Arithmetic operation 算术运算ARP(Automatic Receive Program)自动接受程序Artificial network 仿真网络ASCII(American standard Code for Information Interchange)美国信息交换用标准代码Assembler 汇编程序Assembly language 汇编语言Asynchronous 异步的Asynchronous transmission 异步传输ATM(Asynchronous Transfer Mode) 异步传输模式ATM(Automated Teller Machine)自动出纳机Attribute 属性Auctions on the web 网上拍卖Audio board 声板5Audio file 声音文件Audio input device 声音输入装置Audio-player 播放Audit program 审查程序Auditing system 审查系统Authoring system 写作系统6BBackbone system 主干系统Backup file 备份文件Backward compatibility 反向兼容性Backward recovery 向后恢复Band printer 带式打印机Bandwidth 带宽Bandwidth limitation 带宽限制Bar code 条形码Bar-code reader 条形码读出器Basic exchange format 基本交换格式BASIC programming language BASIC 程序设计语言Batch processing 批处理Beeper 传呼机7Beta testing β测试Binary digit 二进制数字Binary file 二进制文件Binary number system 二进制数字系统Binary system 二进制BIOS(Basic Input/Output System)基本输入/输出系统Bit 量,位Bit(binary digit)位,二进制位,比特Bit-mapped display screen 位映像显示器Block check 块检验Blocking software 封锁软件Bookmark 书签Bootleg version 盗版BPS(Business Professional System) 商业专用系统Bridge 网桥8Broadcast image 广播图象Browser 浏览程序Building blocks 组件Built-in function 内部功能Bus 总线Bus network 总线网络Bus slot 总线槽Business terminal equipment 商务终端设备Button 按扭Byte 字节,位组9CC programming language C 程序设计语言C++ programming language C++程序设计语言Cable length 电缆长度Cable modem 电缆调制解调器Cache memory 超高速缓冲存储器CAD(Computer-Aided Design) 计算机辅助设计CADD(Compute-Aided Design and Drafting) 计算机辅助设计与制图Call-back system 回叫系统CAM(Computer-Aided Manufacturing) 计算机辅助生产Capacity 容量Carrier wave 载波Cartridge tape 盒式磁带CASE(Computer-Aided Software Engineering) 计算机辅助软件工程10CBT(Computer-Based Training) 利用计算机的训练CCD(Charge Coupled Device)电荷藕合器件CD writer 刻录机CDC(Code-Directing Character) 代码引导字符CDP(Certified Data Processor)合格数据处理程序Cell 单元,细胞,信元Cell address 单元地址Cell pointer 单元指示器CEO(Chip Enable Output) 芯片启动输出CERT(Character Error Rate Tester) 字符出错率测试程序Chain printer 链式打印机Channel command 通道命令Character 字符Character-recognition 字符识别Chat room 聊天室11Check bit 校验位,检验位Child record 子记录Chip 芯片,晶片Circuit switching 电路转接,线路交换CIS(Communication Information System) 通信信息(情报)系统Clear entry 消除输入Click 点击Client 客户,委托程序,委托进程,客户机Client-server 客户服务器Clipboard 剪贴板Clouds 云Cluster 簇,束,线束,群集Coaxial tree network 同轴树状网络COBOL programming language COBOL 程序设计语言Coding 编码,编程序12Collision 冲突Color display screen 彩色显示屏Communication 通信Communication parties 传输单元Communications channel 通信信道Communications controller 通信控制器Communications hardware 通信硬件Communications network 通信网络Communications satellites 通信卫星Communications server 通信服务器Communications service 通信业务Communications software 通信软件Communications technology 通信技术Compatibility 兼容性,一致性,互换性Compiler 编译程序13Component 分量,成分,元件,组件,部件Compression 压缩Computer 计算机Computer-based information system 计算机信息系统Computer crime 计算机犯罪Computer industry 计算机行业Computer literacy 计算机扫盲Computer online service 计算机联机服务Computer professional 计算机专业人员Computer programmer 计算机程序设计员Concentration 集中Concentrator 集中器,集线器Concurrent-use license 并行使用许可证Connection 连接Connectivity 连通性,连接性14Connectivity diagram 连通图表Contact 接触点Control structure 控制结构Control unit 控制器,控制部件Controller card 控制器插件Coprocessor 协同处理程序,协同处理机Copy command 复制命令Copyright 版权Copyright protection 版权保护Counterfeit software 盗版软件Courseware 课件CPU(Central Processing Unit) 中央处理机Cracker 黑客CRT(Cathode Ray Tube) 阴极射线管CTS(Clear To Send) 清除发送15Cursor 光标Cursor-movement key 光标移动键Custom software 客户软件Cut command 剪切命令Cyberculture 计算机文化,控制论优化Cybernation 计算机控制化16DDaisy chain 菊链DAT(Data Acquisition Test) 数据采集测试Data access method 数据存取法Data acquisition 数据采集Data compression 数据压缩Data dictionary 数据字典Data file 数据文件Data flow diagram 数据流程图Data integrity 数据完整性Data manipulation language 数据操纵语言Data mining 数据开采Data recovery 数据恢复Data redundancy 数据冗余Data storage hierarchy 数据存储层次17Data transmission 数据传输Data transmission factor 数据传输系数Data warehouse 数据仓库Database 数据库Database server 数据库服务器Database software 数据库软件DBA(Data Base Administrator) 数据库管理程序DBMS(Data Base Management System) 数据库管理系统Debugging 调试Decision making system 判定系统,决策系统Decision table 判定表Dedicated computer 专用计算机Default value 缺省值,系统设定值Delete 删除Democratic network 共同控制网络18Design 设计Desk checking 桌面检验Desktop accessory 桌面附件Desktop publication system 桌面出版系统Developing information system 信息开发系统Dialog box 对话框Dial-up connection 拨号上网Dial-up Internet communication 拨号网间通信Digital 数码的Digital camera 数码照相机Digital cellular phone 数字移动电话Digital signal 数字信号Digital signal processor 数字信号处理器Digital signature 数字签名Digitized speech 数字化语音19DIMS(Data Information and Manufacturing system) 数据信息和制造系统Direct access storage 直接存取存储器,直接访问存储器Direct file organization 直接文件组织Direct implementation 直接实现Direct synchronous multiplexing 直接同步复用Directory 目录,号码表Disk 磁盘Disk drive 磁盘驱动器Diskette 软磁盘,软盘Display 显示Display screen 显示屏幕Disrupt 使混乱,破坏,分裂,瓦解Distance learning 远程学习Distributed database 分布式数据库Disturbance 干扰20DM(Data Memory) 数据存储器DNS(Domain Naming System) 域命名系统Document 文件,资料,文献,文卷Document file 资料文件Documentation 文件编制,资料,文档DOS(Disk Operating System) 磁盘操作系统Dot 点Dot-matrix printer 点阵打印机Download 下载Downsizing 规模缩小化Downward compatibility 向下兼容性Draft-quality 粗劣的印刷质量,草稿字体印刷质量DRAM(Dynamic Random Access Memory) 动态随机存取存储器Drawing program 绘图程序Driver 驱动器21Drum printer 鼓式打印机Drum scanner 鼓形扫描器DSS(Decision Support System) 决策支援系统DTP(Data Transmission Protocol) 数据传送协议Dumb terminal 哑终端,简易终端DVP(Data Validation Program) 数据验证程序Dynamic linking 动态链接22EEBCDIC(Extended Binary Coded Decimal Interchange) 扩充的二-十进制交换码E-cash 电子货币E-commerce 电子商务EDI(Electronic Data Interchange) 电子数据交换EEPROM(Electrically Erasable Read Only Memory) 电可擦只读存储器EIC(External Interface Control) 外部借口控制EIS(External Interrupt Support) 外部中断支援Electroluminescent display 电致发光显示屏Electromagnetic spectrum 电磁光谱Electronic conference 电子会议Electronic image 电子图象Electronic network 电子网络23Electronic secretary 电子秘书Electronic ticketing machine 电子售票机Electronic tutor 电子教案装置Electrostatic plotter 静电绘图机Elementary field 基本字段ELF(Extensible Language Facility) 可扩充的语言功能E-mail 电子邮件Embedded computer 嵌入式计算机Emulation 仿真,仿效Encapsulation 封闭,封装,密封Encryption 加密,编密码End-to-end delay 端到端的时延End-to-end digital connectivity 端到端的数字连接End-user 终端用户ENIAC(Electronic Numerical Integrator and Calculator) 电子数字积分24器和计算器Enter key 输入键EPL(Encoder Programming Language) 编码器程序设计语言EPROM(Erasable Programmable Read Only Memory) 可擦可编程只读存储器EPSS(Error Processing Sub-system) 错误处理子系统Ergonomics 人类工程学Error correction 纠错法ESS(Electronic Switching System) 电子交换系统Evaluation system 评价系统Even parity 偶数奇偶校验Exchange service 交换业务Executable 可执行文件Execution cycle 执行周期Execution program 执行程序Expansion bus 扩展总线25Expansion card 扩充插件卡Expansion slot 扩展槽Expert system 专家系统External hard disk drive 外部硬盘驱动器External modem 外部调制解调器26FFAT(File Allocation Table) 文件分配表Fault freedom 容错性能Fault tolerant system 容错系统Fax 传真Fax machine 传真机FCB(File Control Block) 文件控制块Feasibility study 可行性研究,可能性研究FEC(Forward Error Correction) 向前纠错Fiber-optic cable 光缆Field 字段,场,域Field protect 字段保护Fifth-generation programming language 第五代程序设计语言File 文件27File extension 文件扩充File management system 文件管理系统File name 文件名File server 文件服务程序File virus 文件病毒Filter 过滤,滤波Financial planning system 财务规划系统Find command 查找命令Finder 寻找程序,定位程序,录像器Fingerprint security system 指纹安全系统Firewall 防火墙Firmware 固件Fixed disk drive 固定磁盘驱动器Flatbed plotter 平板绘图仪Flatbed scanner 平板扫描仪28Flat-panel display 平面显示器Flat-panel technique 平面技术Flexible telecommunication networking 灵活的通信联网Floppy disk 软磁盘FLOPS(Floating-point Operations Per Second) 每秒浮点运算次数Flowchart 流程图Font 字型,字体Format selection 格式选择Formatting 格式化,格式编排Formula 公式FORTH programming language FORTH 程序设计语言Forward recovery 正向恢复Fourth-generation programming language 第四代程序设计语言Fragmenting 分割29Frame grabber 帧接受器,帧捕获器Free ware 免费软件Frequency 频率Front-end processor 前端处理机FTP(File Transfer Protocol)文件传送协议Full-duplex 全双工Function 功能,函数,作用Function key 功能键Fuzzy logic 模糊逻辑30GGame port 博弈端口Garbage 无用信息Gateway 关口,网间连接GDS(Group Display System) 群显示系统Genealogy 家谱学,系统GES(General Edit System) 通用逻辑系统GIS(Geographic Information System) 几何图形信息系统Global communication 全球通信GPS(Global Positioning System) 全球定位系统Grammar checker 语法检验程序Graphics 图形学,制图技术Graphics accelerator 图形加速器Graphics coprocessor 图形协同处理程序31Grid 网格,坐标网络Gross index 粗索引Groupware 群件GUI(Graphical User Interface) 图形用户接口32HHacker 黑客Half-duplex transmission 半双工传输Handheld scanner 手持式扫描仪Handshaking 信号交换,接续Hard disk 硬磁盘Hard return 硬回车Hard-copy terminal 硬拷贝终端Hardware 硬件Hardware compatibility 硬件兼容性HDTV(High Definition Television) 高分辨率电视Help menu 求助菜单,求助工程单Head-mounted display 头盔式显示器Hidden computer 隐式计算机33Hierarchical database 分级数据库Hierarchy 分级,分层,层次Hierarchy chart 分级图表High resolution 高分辨率High-level programming language 高级程序设计语言Hold 握住Home directory 主目录Home network 本地网络Home record 引导记录,起始记录Host 主机Host adaptation 主机适应性Host computer 主计算机Host operating system 主操作系统Host-to-host 主机到主机HTML(Hyper text Markup Language) 超文本标记语言34Hybrid network 混合式网络HTTP(Hypertext Transfer Protocol) 超级文本传输协议Hyperlink 超级链接Hypertext 超文本35IIcon 图符Identification system 识别系统Image file 映像文件Imaging system 成像系统IML(Initial Micro-code Load) 初始微码装入Impact 影响,冲击Impact printer 击打式打印机Importing file 输入文件Incremental backup 增量备份法Indexed file organization 索引文件组织Inference engine 推理机Information 信息,情报Information capacity 信息容量36Information function 信息函数Information management 信息管理Information overload 信息超载Information system 信息系统Information technology 信息技术Information transmission system 信息传输系统Information unit 信息单位Information utility 实用程序,信息应用程序,信息公用设施Inheritance 继承Initialize 初始化Ink-jet plotter 喷墨绘图仪Ink-jet printer 喷墨印刷机Input control 输入控制器Input device 输入设备Input hard ware 输入硬件37Inquiry and communication system 查询与通信系统Insert 插入Insertion point 插入点Install 安装,建立Instruction cycle 指令周期Integrated circuit 集成电路Integrated software package 组合软件包Intellectual property 知识产权Intelligent robot 智能机器人Intelligent terminal 智能终端Interactive presentation 交互式演示Inter activity 交互性Interface 接口Intermediate node 中间网点Internal bus 内部总线38Internal hard disk drive 内部硬盘驱动器Internal modem 内部调制解调器International standard interface 国际标准接口Internet 互联网,信息网络实体Interpreter 解释程序,翻译机,转换机ISAM(Indexed Sequential Access Method) 索引顺序存取法ISDN(Integrated Services Digital Network) 综合服务数字网络Isolation 隔离,绝缘ISP(Internally Stored Program) 内部存储程序ISP(Internet Service Provider) 因特网服务提供商39JJAD(Joint Application Design) 联合应用程序设计Jerk 乱窜Jitter 抖动Job file 作业文件Job management 作业管理程序Junk mail 垃圾邮件Justification range 调整范围40KKey field 关键字字段Key search 关键字查找Keyboard 键盘Keyboard console 键盘控制台Kilobyte 千字节Knowledge base 知识库Knowledge engineer 知识工程师Knowledge engineering 知识工程Knowledge system 知识系统41LLanguage translator 语言翻译程序Large-scale integrated circuit 大规模集成电路Laser 激光,激光器Laser communication 激光通信系统Laser printer 激光打印机Latency 延迟,执行时间Latent image 潜像Law 法律Layer 分层LCD(Liquid Crystal Display) 液晶显示器LEO(Low Earth Orbit) 近地轨道License 许可证Light pen 光笔Line printer 行式打印机42Line terminal multiplexer 终端复用器Linear 线性的,一次的Link 连接,连线,链接Linkage instruction 连接命令LISP programming language LISP 程序设计语言Live conversation 实际的对话Load 装入,加载Load server 加载服务器Local-area network 局域网Logic bomb 逻辑炸弹(病毒)Logic error 逻辑错误Logical operation 逻辑操作LOGO programming language LOGO 程序设计语言Look through 搜寻43Loop 循环,回路,环路Loss less 无损耗Lossy 有损耗的,有损失的44MMAC(Memory access Controller) 存储器存取控制器Machine cycle 机器周期Machine language 机器语言Macintosh (苹果公司生产的一种型号的)计算机Macro 宏,宏指令,宏定Macro virus 宏病毒Magnetic tape 磁带Magneto optical disk 磁光盘Mail server 邮件服务器Mailing list 邮件列表Main memory 主存储器Mainframe computer 主计算机Maintenance 维护,维修MAN(Maintenance Alert Network) 维护警报网45Manager 管理程序,管理人员Manipulate 控制,操纵Manipulation 操纵,控制,处理,操作Manual function 手动功能,人工功能Manufacturing support system 制造支持系统Marker 标记符Marketing model 市场销售模型Mark-recognition device 标记识别装置Master file 主文件Mathematic characterization of continuous image 连续图象的数学表征MDA(Multi-Dimensional Analysis) 多维分析MDT(Modified Data Tag) 修改过的数据标志Meeting software 会议软件Mega 兆Memory cycle 存储周期46Mega byte 兆字节Megahertz 兆赫Member record 成员记录Memory 记忆存储,存储器Memory expansion card 存储器扩充卡Memory module 存储模块Menu bar 菜单条Menu-driven program generator 菜单驱动程序生成程序MED(Micro-Electronic Device) 微电子器件Meta-data 元数据MICR(Magnetic Ink Character Recognition) 磁性墨水字符识别Microcomputer 微型计算机Micro controller 微控制器Microprocessor 微处理器Microwave 微波47Middleware communication model 媒件通信模型MIDI(Music Instrument Digital Interface) 乐器数字接口Miniaturization 小型化MIPS(Million Instructions Per Second) 每秒百万条指令Mirror 镜像MIS(Management Information System) 信息管理系统MMX technology MMX 技术Model 模型,机样,型号Modem 调制解调器Module design 模块设计Monitor 监视器,监督Monitor mode 监控方式Monochrome display 单色显示Mouse 鼠标Mouse pointer 鼠标指示器48Moving pictures 活动图象MPP(Massively Parallel Processor) 巨型并行处理器Multifunction device 多功能装置Multimedia 多媒体Multimedia environment 多媒体环境Multipartite virus 复合性病毒Multiplexer 多路转接器Multiplexing 多路转换Multipoint line 多点线路Multi-port 多端口Multiprocessing 多重处理Multiprogramming 多道程序设计(控制)Multitasking 多任务Multi-user platform 多用户平台49NNarrow band services 窄带业务Nationwide network 全国范围的网络Natural language 自然语言Natural language processing 自然语言处理NC language processor NC 语言处理器Necessary bandwidth 必要带宽Net ware 网件Network 网络Network adapter 网络适配器Network computer 网络计算机Network database 网络数据库Network facilities resources 网络设备资源Network harms 网络损害50Network information resources 网络信息资源Network interface card (NIC) 网络接口卡Network piracy 网络盗版Network server 网络服务程序,网络服务器Networked hypertext protocol 网络超文本协议Neural network 神经网络Node 节点,网点Non-interacting control system 非交互式控制系统Non-procedural language 非过程语言Non-volatile chain 非易失链NOS(Network Operating System) 网络操作系统Null set 空集Numeric key 数字键51OOAS(Office Automation System) 办公自动化系统Object 目标,对象,结果,物体Object code 目标代码OCR(Optical Character Recognition) 光符识别Odd parity 奇数奇偶校Off-line equipment 脱机设备Off-line storage 脱机存储器Off-the-shelf software 现成的软件OLE(Object Linking and Embedding) 对象的链接与嵌入OMR(Optical Mark Recognition) 光标记识别Onboard 板载的One-level code 一级代码One-to-many 一对多的52Online processing 联机处理Online storage 联机存储器OODBS(Object Oriented Data Base System) 面向目标的数据库系统OOO(Out Of Order) 发生故障,次序混乱Open network 开放式网络Operating environment 操作环境,运行环境Operating system 操作系统Operation control 操作控制Operator 运算符,操作员Optical card 光卡Optical disk 光盘Optical Ethernet 光以太网Optimization 优化Optoelectronic receiver 光电子接收机Organization 机构,组织,结构,体系53Organization chart 组织图,结构图OS/360(Operating System/360) 360 型操作系统OSI(Open System Interconnection) 开放系统互连Output 输出Owner record 主记录,自由记录54PPackage 分组Packaged software 封装式软件包Packet 包,数据包,分组报文Packet switching 包交换Pager 页面调度程序Painting 涂色Parallel data transmission 并行数据传输Parallel implementation 并行执行Parallel port 并行端口Parallel processing 并行处理Parent record 母记录Parity bit 奇偶校验位Parity scheme 奇偶校验方案55PASCAL programming language PASCAL 程序设计语言Passive 无源的Passive network 无源网络Password 口令Path 路径PBX(Private Branch Exchange) 专用交换分机,用户交换机PC(Personal Computer) 个人计算机PC application software 个人计算机应用软件PC host operating system 个人计算机主机操作系统PCI(peripheral Component Interconnect)外围部件互连PCMCIA(Personal Computer Memory Card International Association) 个人电脑内存储卡国际协会PDA(Personal Digital Assistant) 个人数字助理PDL(Picture Description Language) 画面描述语言Peak 峰值56Peer-to-peer 层间,层到层PEM(Processing Element Memory) 处理单元存储器Perception system 感知系统Peripheral device 外围设备Personal finance software 个人财务软件Personal identification code 个人识别代码PERT chart editing PERT 图编辑PGP(Programmable Graphics Processor) 可编辑图形处理机Phonetic keyboard 语音键盘Photo-digital store 光数字存储器Photolithographic mask layer 光刻掩蔽层Physical storage 物理存储器PIM(Processor Interface Module) 处理程序接口模块PIN(Personal Identification Number) 个人识别号码Pixel store 像素存储器57PL/1 programming language PL/1 程序设计语言Platform position computer 平台位置计算机Plotter 绘图仪Plug and play system 即插即用系统Plug-in card 插件Pointing device 指示装置Point-of-sale terminal 销售点终端Point-to-point line 点对点线路,专用线Polymorphism 多形性,多机组合形势Pop-up menu 弹出选项单Port 端口,进出口Portable operating system 可移植操作系统Portable terminal 便携式终端POST(Power-on Self Test) 通电自检Power supply 电源,供电58PPP(Parallel Pattern Processor) 并行模式处理程序Precision 精确度Preliminary design 初步设计Presentation layer 表示层Presentation graphic 表示图形Presentation software 显示软件Preventive maintenance 预防性维护Previewing 预检,预览Primary storage 主存储器Print server 打印服务程序Printer 打印机Printing document 打印文档Privacy 保密性Procedural error 过程错误Procedural language 过程型语言59Procedure 过程,程序,步骤Process 处理,进程Process model 过程模型Processing 处理,加工Processing hardware 处理硬件Processor 处理程序,处理机Production language compiler 产生式语言编译程序Productivity 生产率Productivity tool 生产率工具Professional programmer 专业程序设计员Program 程序,计划,规划,方案Program file 程序文件Program flowchart 程序流程图Program independence 程序独立性Programmer 程序设计人员,编程器60Programming 程序设计,编程Programming language 程序设计语言Programming procedure 程序设计过程Project management software 工程工程管理,计划管理Project management software 工程工程管理软件PROLOG programming language PROLOG 程序设计语言Proprietary software 专有软件Proprietary system 专用系统Protocol 协议Prototype 样机,原型Prototyping 原型开发,样机研究Pseudo-code 伪代码Public communication carriers 公共通信载体Public domain 公用域Pull-down menu 下拉菜单61Pulse code modulation 脉冲码调制62QQBE(Query By Example) 仿效实例询问QIC(Quality Insurance Chain) 质量保证链Query 询问,查询Query facility 询问功能软件Query language 询问语言Query-and-reporting processor 询问和报告处理程序Quiet code 静止代码QWERTY keyboard QWERTY 键盘63RRAD(Rapid Access Device) 快速存取设备RAM(Random Access Memory) 随机存取存储器,内存Random access storage 随机存取存储器Random file organization 随机文件结构Raster graphics 光栅图形Reading 读,读取Real-time processing 实时处理Reasoning 推理,推论,推导Recalculation 重算Receiving entity 接收实体Receiving system 接收系统Record 记录Reference mark 参考标记64Reference model 参考模型Reference software 参考软件Refresh rate 更新率,刷新率Refreshable program 可刷新程序Regenerate 再生Register 寄存器Relational database 关系数据库Relational model 关系模型Release 释放Reliable 可靠的Reliability 可靠性Remote-control 遥控Remote device 远程设备Remote terminal 远程终端Removable hard disk 可移动硬盘65Repeater 中继器Repeater spacing 中继距离Replace command 替换命令Report generator 报告生成程序Resistor 电阻器Resolution 分辨率Retrieval performance 检索性能Return key 返回键RFI(Read Frequency Input) 读频率输入RGB monitor 红、绿、蓝显示器RIB(Resource Information Block) 资源信息块Ring network 环形网络RISC microprocessor RISC 微处理机Robot 机器人,自动仪Robotics 机器人学,机器人技术66Rollback 重新运行,重算ROM BIOS (Read-Only Basic Input/Output System) 只读存储器基本输入/输出系统Root record 根记录Router 发送程序,路由确定程序,路由器Row 行RPG(Report Program Generator) 报表程序生成程序RPS(Random Pattern Search) 随机模式搜索RS(Record Separator) 记录分隔符Run 运行Rupture 裂断,破裂67SSampling rate 取样率SAR(Source Address Register) 源地址寄存器Satellite 卫星,人造地球卫星Save 存储,保存Save area 保存区Scan 扫描Scanning device 扫描设备,扫描装置Scheduling software 调度软件Screen 屏幕Scrolling 卷动,滚动Scrubbing 除掉,刷去SCSI(Small Computer System Interface) 小型计算机系统接口SDL(System Development Language) 系统开发语言68Search 检索,查找Search command 查找命令Search engine 查找机Searching tool 搜寻工具Second-generation programming language 第二代程序设计语言Secondary application 辅助应用程序Secondary storage 辅助存储器,二级存储器Secondary storage sub system 辅助存储子系统Section overhead 段开销Sector 扇区,分段Security 安全性,保密性,安全措施Security system 安全系统Seek time 查找时间,定位时间Selection control 选择控制Semiconductor 半导体69Semiconductor memory 半导体存储器Semi-structured information 半结构化问题Sender 发送器Sensor 传感器Sequence control 顺序控制Sequential file organization 顺序文件组织Sequential storage 顺序存储器Serial 串行的Serial data transmission 串行数据传输Serial port 串行端口Serial processing 串行处理Server 服务器Service-independent network 与业务无关的网络Session layer 会话层Shared database 共享数据库70Sharing resource 共享资源SHELL software system SHELL 软件系统Shrink-wrapped multiprocessing operating system 精缩环绕多处理操作系统Silicon 硅SIMM(Single in-line Memory Module) 单列直插式存储模块Simplex transmission 单项传输Simulation programming language 模拟程序设计语言Simulator 模拟程序,模拟器Single user 用户Smalltalk programming language Smalltalk 程序设计语言Smart card 智能卡,收费卡Softcopy 软拷贝Software 软件,软设备Software engineer 软件工程师Software engineering 软件工程71Software license 软件许可证Software package 软件包,程序包Software piracy 软件非法翻印,软件侵犯版权Software suite 软件套件Software tool 软件工具Solid error 固定错误Sorting database 分类数据库Sound 声音Sound card 声卡Sound output 声音输出Source code 源代码Source date entry 源数据录入Source program file 源程序文件SPA(Signal Processing Auxiliary) 信号处理辅助设备Speech recognition system 语音识别系统72Speech synthesis 语音合成Speed 速度Speed up 加速Spelling checker 拼法检验程序Split 分发,分散Spreadsheet 电子数据表SQL(Structured Query Language) 结构化查询语言Squeeze 压缩Standardized port 标准化的端口Star network 星形网络STM(Short Term Memory) 短期存储器Storage 存储,存储器Storage hardware 存储硬件Strategic decision 战略性决策Streaming audio 流式音频73Streaming video 流式视频Stress 应力Structure chart 结构图Structured information 结构化信息Structured programming 结构化程序设计Structured walkthrough 结构化普查Subprogram 辅程序,子程序Supercomputer 巨型计算机Superconductor 超导体Supervisor 管理程序,主管人SVDF(Segmented Virtual Display File) 分段虚拟显示文件Swapping 交互,调动Switch 打开,开关,交换机Switching technique 交换技术Synchronous DXC 同步数字交叉连接74Synchronous transmission 同步传输Synchronous transmission system 同步传输系统Syntax 语法,句法Syntax error 语法错误System 系统,体制,装置System analysis 系统分析System analyst 系统分析员System clock 系统时钟System design 系统设计System development 系统开发System engineer 系统工程师System flowchart 系统流程图System implementation 系统实现方法System maintenance 系统维护System recovery 系统恢复75System software 系统软件System testing 系统测试System unit 系统单元76TTabulating machine 制机表Target variable 目标变量Task management 任务管理程序TCT(Terminal Control Table) 终端控制表Telecommunication 远程通信,电信Teleconference 电信会议Telemedicine 电视医疗Telephone network 电话网Telephony 电话学Telex network 用户电报网Tel net 电信网,远程通信网络Terminal 终端Terminal address 终端地址77Terminal emulation 终端仿真Test 测试,检验Test equipment 测试设备Text 正文,文本Text segment 正文段Textual messages 文本信息Thesaurus 主题词表,同义词汇Third-generation programming language 第三腮程序设计语言Through-mode fashion 贯通方式Time slicing 时间分片Time-sharing 分时,时间分配Tong-haul telecommunication system 长途通信系统Top-down program design 自顶向下程序设计Top management 主管,主控Touch screen 触屏TPI(Target Position Indicator) 目标位置指示器TPS(Transaction Processing System) 事务处理系统TPT(Time Priority Table) 时间优先表Track 磁道,轨道,声道Trackball 跟踪球Traffic segregation 流量隔离Transaction 事项,事务处理,交易Transaction file 细目文件,事项文件Transient error 瞬时错误Transmission 传输,发送,传送Transmission unit 传输单元Translate 转换Tributary signals 支路信号Trojan horse 特洛伊木马True color 真彩色79Tuple 元组,字节组Turing test 图灵测试Twisted-pair wire 绞合线Typeface 字样80UUndo command 作废命令Unexpected halt 意外停机Unicode 单一代码UNIVAC(Universal Automatic Computer) 通用自动计算机Universal access 统一的接入Universal product code 通用产品代码Universally 普遍地,通用地UNIX operating system UNIX 操作系统Unprotected field 非保护字段Unstructured file 非结构文件Unstructured information 非结构信息UPS(Uninterruptible Power Supply) 不间断供电电源Upward compatibility 向上兼容性81URL(User Requirements Language) 用户要求语言USE(User System Evaluator) 用户系统评价程序User 用户,使用者User interface 用户接口Utility control console 实用控制台Utility program 实用程序Utility unit 实用设备VValue 值,算式Variable format 可变格式Varying bandwidth 可变宽带Vector graphics 向量图Version 文本,版本Very-high-level programming language 超高级程序设计语言Video compression 视频压缩Video computer system 可视计算机系统Video conference 视频会议Video file 可见文件Video memory 视频存储器Video scan 视频扫描Virtual classroom 虚拟教室83Virtual container 虚容器Virtual memory 虚拟机存储器Virtual office 虚拟办公室Virus 病毒Visual 图象的Visual programming 直观程序设计VLSI(Very-large-scale Integration) 超大规模集成电路Voice encoding techniques 语音编码技术Voice mail 声音邮件Voice output device 声音输出装置Voice recognition system 声音识别系统Volatile file 易变文件Volatile memory 易失性存储器VR(Virtual Reality) 虚拟现实VRAM(Video Random Access Memory) 视频随机存取存储器84VRM(Virtual Resource Manager) 虚拟资源管理程序VSAM(Virtual Sequential Access Method) 虚拟顺序存取法85WWait state 等待状态WAN(Wide Area Network) 广域网络Web browser 网页浏览器Web business 网上商务Web site 网站Wideband subscriber loop system 宽带用户环路系统Window mode 窗口方式Windows operating system Windows 操作系统。

CIRCUIT NOISE EXTRACTION USING FORCED INPUT NOISE

专利名称:CIRCUIT NOISE EXTRACTION USING FORCEDINPUT NOISE WAVEFORM发明人:Lun Ye,Diwakar Ramadasu,Shruthi Arun申请号:US13672999申请日:20121109公开号:US20140137063A1公开日:20140515专利内容由知识产权出版社提供专利附图:摘要:Techniques for use in integrated circuit design systems for extracting noise threshold data for selected cells. For example, a method comprises the following steps.A cell is selected from one or more cells in a given collection of standardized cells. Eachof the one or more cells represents one or more functional circuit design blocks that are usable as part of a design of an integrated circuit. A noise signal is generated or selected. The noise signal is applied to an input node of the selected cell. Noise threshold data is identified using a noise analysis module, for a given set of process, voltage and temperature variations, for an output node of the selected cell based on the noise signal applied to the input node of the selected cell. The noise threshold data is stored with the selected cell as part of the given collection of standardized cells such that the noise threshold data is subsequently usable during a post layout noise analysis operation of an integrated circuit design that includes the selected cell.申请人:LSI CORPORATION地址:Milpitas CA US国籍:US更多信息请下载全文后查看。

低相噪低温漂介质振荡器设计

低相噪低温漂介质振荡器设计作者:张文锋高晓强来源:《科技资讯》2021年第13期摘要:该文设计了一款低相噪、低温漂同轴介质振荡器,该振荡器主要包括三部分:负阻电路部分、同轴介质谐振部分、输出缓冲放大部分。

其中,负阻部分和缓冲放大部分使用MMIC工艺实现,谐振部分采用同轴介质和薄膜工艺实现,整体组装采用微组装工艺,在实现产品小型化的同时,达到了低相噪、低温漂的设计目标。

最终产品的尺寸为:14 mm×14mm×5 mm。

测试结果表明:在电源电压+9 V、电调电压0~9 V条件下,该产品的输出频率为2.958~2.988 GHz,相位噪声为-107 dBc/Hz@10 kHz,温漂为:3 MHz。

关键词:负阻单片同轴介质谐振器低相位噪声低温漂中图分类号:TN752 文献标识码:A文章编号:1672-3791(2021)05(a)-0010-05Abstract: In this paper, a low phase noise, low temperature drift CRO is designed. The oscillator mainly includes three parts: negative resistance circuit part, coaxial dielectric resonance part, output buffer amplifier part. Among them, the negative resistance part and buffer amplification part are realized by MMIC process, the resonant part is realized by coaxial medium and thin film process, and overall assembly is realized by micro-assembly process. While realizing the product miniaturization, the design goal of low phase and low temperature drift is achieved. The size of the final product is 14 mm×14 mm×5 mm. The test results show that the output frequency of the product is 2.958~2.988 GHz, the phase noise is -107 dBc/Hz@10 kHz, and the temperature drift 3 MHz under the condition of the power supply voltage +9 V and the electric regulating voltage 0~9 V.Key Words: Negative resistance MMIC; Coaxial dielectric resonator; Low phase noise; Low temperature drift隨着现代通信系统、雷达系统的蓬勃发展,对频率源器件的相位噪声以及尺寸要求越来越高,压控振荡器作为频率源的核心器件,其相位噪声的好坏以及尺寸的大小会直接影响频率源系统最终的相位噪声性能以及尺寸[1]。

集成CMOS模拟电路 第七章 噪声

2 / 3 。深亚微米工艺下其值更大,0.25微米工艺下为2.5。

该系数也是随漏源电压变化的。本书中认为器件是长沟道器件。

CMOS模拟集成电路设计 第七章 噪声 Copyright 2013, zhengran

15

7.2 噪声的类型

例: 求单个MOS管能产生的最大热噪声电压。

2 2 Vn2,out I n rO 2 4kT(2 / 3) g m rO

CMOS模拟集成电路设计 第七章 噪声 Copyright 2013, zhengran

6

7.1 噪声的统计特性

1、噪声谱 噪声谱函数也称噪声的功率谱密度(PSD:Power Spectral Density) 函数,表示每Hz频率上信号具有的功率大小。x(t)的PSD函数Sx(f), 被定义为f附近1Hz带宽内x(t)具有的平均功率。 也就是把x(t)加到一个中心频率为f1带宽为1Hz的带通滤波 器,对输出取平方,在一个较长的时间内计算其平均值,就 得到了Sx(f1)(图a)。经过同样的处理可以得到Sx(fn),最后得到 2 波形如图(b)所示。其单位为 V Hz 或 V Hz 。

MOS晶体管的欧姆区热噪声 这里所说的欧姆区包含了多晶硅 区域(栅)和有源区(D/S) 。管子比 较宽的时候,有源区的电阻可以 忽略掉。但栅的分布电阻会较大。 栅电阻分布可以用(c)等效。采用 下图所示的方法进行栅连接可以有 效的减小栅的等效电阻。(本章的 分析不考虑欧姆区热电阻)

CMOS模拟集成电路设计

本章我们将介绍噪声时域和频域特性、噪声的类型、噪声在 电路中的表示方法以及噪声对各种电路的具体影响。

CMOS模拟集成电路设计

第七章 噪声

Copyright 2013, zhengran

电动机和磁悬浮技术相关内容说明书

IndexAC motor,461active magnetic bearings,1,10 actuator,111,152 electrostatic,488gain,117measuring,131micro magnetic,487 model,330model assembly,117 response limitations,127stiffness,117voice coil,495actuator offset,mechanical,187 aerodynamic losses,136,140 aeroengine,279aerospace,7air drag losses,159algorithmlevitation control,467P+2,467P-2,467aliasing,236,245alloyscobalt,93AMB system model,328Amp´e re’s loop law,115Amp´e re’s law,72amplifier,112analog,97losses,148operating modes,126 power,69,77,97 switching,97,450transconductance,121 transpermance,122analogcontrol,229,231,233 electronics,229filter,245hardware,236analog-to-digital A/Dconversion channel,230 conversion resolution,231,233,245 conversion time,231,238 converter,229,230,233,234,246 anti-aliasingfilter,231,236,333 applications of AMB,17arithmeticsfixed-point,220floating point,245integer,220,245,246artificial heartimplantable,480pump,462,480artificial heart pump,17automatic balancing,426auxiliary bearing,389,407,412,513 contact,407,410,412–421,423,424 contact modes,413–421,423,424 friction,413,415,419,424 touchdown recovery,410,427,431 axialself-bearing motor,477axis of geometry,215back-up bearing,389524Indexbackward difference,239,242 backward whirl,390,396,413,414,424 balancingactive,516automatic,426bandwidth,320,321power bandwidth,153base motion,409Beams,Jesse,499bearingauxiliary,407,412ball,475combined,motor,461elastic suspension,260forces,171,173homopolar,140,148load capacity,81PM repulsion,477stiffness,153,173thrust,magnetic,93bearingless motor,461bi-quad representation,246biascurrent,31–33,35,41,79,224flux,28linearization,79,95,440,443 permanent magnet,95,468 bismuth,496blade loss,409braking torque,135,144cylinder,141disc,141measurement,146cable losses,138,148Campbell diagram,207,212 capacitive displacement sensor,103 casing model,339center of gravity control,361central difference,243chaotic motion,390characteristic polynomial,35,61 characteristics of AMB,15circuitmagnetic,74classification of AMB,10closed loop model,341cobalt alloys,93coefficientdrag,141,144influence,420coercivefield intensity,74coilconfiguration,411design,82,88temperature,88winding scheme,90collocated,199,203,204non-,194,199,200,203,208 collocation,437combined motor bearing,461 compliancedynamic,66compressorslosses in,149conductor,71conicalmode,198,199,206,208,210–212, 214motion,198continuous-time,233control,237,240,243–245differential equation,233 eigenvalue,235,240equivalent,243frequency variable,236plant,233,234,238signal,239system,234–238,240,243 control,29,33,152H∞,37,52,57,61,214,242,367μ,370axial,220bandwidth,41,205,211,321 center of gravity,361COG coordinate,210–212 complexity,383conical mode,211,212,214,224 current,49–52,193–195,224 decentralized,342decentralized/local,194–197,199, 203–208,210,212 decoupled,208,211,212,224 design,33,34,37,52,54,193,208, 215digital,29,38,50,57,65,220 digital PID,471fault tolerant,514Index525flexible rotor,194,215force,34,37,207,209gain,65gain compensation,322gain scheduled,377harmonic,426levitation,467linear,31,34,53,54LPV,377LQ,243LQ/LQG,54,56,214LQG,441MIMO(multi-channel),30,52,65, 204,208,219minimal energy,160Mixed PID,361modal,209,210moment of force,209non-collocated PID,352order,57parallel mode,211,212,214,224 passive,28,57,375PD,418,425,467,479PD/PID,39,42,44–46,57,194,196, 199,205–208,213,237,239–245 phase,65phase compensation,322phase lag,47phase lead,321PID,47,342,411,413,417pole-placement,54,56,214,243rigid body,194,199,214robust,42,57,61,513roll off,205SISO(single-channel),30,51,65,208, 219state estimator/observer,214state space,52,53,60 synchronous,378,426,427 synchronous current,220,223 synchronous displacement,220 synchronous force,221,222,224 system,69μ−synthesis,37,52,57,61,214,242 tilt and translate,361unbalance,215–217,219,220,224, 378,426underlying current,49,50 underlying force,51voltage,49,50,53,54,224 controllerdesign,319cooling,81,151,158coordinatesbearing,193center of gravity/mass(COG),193, 194,196,211,212sensor,193,209copper losses,137copper resistance,87corrective procedures,516couplingA-B,208,211cross-,208,211,214de-,211coupling effects,174cracked rotor,410critical speed,167,182,183 bending,215,217,218rigid body,216,220,221currentmeasurement,105phase,475sheet,466,468,470damping,28,29,34,36,39,61,65,66, 153,199,206,212,337critical,36,43cross-,203external,204,259inner,203matrix,196,201,203,210,213“natural”,196,208nutation,207overcritical,36synchronous,216undercritical,36dead time,238decentralized control,342 decomposition,199,210degree of freedom(DOF),28,30,51, 52,59,65,191,196,208,213 delay,333computation,231,245,246 sampling,238–241,243–246time,230,231,245densitygas,141526Indexdependability,507design,147coil,88limitations,151magnets,81quality,510software,510systematic checks,510thrust magnetic bearings,93touch-down bearing,401 destabilization,199,201,203,208,214 diagnosis,316,515active,515diamagnetic materials,6,495difference equation,233differentialdriving mode,linearization,80 sensing,101differential equation,59,195,210 closed-loop,35,212first-order,52,53homogeneous,36,55 inhomogeneous,58matrix,193,194,196,201,210,213 second-order,53state space,213vector,52differential winding,124digitalcontrol,229,231,233,237,245 control design,243control,PID,471filter,231,245hardware,230,231signal processor,467,472,478,482 digital signal processor(DSP),229,230, 232,245,247,248digital-to-analog D/Aconversion resolution,231 conversion time,231converter,229–231,233,234,236,245 discrete-time,233control,233,236–241,244,245 eigenvalue,235,240equivalent,243filter,241frequency response,236frequency variable,236plant,237,244system,231,233,235,236,240 transfer function,236,241diskrigid model,413displacementvirtual,78dither,generalized,443dragviscous,140drag coefficient,141,144shrouded cylindrical rotor,142droprotor,412dynamiccompliance,66stiffness,28,34,46,63,66 dynamicsrigid rotor,167dynamic stiffness,153Earnshaw’s theorem,5eccentricity,169eddy current losses,135,137,139,159 eddy currents,14,84,130,452 sensor,101,482eigendamping,37,41 eigenfrequencies,30,37,41,59,171 closed-loop,205,208gyroscopic effects,176nutation,207,212rigid body,205,207,208,212 eigenmode,55backward,198bending,205closed-loop,205conical,198,204,206,207 coupling,200decomposition,198forward,204,206nutation,207,212parallel,198,204precession,198rigid body,205,206,209 eigenvalues,36,50,53,55,58,61,196, 198,206,235–237,240,246,320 closed-loop,34,36,40,41,196,198, 199conjugate complex,35open-loop,33,35,49,205,208Index527real,36,201trajectory,196,197,199,212 electro-dynamic levitation,14 electromagnet,27–30,32,35,44,69, 115inductance,436elevator guideways,435,442energymagnetic,489equations of motionflexible rotor,272estimationparameter,447Euler angles,191Euler-Bernoulli beam model,337 exampleH∞control,369actuator model,120asymmetric rotor,375center of gravity control,362 mixed PID control,362non-collocated PID control,352 PID control,344PID performance analysis,351 rotor sensitivity,360sensitivity analysis,357system model,336tilt and translate control,362 excitation,182backward whirl,187external,58force,28,58,59forward whirl,185frequency,58,59harmonic,55mechanical sources,187node,62non-periodic,188parametric,188periodic,55sensor and actuator offset,187 unsymmetries of the rotor,188 factorforce-current,k i,79force-displacement,k s,79fail-safe,513failure modes,411failures of AMB,508,513Faraday’s law,115,436fault detector,411fault tolerance,407faults,516AMB system,408rotor,409,410feedback,34gain,41,42integrating,45,47output,54,56,57state,54,56,214velocity,43,47ferromagnetic,28,35ferromagnetic materials,6,73,495fieldmagnetic,71filteranti-aliasing,333Finite Element Method,251,267 model reduction,292finite element modeling,82flexibilityrotor,319flexiblemode shapes,rotor,324flexible rotor,155,191,193,194,203, 205,208,215,251,263 equations of motion,272with AMB,288fluid bearingidentification,312,313fluid structure interaction,312fluxdistribution,465leakage,88measurement,105flywheels,17losses in,149forcelevitation,465Lorentz,70,473,494magnetic,77,152 magnetomotive,75maximum,152specific,489force-free,223,224force/currentfactor,33,45,48,192matrix,210528Indexrelationship,31,45force/displacementfactor,33,192matrix,193relationship,31,33forced vibrations,256aeroengine,285response,262unbalance,284forcesbearing,171nonconservative,167,174,179 forward whirl,414,419Fourier/frequency analyzer,247 FPGA,231free rotor,175free-free mode shapes,324frequency domain,57,59,61 frequency response,34,52,55,60–63, 223,236,237,241,243,244 amplification,58–60amplitude,59–61identification,302matrix,61measurement,247,249phase,60,61unbalance,185friction,413,415,419,424gain compensation,322gain margin,356gain scheduled control,377gap sensor,467gas density,141gas friction losses,136,140graphitepyrolithic,496gyrodynamics,176gyroscopic effects,173,176elastic rotor,274gyroscopics,28,65,231,242,247,248, 377effect,191,198,200,204,208,211 matrix,194,196,198,199,201,213 rotor,202H-bridge,98Hall effect,105current measurement,107hallbach array,497harmonic balance,420harmonic control,426heartartificial,pump,462,480 implantable,artificial,480 transplant,480heat loss,84heteropolar,159heteropolar magnetics,82high speed,7high speed rotor,154high temperature,158 homopolar,159homopolar bearing,140,148 homopolar magnetics,83,97hybridmagnetic bearing,468 hysteresis,74,151,491losses,159hysteresis losses,137,138identification,229,247,252,299,516 for diagnosis,316excitation by AMB,305fluid structure interaction,312 parameter estimation,304 response functions,302 implantable artificial heart,480 impulse responseidentification,302inductance,72,76 electromagnet,436inertia properties,167influence coefficient,420 information processing,152initial condition,36,52 instrumentation,39built-in,230,246,247external,247,248integratorgain,PID controller,346inter-sample skew,230,231 interlacingdefect repairing,326pole-zero,323interrogation signal,446,450,454 iron resistivity,139ISO standardsIndex529for AMB,509quality,509sensitivity,358unbalance,181Jeffcott rotor,252kinematic viscosity,141lamination,139Laval rotor,252leakageflux,88levitationcoil current,470control,467control algorithm,467force,465Levitron,5lifetime at high temperature,158 LIGA,487linearperiodic,443time invariant,439linearity/nonlinearity,31,33,41,43,48, 50,51,57linearization,28,33,44,46,48,49,124 bias,95current bias,79square root,126load capacity,39,44,47,67,81,151 radial bearings,92specific,92thrust bearing,94loadscentrifugal,491torque,467Lorentzforce,473self-bearing motor,462,473Lorentz force,10,13,70,494loss mechanisms,135losses,135,159aerodynamic,140,147amplifier,148cable,138,148copper,84,137eddy current,135,137,139 electrical power,95gas friction,140hysteresis,137,138iron,84,147magnetic,136mitigation,147power amplifier,138rotational,492stator,148windage,135,140,501low passfilter,205,215,239,241,242, 245LPV control,377LQG control,440,441Lyapunovfunction,448machinesmart,411MAGLEV,6,14magnetpermanent,496rare earth,496magneticcircuit,74field,71field energy,77flux,71flux density,71force,77permeability,72polarization,73saturation,81,92,435,453 magnetic actuator,111magnetic bearingactive,27–29,37,47active micro,498hybrid,29,468Lorentz force,27passive,27–29,37reluctance force,27 superconducting,27types,493magnetic displacement sensor,103 magneticfluxload capacity,151magnetic force,10magnetic loss,136magnetism,70magnetization curve,76 magnetomotive force,75530Indexmaintainability,410margin,gain and phase,356massmatrix,194,201,203,213rotor,205materialscarbonfiber,155cobalt,152diamagnetic,6,495 ferromagnetic,6,10,151,495for high temperature,158 strength,94superconducting,12,495 maximum singular value,350 measurementforce,306mechanical energyconversion,48kinetic,52potential,52mechatronics,39,135definition,4MEMS,487micro magnetic actuator,487 microprocessor,229–231,245,247,248fixed-point,220MIMOcontrol,230,231,246control design,241–243,245,247 measurement,247transfer function,247,248modal analysis,252for rotating structures,307modal parameters,300modal truncation,337mode shapesflexible rotor,324free-free,324modelactuator,330AMB system,328assembly,335casings and substructures,339 closed loop,341Euler-Bernoulli beam,337rotor,331sensor,332state space,113,329structure,330synchronously reduced,342 modelingfinite element,82modes,337modulationpulse-width,97moment of inertiapolar,206transverse,205,206monitoring,229,230,247,248motorAC,461,468axial self-bearing,477 bearingless,461combined,bearing,461 induction,466,500Lorentz self-bearing,462,473self-bearing,461,479self-bearing or bearingless,27 motor control,230multi-processor,230multiplexer,230,246multiply-accumulate(MAC),246 natural vibrations,256,262 aeroengine,279flexible rotor,277networkthermal,85non-collocation,320,323non-conservative forces,167,179,203, 214matrix,213,214nonlinearmagnetic analysis,76nonlinear dynamicsamplitude jump,428aperiodic response,415contact modes,413–421,423,424 rotordynamics,413–421,423,424 normvector,349H∞,366notchfiltergeneralized,216,219,220 nutation,167,178Nyquist frequency,236–238Ohm’s law,436Index531operating point,31,34,35,45,48 optical displacement sensor,104 optimizationbearing geometry,88order reduction,246,373oscillationamplitude,37,58damped,36,37,43harmonic,37,58periodic,37phase,58pseudo-periodic,37 oscilloscope,247,248over-sampling,231Pad´e approximation,333Pad´e approximation,245parallelmode,198,199,204,206,208,210–212,214paramagnetic material,73 parameter estimation,304 parameter estimator,447parametric excitation,188PD control,321,418,425,467,479 performanceassessment,347peripheral,229–231permanent magnets,5,12,28,29,31, 95bias,468permeability,10persistency of excitation,447,450 phasecurrents,475phase compensation,322phase laganti-aliasingfilter,236sampling delay,237–239,244 phase lead controller,321phase margin,238,356PIDcontrol,digital,471PID control,342,411,413,417non-collocated,352pinned beam,320plantMIMO,208rigid body,208polarity sequence,140polarizationmagnetic,73poles,320angle,78number,463pair number,464plus two or minus two,462 salient,466–468shoes,88transfer function,323positionsensor,99position reference command,44–46 position sensor,69,435powerspecific,489power amplifier,27,29,41,42,44,50, 69,77,97,153bandwidth,50,56current,29,44,48,49dynamics,30,34,44,57voltage,29,48power amplifier losses,138power bandwidth,153power failure,410power supply,513precession,167,178precision bearings,161preventive maintenance,229,248 principal/inertial axis,215,223,224 probeproximity,478processordigital signal,467,472,478,482 properties of AMB,15proximityprobe,478pulse width modulation(PWM),97, 224signal pattern,230unit,229,231pumpartificial heart,462,480 performance,482rotary blood,480real time operating system,510 recomposition,209532Indexredundancy,408–411,511 reliability,505reluctance force,10remanence,74resistancecopper,87resistivityiron,139resonance,182rigid body,221responseunbalance,351,467,468,472,475, 479response functionsidentification,302 measurement,303retainer bearing,389Reynolds number,140rigid disk model,413rigid rotor,320equations of motion,171rigid rotor/body,191,193,194,196, 200,204,208,210,212,214 robust control,513robustness,34,50,56,57,61,63,356 root locus,325rotaryblood pump,480rotationforce-free,160high speed,7high-speed,154precision,161rotational losses,492rotor,29-stator contact,33,62drop,412excitation,182flexibility,319flexible,155,251,263free,175model,331modes,337non-rotating,175position,29,30,39,46,47rigid,320rigid,dynamics,167velocity,52rotor lossesmeasurement,146rotor responsebackward whirl,413,419contact modes,413,418,424 forward whirl,414rotor speedgyroscopic effects,176influence on eigenfrequencies,178 rotor/stator contact,390rub,410,414,419,420,423,424,431 safety,505definitions,507philos.background,506salient pole,466–468sample-and-hold,230,234sampling period,231,233,234,239,241 sampling rate/frequency,231,233,236, 237,244–246saturation,74,151dynamic,205magnetic,81,435,453numerical,220power amplifier,223scaling,489,490secant algorithm,239,242,244self monitoring,411self–sensing,435self-bearing motor,27,461,479 sensitivity,355ISO standards,358sources of,361sensitivity function,62,63sensor,27,41,42capacitive,displacement,103 displacement,position,411 dynamics,30,34,44,57eddy current,29,101,482gap,467inductive,29inductive,displacement,101 magnetic displacement,103model,332noise,56optical,3optical displacement,104position,69,99transverseflux,102sensor offset,mechanical,187Index533Shannon theorem,236,245signalinterrogation,446,450,454signal generator,247signal injection,247singular value,350SISOcontrol,230,241transfer function,247size of the bearing,158skew-symmetric,194,201,203,211 small gain theorem,356smartdefinition,514examples,514machines,514smart machine,411smart machine technology,161 software,510as a machine element,4 development system,510specific force,489specific load capacity,152specific power,489speedsupercritical,155spring-damper,28,34,37,49 mechanical,30,31,34,44square root linearization,126 stability margins,gain and phase,356 stability of motion,171,174stability/instability,28,31,33,35 asymptotic,58,61closed-loop,41,57limit-stable,36open-loop,30,35,49,50 stabilization,29,33standards,509for magnetic bearings,9ISO,sensitivity,358state spacedescription,196,214matrix,199state space model,113,329statorslotless,474slotted,474stiffness,30,34,36,39,42,44,61,65, 66,199closed-loop,39,42compensation matrix,211,212,224 coupling,214cross-,201,203dynamic,28,34,46,63,66,153 external,222high,41,42low,40,50matrix,196,201,203,210,213 mechanical,31“natural”,42,196,208negative bearing,31,33,40,42,45, 193,194,211,223,224static,28,34,42,47,63,67strengthmaterial,94stresses,centrifugal forces,154 substructure model,339 superconducting materials,495 superconductivity,12,14,18 superconductor,495suspensionactive,29five axes,29passive,28permanent magnet,29rigid body,30switchingamplifier,97,446,450noise,97ripple,446,450three state,451symmetric,194,198,201,203–205,208, 211,212non-,199,212synchronous control,378,426,427 synchronously reduced model,342 synthesisμ,370system model,328technology of AMB,9temperaturecoil,88test rigaeroengine,279for identification,312534Indexfor modal analysis,308for touch-down,391thrust magnetic bearings,93tilt and translate control,361tilting motion,198time domain,36,55,59–61timer interrupt,232torquebraking,135,144dynamic,479load,467reaction,473rotating,468,471touch-down bearing,389ball bearings,400contact dynamics,391contact force,399control reconfig.,518design guidelines,401friction force,395test rig,391time history of touch-down,399,400 vertical axis arrangement,403whirl motion,396touchdown,407,413avoiding,407,426dynamics,412recovery,410,427,431 transconductance amplifier,112,121 transfer function,60–64,211,219,235, 236,241,247,248matrix,60,219poles and zeros,323transformFFT,61Fourier,55,61Laplace,59,60transformationZ,236bilinear,243Fast Fourier(FFT),247Laplace,235matrix,193,209–211natural coordinates,365Tustin,243transitionmatrix,235sampling instant,234,235state,233translational motion,211 transpermeance amplifier,122 transplantheart,480transportation,6transverseflux sensor,102turbo–molecular pump,435,444turbo-machinery,17turbomolecular pumps,149 unbalance,38,256,409,413,414,420 adaptation,216,218 compensation,516definition,180excitation,55excitation of rotor vibr.,183force attenuation,28,216forced vibrations,284forward whirl,185quality grade,181residual,215,216response,215,220,222,224,262,468, 472,475,479technical example,169vibration attenuation,216 unbalance control,229,378,426 unbalance response,351,467unit circle,235,236unsymmetry of the rotor,188 vacuum,501vacuum applicationslosses in,149velocity,34,43,48,52,53,239velocity measurement,104vertical axis,403vibrational control,443vibrationsbending,461forced,256,284,285natural,167,171,175,256,262,277, 279steady state,475virgin magnetization curve,84virtual displacement,78viscositykinematic,141viscous drag,140voice coil actuator,495Index535voltage control,439whirlbackward,413,414forward,414whirl motion,396whirl,forward and backward,167,178 windage losses,135,136,140,501windingdifferential,124zero power control,160zero-order hold(ZOH),233,234,238, 239,243zerostransfer function,323。

qca非门容错设计和仿真