第3章 VHDL数据类型与顺序语句

合集下载

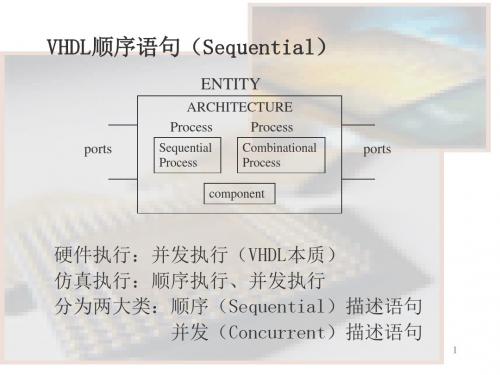

VHDL顺序语句(Sequential)

17

…… L2: loop a:=a+1; exit L2 when end …… loop L2; a >10;

18

2)for

…

loop 语句

loop

[标号]:for 循环变量 in 离散范围 顺序处理语句; end l 内部自动声明的局部量, 仅在 loop 内可见;不需要指定其变化方式。 ② 离散范围必须是可计算的整数范围: 整数表达式 to 整数表达式 整数表达式 downto 整数表达式

PROCESS BEGIN -- sequential statements WAIT ON (a,b) ; END PROCESS;

38

二、块语句

块语句将一系列并行描述语句进行组合,目 的是改善并行语句及其结构的可读性。可使结构 体层次鲜明,结构明确。 语法如下:

标记:block [( 块保护表达式 )]

when 值|值|值|…|值 => 顺序处理语句;

以上三种方式的混合;

when others => 顺序处理语句;

14

Case 语句使用注意:

1)分支条件的值必须在表达式的取值范围内。 2)两个分支条件不能重叠。 3)CASE语句执行时必须选中,且只能选中一 个分支条件。

4)如果没有others分支条件存在,则分支条

{ 块说明项 } begin { 并行语句 } end block [ 标记 ];

39

1、块语句的使用不影响逻辑功能 以下两种描述结果相同: 描述一: a1: out1<=‘1’ after 2 ns; a2: out2<=‘1’ after 2 ns; a3: out3<=‘1’ after 2 ns; 描述二: a1: out1<=‘1’ after 2 ns; blk1: block begin a2: out2<=‘1’ after 2 ns; a3: out3<=‘1’ after 2 ns; end block blk1;

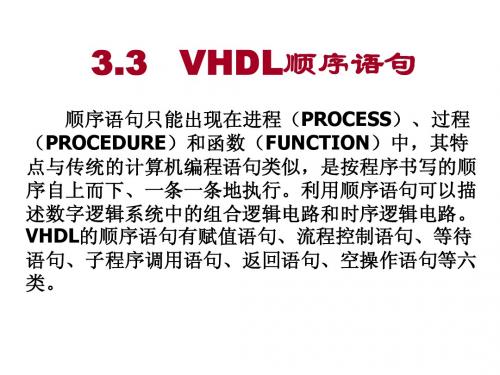

3.3 VHDL顺序语句

VHDL顺序语句 3.3 VHDL顺序语句

顺序语句只能出现在进程( )、过程 顺序语句只能出现在进程(PROCESS)、过程 )、 (PROCEDURE)和函数(FUNCTION)中,其特 )和函数( ) 点与传统的计算机编程语句类似, 点与传统的计算机编程语句类似,是按程序书写的顺 序自上而下、一条一条地执行。 序自上而下、一条一条地执行。利用顺序语句可以描 述数字逻辑系统中的组合逻辑电路和时序逻辑电路。 述数字逻辑系统中的组合逻辑电路和时序逻辑电路。 VHDL的顺序语句有赋值语句、流程控制语句、等待 的顺序语句有赋值语句、 的顺序语句有赋值语句 流程控制语句、 语句、子程序调用语句、返回语句、 语句、子程序调用语句、返回语句、空操作语句等六 类。

PROCESS(a) ( ) BEGIN IF (a(7)=‘0’) THEN y<=”111”; ( ) ) ; ELSIF (a(6)=’0’) THEN y<=”011”; ELSIF (a(5)=’0’) THEN y<=”101”; ELSIF (a(4)=’0’) THEN y<=”001”; ELSIF (a(3)=’0’) THEN y<=”110”; ELSIF (a(2)=’0’) THEN y<=”010”; ELSIF (a(1)=’0’) THEN y<=”100”; ELSE y<=”000”;

IF语句 一、IF语句 格式1 格式1:IF 条件句 Then 顺序语句; 顺序语句; IF; END IF; 格式2:IF 条件句 Then 格式2 顺序语句; 顺序语句; ELSE 顺序语句; 顺序语句; IF; END IF;

格式3:IF 条件句 Then 格式3 顺序语句; 顺序语句; ELSIF 条件句 Then 顺序语句; 顺序语句; … ELSE 顺序语句; 顺序语句; IF; END IF;

顺序语句只能出现在进程( )、过程 顺序语句只能出现在进程(PROCESS)、过程 )、 (PROCEDURE)和函数(FUNCTION)中,其特 )和函数( ) 点与传统的计算机编程语句类似, 点与传统的计算机编程语句类似,是按程序书写的顺 序自上而下、一条一条地执行。 序自上而下、一条一条地执行。利用顺序语句可以描 述数字逻辑系统中的组合逻辑电路和时序逻辑电路。 述数字逻辑系统中的组合逻辑电路和时序逻辑电路。 VHDL的顺序语句有赋值语句、流程控制语句、等待 的顺序语句有赋值语句、 的顺序语句有赋值语句 流程控制语句、 语句、子程序调用语句、返回语句、 语句、子程序调用语句、返回语句、空操作语句等六 类。

PROCESS(a) ( ) BEGIN IF (a(7)=‘0’) THEN y<=”111”; ( ) ) ; ELSIF (a(6)=’0’) THEN y<=”011”; ELSIF (a(5)=’0’) THEN y<=”101”; ELSIF (a(4)=’0’) THEN y<=”001”; ELSIF (a(3)=’0’) THEN y<=”110”; ELSIF (a(2)=’0’) THEN y<=”010”; ELSIF (a(1)=’0’) THEN y<=”100”; ELSE y<=”000”;

IF语句 一、IF语句 格式1 格式1:IF 条件句 Then 顺序语句; 顺序语句; IF; END IF; 格式2:IF 条件句 Then 格式2 顺序语句; 顺序语句; ELSE 顺序语句; 顺序语句; IF; END IF;

格式3:IF 条件句 Then 格式3 顺序语句; 顺序语句; ELSIF 条件句 Then 顺序语句; 顺序语句; … ELSE 顺序语句; 顺序语句; IF; END IF;

EDA技术 第04讲 VHDL03 顺序语句

SVEC(3) <= S2; --将最下面的赋予S2的值‘0’,赋给SVEC(3) S2; --将最下面的赋予S2的值‘ ,赋给SVEC(3) V1 := ‘0’; --将V1置入新值0 --将V1置入新值0 V2 := ‘0’; --将V2置入新值0 --将V2置入新值0 S2 <= ‘0’; --S2最后一次赋值,将覆盖上面准备赋入的‘1’ --S2最后一次赋值,将覆盖上面准备赋入的‘ END PROCESS; PROCESS; 自学课本P176的两个赋值进程举例.

12

集合块赋值目标:位置关联赋值方式和名字关联赋值方式。 【例3】 SIGNAL A,B, C, D :STD_LOGIC: A, STD_LOGIC: SIGNAL S: STD_LOGIC_VECTOR( 1 TO 4) S: ... VARIABLE E, F :STD_LOGIC; E, STD_LOGIC; VARIABLE G :STD_LOGIC_VECTOR(1 TO 2 ); ); VARIABLE H :STD_LOGIC_VECTOR(1 TO 4 ); ); S <= (‘ (‘0’,‘1’,‘0’,‘0’) ; ; --位置关联方式赋值 --位置关联方式赋值

HYIT

16

例5: library ieee; use ieee.std_logic_1164.all; entity dff3 is port(clk,d1: in std_logic; q1: out std_logic); end; architecture bh of dff3 is signal a,b: std_logic; begin process(clk) is begin

OUTPUT: OUTPUT:OUT BOOLEAN); BOOLEAN);

第三章VHDL语言数据类型及运算操作符

实数常量的书写方式举例

65971.333333

--十进制浮点数

8#43.6E+4#

--八进制浮点数

43.6E-4

--十进制浮点数

第三章VHDL语言数据类型及运算操作符

3、位(BIT)数据类型

位数据类型也属于枚举型,取值只能是1 或0。位数据类型的数据对象,如变量、信 号等,可以参与逻辑运算,运算结果仍是 位的数据类型。VHDL综合器用一个二进制 位表示BIT。在程序包STANDARD中定义 的源代码是:

第三章VHDL语言数据类型及运算操作符

总结:

在运行中不变,若要改变必须要改变设计, 也就是说改变常量说明,重新编译。

常量必须在程序的实体、结构体或过程的 说明区中,对其标识符类型常量值进行指 定。

定义在实体中的常量仅在实体中使用。以 此类推。

第三章VHDL语言数据类型及运算操作符

3.1.2变量(Variable)

线)信号,共有16个信号元素

第三章VHDL语言数据类型及运算操作符

以下示例定义的信号数据类型是设计者自 行定义的,这是VHDL所允许的:

TYPE FOUR IS(‘X’,‘0’,‘I’, ‘Z’);

SIGNAL S1﹕FOUR; SIGNAL S2﹕FOUR:=‘X’; SIGNAL S3﹕FOUR:=‘L’;

第三章VHDL语言数据类型及运算操作符

格式: CONSTANT 常数名:数据类型:=表达式; 例: CONSTANT VCC: REAL:=5.0; CONSTANT DALY:TIME:=100ns; CONSTANT BUS:BIT_VECTOR:=“1010 ” CONSTANT G1:BIT:= ‘ 1’; 数据类型和表达式表示的数据类型应该一致。 ‘ ’表示是位信息, 而 “ ”表示的是位矢量

EDA VHDL第三章顺序语句

3.4 VHDL描述语句

例:变量赋值实现循环语句功能 process(indicator, sig) variable temp: std_logic; begin temp:='0'; for i in 0 to 3 loop

temp:=temp xor (sig(i) and indicator(i));

3.4 VHDL描述语句

顺序语句:

1. 赋值语句 2. WAIT语句 3. IF 语句 4. CASE 语句 5. L00P 语句 6. NEXT语句 7. EXIT语句 8. RETURN语句 9. NULL 语句 10.过程调用语句 11.断言语句

3.4 VHDL描述语句

一、对象与赋值语句

所有对象分:变量和信号 对象:=表达式; 对象<=表达式; --变量赋值 --信号赋值

要求: 表达式的值必须与对象的类型.宽度一致

3.4 VHDL描述语句

2. 变量赋值与信号赋值

变量赋值与信号赋值的差异

1)赋值方式的不同:

变量:=表达式; 信号<=表达式; 2)硬件实现的功能不同: 信号代表电路单元、功能模块间的互联,代表

实际的硬件连线;

变量代表电路单元内部的操作,代表暂存的临 时数据。

3.4 VHDL描述语句

3)有效范围的不同

信号:程序包、实体、结构体:全局量 变量:进程、子程序:局部量 ARCHITECTURE {SIGNAL Declarations} label1:PROCESS {VARIABLE Declarations} .................. label2:PROCESS {VARIABLE Declarations}

output<=temp;

VHDL语言的顺序语句

vhdl语言的顺序语 句

目 录

• 顺序语句概述 • 顺序语句概述 • 赋值语句 • 条件语句 • 循环语句 • 控制流语句

01

CATALOGUE

顺序语句概述

过程块(process block)

过程块是顺序语句的一种形式,它包含一系列的顺序语句,按照一定的顺序执行。

过程块通常在仿真过程中按照时间顺序逐行执行。

loop-statement循环语句

语法示例

```vhdl

loop_statement: process(some_signal)

loop-statement循环语句

01

02

begin

• 循环体

03

if some_condition then

loop-statement循环语句

• 条件满足时执行的代码

并行过程块(concurrent process block)

并行过程块是另一种形式的顺序语句,它包含一系列的顺序语句,这些语句在仿真过程中同时执行。

并行过程块通常用于描述数字系统的并发行为。

02

CATALOGUE

赋值语句

连续赋值语句

总结词

在连续赋值语句中,信号或变量的值 在每个仿真时间步都会更新。

case语句

end case;

```

conditional语句

描述:类似于其他编程语言中的三元操作符。

01

02

语法

```vhdl

03

04

signal_name <= "0" when condition else "1";

```

05

06

上述语句表示,如果条件为真,则将 `signal_name`设置为"0",否则设置为 "1"。

目 录

• 顺序语句概述 • 顺序语句概述 • 赋值语句 • 条件语句 • 循环语句 • 控制流语句

01

CATALOGUE

顺序语句概述

过程块(process block)

过程块是顺序语句的一种形式,它包含一系列的顺序语句,按照一定的顺序执行。

过程块通常在仿真过程中按照时间顺序逐行执行。

loop-statement循环语句

语法示例

```vhdl

loop_statement: process(some_signal)

loop-statement循环语句

01

02

begin

• 循环体

03

if some_condition then

loop-statement循环语句

• 条件满足时执行的代码

并行过程块(concurrent process block)

并行过程块是另一种形式的顺序语句,它包含一系列的顺序语句,这些语句在仿真过程中同时执行。

并行过程块通常用于描述数字系统的并发行为。

02

CATALOGUE

赋值语句

连续赋值语句

总结词

在连续赋值语句中,信号或变量的值 在每个仿真时间步都会更新。

case语句

end case;

```

conditional语句

描述:类似于其他编程语言中的三元操作符。

01

02

语法

```vhdl

03

04

signal_name <= "0" when condition else "1";

```

05

06

上述语句表示,如果条件为真,则将 `signal_name`设置为"0",否则设置为 "1"。

第3章 VHDL数据类型与顺序语句

3.1 VHDL数据类型

3.1.4 布尔数据类型BOOLEAN

布尔(BOOLEAN)数据类型 在程序包STANDARD中有定义 它是一个二值枚举型数据类型,取值有FALSE和TRUE两种。 综合器用一个二进制位表示布尔型变量或信号。 例如,当A大于B时,在IF语句中的关系运算表达式(A>B) 的结果是布尔量TRUE,反之为FALSE。综合器将其变为1或0信 号值。

根据IEEE库程序包STD_LOGIC_1164中的数据类型。数据类 型STD_LOGIC定义的九种值如下所示:

'U','X',‘0‟,'1','Z','W','L','H','-'

3.1 VHDL数据类型

3.1.2 STD_LOGIC和STD_LOGIC_VECTOR类型 'U','X',‘0‟,'1','Z','W','L','H','-'

与逻辑运算,运算结果仍是位数据类型。VHDL综合

器用一个二进制位表示BIT。在程序包STANDARD中

有定义。

3.1 VHDL数据类型

3.1.1 BIT和BIT_VECTOR类型

2) 位矢量(BIT_VECTOR)数据类型 位矢量是基于BIT数据类型的数组,在程序包STANDARD

中有定义

使用位矢量必须注明位宽,即数组中的元素个数和排列, 例如: SIGNAL A﹕BIT_VECTOR (7 DOWNTO 0);

顺序语句只能出现在进程(Process)和子程序中,子程 序包括函数和过程。 一个进程是由一系列顺序语句构成的,而进程本身属并行 语句,在同一设计实体中,所有的进程是并行执行的。

EDA VHDL第三章 VHDL数据类型和运算操作符

illegal%name _illegalname 9illegal entity data_ _BUS Not-Ack

上一次课的内容

程序包、库和配置 VHDL四类语言要素:数据对象、词法规则与 标识符 本次课程内容:

数据类型、 运算操作符

扩展标识符

扩展标识符是VHDL‟93版增加的标识符书写规则: (1)用反斜杠来定界,免去了87标准基本标识符的一些限制。 (2) 可以数字打头,允许包含图形符号、空格符。 例如:\mode A, \$100\, \p%name\等。 (3)反斜杠之间的字符可以用关健字。 如:\buffer\, \entity\, \end\等。 (4) 标识符的界定符两个斜杠之间可用数字打头。 如: \100$\,\2chip\,\4screens\等。 (5) 允许多个下划线相连。例:\TWO_Computer_sh\等。 (6) 扩展标识符区分大小写。例如: \EDA\ 与\eda\不同。 (7) 扩展标识符与短标识符不同。 如:\COMPUTER\ 与Computer不同。

3.3.2 词法规则与标识符

1.词法规则 1) 注释 以--开头直到本行末尾(出现回 车或换行符)的文字

提高VHDL语言设计程序的可读性,

1.词法规则

2) 数字

表达方式:十进制,二进制、八进 制、十六进制等为基的数 ①十进制整数表示法 78_567(=78567) ②以基表示的数 格式: 基数符号#数值#指数部分

举例如下: VARIABLE result: std_logic:='0' ; VARIABLE x,y: integer; VARIABLE a:integer range 0 to 255 :=0 ;

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

3.1 VHDL数据类型

3.1 VHDL数据类型

3.1.6 其他预定义类型

1. 字符类型

标识符的大小写一般是不区分的,但用了单引号的大小写是区分的

2. 实数类型

类似于数学上的实数,其取值范围为:-1.0E38∽+1.0E38

3. 字符串类型

字符数据类型的一个非约束型数组,或称为字符串数组,字符串必须用双引号标明

各值的含义是: 'U'--未初始化的,'X'--强未知的, ‘0‟--强0,'1'--强1,'Z'--高阻态,'W'--弱未知的, 'L'--弱0,'H'--弱1, '-„ --忽略。

在程序中使用此数据类型前,需加入下面的语句: LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL ;

3.1 VHDL数据类型

3.1.5 SIGNED和UNSIGNED类型

SIGNED和UNSIGNED类型的数据可以进行算术运算和 关系运算,但不能进行逻辑运算,显然这和整数类型相 同。

3.1 VHDL数据类型

3.1.5 SIGNED和UNSIGNED类型

Synopsys公司在IEEE库中加入的程序包STD_LOGIC_ARITH中定 义了如下的数据类型:

3.1 VHDL数据类型

3.1.5 SIGNED和UNSIGNED类型

2) 有符号数据类型(SIGNED TYPE)

SIGNED数据类型表示一个有符号的数值,综合器将其解释

为补码,此数的最高位是符号位,例如:SIGNED(“0101”) 代 表 +5 ; SIGNED(“1011”) 代表 -5。 若将上例的VAR定义为SIGNED数据类型,则数值意义就不同 了,如: VARIABLE VAR﹕SIGNED(0 TO 10); 其中,变量VAR有11位,最左位VAR(0)是符号位。

3.1 VHDL数据类型

3.1.7 数据类型转换函数

3.1 VHDL数据类型

3.2 VHDL最常用的顺序语句

顺序语句和并行语句是VHDL程序设计中

两大基本描述语句系列。

顺序语句是相对于并行语句而言Fra bibliotek,其 特点是每一条顺序语句的执行(指仿真执行) 顺序是与它们的书写顺序基本一致的 。

3.2 VHDL最常用的顺序语句

顺序语句只能出现在进程(Process)和子程序中,子程 序包括函数和过程。 一个进程是由一系列顺序语句构成的,而进程本身属并行 语句,在同一设计实体中,所有的进程是并行执行的。

任一给定的时刻内,在每一个进程内,只能执行一条顺 序语句。一个进程与其设计实体的其他部分进行数据交换的 方式只能通过信号或端口。 VHDL有六类基本顺序语句:赋值语句、流程控制语句、等 待语句、子程序调用语句、返回语句和空操作语句。

3.2 VHDL最常用的顺序语句

转向控制语句

转向控制语句通过条件控制开关决定是否执行一条 或几条语句,或重复执行一条或几条语句,或跳过一条 或几条语句。转向控制语句共有五种:CASE 语句、IF 语句、LOOP语句、NEXT语句和EXIT语句。

3.2 VHDL最常用的顺序语句

3.2.1 赋值语句

3.1 VHDL数据类型

3.1.4 布尔数据类型BOOLEAN

布尔(BOOLEAN)数据类型 在程序包STANDARD中有定义 它是一个二值枚举型数据类型,取值有FALSE和TRUE两种。 综合器用一个二进制位表示布尔型变量或信号。 例如,当A大于B时,在IF语句中的关系运算表达式(A>B) 的结果是布尔量TRUE,反之为FALSE。综合器将其变为1或0信 号值。

3.1 VHDL数据类型

数据类型可以分成四大类

标量型(SCALAR TYPE): 用于描述一个单值数据对象,包括 实数类型、整数类型、枚举类型和时间类型。 复合类型(COMPOSITE TYPE):由细小的数据类型(如:标量)复 合而成。复合类型主要有数组型(ARRAY)和记录型(RECORD)。 存取类型(ACCESS TYPE) :为给定的数据类型的数据对象提 供存取方式。 文件类型(FILES TYPE) :用于提供多值存取类型。

信号赋值语句 变量赋值语句

赋值目标

赋值符号

赋值源

3.2 VHDL最常用的顺序语句

3.2.1 赋值语句

1.信号和变量赋值

赋值语句有两种,即信号赋值语句和变量赋值语句。 变量赋值与信号赋值的区别在于: 变量的有效只局限于所定义的一个进程中,或一个 子程序中,是局部的、暂时性数据对象。它的赋值是立 即发生的,即是一种时间延迟为零的赋值行为。 信号与之不同,信号具有全局性特征,它可作为设 计实体内部各单元之间数据传送的载体,而且可通过信 号与其他的实体进行通信(端口本质上也是一种信号)。 信号赋值过程总是有某种延时的,它反映了硬件系 统并不是立即发生的 。

根据IEEE库程序包STD_LOGIC_1164中的数据类型。数据类 型STD_LOGIC定义的九种值如下所示:

'U','X',‘0‟,'1','Z','W','L','H','-'

3.1 VHDL数据类型

3.1.2 STD_LOGIC和STD_LOGIC_VECTOR类型 'U','X',‘0‟,'1','Z','W','L','H','-'

与逻辑运算,运算结果仍是位数据类型。VHDL综合

器用一个二进制位表示BIT。在程序包STANDARD中

有定义。

3.1 VHDL数据类型

3.1.1 BIT和BIT_VECTOR类型

2) 位矢量(BIT_VECTOR)数据类型 位矢量是基于BIT数据类型的数组,在程序包STANDARD

中有定义

使用位矢量必须注明位宽,即数组中的元素个数和排列, 例如: SIGNAL A﹕BIT_VECTOR (7 DOWNTO 0);

3.1 VHDL数据类型

3.1.1 BIT和BIT_VECTOR类型

BIT 和BIT_VECTOR 可以参与多种运算操作,如逻辑运算,关系运算

以及算术运算

3.1 VHDL数据类型

3.1.1 BIT和BIT_VECTOR类型 1) 位(BIT)数据类型 位数据类型也属于枚举型,取值只能是1或0。

位数据类型的数据对象,如变量、信号等,可以参

3.2 VHDL最常用的顺序语句

3.2.1 赋值语句

【例】 SIGNAL S1,S2:STD_LOGIC;

PROCESS(S1,S2) VARIABLE V1,V2:STD_LOGIC; BEGIN V1 := ‘1’; --立即将V1置位为1 V2 := ‘1’; --立即将V2置位为1 S1 <= ‘1’; --S1被赋值为1 S2 <= ‘1’; --在本进程中,这个S2不是最后一个赋值语句 , 不作赋值操作 V1 := ‘0’; --将V1置入新值 0 V2 := ‘0’; --将V2置入新值 0 S2 <=‘0’; --由于这是S2最后一次赋值,赋值有效, --此‘0’将上面准备赋入的‘1’覆盖掉 END PROCESS;

3.2 VHDL最常用的顺序语句

3.2.1 赋值语句

变量赋值语句和信号赋值语句的语法格式如下:

变量赋值目标 := 赋值源;

信号赋值目标 <= 赋值源;

在信号赋值中,需要注意的是,当在同一进程中,同 一信号赋值目标有多个赋值源时,信号赋值目标获得的是 最后一个赋值源的赋值,其前面相同的赋值目标不作任何 变化。

3.1 VHDL数据类型

3.1.7 数据类型转换函数

conv_std_logic_vector 函数的转换结果是将被转换的数据先转换 成2进制补码形式,然后取其低“位长”,作为输出。 conv_std_logic_vector 函数的转换结果是将被转换的数据先转换 成2进制补码形式,然后取其低“位长”,作为输出。

UNSIGNED数据类型代表一个无符号的数值,例如,十进 制的8可以作如下表示: UNSIGNED(“1000") 要定义一个变量或信号的数据类型为UNSIGNED,则其 位矢长度越长,所能代表的数值就越大。

VARIABLE VAR﹕UNSIGNED(0 TO 10); SIGNAL SIG﹕UNSIGNED(5 DOWNTO 0); 其中,变量VAR有11位数值,最高位是VAR(0),而非 VAR(10);信号SIG有6位数值,最高位是SIG(5)。

3.1

VHDL数据类型

这四大数据类型可分为:在现成程序包中可以 随时获得的预定义数据类型和用户自定义数据类型

两个类别。预定义VHDL数据类型是VHDL最常用、最

基本的数据类型。这些数据类型都已在VHDL的标准

程序包STANDARD和STD_LOGIC_1164及其他的标准程

序包中作了定义,在设计中可随时调用。

无符号型(UNSIGNED)、 有符号型(SIGNED)、小整型(SMALL _INT)。 在使用之前,注意必须加入下面的语句:

LIBRARY IEEE; USE IEEE.STD_LOGIC_ARITH.ALL ;

3.1 VHDL数据类型

3.1.5 SIGNED和UNSIGNED类型

UNSIGNED用于无符号数的运算,SIGNED用于有符号数的运算。 1) 无符号数据类型(UNSIGNED TYPE)

信号A被定义为一个具有8位位宽的矢量,它的最左位是 A(7),最右位是A(0)。

3.1 VHDL数据类型

3.1.2 STD_LOGIC和STD_LOGIC_VECTOR类型